#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/109953

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Design, Simulation, Fabrication and Characterisation of 4H-SiC Trench MOSFETs

By

#### Zohreh Mohammadi

Dissertation Submitted for the Degree of

Doctor of Philosophy

School of Engineering

June 2018

# Table of Contents

| List  | of Figures                                                | v     |

|-------|-----------------------------------------------------------|-------|

|       | of Tables                                                 | xiii  |

| Decla | aration                                                   | XV    |

| Ackn  | nowledgement                                              | xvii  |

|       | ications List                                             | xviii |

| Abst  | ract                                                      | xix   |

| List  | of Abbreviations                                          | XX    |

| Char  | oter 1: Background Theory                                 |       |

| 1.1   | Wide Band Gap Material                                    | 1-5   |

|       | 1.1.1 High Avalanche Breakdown Electric Field             | 1-6   |

|       | 1.1.2 High Electron Saturation Velocity                   | 1-6   |

| 1.2   | Metal Oxide Field Effect Transistor (MOSFET) Structures   | 1-7   |

|       | 1.2.1 On State                                            | 1-9   |

|       | 1.2.2 Off State                                           | 1-12  |

| 1.3   | MOS Capacitor                                             | 1-14  |

|       | 1.3.1 Characteristics of an Ideal MOS Capacitors          | 1-14  |

|       | 1.3.2 Inversion or Deep Depletion (Vg≪0)                  | 1-16  |

|       | 1.3.3 Depletion (Vg<0)                                    | 1-17  |

|       | 1.3.4 Accumulation Region (Vg> VTh)                       | 1-18  |

|       | 1.3.5 Electrical Properties of a MOS Capacitor            | 1-18  |

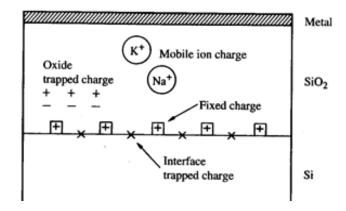

|       | 1.3.6 Charges                                             | 1-22  |

|       | 1.3.7 Leakage currents                                    | 1-29  |

|       | 1.3.8 Electrical Characteristics of Trench MOS Capacitors | 1-34  |

| 1.4   | Conclusion                                                | 1-42  |

| 1.5   | References                                                | 1-44  |

| Char  | oter 2: Literature Review                                 |       |

| 2-1   | Oxide Reliability                                         | 2-5   |

|       | 2.1.1 Optimization of Electric Field                      | 2-7   |

| 2-2   | Channel Mobility                                          | 2-13  |

| 2-3   | Time Dependent Dielectric Breakdown                       | 2-15  |

| 2-4   | Threshold Voltage Shift                                   | 2-16  |

| 2-5   | Conclusion                                                | 2-17  |

| 2-6   | References                                                | 2-18  |

| Char  | oter 3: Design and Simulation of 4H-SiC trench MOSFET     |       |

| 3.1   | Design of a 10 kV Trench MOSFET Ideal Structure           | 3-2   |

|       | 3.1.1 Drift region Design                                 | 3-2   |

|       | 3.1.2 P-body Design                                       | 3-4   |

|       | 3.1.3 Other Parameters                                    | 3-6   |

|       | 3.1.4 Ideal Structure of 10kV, 4H-SiC Trench MOSFET       | 3-7   |

|       | 3.1.5 Gate Protection                                     | 3-11  |

|       | 3.1.6 Threshold Voltage                                   | 3-14  |

| 3.2   | 1.2 kV Trench MOSFET                                      | 3-15  |

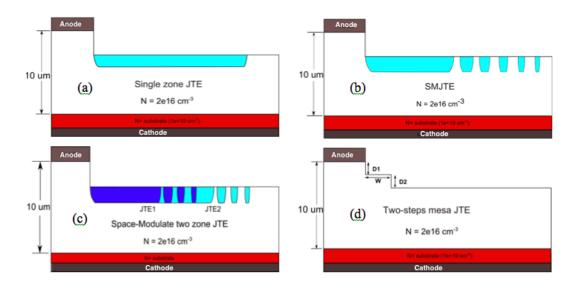

| 3.3  |           | e Trench Edge Termination                                      | 3-19  |

|------|-----------|----------------------------------------------------------------|-------|

| 3.4  | Concl     |                                                                | 3-29  |

| 3.5  | Refere    | ences                                                          | 3-30  |

| _    |           | tching of 4H-Silicon Carbide (SiC) by Inductively Coupled Plas | sma   |

|      | tive Ion  |                                                                |       |

| 4.1  | Challe    | enges in Fabricating Trenches in SiC                           | 4-6   |

|      | 4.1.1     | e                                                              | 4 - 7 |

|      | 4.1.2     | Origin of Striation                                            | 4-11  |

| 4.2  |           | iew of Dry Etching Process                                     | 4-16  |

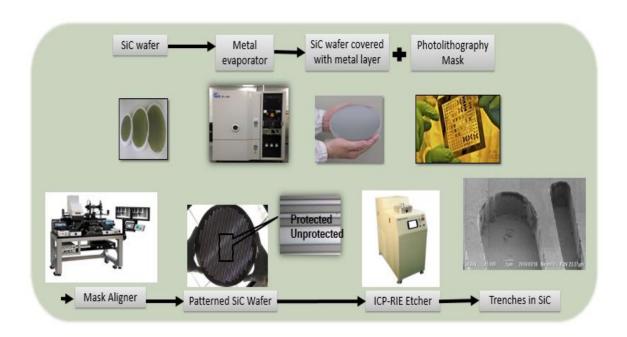

| 4.3  | _         | one: Sample and Mask Preparation                               | 4-19  |

| 4.4  | Step to   | wo: Photolithography process                                   | 4-24  |

|      | 4.4.1     | Experiments Setup                                              | 4-24  |

|      | 4.4.2     | Results                                                        | 4-36  |

| 4.5  | Step t    | hree: ICP-RIE etching of trenches in SiC                       | 4-50  |

|      | 4.5.1     | Experimental setup:                                            | 4-50  |

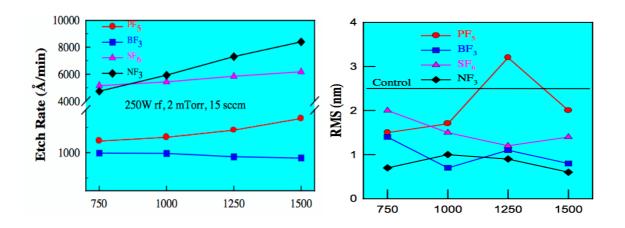

|      | 4.5.2     | Choice of Etching Gas                                          | 4-51  |

|      | 4.5.3     | Results                                                        | 4-57  |

| 4.6  | Conclu    | usion                                                          | 4-66  |

| 4.7  | Refere    | ences                                                          | 4-67  |

| Char | ter 5: Fa | abrication and Characterisation of 4H-SiC trench MOSFETs       |       |

| 5.1  |           | acterisation techniques                                        | 5-2   |

|      | 5.1.1     | - · · · · · · · · · · · · · · · · · · ·                        | 5-4   |

|      | 5.1.2     |                                                                | 5-7   |

|      | 5.1.3     | Threshold voltage measurement (VTh)                            | 5-8   |

|      |           | Field Effect Mobility (µFE)                                    | 5-10  |

|      |           | Current Density                                                | 5-11  |

|      |           | Drain to Source On State Resistance (RDS(on))                  | 5-11  |

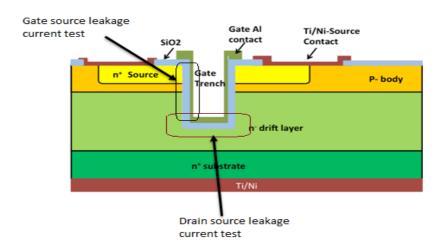

|      | 5.1.7     | Leakage currents                                               | 5-14  |

|      | 5.1.8     | Breakdown Voltage (Vbr)                                        | 5-15  |

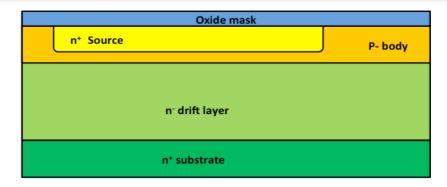

| 5.2  | Fabric    | eation Process of 4H-SiC Trench MOSFET                         |       |

|      | 5-16      |                                                                |       |

|      | 5.2.1     | Alignment marks                                                | 5-21  |

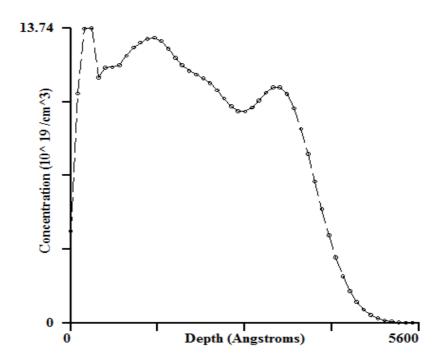

|      | 5.2.2     | Source Implantation                                            | 5-24  |

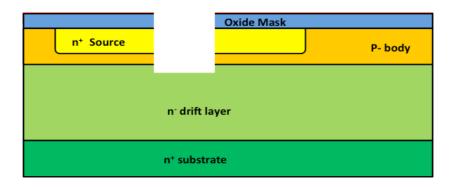

|      | 5.2.3     | Etching Trenches                                               | 5-27  |

|      | 5.2.4     | Cleaning Process                                               | 5-29  |

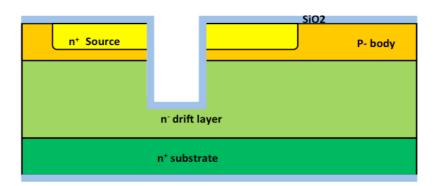

|      | 5.2.5     | Gate Oxide                                                     | 5-30  |

|      | 5.2.6     | Opening Source and Drain Contacts                              | 5-31  |

|      | 5.2.7     | Source and Drain Metal Contacts                                | 5-32  |

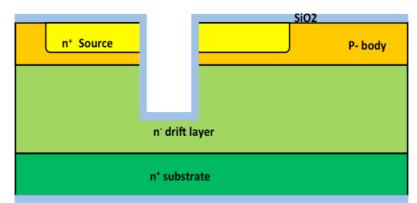

|      | 5.2.8     | Gate Metal Contact                                             | 5-34  |

| 5.3  | Result    |                                                                | 5-37  |

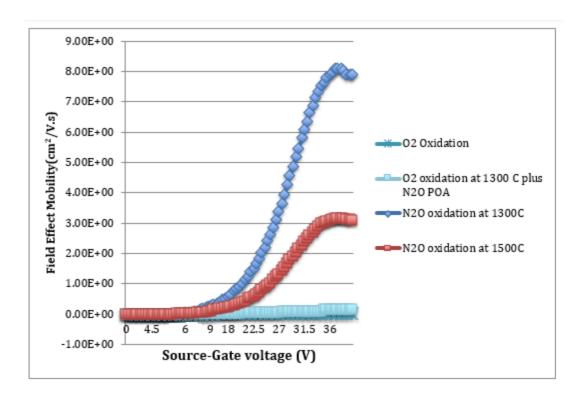

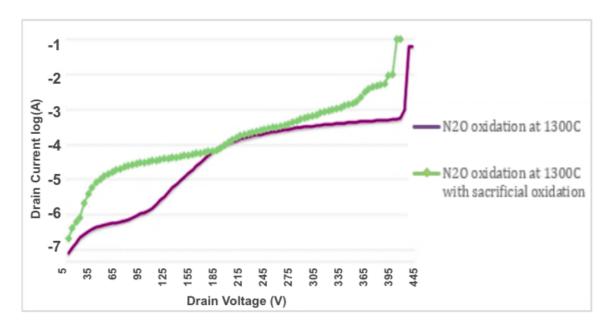

|      | 5.3.1     | Choice of the Gate Oxidation Method: Direct Nitrous Oxide (    |       |

|      |           | tion Growth                                                    | 5-38  |

|      | 5.3.2     | Post Oxidation Annealing (POA)                                 | 5-44  |

|      | 5.3.3     | Results: Comparison of Post Oxidation Annealing Methods        | 5-46  |

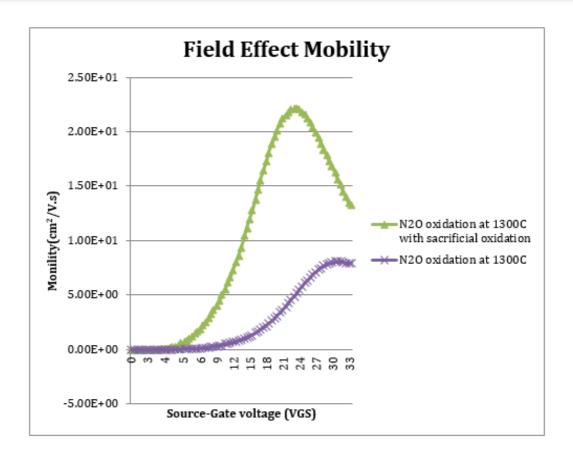

|      | 5.3.4     | Post Etch Treatments                                           | 5-59  |

|      | 5.3.5     | Comparison of all treatments types                             | 5-70  |

| 5 4  | Conclu    |                                                                | 5-81  |

| 5.5  | References                                      | 5-83 |

|------|-------------------------------------------------|------|

| Chap | oter 6: Recommendations                         |      |

| 6.1  | Improving Current Density and Breakdown Voltage | 6-2  |

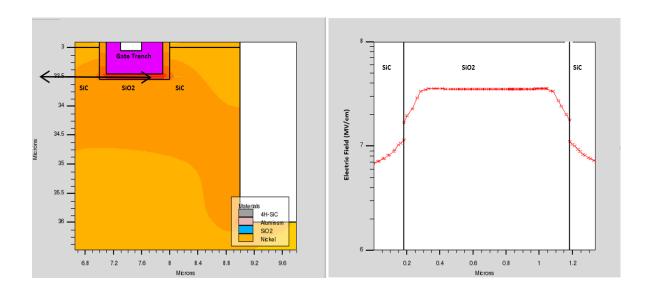

|      | 6.1.1 Gate Shield                               | 6-7  |

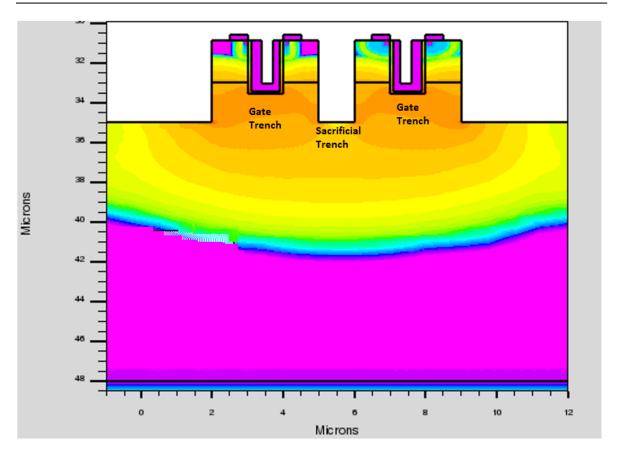

|      | 6.1.2 Sacrificial Trench                        | 6-12 |

| 6.2  | Sacrificial Oxidation                           | 6-14 |

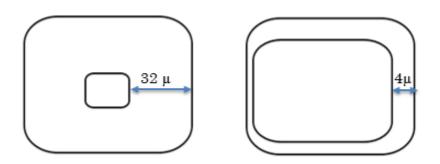

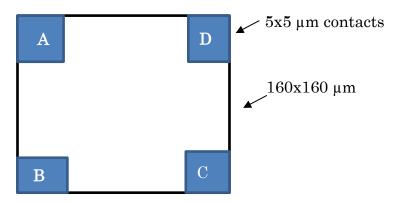

| 6.3  | Test Structures                                 | 6-15 |

| 6.4  | Accurate measurement of the channel mobility    | 6-18 |

| 6.5  | Reference                                       | 6-18 |

# List of Figures

| Figure 1.1: Structure of (A) planar MOSFET (B) trench MOSFET                                                                                                                                                                       | 1-10 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2: Current flow in trench MOSFET                                                                                                                                                                                          | 1-12 |

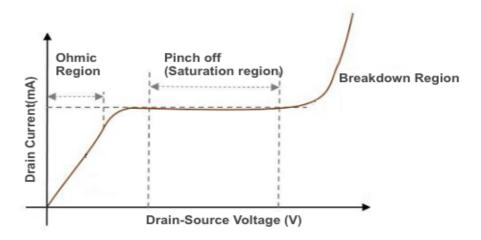

| Figure 1.3 : Current-Voltage characteristics of a MOSFET                                                                                                                                                                           | 1-13 |

| Figure 1.4: Depletion region created in a PN junction.                                                                                                                                                                             | 1-15 |

| Figure 1.5: Structure of a MOS capacitor                                                                                                                                                                                           | 1-17 |

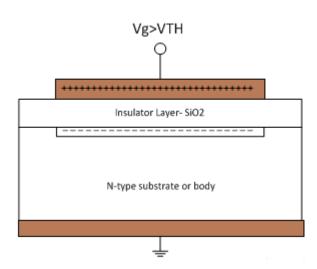

| Figure 1.6: Applying a large negative voltage to the gate results in two different behaviour in Si and SiC MOS capacitors, while inversion is observed in Si MOS capacitor (A), a deep depletion is created in a SiC MOS capacitor | 1-18 |

| Figure 1.7: Depletion mode in SiC MOS structure                                                                                                                                                                                    | 1-19 |

| Figure 1.8: Accumulation mode in MOS structure                                                                                                                                                                                     | 1-20 |

| Figure 1.9: The energy band models a n- type SiC MOS capacitor assuming no defects exist                                                                                                                                           | 1-22 |

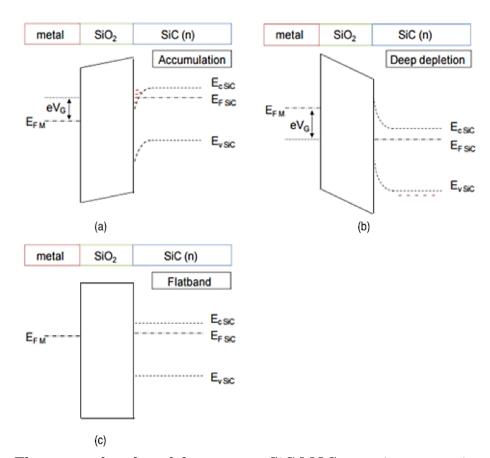

| Figure 1.10: Oxide charges in SiC MOS structures                                                                                                                                                                                   | 1-24 |

| Figure 1.11: Different type of trap charges                                                                                                                                                                                        | 1-26 |

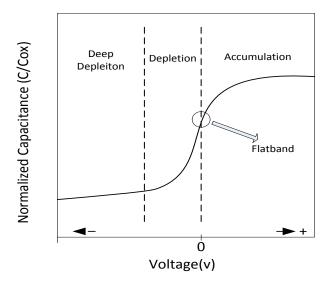

| Figure 1.12: C-V characteristic of an ideal n-type SiC MOS capacitor                                                                                                                                                               | 1-27 |

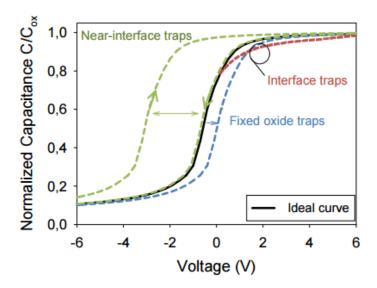

| Figure 1.13: changes in C-V graph induced by oxide and interface charges                                                                                                                                                           | 1-28 |

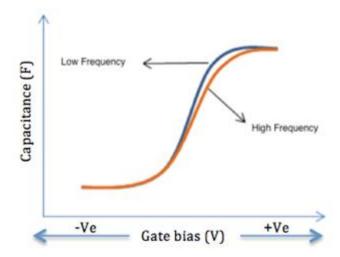

| Figure 1.14: High-low frequency measurement technique                                                                                                                                                                              | 1-29 |

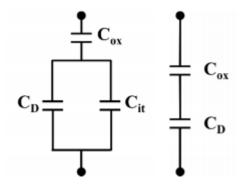

| Figure 1.15: The equivalent circuits of capacitance in MOS capacitor under (A) low and (B) high frequency measurement                                                                                                              | 1-29 |

| Figure 1.16: Quantum physics theory: Electron (blue in the picture) can pass the potential barrier and move from one medium to another medium                                                                                      | 1-32 |

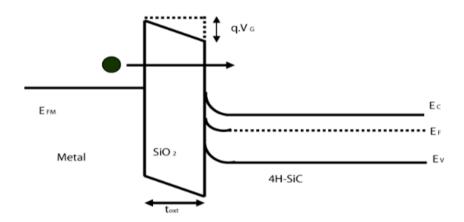

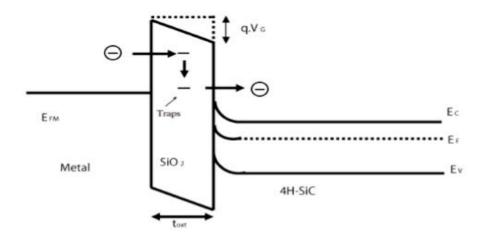

| Figure 1.17: Direct tunneling in a MOS capacitor                                                                                                                                                                                   | 1-32 |

| Figure 1.18: FN tunneling in MOS device                                                                                                                                                                                            | 1-33 |

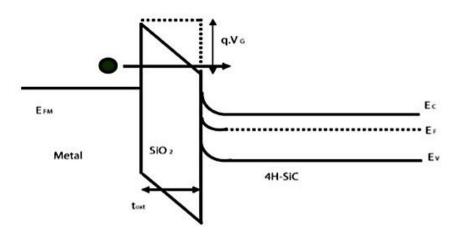

| Figure 1.19: Conduction (top) and valence band (bottom) offsets of different semiconductors with respect to SiO2                                                                                                                   | 1-35 |

| Figure 1.20: Trap assisted tunneling                                                                                                                                                                                               | 1-36 |

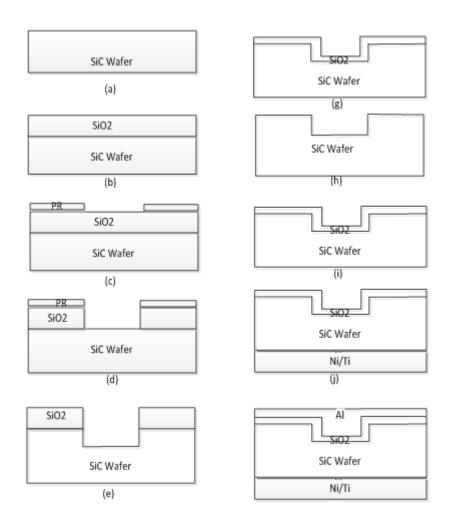

| Figure 1.21: Fabrication process of a trench MOS capacitor                                                                                                                                                                         | 1-38 |

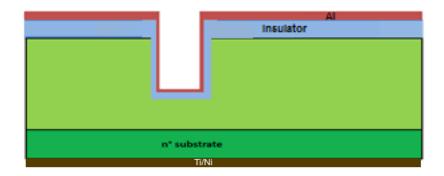

| Figure 1.22: Structure of trench MOS capacitor                                                                                                                                                                                     | 1-39 |

| Figure 1.23: 4H-SiC trench MOS capacitor (A) after etch (B) after gate metal deposition $$                                                                                                                                         | 1-39 |

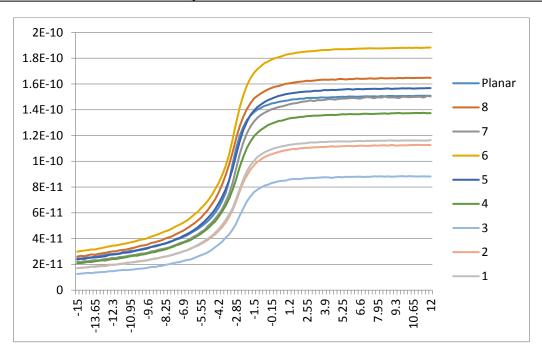

| Figure 1.24: C-V measurement of fabricated 4H-SiC trench MOS capacitors                                                                                                                                                            | 1-41 |

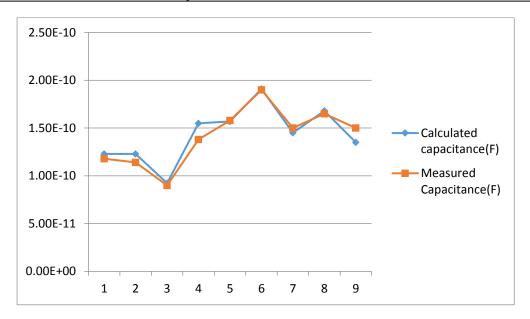

| Figure 1.25: Comparison of capacitance from measurement of the fabricated capacitors and ideal value (calculation).                                                                                                                | 1-49 |

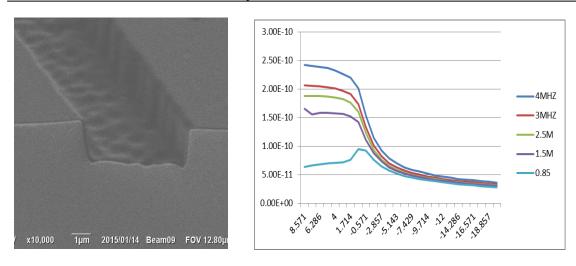

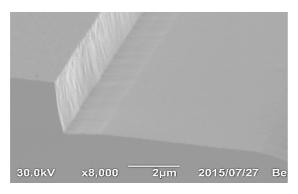

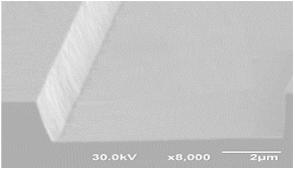

| Figure 1.26: 4H-SiC trench MOS capacitor with rough sidewalls (a) and its resulting C-V measurement                                                                                                                                        | 1-43       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

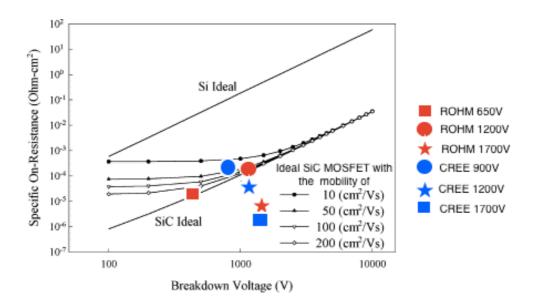

| Figure 2.1: Specific on-resistance vs. breakdown voltage of SiC devices                                                                                                                                                                    | 2-4        |

| Figure 2.2: Formation of a p-n junction showing charge, electric field and potential distribution                                                                                                                                          | 2-6        |

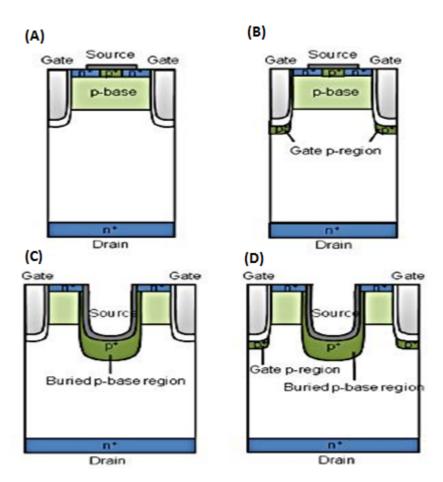

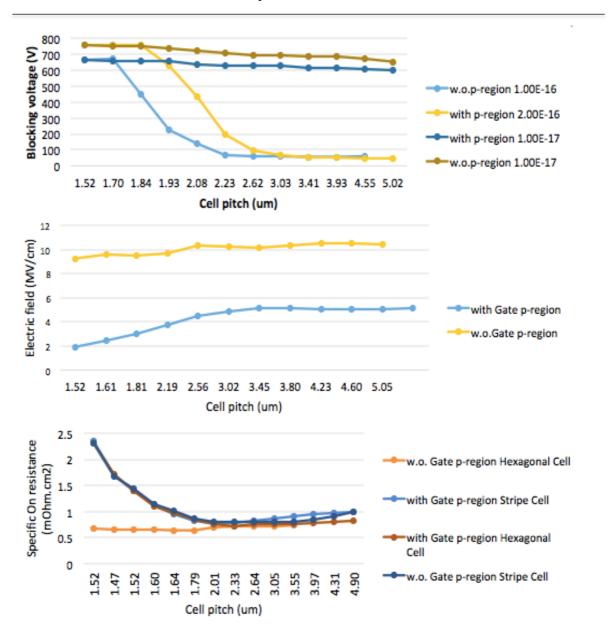

| Figure 2.3:A) conventional trench MOSFET (B) trench MOSFET with gate p-region c) buried p-region d) gate p-region and buried p-region                                                                                                      | 2-10       |

| Figure 2.4: Cell pitch dependence of (a) blocking voltage with different p-base dosage (b) gate oxide electric field at the breakdown and (c) specific on-resistance of the UMOSFET structure with Gate p-region and without gate p-region | 2-12       |

| Figure 2.5: Trench MOSFET with polysilicon trench                                                                                                                                                                                          | 2-13       |

| Figure 2.6: IOP-trench MOS transistor                                                                                                                                                                                                      | 2-14       |

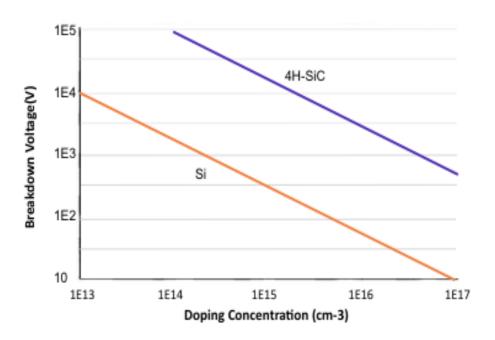

| Figure 3.1: Breakdown voltage for Abrupt Parallel Plane Junction                                                                                                                                                                           | 3-6        |

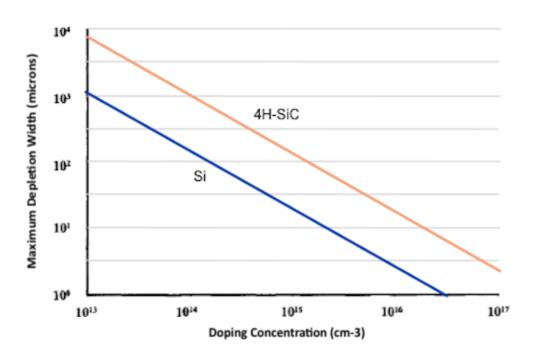

| Figure 3.2: Maximum Depletion Width at Breakdown in Si and SiC                                                                                                                                                                             | 3-7        |

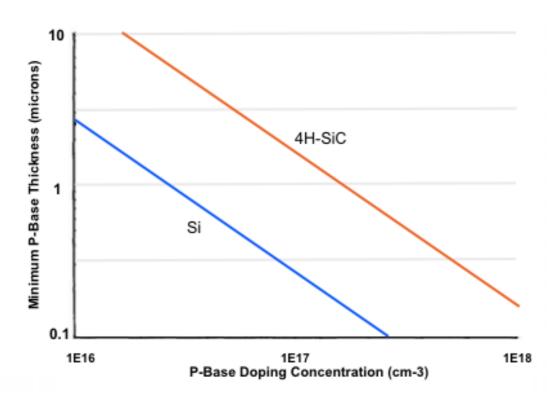

| Figure 3.3: Depletion layer width inside the P-body region in Si and 4H-SiC                                                                                                                                                                | 3-9        |

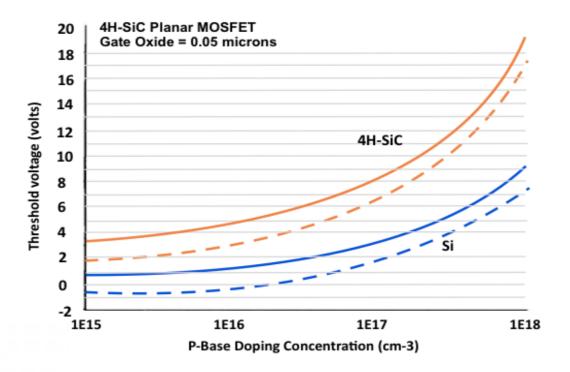

| Figure 3.4: Threshold voltage of 4H-SiC MOSFETs (dashed lines represent the use N+ polysilicon gate and an oxide fixed charge of 2x1011cm-2)                                                                                               | 3-10       |

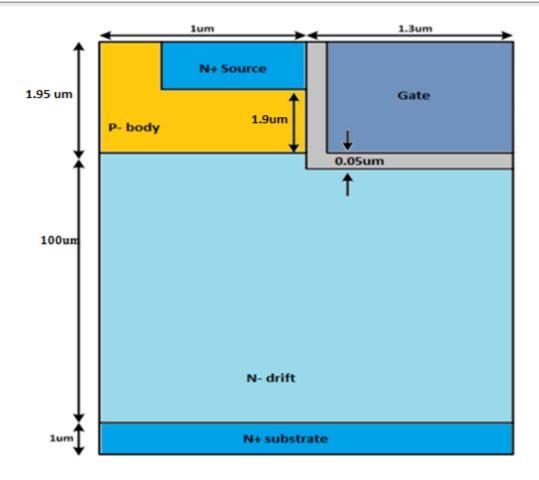

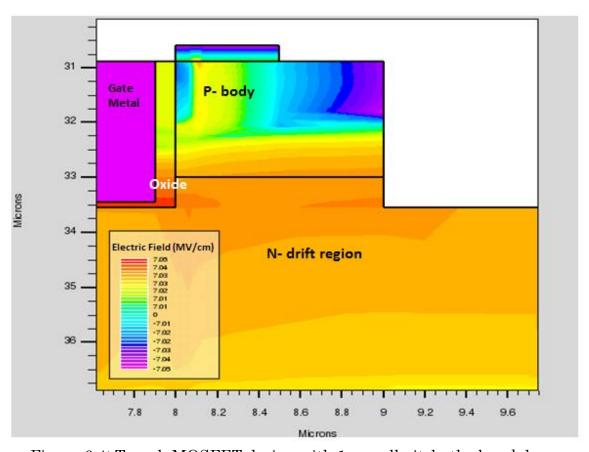

| Figure 3.5: Ideal structure of 4H-SC 10kV trench MOSFET (um=µm)                                                                                                                                                                            | 3-12       |

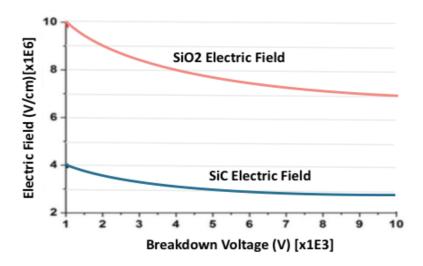

| Figure 3.6: Electric field on gate oxide and SiC drift region as a function of breakdown voltage for fixed drift thickness and different doping concentration of drift                                                                     | n<br>3-13  |

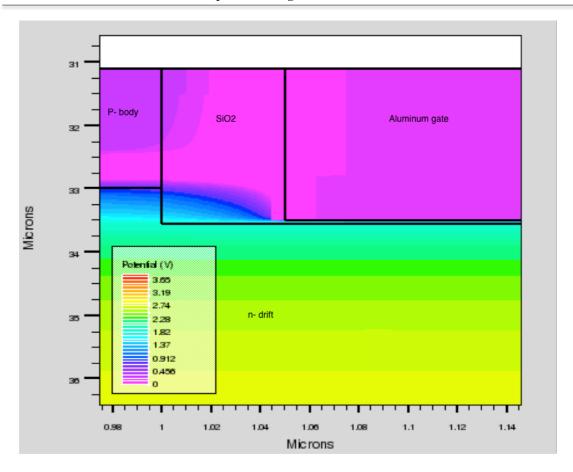

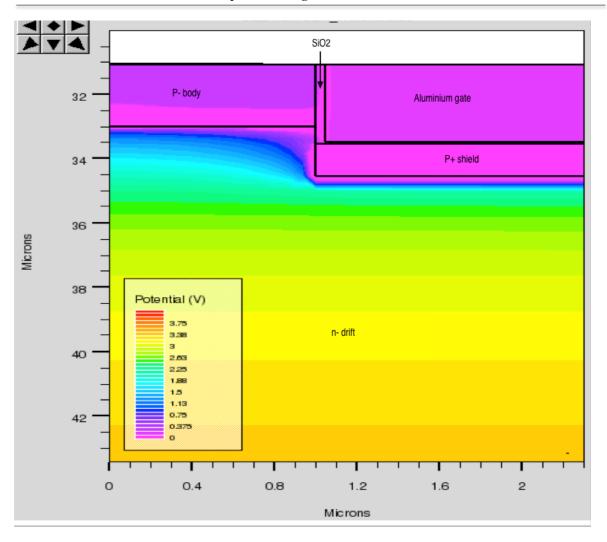

| Figure 3.7: The potential distribution at breakdown for 100 µm drift region and doping of 1.5x1015cm-3, the structure shows the potential across insulator has increased to a value more than zero.                                        | 3-14       |

| Figure 3.8: Potential distribution of shielded trench MOSFET with no gate voltage applied at 10KV for doping of 1.5x1015cm-3 and thickness of 100 µm                                                                                       | 3-16       |

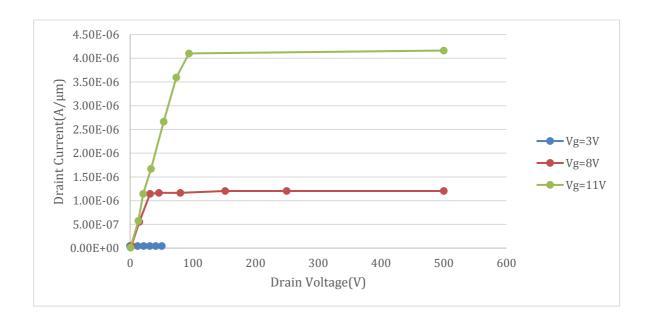

| Figure 3.9: Forward Characteristics of 10kV trench MOSFET with shield                                                                                                                                                                      | 3-17       |

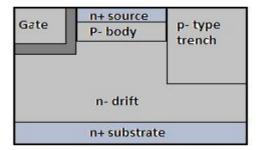

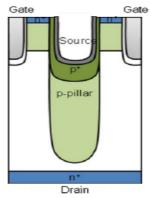

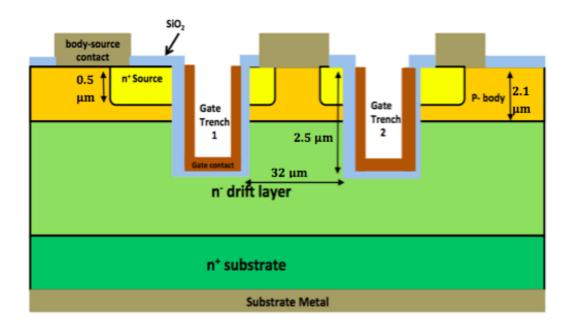

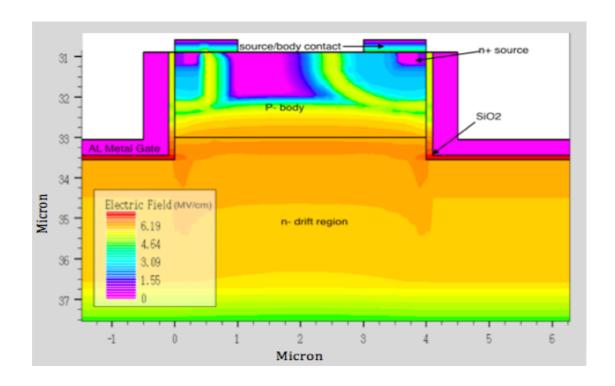

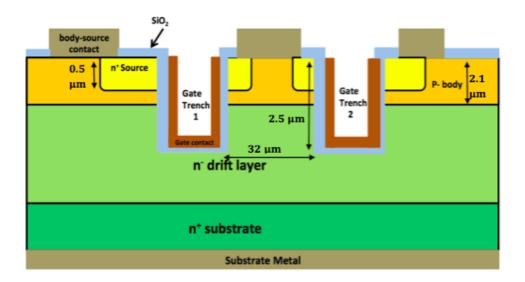

| Figure 3.10: Structure of 1.2 kV trench MOSFET (without junction termination) that was fabricated in this project                                                                                                                          | 3-20       |

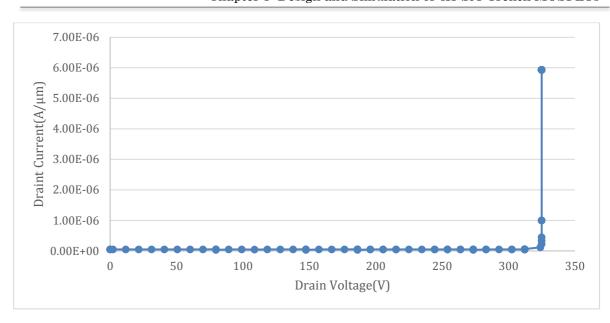

| Figure 3.11: Simulation results of the breakdown voltage of 1.2 KV trench MOSFET fabricated in this project.                                                                                                                               | 3-21       |

| Figure 3.12: Breakdown happens in the oxide layer at the corner of trenches i devices without gate protection                                                                                                                              | in<br>3-21 |

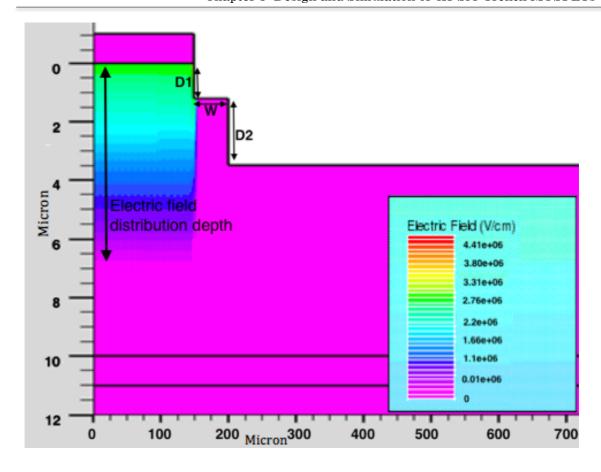

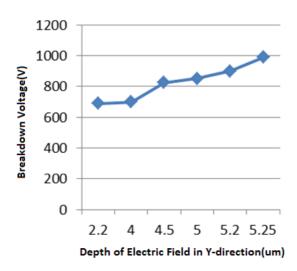

| Figure 3.13: Schottky diode with double trench junction termination                                                                                                                                                                        | 3-23       |

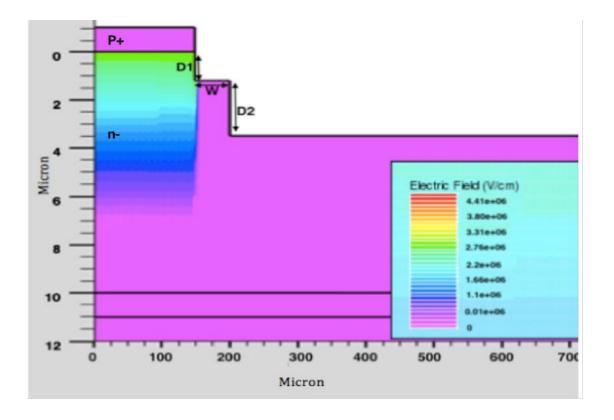

| Figure 3.14: Effect of Width on the electrical field distribution D1=1.4 µm and D2=3.5 µm are kept constant (a) W=5µm (b) W=2.5 µm                                                                                                         | 3-25       |

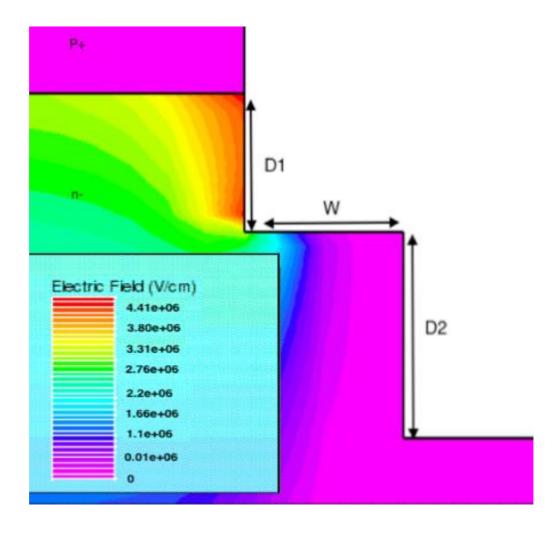

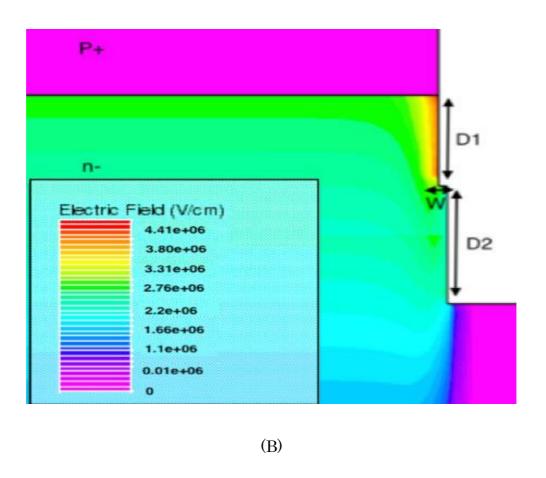

| Figure 3.15: Effect of changing depth of second trench, D2, on electrical field distribution while keeping W and D1 constant, D1=1 μm, W=50 μm, (a) D2=3.5 μm (b) D2=1.35 μm                                                                                                                           | 3-27 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

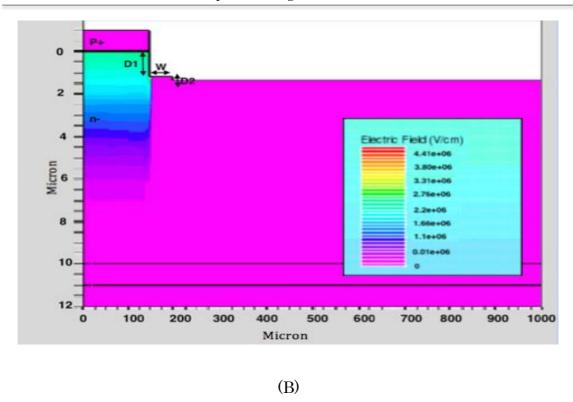

| Figure 3.16: Breakdown voltage vs. the electric field distribution depth in Y-direction using double trench junction termination.                                                                                                                                                                      | 3-29 |

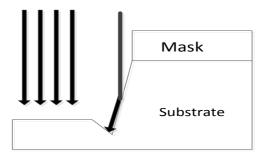

| Figure 4.1: Difference between (A) isotropic and (B) anisotropic etch                                                                                                                                                                                                                                  | 4-5  |

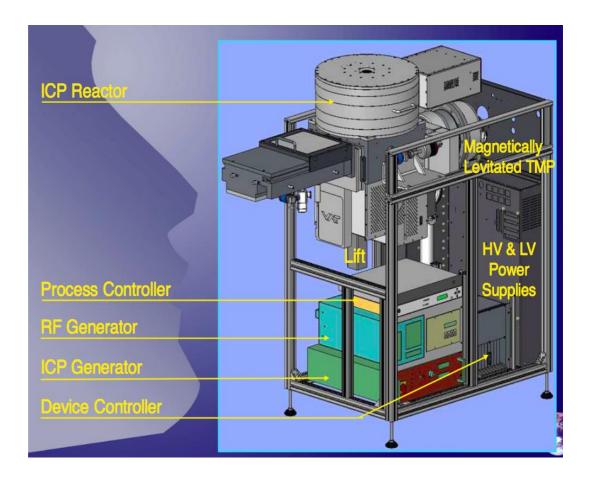

| Figure 4.2: Illustration of Corial ICP-RIE etcher instrument [1]                                                                                                                                                                                                                                       | 4-6  |

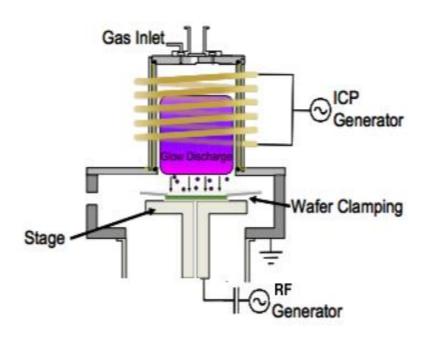

| Figure 4.3: Inside ICP reactor in ICP-RIE etcher [2]                                                                                                                                                                                                                                                   | 4-7  |

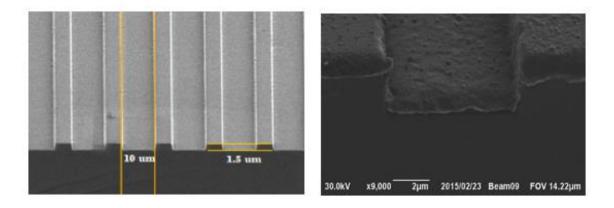

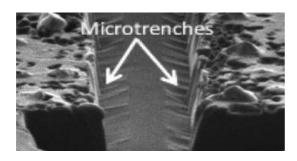

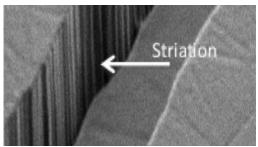

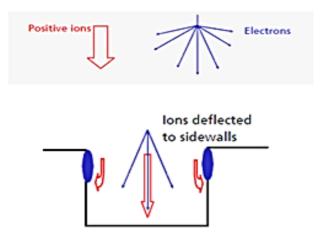

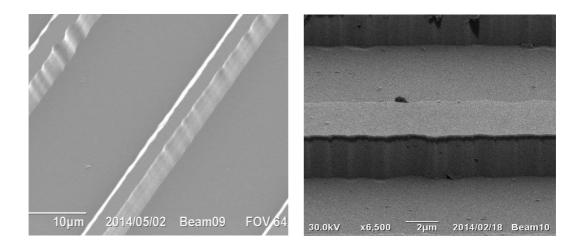

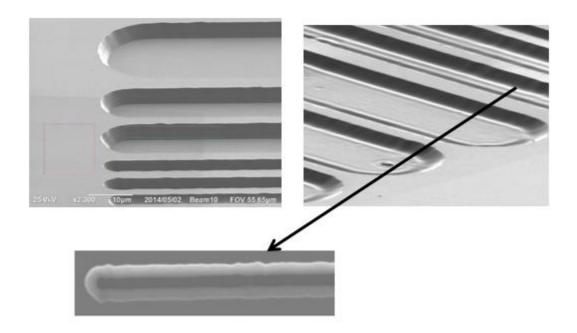

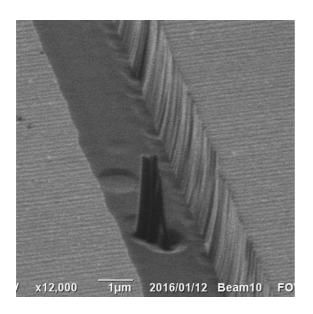

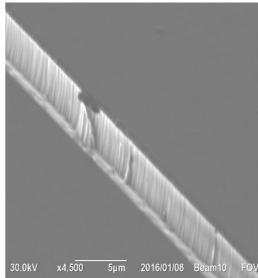

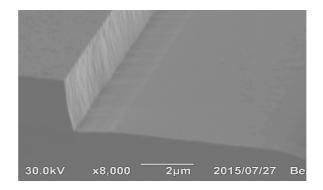

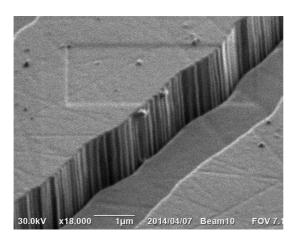

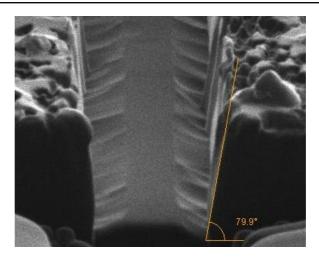

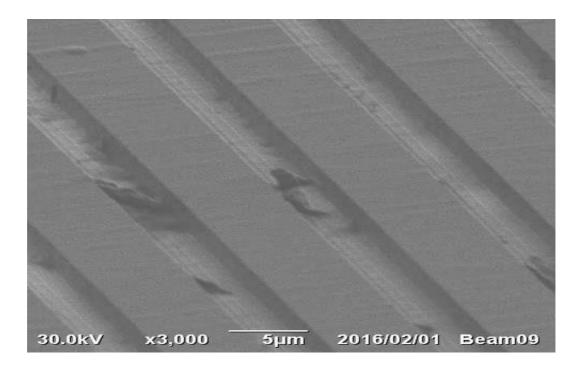

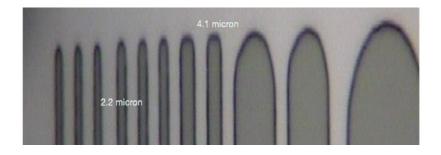

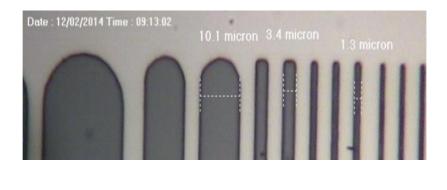

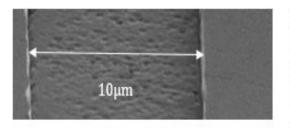

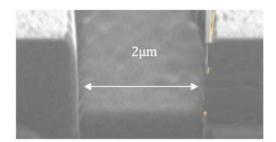

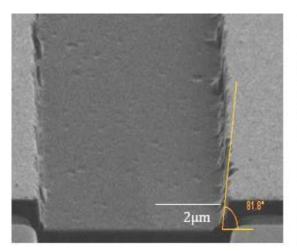

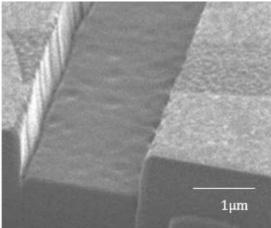

| Figure 4.4: Common challenges in fabricating trenches in SiC: SEM images of (A) microtrenches: small trenches at the corner of the main trench, this can result in crowding the electric field and hence lower breakdown (B) striation is roughness of sidewall which can increase the leakage current | 4-10 |

| Figure 4.5: Schematic of first suggested cause of microtrenches: ion deflection due to sloped sidewall                                                                                                                                                                                                 | 4-11 |

| Figure 4.6: Schematic of microtrenches formation via differential charging effect based mechanism                                                                                                                                                                                                      | 4-11 |

| Figure 4.7: SEM image of Ar ion etching of SiC. This result confirms that in the absence of electron there will be no microtrenches.                                                                                                                                                                   | 4-12 |

| Figure 4.8: The results show that microtrenches sizes are equivalent for different trench width (SEM image)                                                                                                                                                                                            | 4-13 |

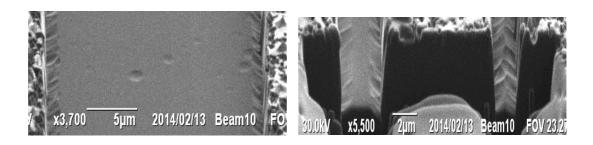

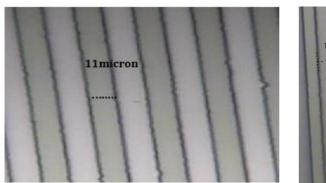

| Figure 4.9: SEM images of (A) striation in photoresist before etching metal mask and SiC (B) after etching SiC, before removing metal mask (photoresist mask is removed)                                                                                                                               | 4-14 |

| Figure 4.10: Effect of photoresist thickness and sensitivity on LER. Photoresist B is 2.5 times more sensitive [10]                                                                                                                                                                                    | 4-15 |

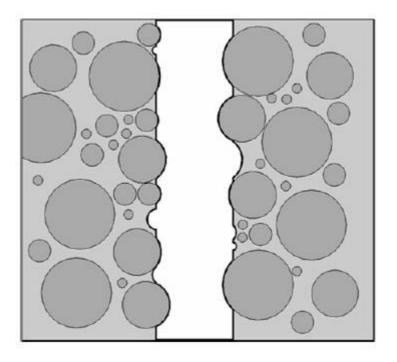

| Figure 4.11: Intrinsic non-uniformities in photoresist can cause striation along the edge                                                                                                                                                                                                              | 4-16 |

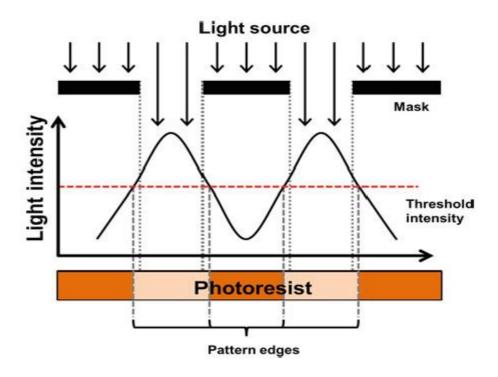

| Figure 4.12: The light intensity that reaches the unprotected photoresist is not step shaped                                                                                                                                                                                                           | 4-17 |

| Figure 4.13: SEM images of photoresist after (A) post bake only (B) with TEOS as non-reflective surface and post-bake. None of these methods helps to improve the vertical striation.                                                                                                                  | 4-18 |

| Figure 4.14: Photolithography process                                                                                                                                                                                                                                                                  | 4-20 |

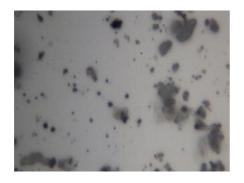

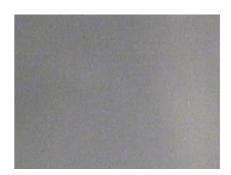

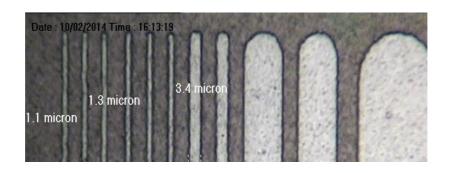

| Figure 4.15: Sample default on the surface of test grade material: This can prevent through contact with mask (miscroscopic image)                                                                                                                                                                     | 4-22 |

| Figure 4.16: Microscopic images of SiC wafer (A) before (B) after cleaning                                                                                                                                                                                                                             | 4-23 |

| Figure 4.17: Microscopic image of effect of laser cutting on the edge of sample                                                                                                                                                                                                                        | 4-23 |

| Figure 4.18: SEM images of (A) grass effect (B) striation caused by photoresist left on the photolithography mask                                                                                                                                                                                      | 4-25 |

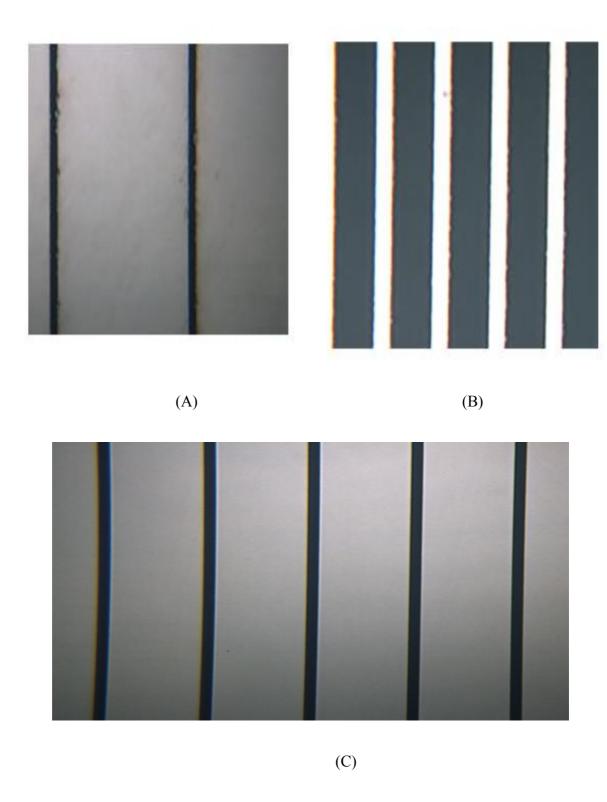

| Figure 4.19: Microscopic images of photolithography chrome mask (A) before Cleaning Mask, (B) after 2 min Piranha cleaning(C) after 6 min Piranha clean                                                                                                                                                         | 4-26         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 4.20: Microscopic images of pattern on photoresist (A) without edge bead removal (B) with edge bead removal                                                                                                                                                                                              | 4-29         |

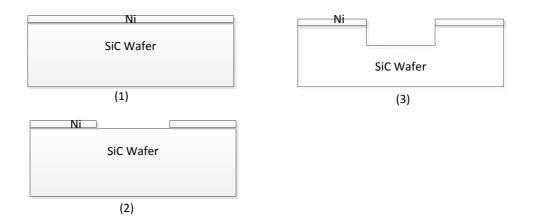

| Figure 4.21: Etching SiC procedure using metal mask:1) deposit a 0.15 um thick layer of Ni, 2) pattern the photoresist on top on of the Ni mask layer and then etch Ni layer, etch Ni 3) etch SiC                                                                                                               | 4-30         |

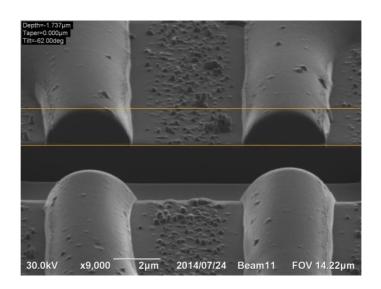

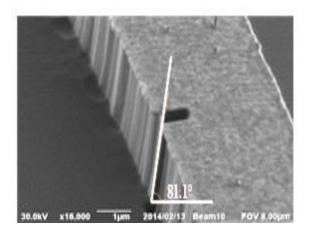

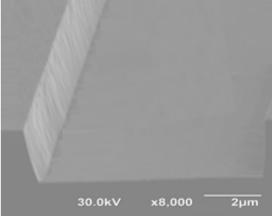

| Figure 4.22: SEM images of overshadow protection of sidewall created when using Ni mask. This size of this overshadow protection is bigger in higher ICP powers.                                                                                                                                                | 4-32         |

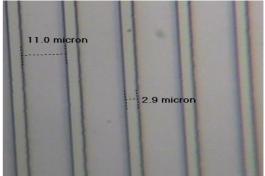

| Figure 4.23: SEM picture illustrate the peak to peak measurement of striation for Ni mask                                                                                                                                                                                                                       | 4-32         |

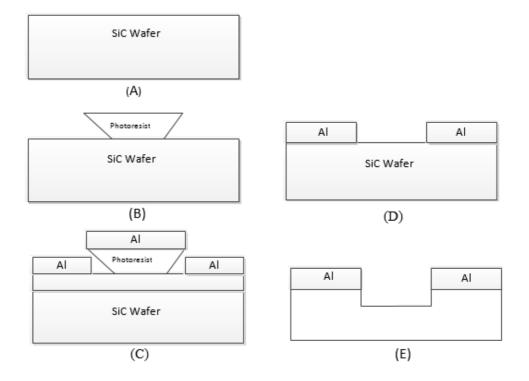

| Figure 4.24: Lift off process using Al (A) clean SiC sample surface (B) pattern the photoresist on the SiC wafer (C) deposit Al on top of the photoresist (D) put the sample in ultrasonic acetone bath, this will remove the photoresist and the Al on top of it (E) the unprotected SiC parts will be etched. | 4-33         |

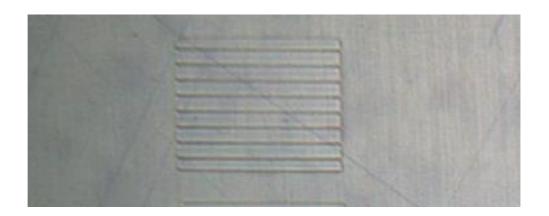

| Figure 4.25: Microscopic pictures of trench pattern (1) after photolithography, (2) after etching of Ti mask, (3) after etching SiC                                                                                                                                                                             | <b>4-</b> 36 |

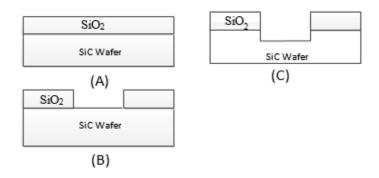

| Figure 4.26: Etching SiC procedure using SiO2 mask (A) deposit SiO2 layer on SiC (B) pattern SiO2 using dry RIE etch and S1818 photoresist and the mask layer (C) etch SiC using ICP-RIE etcher                                                                                                                 | 4-37         |

| Figure 4.27: SEM image of micro-etch problem due to low densification of SiO2 mask layer.                                                                                                                                                                                                                       | 4-38         |

| Figure 4.28: SEM image of microtrench effect in SiC using SiO2 mask 38                                                                                                                                                                                                                                          |              |

| Figure 4.29: Soft bake of a S1818 photoresist at (A) 100°C and (B) 125°C.                                                                                                                                                                                                                                       | 4-41         |

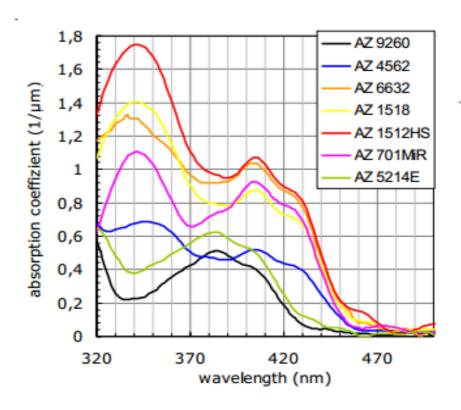

| Figure 4.30: Absorption coefficient vs. wavelength for AZ series photoresist                                                                                                                                                                                                                                    | 4-42         |

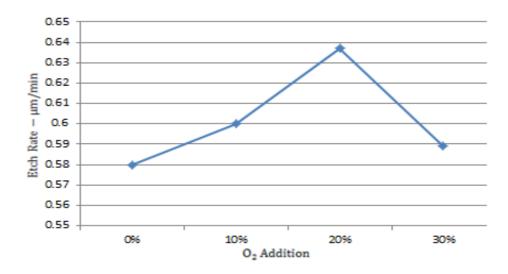

| Figure 4.31: SEM images of striation in SiC trench using (A) Ni mask (B) SiO2 mask                                                                                                                                                                                                                              | 4-45         |

| Figure 4.32: SEM image of various masks using equivalent etching recipe (A) SiO2 (B) Ni and (C) Al.                                                                                                                                                                                                             | 4-48         |

| Figure 4.33: SEM image illustrating the presence of carbonated photoresist remaining in SiC trenches                                                                                                                                                                                                            | 4-49         |

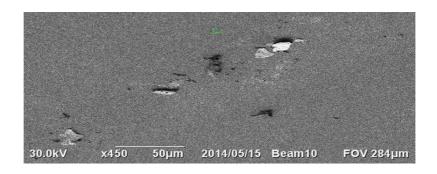

| Figure 4.34: SEM images of remainder of micro metals after Ni removal                                                                                                                                                                                                                                           | 4-50         |

| Figure 4.35: After etching the same pattern on SiC using (A) Ti mask (B) Lift off using Al (C) Ni mask. The results show that bigger pattern are achieved when using lift off technique (microscopic images)                                                                                                    | 4-51         |

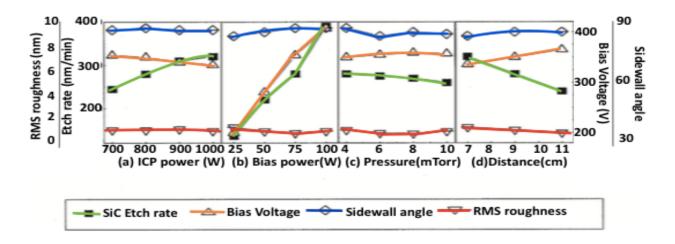

| Figure 4.36: Effect of ICP power on etch rate and roughness (RMS)                                                                                                                                                                                                                                               | 4-54         |

| Figure 4.37: Effect of ICP-RIE etch parameters etch results using NF3 gas                                                                                                                                                                                                                                       | 4-55         |

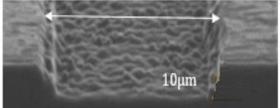

| Figure 4.38: SEM images of (A) roughness increase due to addition of O2 to SF6 at ICP power of 200 W (B) striation becomes severe due to the addition of O2 at an ICP power of 1000 W.                                                                               | 4-57         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 4.39: Effect of O2 on the etch rate (ICP power = 500 W, RF power = 60 W, pressures = 10 mTorr)                                                                                                                                                                | 4-58         |

| Figure 4.40: SEM images of etch results using (A) Ar/SF6/ O2 (1/4/1) (B) Ar/SF6 (1/4)                                                                                                                                                                                | 4-58         |

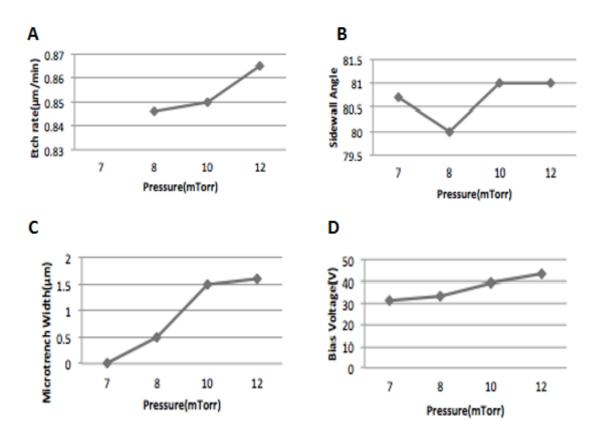

| Figure 4.41: SEM images illustrating increase in microtrenches by increasing the ICP power, (a) 200 W and (b) 500 W both at constant working pressure of 10 mTorr and RF power of 60 W                                                                               | 4-60         |

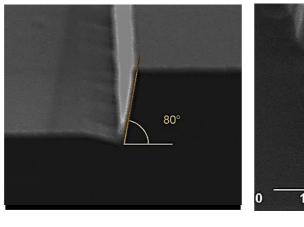

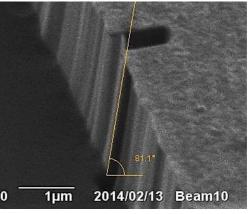

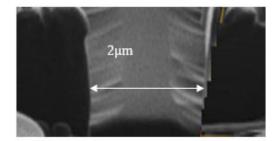

| Figure 4.42: Effect of ICP power on (A) etch rate (B) sidewall angles (C) microtrenches width and (D) bias voltage (constant working pressure of 10 mTorr and RF power of 60 W)                                                                                      | 4-61         |

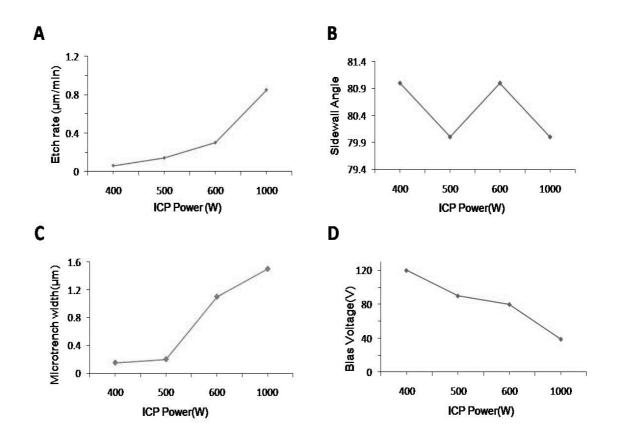

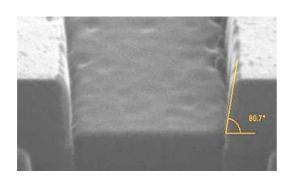

| Figure 4.43: Effect of different etch RF power on (A) etch rate (B) sidewall angles (C) microtrenches width and (D) bias voltage (at constant working pressure of 10 mTorr and ICP power of 900 W)                                                                   | 4-62         |

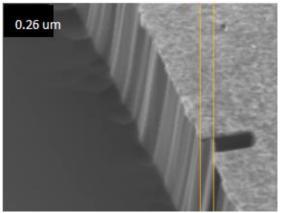

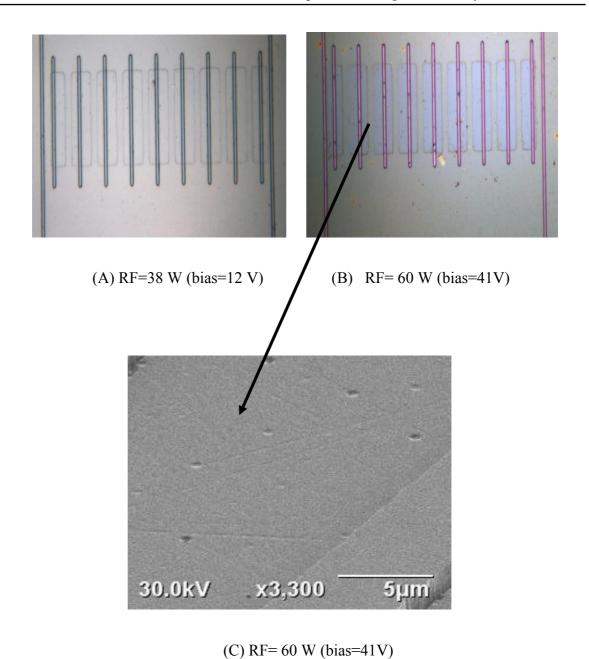

| Figure 4.44: SEM images illustrating the effect of RF power on sidewall angles (1) RF=38 W (bias=12 V), (2) RF= 50 W (bias=25V), (3) RF= 60 W (bias=41V) at constant working pressure of 10 mTorr and ICP power of 900 W                                             | <b>4-6</b> 3 |

| Figure 4.45: Microscopic images illustrating obvious milling effect at higher RF power (B and C) while microtrenches were unaffected. This suggest that microtrenches are not caused by physical etch (milling).                                                     | 4-64         |

| Figure 4.46: SEM images illustrating elimination of microtrenches by decreasing pressure. Sidewall striation is degraded severely. ICP power, RF power are 200W, 60W respectively, with a SF6/Ar gas combination.  Working pressure is (A) 7 mTorr and (B) 10 mTorr. | 4-65         |

| Figure 4.47: Effect of different etch pressure on (A) etch rate (B) sidewall angles (C) microtrenches width and (D) bias voltage                                                                                                                                     | <b>4-</b> 66 |

| Figure 4.48: SEM images illustrating that sidewall angles are unaffected by the pressure. ICP Power is 200 W, with a SF6/Ar gas combination. Working pressure is (A) 10 mTorr and (B) 7 mTorr                                                                        | 4-67         |

| Figure 4.49: SEM images illustrating microtrench effect in SiC using SiO2 mask (B) after optimising etch recipie to achive bigger overshadow and hence minimise microtrench effect                                                                                   | 4-68         |

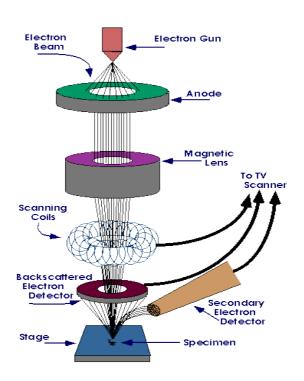

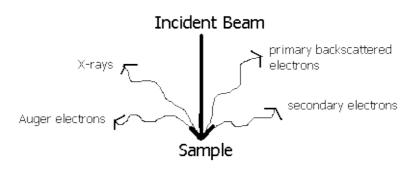

| Figure 5.1: Components of an SEM (Courtesy of Iowa State University)                                                                                                                                                                                                 | 5-11         |

| Figure 5.2: Ejected electrons X-rays from the samples after beam incident [1]                                                                                                                                                                                        | 5-12         |

| Figure 5.3: Typical I-V characteristics of MOSFET                                                                                                                                                                                                                    | 5-14         |

| Figure 5.4: Threshold voltage measurement using ID-VGS graph                                                                                                                                                                                                         | 5-16         |

| Figure 5.5: Drain source on resistance components on a trench MOSFET [3]                                                                                                                                                                                             | 5-19         |

| _                             | rench MOSFET specific on-resistance vs. breakdown voltage for<br>nel mobility[4]                                                                                                     | 5-21         |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 5.7: B                 | reakdown characteristic of a MOSFET                                                                                                                                                  | 5-22         |

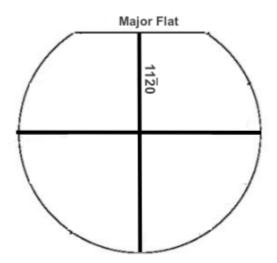

| Figure 5.8: T                 | he major flat is used to identify the 1120 plane on the wafer                                                                                                                        | 5-23         |

| 5.9(I): Al Gat                | e metal is deposited on the gate oxide                                                                                                                                               | 5-28         |

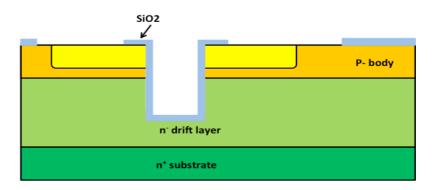

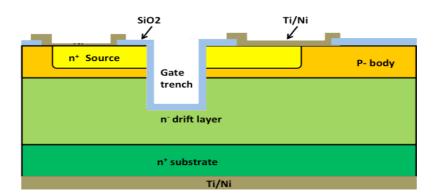

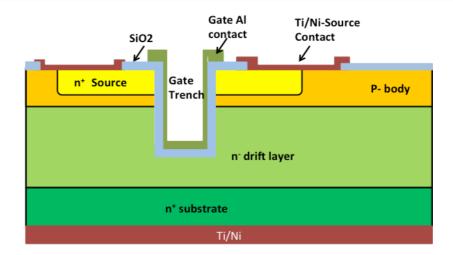

| Figure 5.9: St<br>MOSFET      | tep by step overview of fabrication process of 4H-SiC trench                                                                                                                         | 5-28         |

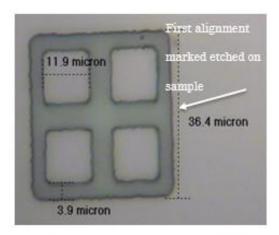

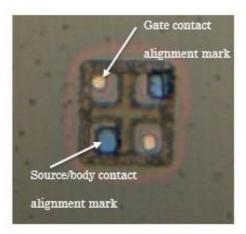

| _                             | Microscopic image of (A) First alignment mark (B) alignment at the end of the process                                                                                                | 5-29         |

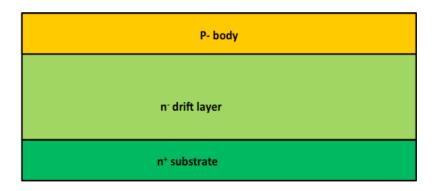

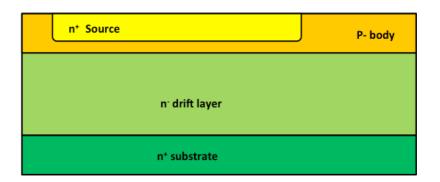

| Figure 5.11:                  | Structure of 1.2Kv trench MOSFET fabricated in this work                                                                                                                             | 5-30         |

|                               | Comparison of two different sizes of alignment marks, the inner both (A) and (B) is misaligned toward the left and the bottom by cance, but misalignment is more obvious in case (B) |              |

| Figure 5.13:                  | Simulation of Nitrogen ion implant range in SiC                                                                                                                                      | <b>5-</b> 33 |

| Figure 5.14:                  | Simulation of Nitrogen ion implant range in SiO2                                                                                                                                     | 5-33         |

| Figure 5.15:<br>removing the  | Microscopic image of SiC surface after source implantation and oxide mask                                                                                                            | d<br>5-34    |

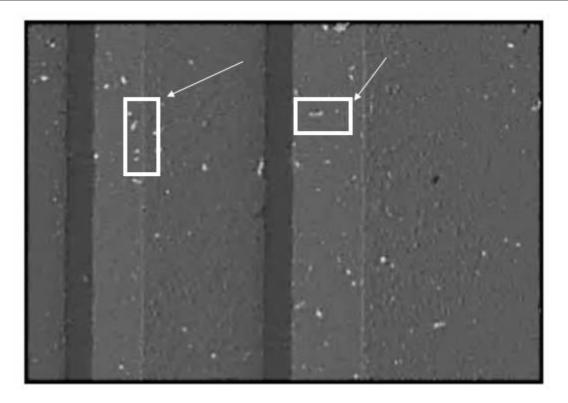

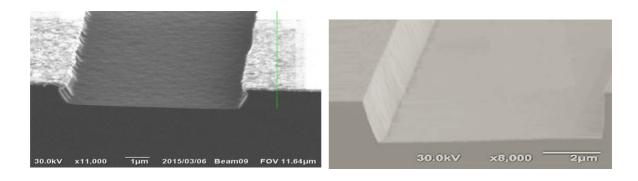

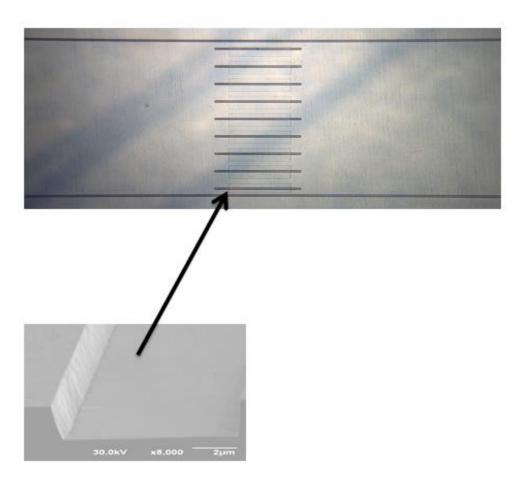

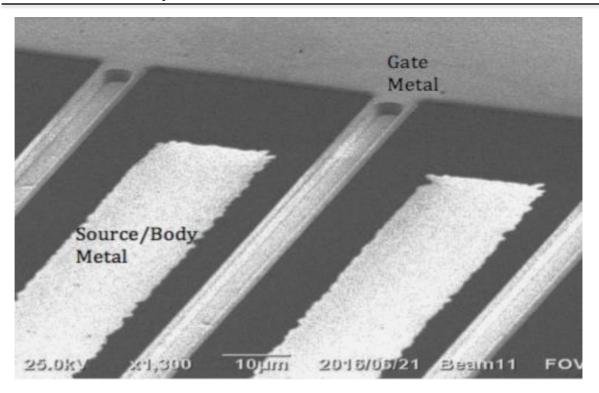

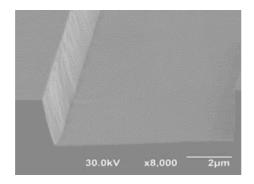

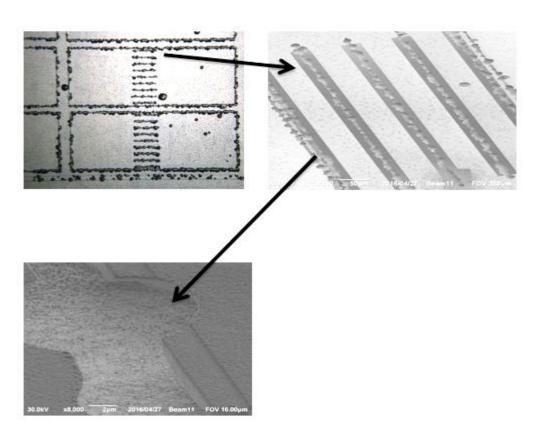

| Figure 5.16:<br>the mask      | SEM images of the samples after etching trenches and removing                                                                                                                        | ng<br>5-35   |

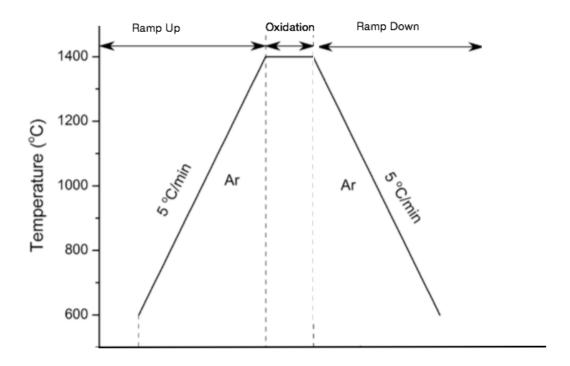

| Figure 5.17:                  | Thermal oxidation process of gate oxide                                                                                                                                              | 5-38         |

| Figure 5.18:                  | Samples surface after removing oxide from source/body contact                                                                                                                        | ts<br>5-39   |

| Figure 5.19: annealing        | After depositing source/body contacts (silver colour) before RTA                                                                                                                     | A<br>5-39    |

| Figure 5.20:<br>University    | Electron beam evaporator deposition system in Warwick                                                                                                                                | 5-40         |

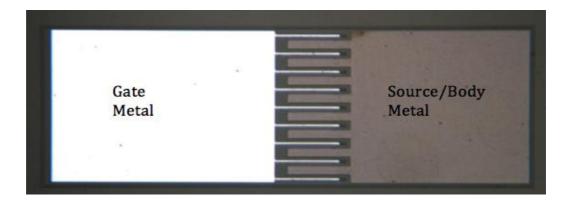

| Figure 5.21:                  | Trench MOSFET after depositing gate metal                                                                                                                                            | 5-41         |

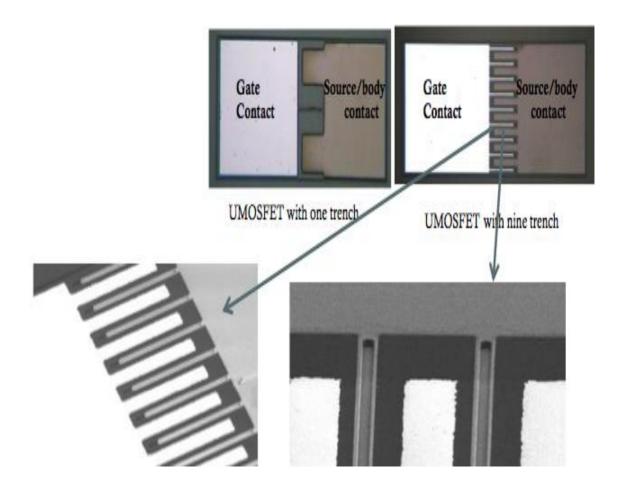

| Figure 5.22:                  | Trench MOSFET gate metal                                                                                                                                                             | 5-42         |

| Figure 5.23:                  | Trench MOSFET Structure                                                                                                                                                              | 5-43         |

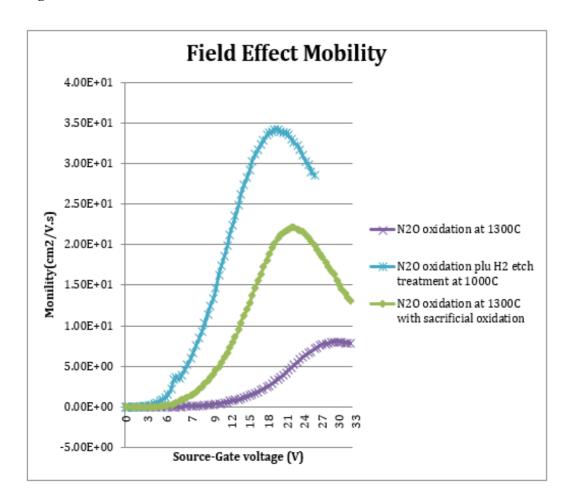

| Figure 5.24:                  | Comparison of field effect motilities                                                                                                                                                | 5-47         |

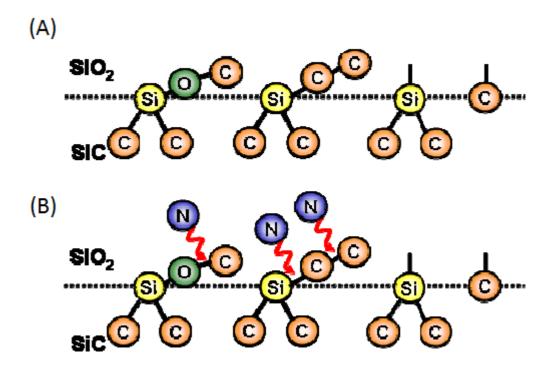

| (B) Br                        | Illustration of SiC/SiO2 interface: (A) intrinsic defects eaking Si-C bond by Nitrogen annealing (C) termination of d by Hydrogen                                                    | 5-49         |

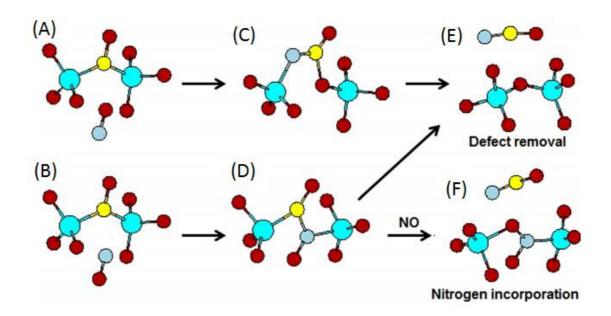

| Figure 5.26:<br>B-D-E will ta | Effect of NO passivation on Si-C-Si defect. Either A-C-E or ke place.                                                                                                                | 5-50         |

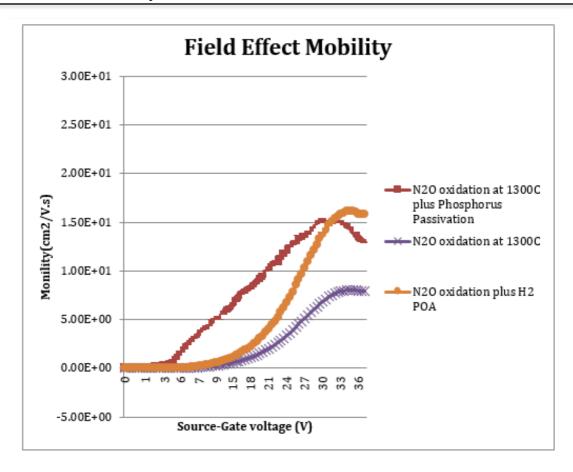

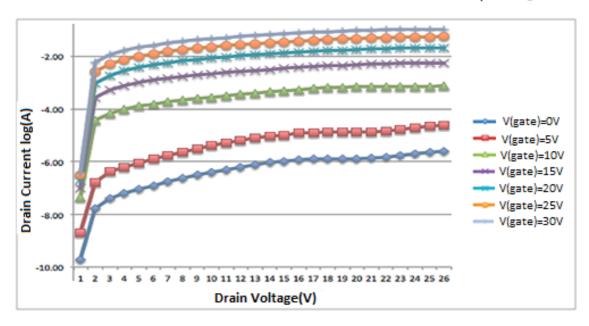

| -                             | Comparison of motilities for trench MOSFETs with different post oxidation treatments                                                                                                 | 5-54         |

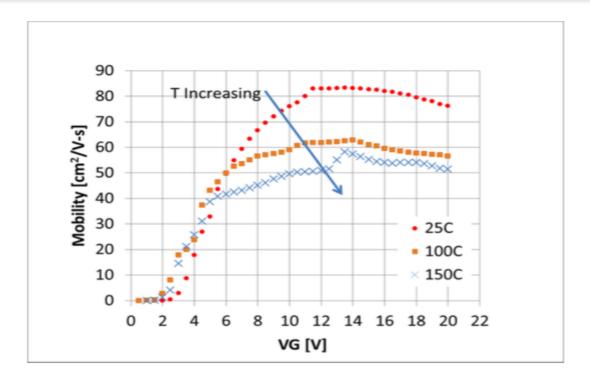

| Figure 5.28:<br>SiC         | Negative temperature dependencies of mobility on the a-face                                                                                                         | 5-56 |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

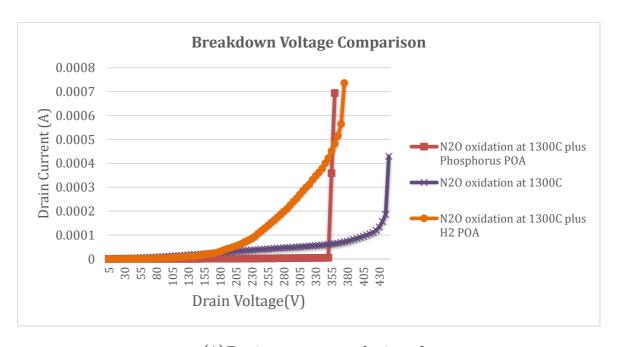

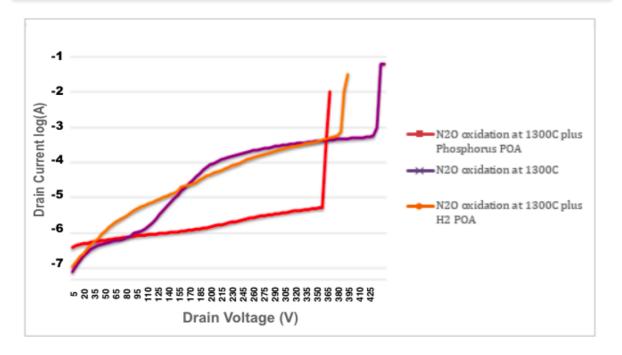

|                             | Comparison of breakdown voltages of trench MOSFETs with etch and post oxidation treatments                                                                          | 5-61 |

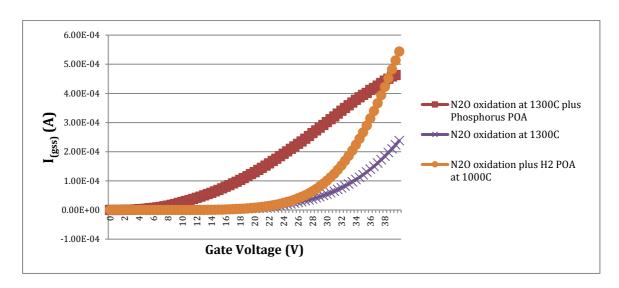

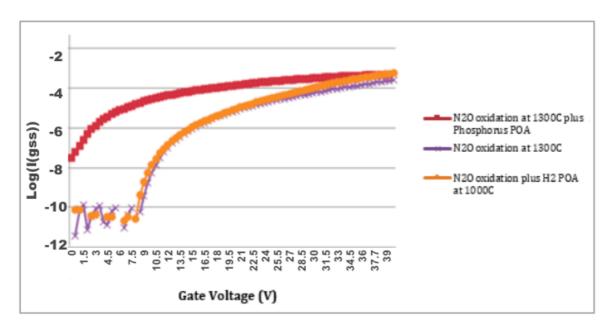

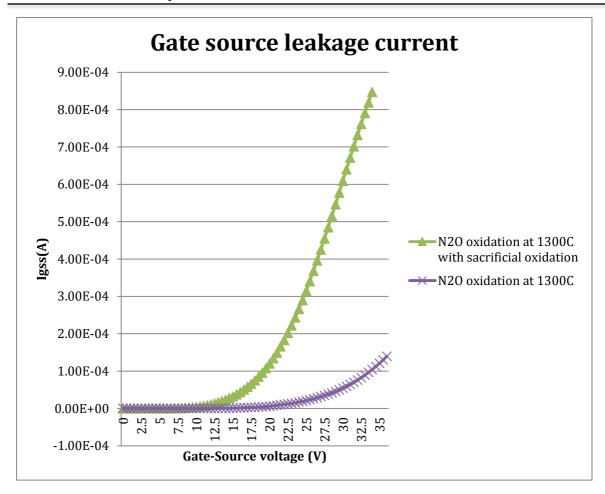

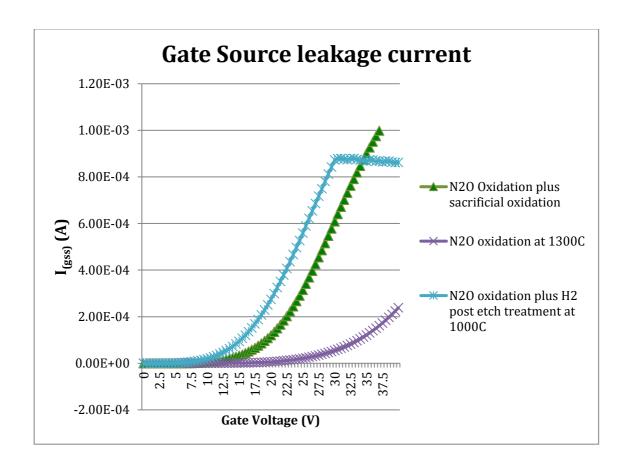

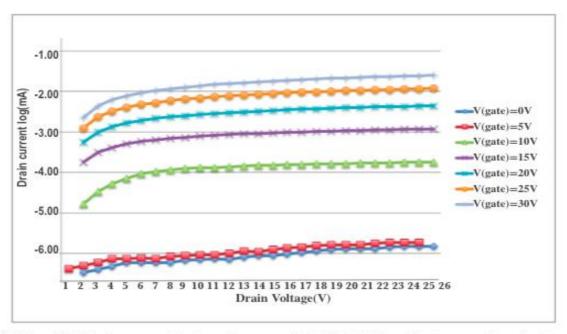

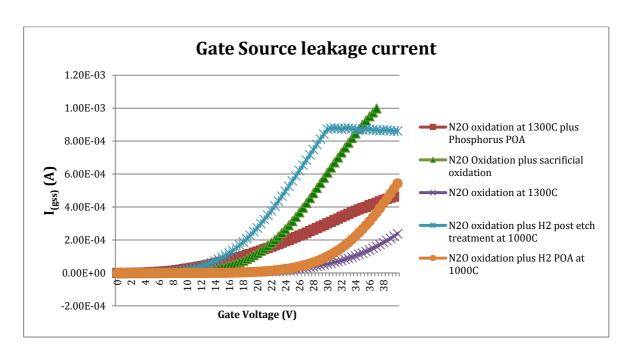

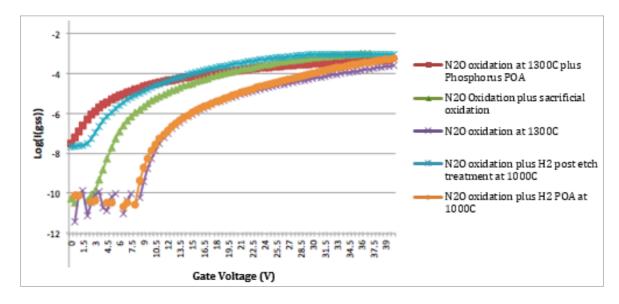

| U                           | Gate source leakage current (Igss) of trench MOSFETs with oxidation treatments                                                                                      | 5-62 |

| _                           | Areas of measurement using different leakage tests in a trench hout gate shield                                                                                     | 5-64 |

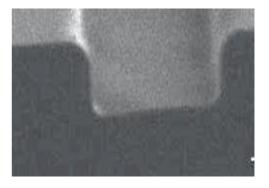

|                             | SEM images of (A)trenches before sacrificial oxidation, fter sacrificial oxidation: the corners are rounded                                                         | 5-67 |

| Figure 5.33: oxidation      | Comparison of motilities with and without gate sacrificial                                                                                                          | 5-68 |

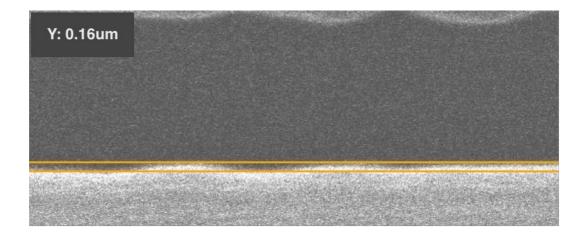

| the gate oxide              | Topography images from AFM: SiC surface after removing grown in (A) direct O2 + NO annealing (B) direct NO growth. In square roughness is (A)0.193 and (B) 0.132 nm | 5-69 |

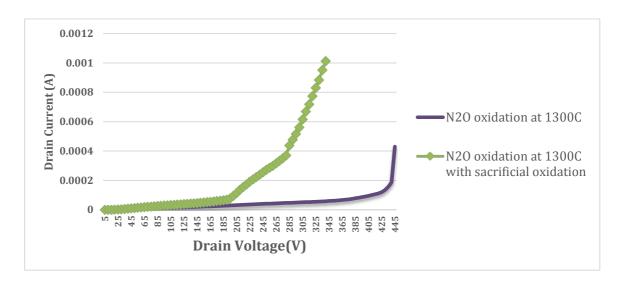

| -                           | Comparison of leakage current with and without gate cial oxidation                                                                                                  | 5-70 |

| _                           | Comparison of breakdown voltages with and without cial oxidation                                                                                                    | 5-71 |

| -                           | SEM pictures of the results of post trench etch annealing at for 15 min 2it/min                                                                                     | 5-73 |

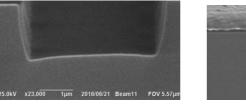

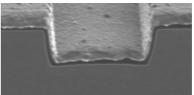

| (B)after H2 po              | SEM images of trench structures (A)without annealing, ost etch treatment at 1000°C for 30 min (Picture is taken after a and gate metal deposition)                  | 5-74 |

| Figure 5.39:                | Comparison of motilities using post etch treatments                                                                                                                 | 5-75 |

| Figure 5.40:                | Comparison of gate source leakage current using post etch                                                                                                           | 5-76 |

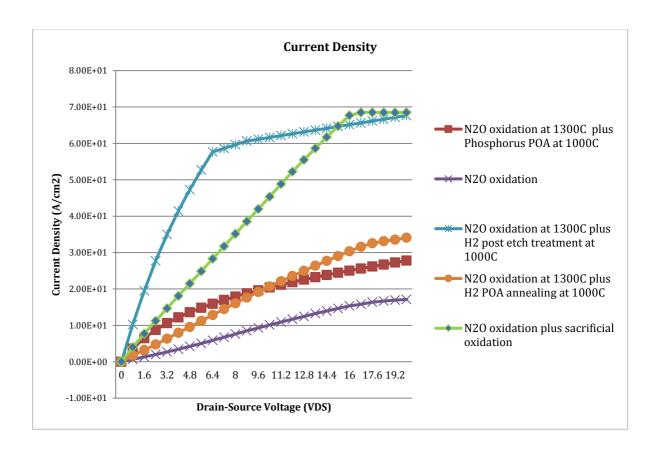

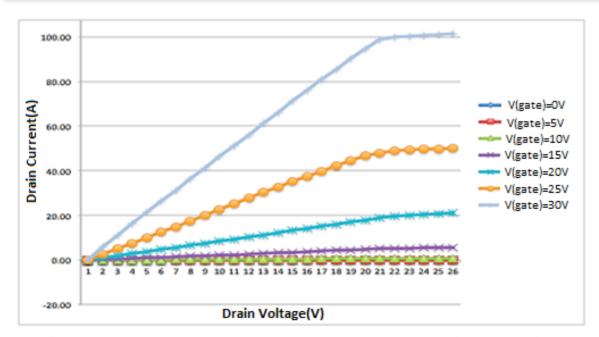

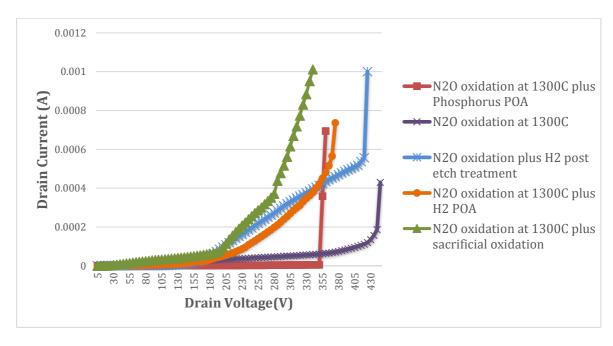

| Figure 5.41: different post | Comparison of current densities for trench MOSFETs with etch and post oxidation treatments (Vg=20 for all the cases)                                                | 5-77 |

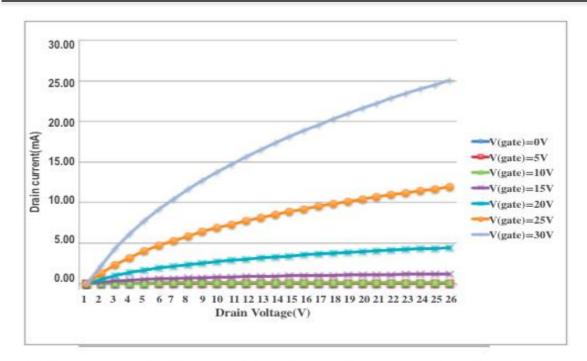

| of trenches an              | I-V characteristics of trench MOSFETs with different number ad different trench length. The current is proportional to the rench length                             | 5-79 |

| _                           | Gate source leakage current (Igss) of trench MOSFETs with etch and post oxidation treatments                                                                        | 5-81 |

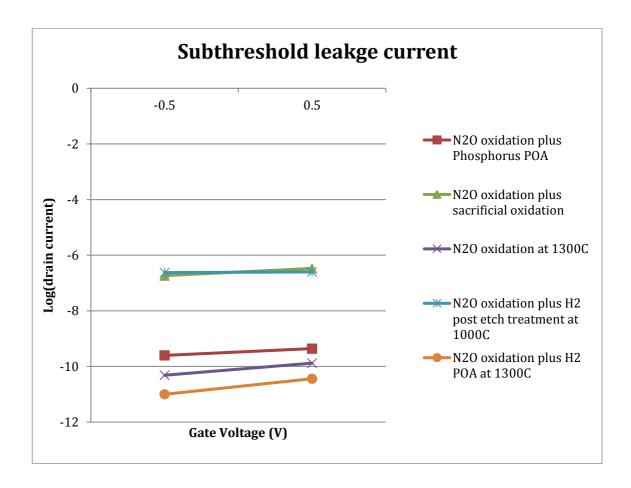

| 0                           | Subthreshold leakage of trench MOSFETs with different post oxidation treatments                                                                                     | 5-82 |

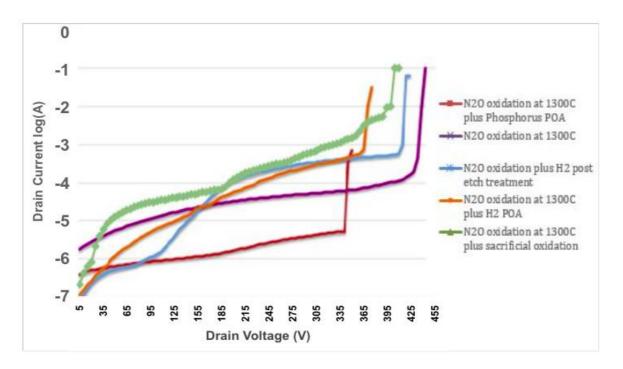

| Figure 5.45: differe        | Comparison of breakdown voltages of trench MOSFETs with nt post etch and post oxidation treatments                                                                  | 5-86 |

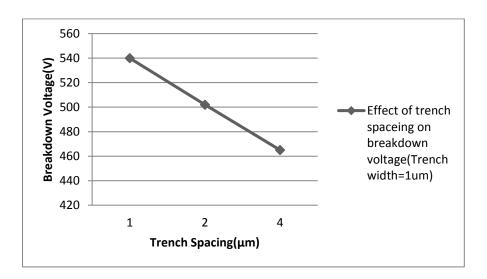

| Figure 6.1: Ef              | fect of space between trenches on breakdown voltage                                                                                                                 | 6-5  |

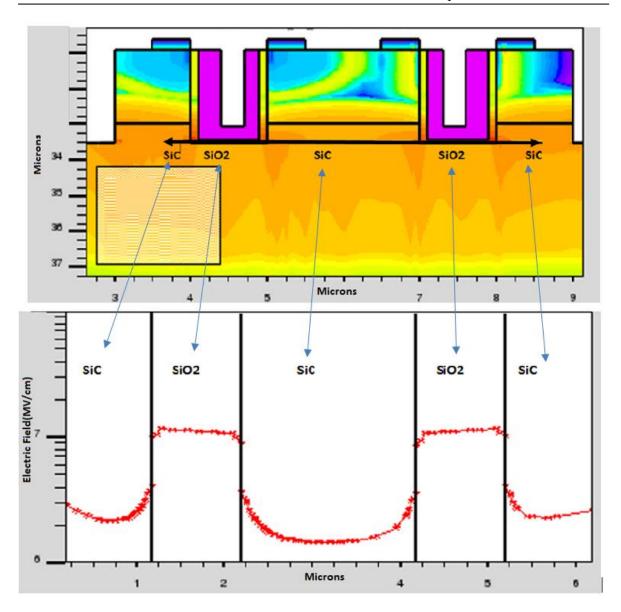

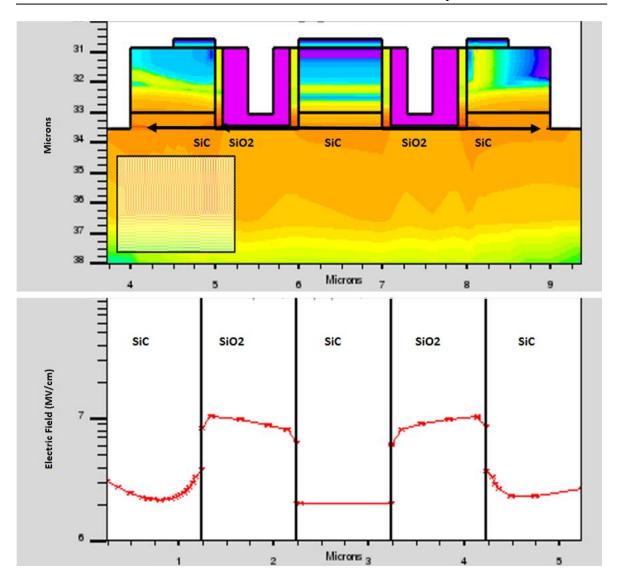

| -                           | fect of trench spacing on the electric field in a Trench MOSFET th spacing=2μm (B) trench spacing=1μm. It can be seen that                                          |      |

|         | when trenches are closer, the electric field in the oxide layer at the                                                                                                                            |      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|         | ·                                                                                                                                                                                                 | 6-7  |

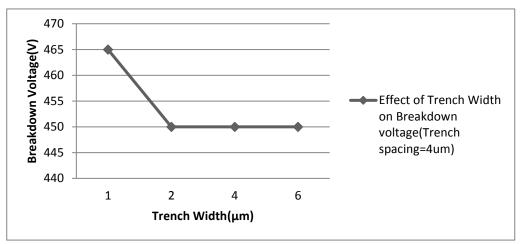

| Figure  | 6.3: Effect of trench width on breakdown voltage                                                                                                                                                  | 6-8  |

|         | 6.4: Trench MOSFET design with 1µm cell pitch, the breakdown happens in trench bottom and trench corners                                                                                          | 6-9  |

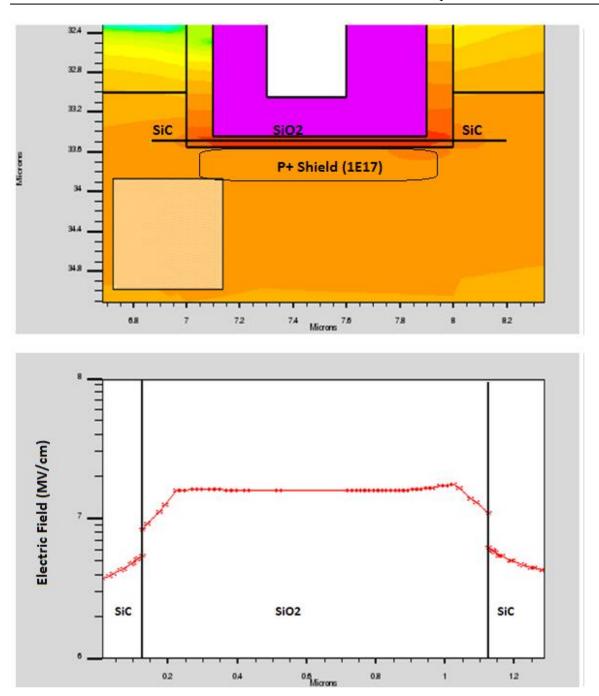

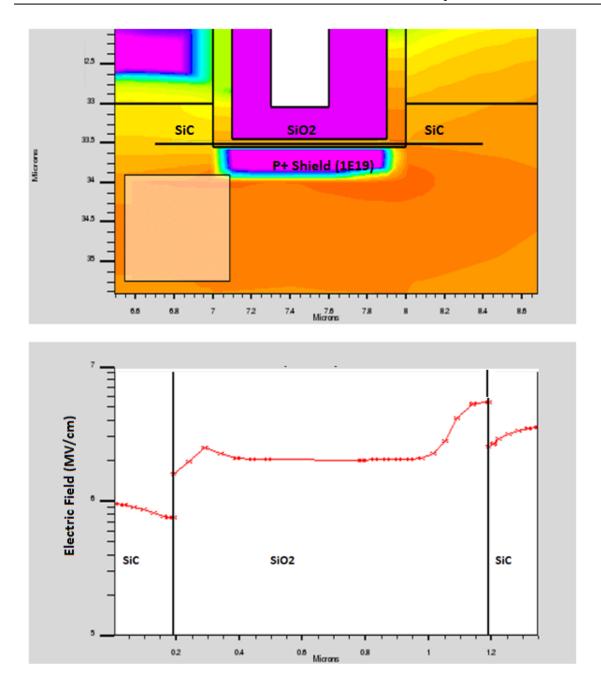

| voltage | 6.5; Effect of P+ gate shield with different doping on the breakdown e, with lower doping like case (A), the breakdown still occurs in the ayer, at voltages much closer to the breakdown voltage | 6-12 |

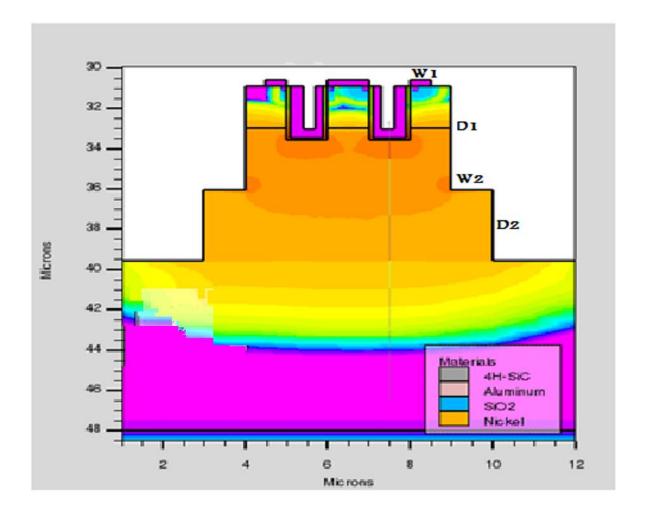

| _       | 6.6: Trench MOSFET design with P+ gate shield and double trench JTE, highest breakdown voltage of 1650V is achieved.                                                                              | 6-13 |

| _       | 6.7: Structure of trench MOSFET with sacrificial trenches in the middle of gate trenches. The breakdown voltage is 1500V.                                                                         | 6-15 |

| _       | 6.8: Electric field across trench corners and oxide layer with sacrificial trench design. The design is shown in Figure 6.7.                                                                      | 6-15 |

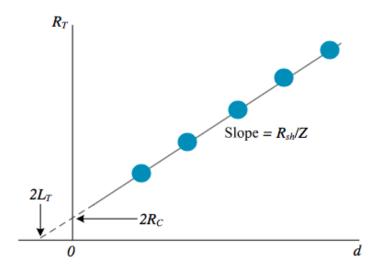

| Figure  | 6.9: TLM structure used to measure the resistance of ohmic                                                                                                                                        | 6-17 |

| Figure  | 6.10: TLM plot of the total resistance as a function of contact spacing                                                                                                                           | 6-18 |

# List of Tables

| Table 1 1: Comparison of Si with different SiC polytypes                                                                                                                                   | 1-6  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2.1: Oxide electric field taking into account the trench width and rounded corners                                                                                                   | 2-9  |

| Table 3.1: Effect of the P-doping on the threshold voltage                                                                                                                                 | 3-6  |

| Table 3.2: Regional doping concentration of ideal 10kV SiC trench<br>MOSFET                                                                                                                | 3-9  |

| Table 3.3: Effect of P-doping from simulation of 4H-SiC trench MOSFET                                                                                                                      | 3-16 |

| Table 3.4: Effect of gate dielectric thickness for P-body doping of 1×1017cm-3 achieved from simulation of 4H-SiC trench MOSFET                                                            | 3-16 |

| Table 3.5: Properties of 1.2 kV MOSFET                                                                                                                                                     | 3-17 |

| Table 3.6: Breakdown voltages achieved for different double trench junction termination on a Schottky diode with ideal breakdown voltage of 1.2 kV.                                        | 3-26 |

| Table 4.1: Lift off technique processes using AZ 5214 resist / Al mask                                                                                                                     | 4-33 |

| Table 4.2: Etch recipe for RIE etch of Ti                                                                                                                                                  | 4-34 |

| Table 4.3: Comparison of mask selectivity                                                                                                                                                  | 4-36 |

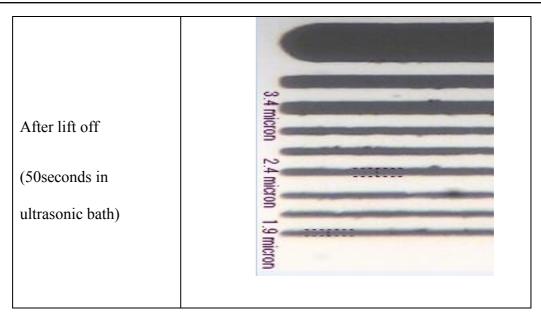

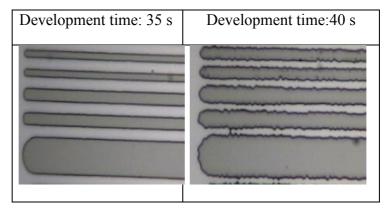

| Table 4.4: Lift off technique using AZ 5214 negative resist and Al mask: 5 more seconds of development time resulted in severe striation                                                   | 4-38 |

| Table 4.5: Development time vs. wavelength for AZ ECT 3000 resistance                                                                                                                      | 4-40 |

| Table 4.6: Effect of exposure dosage on the patterns: very high / low dosage                                                                                                               | 4-41 |

| Table 5.1: Properties of the SiC wafer                                                                                                                                                     | 5-19 |

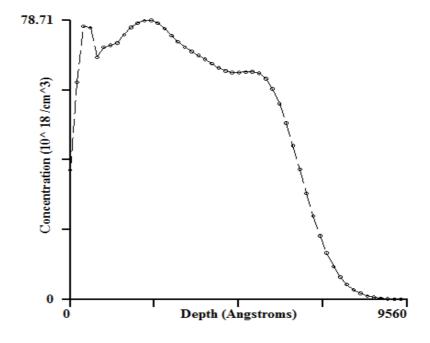

| Table 5.2: Ni implantations energy and dosage used to implant n+ source in trench MOSFETs in this work. The resulting profile in both SiC and TEOS is shown in Figure 5.12 and Figure 5.13 | 5-27 |

| Table 5.3: List of recipes used and the resulting gate oxide thickness                                                                                                                     | 5-40 |

| Table 5.4: Comparison of traps density and mobility for different gate oxidation recipes                                                                                                   | 5-43 |

| Table 5.5: Density of nitrogen and phosphorus after NO and phosphorus passivation. The oxide is removed to make this measurement                                                           | 5-52 |

| Table 5.6: Comparison of electrical parameters measured from trench MOSFETs with different post etch and post oxidation treatments                                                         | 5-54 |

| Table 5.7: Comparison of electrical parameters measured from trench MOSFETs with different post etch and post oxidation treatments                                                         | 5-78 |

| Table 6 1: Double trench junction termination parameters. The parameters corresponds to the parameters shown in Figure 6.6                                                                 | 6-14 |

| Table 6 2: Parameters used to simulation sacrificial trenches in middle   |      |

|---------------------------------------------------------------------------|------|

| of gate trenches. These parameters resulted in breakdown voltage of 1500V | 6-14 |

| Table 6 3: Comparison of sacrificial oxidation method and traps density   |      |

| for different trench plane.                                               | 6-16 |

## Declaration

This thesis is submitted to the University of Warwick in support of the application for the degree of Doctor of Philosophy. It has not been submitted in part, or in whole, for a degree or other qualification at any other University. Parts of this thesis are published by the author in peer-reviewed research papers listed. Apart from commonly understood and accepted ideas, or where reference is made to the work of others, the work described in this thesis is carried out by the author in School of Engineering of the University of Warwick.

Zohreh Mohammadi

2013-2018

To Mum, Dad, Zahra and Hamid

## Acknowledgement

This work was not possible without the support of everyone around me.

Thank you Professor Phil Mawby for your support from the very first day and for believing in me and investing in me. I appreciate everything I have learnt from you in research and in life. I truly believe my career has changed for better because of working with you.

Dr. Mark Crouch and Corinne Maltby: this work was not possible without your continuous support in the cleanroom. Thank you and I always remember the experience of working with you as some of my best working days.

Dr. Alatise, Dr. Jennings, Dr. Gammon, thanks for teaching me and spending the time to transfer your skills to me and answering my questions in different time during this work.

My colleagues Dr. Fisher, (soon to be)Dr. Bonyadi, Dr. Rong, Dr. Fan, (soon to be) Dr. Dai: Thanks for sharing your research results. This work was the continuous of your work and I cannot wait to see your success and work with you again. Thanks for the great 3 years in the office as well.

My friend, Jenny: Thanks for not giving up on me when I was very lost in the middle of writing this thesis and all your inputs and feedbacks.

My family, Mum, Dad, Zahra and Hamid: you were the inspiration behind all my success. It is amazing that we eventually get to celebrate all our graduations in the same year.

## **Publications List**

- Mohammadi, Z., Shah, V., Jennings, M., Fisher, C. and Mawby, P. (2015).

Elimination of Microtrenching in Trenches in 4H-Silicon Carbide Using Shadow Masking. Materials Science Forum, 821-823, pp.533-536.

- T. X. Dai, Z. Mohammadi, S. A.O. Russell, C. A. Fisher, M. R. Jennings, P. A. Mawby, "4H-SiC Trench Structure Fabrication with Al<sub>2</sub>O<sub>3</sub> Etching Mask", Materials Science Forum, Vol. 897, pp. 371-374, 2017

- Rong, H., Z. Mohammadi, Sharma, Y., Li, F., Jennings, M. and Mawby, P. (2014).

4H-SiC Diode Avalanche Breakdown Voltage Estimation by Simulation and Junction Termination Extension Analysis. *Materials Science Forum*, 778-780, pp.824-827.

#### Abstract

For solid-state power devices, there exists need for a material with a higher band gap which will result in a higher critical electric field, improved power efficiency and thermal performance. This has resulted in the use of Silicon Carbide (SiC) as a serious alternative to Silicon for power devices. SiC trench MOSFETs have attracted major attention in recent years because of 1) lower on resistance by eliminating the JFET effect which exists in lateral MOSFETs, 2) higher channel density which lowers the threshold voltage and 3) reduction of the required surface area because of the vertical channel. These advantages allow faster switching speeds and the potential for a higher density of devices leading to more compact modules.

This work was focused on fabrication of the first generation of 4H-SiC trench MOSFETs in Warwick University. Two main goals were achieved in this work: a comprehensive understanding of fabrication of trenches in 4H-SiC and fabrication of first generation of 4H-SiC trench MOSFET with mobility as high as  $35 \, cm^2/V.s.$

A detailed study of fabrication of trenches in 4H-SiC showed that both masking method and the etching recipe affect the smoothness, the shape and the angle of the sidewalls. The biggest challenges in etching trenches in SiC were found to be roughness of sidewalls and microtrenches. Microtrenches are small trenches in the corner of the sidewall that results in lower breakdown voltages. The results showed that while Nickel (Ni) is the best mask to eliminate microtrenches, Silicone dioxide (SiO<sub>2</sub>) results in the smoothest and cleanest sidewall hence lowest leakage current. SiO<sub>2</sub> was used as the etching mask and a sidewall shadow was created by optimizing the etching RF power that helped to protect the trench sidewall and hence successfully eliminate microtrenches.

The trench MOSFET fabrication results showed that without any post etch or oxidation treatments the mobility can be as low as  $5cm^2/V$ . s. Post etch treatment using hydrogen  $(H_2)$  annealing resulted in the highest mobility as high as  $35 cm^2/V$ . s while post oxidation  $H_2$  annealing or phosphorus activation resulted in higher mobility close to  $15 cm^2/V$ . s. The downside of post etch treatments is slightly higher leakage current than the post oxidation treatment.

## List of Abbreviations

SiC Silicon Carbide

MOSFET Metal Oxide Semiconductor Field Effect Transistors

MOS Metal Oxide Semiconductor

IGBT Insulated Gate Bipolar Transistor

SEM scanning electron microscope

AFM atomic force microscopy

ICP-RIE Inductively coupled plasma- Reactive Ion Etcher

HF Hydrogen fluoride

N<sub>2</sub> Nitrogen

N Nitrogen atom

H<sub>2</sub> Hydrogen

POB post exposure bake

Al Aluminium

Ti Titanium

Ni Nickel

SiO<sub>2</sub> Silicon dioxide

Ar Argon

O<sub>2</sub> Oxygen

Cl<sub>2</sub> Chlorine

RTA Rapid Thermal Annealing

N<sub>2</sub>O Nitrous oxide

N<sub>2</sub> Nitrogen

NO Nitric oxide

POA Post Oxidation Annealing

P Phosphorus

NF<sub>3</sub> Nitrogen trifluoride

SF<sub>6</sub> Sulfur hexafluoride

# List of Symbols

| A                | Active die area (cm²)                   |

|------------------|-----------------------------------------|

| E                | Electric field (Vcm <sup>-1</sup> )     |

| $V_{GS}$         | Gate source voltage (V)                 |

| $I_D$            | Drain current (A)                       |

| $V_{DS}$         | Drain source voltage (V)                |

| $V_{Th}$         | Threshold voltage (A)                   |

| $I_D$            | Drain current (A)                       |

| $u_{FE}$         | Field Effect Mobility $(cm^2/V.s)$      |

| $g_m$            | gate transconductance                   |

| $I_{D/cm^2}$     | Current Density (A/cm2)                 |

| $R_{DS(on)}$     | Drain to Source On State Resistance (Ω  |

| $R_s$            | Source resistance $(\Omega)$            |

| $R_{ch}$         | Channel resistance $(\Omega)$           |

| $R_{epi}$        | Epi layer resistance $(\Omega)$         |

| $R_{subs}$       | Substrates resistance ( $\Omega$ )      |

| $V_{\rm br}$     | Breakdown Voltage (V)                   |

| $I_{gss}$        | Gate source leakage current (A)         |

| I <sub>dss</sub> | drain-source leakage current (A)        |

| $N_D$            | Drift region doping (cm <sup>-3</sup> ) |

| $BV_{pp}$        | parallel plane breakdown voltage(V)     |

| $W_{pp}$         | parallel plane depletion width( $\mu$ ) |

|                  |                                         |

$N_A$  doping concentration of the P-body (cm<sup>-3</sup>)

$C_{ox}$  the specific capacitance of the gate oxide

$k_B$  Boltzmann's constant

T absolute temperature

$\mathcal{E}_{S}$  semiconductor dielectric constant

$n_i$  intrinsic carrier concentration

$N_c$  effective density of state of the conduction band

$N_v$  the effective density of state of the valance band

$\it E_{\it g}$  energy gap

$\mathcal{E}_{OX}$  oxide dielectric constant

$N_{\it bulk}$  bulk doping of the semiconductor

$\it m_{SC}$  the effective mass in semiconductor

h Planck's constant

$m_{\mathit{OX}}$  the effective mass in the oxide

$\Phi_B$  the barrier height of the oxide/semiconductor interface

$E_{OX}$  electric field across oxide

Chapter

1

## Introduction to 4H-SiC

## Trench MOSFETs

## 1 Introduction

During recent years, it has been widely recognized that power switching devices in Silicon (Si) are approaching their theoretical limits and there is a need for another material with higher band gap, higher critical electric field, improved power efficiency and thermal performance. Silicon Carbide (SiC)

devices have been suggested as a suitable replacement to Si because of many advantages associated with this material.

Power semiconductors such as Schottky barrier diodes, MOSFETs are the heart of the power electronics. SiC Power semiconductors offer faster switching, less power loss and can be used in higher voltage and temperature applications. These advantages make SiC devices great candidate for applications such as convertors for renewable sources, electrical cars and trains. Using SiC devices results in higher energy efficiency and can also improve the size of passive components and weight by 50% [1].

SiC devices are widely used in power convertors such as AC/DC power convertors for renewable energy sources, PFC, UPS and power convertors for industrial applications such as air-conditioning. The main advantage that makes SiC suitable for this application is the higher energy efficiency compared to the SiC devices.

The other application of SiC power devices is in electrical distribution systems. The electricity grid is moving toward distributed energy resources in the recent years by addition of many distributed and renewable resources such as combined heat and power (CHP) plants, solar and wind farms. This results in more losses in the system as energy needs to be transmitted over long distance from these distributed resources. Also these resources degrade the frequency instability of the grid because of their low inertia and also volatile energy

generation. The grid should operate at frequency of 50Hz (in the UK) to avoid any damage to the connected electrical assets. At any time the consumption and generation of electricity should be equal to keep the frequency at 50 Hz and the volatile nature of renewable resources means that control of frequency is more difficult. The other main challenge with the renewable resources is their contribution to reduction in grid inertia. This is mainly due to the fact that inverter connected solar and wind farms do not provide rotational inertia. Low inertia results in faster frequency changes in the grid [1]. Currently National Grid uses assets with response times as fast as 1 seconds to balance the frequency during the consumption/generation imbalance to restore the frequency back to 50Hz but it is predicted that there will be need for assets with sub second response time. SiC Power systems offer high speed control of supplies and motors and also enables high voltage, high frequency power conversion that is necessary to add large scale renewables to the grid. This means that using such systems not only offer higher energy efficiency but also offer high speed of control during any electricity imbalance [2].

Other applications of SiC devices include aerospace and military where there is a need for stable power devices in extreme temperature since SiC can operate at temperate as high as 250 °C.

#### 1.1 Wide Band Gap Material

4H-SiC material has a bandgap three times higher than Si (Table 1.1) which is a key benefit in term of power devices. Higher band gap results in a higher intrinsic temperature, at which the intrinsic carrier concentration becomes comparable to the doping concentration, resulting in a sudden current increase and hence failure of the device.

The intrinsic carrier concentration  $(n_i)$  of a semiconductor is given by equation 1.1, where  $N_c$  is the effective density of state of the conduction band,  $N_v$  is the effective density of state of the valance band,  $E_g$  is the band gap energy,  $k_B$  is the Boltzmann constant and T is the absolute temperature.

$$n_i = \sqrt{N_c N_v} \cdot \exp(-\frac{E_g}{2.k_B T})$$

Equation (1.1)

As can be seen, the intrinsic concentration depends on the energy band gap and the temperature. Hence due to the narrow band gap of Silicon (Si), the intrinsic carrier concentration of Si increases rapidly with the increase in the temperature and hence Si devices fail in lower temperature compared to SiC device. This high intrinsic temperature of SiC allow the device to reach temperature as high as 700°C before it fails.

#### 1.1.1 High Avalanche Breakdown Electric Field

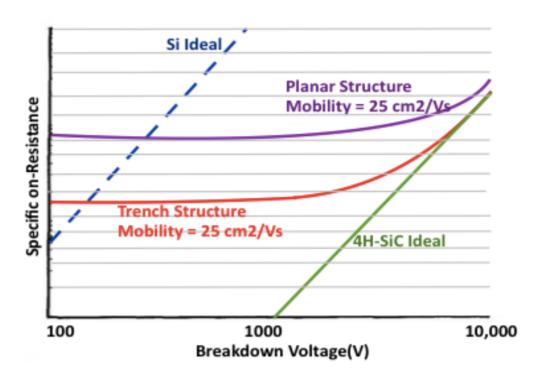

With a breakdown electric field 10 times higher than Si for the same voltage rating, 4H-SiC devices can be designed with thinner, more highly doped drift regions, which results in less specific on resistance. This leads to higher power efficiency and decreasing power loss with respect to 4H-SiC.

| Property                                      | Si                 | 3C-SiC               | 6H-SiC               | 4H-SiC             |

|-----------------------------------------------|--------------------|----------------------|----------------------|--------------------|

| Bandgap(eV)                                   | 1.12               | 2.35                 | 3.08                 | 3.28               |

| Breakdown field (MV/cm)                       | 0.3                | 1.5                  | 2.2                  | 2.3                |

| Intrinsic carrier concentration ( $cm^{-3}$ ) | 1x10 <sup>10</sup> | 1.5x10 <sup>-1</sup> | 1.6x10 <sup>-6</sup> | 5x10 <sup>-9</sup> |

| Electron mobility $(cm^2/Vs)$                 | 1350               | 900                  | 370                  | 800                |

| Hole mobility ( $cm^2/Vs$ )                   | 480                | 40                   | 80                   | 120                |

| Saturated electron velocity $(10^7 cm/s)$     | 1                  | 2                    | 2                    | 2                  |

| Thermal conductivity (W/cmK)                  | 1.5                | 4.9                  | 4.9                  | 4.9                |

| Dielectric constant                           | 11.8               | 9.6                  | 9.7                  | 9.7                |

| Electron affinity (eV)                        | 4.05               | 3.8                  | 3.3                  | 3.1                |

Table 1-1: Comparison of Si with different SiC polytypes

#### 1.1.2 High Electron Saturation Velocity

An electron saturation velocity twice that of Si, enables faster switching frequencies. A higher electron saturation velocity also results in shorter

reverse recovery time as charge stored in the depletion region can be removed faster.

Other advantages such as the thermal conductivity being three times that of Si devices results in a higher thermal stability making 4H-SiC material perfect thermal conductors with further reduction in cooling requirements. 4H-SiC is the most favorable SiC polytype due to higher carrier mobility and a higher degree of isotropy.

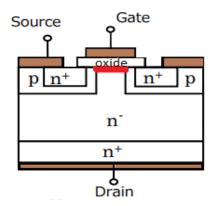

# 1.2 Metal Oxide Field Effect Transistor(MOSFET) Structures

Metal Oxide Field Effect Transistor (MOSFET) structure can be designed so that the channel region is lateral or vertical. The first SiC MOSFETs introduced were mostly based on lateral channels (Figure 1.1A). The recent attempts to block voltages higher voltages, resulted in the introduction of the double diffused MOSFET (DMOSFET), where a drift layer is included on top of the drain region to support high voltages, the channel is formed laterally when voltage is applied to the gate. As can be seen in Figure 1.1, there still exist a JFET region in this type of MOSFET like lateral MOSFETs. Also the lateral

channel imposes limitation on the cell pitch and requires a large surface area to accommodate the lateral channel.

(A): N-channel DMOSFET, the current channels (shown in red) are horizontal under the gate oxide.

(B): N-channel trench MOSFET, the current channels (show in red) are vertical on the trench sidewalls

Figure 1.1: Structure of (A) planar MOSFET (B) trench MOSFET

The attempts to reduce the specific-on resistance resulted in introducing trench MOSFETs. Trench MOSFET includes a vertical structure where the source and drain are on the opposite side of the wafer to support higher voltages. The gate is located in a trench and the channel is created on the vertical wall of the trench (Figure 1.1B). The trench is extended to the drift region and hence the parasitic JFET effect that exists in the lateral channel MOSFET is eliminated and therefore the specific on resistance is improved significantly. Since the current channels are vertical, using trench technology offers a higher channel density and helps to minimize the required surface area, since the channels exist on the side walls.

#### 1.2.1 On State

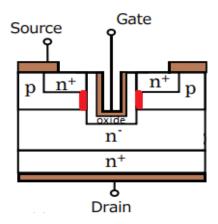

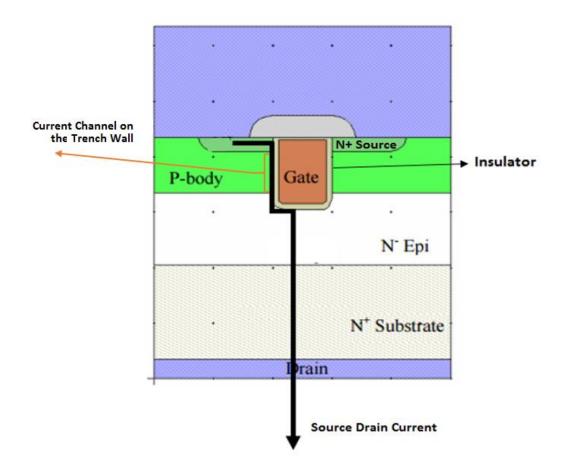

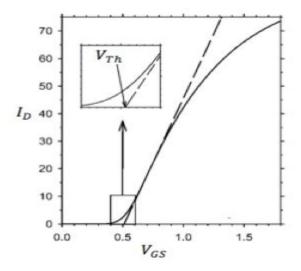

Figure 1.2 shows the current flow in a trench MOSFET during the on state when the device is conducting current. The gate metal/insulator/P-body region create a MOS capacitor and hence applying voltage to the gate metal that is higher than a minimum voltage, called threshold voltage  $(V_{Th})$ , creates a current channel on the trench side wall in the P-body region. This will create a current path from the N+ source to the drain.

Figure 1.2: Current flow in trench MOSFET [3]

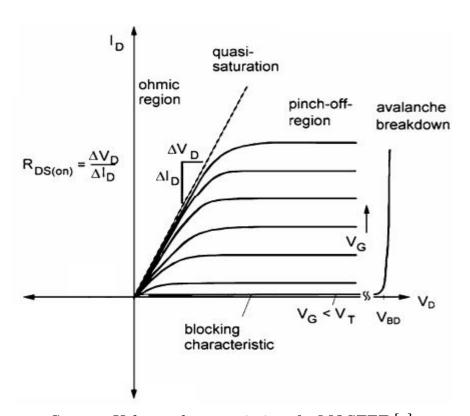

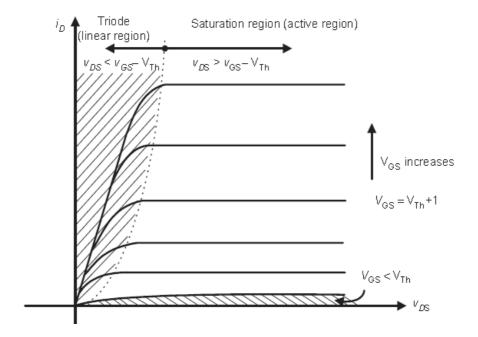

The amount of the source drain current depends on the gate voltage and the on-resistance between the drain and source. The current-voltage (I-V) curve of a MOSFET is shown in Figure 1.3. As can be seen, during the on state the I-V curve is divided into two regions: linear (ohmic) and saturation (pinch-off) regions. For low drain voltage  $(V_D)$ , the I-V characteristics have a linear form, this area is called ohmic region. When the drain voltages is increased the drain current saturate at a maximum level (pinch off or saturation region). The transition between the ohmic region and the pinch off region is called quasi saturation.

As can be seen, the higher the gate voltage is, the higher the drain current would be. If the drain voltage is increased to more than the breakdown voltage rating of the device, avalanche breakdown happens, and the amount of current passing between the source and the drain increases rapidly and suddenly. The avalanche breakdown is due to the increase of electric field to more than the critical electric field of the semiconductor material. Though as would be discussed in this work, basic SiC trench MOSFET structure such as the one shown in Figure 1.2 enters breakdown because of breakdown of the insulator layer not the semiconductor material.

Figure 1.3 : Current-Voltage characteristics of a MOSFET [4]

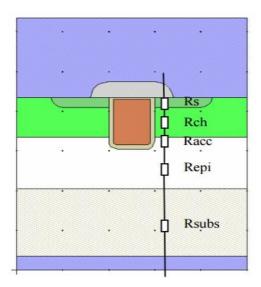

The other factor that affect the I-V characteristics, is the on resistance between the source and drain  $(R_{DSON})$ . The amount of current that can pass through source to drain when the voltage is increased, depends on  $R_{DSON}$ . The slope of the curve on the ohmic region is representative of  $R_{DSON}$ , lower slope means higher  $R_{DSON}$ . Higher on resistance, results in higher energy loss, lower switching speed and lower channel mobility and should be minimized.

#### 1.2.2 Off State

Off state refers to the state where there is no voltage applied to the gate contact (or if the gate voltage is less than the threshold voltage). During the off state, the current channel does not exist on hence there is no current flow between the N+ source and the drain region except for very little leakage current. The drain voltage in this state is supported by the depletion region that is created by the P-body/N- drift junction. The effect of the N+ source/P- body/N-drift bipolar transistor is suppressed by shorting the P-body and N+ source [5]. It is very important to choose the right thickness and doping for the P-body region, otherwise the depletion region in the P-body will reach to N+ source that will result in a large leakage current. The reach through design can result in premature breakdown of the device.

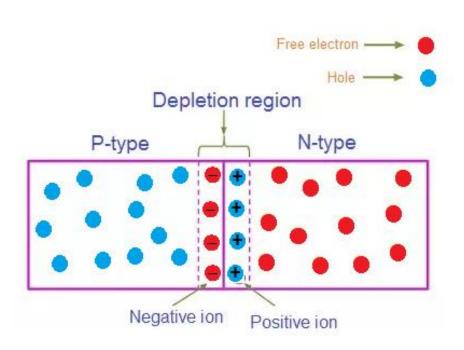

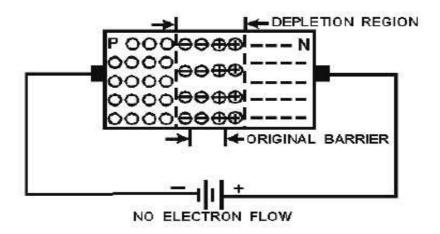

Figure 1.4 shows the creation of depletion region across P/N junction. The depletion region is created when the device is in reverse biased operation mode when a positive voltage is applied to the N- doped (drift) region. Majority

carriers in the N- doped region (free electrons) are attracted to the positive terminal, leaving immobile positive ions near the P/N junction. The positive ions near the junction on the N- doped region, will start to repel the holes on the P-doped side. The holes will leave immobile negative ions near the P/N junction. This will create a depletion region near the P/N junction of immobile ions that will block the current (Figure 1.4). The ions near the junction create a strong electric field that will block the voltage.

Figure 1.4: Depletion region created in a PN junction.

Higher drain voltages, result in higher electric field in the P/N junction.

When this electric field reaches the critical electric field of SiC material, an

abrupt leakage current is observed. This maximum drain voltage is called breakdown voltage. The blocking capacity of the trench MOSFET is determined by the N- drift region thickness and doping. This will be discussed in more details in the Chapter 3.

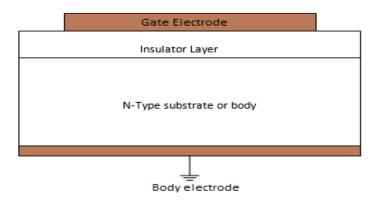

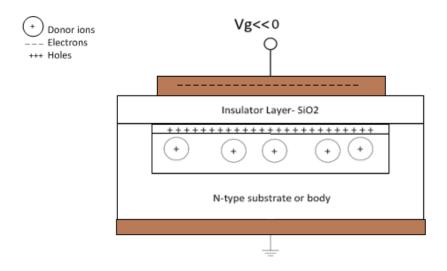

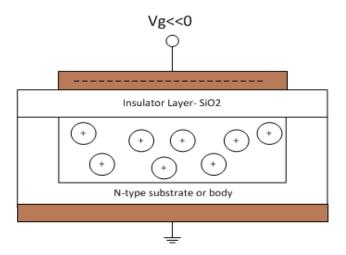

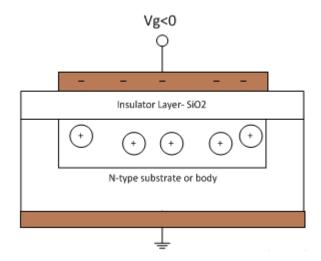

# 1.3 MOS Capacitor