### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/137165

### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Aspects of Practical Implementations of PRAM Algorithms

Somasundaram Ravindran

A thesis submitted for the Degree of Doctor of Philosophy

Department of Computer Science University of Warwick

December 1993

To my daughter Meera, with love.

1

#### Acknowledgments

I am very grateful to my supervisor, Dr Alan Gibbons, who introduced me to the area of parallel computation and provided encouragement and support in my research. His quick mind and knowledge of the field greatly helped me in my thinking, writing proofs, and making me realise what I was doing in a much broader context. He was also a constant source of support in non-technical matters.

I would also like to thank the many members of the Computer Science Department at the University of Warwick who provided a diversity of assistance over the past three years.

Above all I would like to gratefully thank my wife, Mythili. Without her constant help and support, this thesis would not have been possible.

#### **Declaration**

This thesis is submitted to the University of Warwick in support of my application for admission to the degree of Doctor of Philosophy. No part of it has been submitted in support of an application for another degree or qualification of this or any other institution of learning. Parts of the thesis appeared in the following papers in which my own work was that of a full pro-rata contributor:

- 1. S. Ravindran, B. Dessau and A.M. Gibbons, "An overview of PRAM to practical PRAM algorithmics", *Report 6.2.1, Parallel Universal Message-passing Architecture*, ESPRIT Project 2701 of the EC, 1991.

- 2. S. Ravindran and A.M. Gibbons, "Dense edge-disjoint embedding of binary trees in the hypercube", *Information Processing Letters*, Vol. 45, 321-325, 1993.

- 3. S. Ravindran and A.M. Gibbons, "Densely embedding the complete binary tree in communication networks", 9<sup>th</sup> British Colloquium for Theoretical Computer Science, University of York, England, March 1993.

- 4. S. Ravindran, A.M. Gibbons and M.S. Paterson, "Dense edge-disjoint embedding of complete binary trees in interconnection networks", submitted to *Theoretical Computer Science*, December 1993.

- 5. S. Ravindran, N.W. Holloway and A.M. Gibbons, "Approximating minimum weight perfect matchings for complete graphs satisfying the triangle inequality", in *Proceedings of* 19<sup>th</sup> International Workshop on Graph-Theoretic Concepts in Computer Science, Lecture Notes in Computer Science, Springer-Verlag, 1993.

S. Ravindran

20th December 1993

#### Abstract

The PRAM is a shared memory model of parallel computation which abstracts away from inessential engineering details. It provides a very simple architecture independent model and provides a good programming environment. Theoreticians of the computer science community have proved that it is possible to emulate the theoretical PRAM model using current technology. Solutions have been found for effectively interconnecting processing elements, for routing data on these networks and for distributing the data among memory modules without hotspots. This thesis reviews this emulation and the possibilities it provides for large scale general purpose parallel computation. The emulation employs a bridging model which acts as an interface between the actual hardware and the PRAM model. We review the evidence that such a scheme can achieve scalable parallel performance and portable parallel software and that PRAM algorithms can be optimally implemented on such practical models. In the course of this review we presented the following new results:

- Concerning parallel approximation algorithms, we describe an NC algorithm

for finding an approximation to a minimum weight perfect matching in a

complete weighted graph. The algorithm is conceptually very simple and it

is also the first NC-approximation algorithm for the task with a sub-linear

performance ratio.

- 2. Concerning graph embedding, we describe dense edge-disjoint embeddings of the complete binary tree with n leaves in the following n-node communication networks: the hypercube, the de Bruijn and shuffle-exchange networks and the 2-dimensional mesh. In the embeddings the maximum distance from a

leaf to the root of the tree is asymptotically optimally short. The embeddings facilitate efficient implementation of many PRAM algorithms on networks employing these graphs as interconnection networks.

Concerning bulk synchronous algorithmics, we describe scalable transportable

algorithms for the following three commonly required types of computation;

balanced tree computations, Fast Fourier Transforms and matrix multiplications.

# **Contents**

| 1 | Intro | oductio  |                   |          |     |     |      |      |     |    |    |   |   |   |   |   |   | 1  |

|---|-------|----------|-------------------|----------|-----|-----|------|------|-----|----|----|---|---|---|---|---|---|----|

| 2 | Clas  | sical PF | AM Design         |          |     |     |      |      |     |    |    |   |   |   |   |   |   | 6  |

|   | 2.1   | Introdu  | ction             |          |     |     |      |      |     |    |    |   |   |   |   |   | • | 6  |

|   | 2.2   | The PF   | AM model          |          |     |     |      |      | ٠   |    |    |   |   |   |   | • |   | 9  |

|   |       | 2.2.1    | Concepts of effic | ient and | lop | tim | al a | ilgo | rit | hn | ıs |   |   |   | • |   |   | 11 |

|   | 2.3   | Basic I  | RAM techniques    |          |     |     |      |      |     |    |    |   |   | ٠ |   | ٠ |   | 12 |

|   |       | 2.3.1    | Balanced tree .   |          |     |     |      |      | •   |    |    |   |   |   |   |   |   | 12 |

|   |       | 2.3.2    | Doubling          |          |     |     |      |      |     |    |    |   |   |   |   |   |   | 14 |

|   |       | 2.3.3    | Divide-and-conq   | uer      |     | ٠   |      |      |     |    |    |   |   |   |   |   |   | 15 |

|   |       | 2.3.4    | Reducing the nu   | mber of  | pro | ces | sor  | s.   | ٠   |    |    | ٠ | ٠ |   |   |   | • | 16 |

|   | 2.4   | PRAM     | algorithmic tools |          |     |     |      |      |     |    |    |   |   |   |   |   | ٠ | 18 |

|   |       | 2.4.1    | Prefix computati  | on , , , |     |     |      |      | ٠   |    |    | ٠ | 4 | ٠ |   | ٠ |   | 18 |

|   |       | 2.4.2    | List ranking      |          |     |     |      |      |     |    |    |   |   |   |   |   |   | 21 |

# **Contents**

| 1 | Intr                  | oduction | n                                            | 1  |  |  |  |  |  |  |

|---|-----------------------|----------|----------------------------------------------|----|--|--|--|--|--|--|

| 2 | Classical PRAM Design |          |                                              |    |  |  |  |  |  |  |

|   | 2.1                   | Introdu  | uction                                       | 6  |  |  |  |  |  |  |

|   | 2.2                   | The PR   | RAM model                                    | 9  |  |  |  |  |  |  |

|   |                       | 2.2.1    | Concepts of efficient and optimal algorithms | 11 |  |  |  |  |  |  |

|   | 2.3                   | Basic F  | PRAM techniques                              | 12 |  |  |  |  |  |  |

|   |                       | 2.3.1    | Balanced tree                                | 12 |  |  |  |  |  |  |

|   |                       | 2.3.2    | Doubling                                     | 14 |  |  |  |  |  |  |

|   |                       | 2.3.3    | Divide-and-conquer                           | 15 |  |  |  |  |  |  |

|   |                       | 2.3.4    | Reducing the number of processors            | 16 |  |  |  |  |  |  |

|   | 2.4                   | PRAM     | algorithmic tools                            | 18 |  |  |  |  |  |  |

|   |                       | 2.4.1    | Prefix computation                           | 18 |  |  |  |  |  |  |

|   |                       | 2.4.2    | List ranking                                 | 21 |  |  |  |  |  |  |

|   |      |                                                                    | vii |  |  |  |  |

|---|------|--------------------------------------------------------------------|-----|--|--|--|--|

|   | 2.5  | Graph algorithms                                                   | 23  |  |  |  |  |

|   |      | 2.5.1 Euler tour on trees                                          | 25  |  |  |  |  |

|   |      | 2.5.2 Tree contraction                                             | 27  |  |  |  |  |

|   |      | 2.5.3 Ear decomposition                                            | 27  |  |  |  |  |

|   |      | 2.5.4 Matrix computations                                          | 28  |  |  |  |  |

| 3 | Para | allel Approximation Algorithm                                      | 30  |  |  |  |  |

|   | 3.1  | Introduction                                                       | 30  |  |  |  |  |

|   | 3.2  | Performance ratios of approximation algorithms                     | 32  |  |  |  |  |

|   | 3.3  | Minimum weight perfect matching                                    | 33  |  |  |  |  |

|   | 3.4  | Approximate minimum weight perfect matching in a complete weighted |     |  |  |  |  |

|   |      | graph                                                              | 35  |  |  |  |  |

|   |      | 3.4.1 Validity of the approximation ratio claim                    | 38  |  |  |  |  |

|   |      | 3.4.2 Parallel execution and complexity of the algorithm           | 41  |  |  |  |  |

|   | 3.5  | Further work                                                       | 44  |  |  |  |  |

| 4 | Rea  | distic Issues                                                      | 46  |  |  |  |  |

|   | 4.1  | Introduction                                                       | 46  |  |  |  |  |

|   | 4.2  | Interconnection Networks                                           | 47  |  |  |  |  |

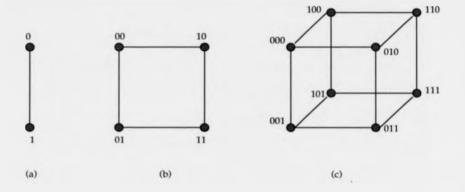

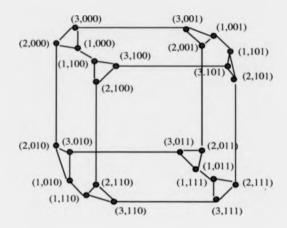

|   |      | 4.2.1 The hypercube family                                         | 48  |  |  |  |  |

|   |      | 4.2.2 The shuffle-exchange and de Bruijn networks                  | 54  |  |  |  |  |

|   |     |         |                                                  | viii |

|---|-----|---------|--------------------------------------------------|------|

|   |     | 4.2.3   | Meshes                                           | 56   |

|   |     | 4.2.4   | Randomly-wired networks                          | 58   |

|   | 4.3 | Conten  | ntion and congestion                             | 61   |

|   |     | 4.3.1   | Hashing                                          | 63   |

|   |     | 4.3.2   | Combining                                        | 66   |

|   |     | 4.3.3   | Routing                                          | 69   |

|   |     | 4.3.4   | Information dispersal algorithm                  | 73   |

|   | 4.4 | Synchr  | ony and asynchrony                               | 74   |

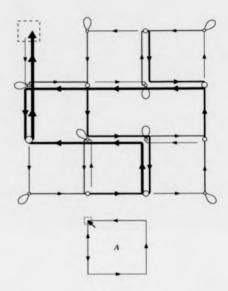

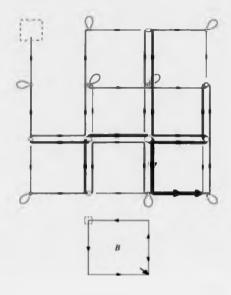

| 5 | Emb | eddings | <b>§</b>                                         | 75   |

|   | 5.1 | Introdu | action                                           | 75   |

|   | 5.2 | Efficie | ncy requirements                                 | 76   |

|   | 5.3 | The em  | nbeddings                                        | 77   |

|   |     | 5.3.1   | Embedding in the de Bruijn graph                 | 79   |

|   |     | 5.3.2   | Embedding in the shuffle-exchange graph          | 82   |

|   |     | 5.3.3   | Embedding in the 2-dimensional mesh              | 84   |

|   |     | 5.3.4   | Embedding in the hypercube                       | 87   |

|   | 5.4 | Depths  | s of the embedded trees                          | 92   |

|   |     | 5.4.1   | Maximum root-to-leaf distances of the embeddings | 93   |

|   |     | 5.4.2   | Lower bounds for the embedded tree depths        | 95   |

|   |      |                                               | ΪX  |

|---|------|-----------------------------------------------|-----|

|   | 5.5  | Further remarks and algorithmic issues        | 97  |

|   | 5.6  | Summary and open problems                     | 100 |

| 6 | Prac | tical Parallel Models of Parallel Computation | 102 |

|   | 6.1  | Introduction                                  | 103 |

|   | 6.2  | The practical PRAM model                      | 104 |

|   | 6.3  | Latency hiding                                | 106 |

|   | 6.4  | Asynchronous computation                      | 113 |

|   | 6.5  | Memory management                             | 117 |

|   | 6.6  | Conclusion                                    | 120 |

| 7 | Bull | s Synchronous Parallel Algorithms             | 121 |

|   | 7.1  | Introduction                                  | 121 |

|   | 7.2  | Balanced tree computation                     | 123 |

|   | 7.3  | Fast Fourier Transform                        | 124 |

|   | 7.4  | Transitive closure and graph algorithms       | 127 |

|   | 7.5  | Further work                                  | 129 |

| 8 | Con  | clusions                                      | 130 |

# **Chapter 1**

# Introduction

A few years ago parallel computers could be found only in research laboratories. Due to the rapidly decreasing cost of processors, memory and communication, they are now available commercially. It is possible that, within a decade, parallel computation will dominate in all areas of computer science and its applications. A deep understanding of parallel computations is therefore highly desirable.

The complexity theory research community has developed a rich literature in the design and analysis of efficient parallel algorithms. To date, most of this work has been based on the *Parallel Random Access Machine* (PRAM). The PRAM model consists a number of processing elements and a (shared) memory. The processing elements operate in lock step synchrony and access a location in the shared memory in unit time (chapter 2 gives a detailed description of the PRAM model). The realistic issues are ignored by the PRAM model. The PRAM algorithms do not take account of the low level details of parallel computation, such as interprocessor or processors-to-memory communication, memory management and hardware failure.

For this reason, the PRAM provides a very simple and natural model for architecture independent parallel algorithm design.

One benefit of PRAM studies is an extensive list of *fast* parallel algorithms. By a *fast* algorithm we mean one that that takes polylogarithmic parallel time using a polynomial number of processors. Problems which can be solved by a *fast* algorithm are said to belong to the class NC. This class name is an acronym for Nick (Pippenger's) Class. The search for parallel solutions to place the problems in NC has demonstrated that entirely new algorithmic techniques are appropriate and it is usually a bad starting point to attempt to parallelise the best sequential algorithms. Design techniques and tools have therefore been developed for parallel computation which are completely different from the sequential domain. In fact, some of the commonly used methods in sequential algorithm design do not adapt well to parallelism. Moreover, many problems in the class P, i.e. the problems have polynomial time sequential solution, have been proven P-complete. If a problem is P-complete then it is very unlikely that the problem belongs to the class NC.

The primary interest of the study of parallel complexity is placing the problems in P into the class NC. In fact, there are problems in P but we do not know whether they lie in NC, and they have not been proven to be P-complete. However, for such problems it may be possible to find an NC approximation algorithm to the problems. For example, if the problem is a minimisation problem then we find a solution which is not minimum, but the solution is never greater than some factor of the optimal solution.

Although the PRAM model has been prominent in the development of the design

and analysis of parallel algorithms, the unrealistic characteristics of the model may make us think that the model is not suitable for general purpose parallel computation. However, we shall see in this thesis that the PRAM model can be emulated by a feasible parallel computer. A feasible parallel computer is a number of processing elements interconnected by a network, where each processing element performs computational and/or memory operations and the processing elements may or may not have to be synchronised. The memory of a feasible parallel computer is distributed among memory modules.

In contrast to a PRAM, a (non local) memory access in a feasible parallel computer takes much longer than a local computation. This is because the data have to be transferred through an interconnection network. Further delays can occur due to congestion in the interconnection network and contention at the memory modules. Moreover, a PRAM assumes that the processors and the communications links are fault-free. Theoretical solutions have been found for routing data to the right processing element within a reasonable time, for distributing the data among memory modules so that the distribution will not slow down the computation, and for coping with processors and network failures.

At present, almost all of the parallel software designed for a realistic physical parallel model is not portable. This is because the algorithms are often developed for a particular network topology of fixed size. This software is not based on general principles and to date has not been written for a common virtual machine. Progress in technology suggests to us that rapid changes in parallel machines are still to come. Hence, current software will not have a long life time. The major challenge in parallel

computing is developing architecture independent parallel software with an expected lifetime of several decades. We need an interface (or bridging) model between the software and hardware. Such a model will offer architecture independent software and will be compatible with technological evolution.

Using the theoretical solutions for routing and for memory management we can build a bridging model with virtual shared memory. A user can view this model as an extended PRAM, which hides hardware details from the user. The model is called *practical PRAM*. Recently a number of *practical PRAMs* have been proposed which variously take account of communication delay, contention and congestion, asynchrony and component failures. In this thesis we review these models and show that it is possible to develop an architecture independent software with a long life time.

The remainder of this thesis is organised as follows.

- Chapter 2 reviews the design techniques and tools of parallel computation,

and provides the evidence for the significance of the PRAM model.

- Chapter 3 gives a novel approximation algorithm for a problem whose parallel complexity remains unknown. It is not known whether the problem lies in NC, and it has not been proven to be P-complete.

- Chapter 4 focuses on the realistic issues which are ignored by the PRAM model. If an interconnection network is to be used for general problem solving then it ought have certain desirable graph theoretic properties. Chapter 4 describes interconnection networks which satisfy these properties. Further-

more, chapter 4 reviews the theoretical solutions for routing, for memory management and for fault tolerance.

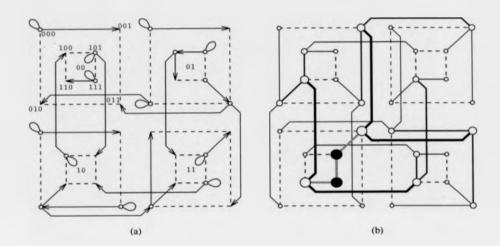

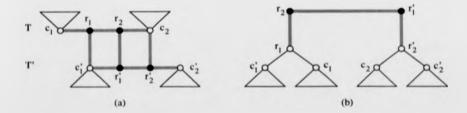

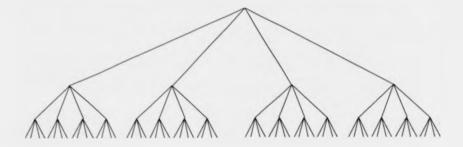

- The most commonly occurring structure in parallel computation is the complete binary tree. It is precisely because such logarithmic depth structures are used (either explicitly or implicitly) that polylogarithmic time complexities are attained for many PRAM algorithms. Chapter 5 shows that the complete binary tree can be embedded in the interconnection networks, the mesh, hypercube, de Bruijn and shuffle-exchange networks, so that an algorithmically important parameter, the maximum distance from a leaf to the root, is optimised asymptotically. Thus, O(log n) time PRAM algorithms which use the complete binary tree as the algorithmic structure can be translated to optimal time on the interconnection network.

- With the use of theoretical solutions which are described in chapter 4, chapter 6

demonstrates that there is no hindrance in designing practical parallel models

of parallel computation. Moreover, this chapter shows that a PRAM algorithm

can be implemented on the practical parallel model without any significant

delay in run time.

- Chapter 7 shows that scalable transportable algorithms for practical parallel models can be written for certain basic tasks, balanced tree computations, Fast Fourier transforms and matrix multiplication.

# Chapter 2

# **Classical PRAM Design**

### 2.1 Introduction

The PRAM model of parallel computation is described in detail in section 2.2. At first glance, the PRAM model of computation might not appear to be suitable as a general model for designing and analysing parallel algorithms. For sequential computation, it has been of considerable advantage to deal with an abstraction of the von Neumann machine, namely the Random-Access Machine or RAM (see [3] for details of the model). Similar advantages justify the PRAM model:

- Ease of use: Algorithms can be specified with little intricacy.

- Portability: PRAM algorithms do not need to take into account memory organisation, network topology or other hardware design attributes of real parallel machines, so that they eliminate obstacles to portability.

Scalability: Typically the number of processors which are used can be increased in a natural way such that the speed of the computation retains the same functional dependence on the problem size.

The main preoccupation of PRAM algorithm designers has been to place the problem in hand in the class NC. Various idealised models of parallel computation other than the PRAM model have been used in the study of parallel algorithms and their complexity. These include Boolean circuits and alternating Turing machines. The complexity class NC remains unchanged when defined by these models [138, 149]. This motivates the definition of the complexity class NC. Note that when using a family of Boolean circuits as a model of parallel computation, the family is usually required to satisfy a *logspace uniformity condition* [139]. A family of Boolean circuits is logspace uniform if there is a deterministic Turing machine can construct some standard encoding of the  $n^{th}$  circuit using  $O(\log n)$  work space.

It is reasonable to seek an NC algorithm for a problem, if the problem can be solved sequentially in polynomial time. Let P be the class of decision problems that can be solved by a deterministic Turing machine within a polynomial number of sequential steps [3]. We can see that  $NC \subseteq P$  by converting NC algorithms into sequential algorithms in the obvious way. A fundamental open question is whether every problem in P lies in NC. The parallel computation thesis states that "time bounded parallel machines are polynomially related to space bounded sequential machines" [18, 22, 43, 57, 122]. That is NC computations can be simulated by Turing machines using only polylogarithmic space. Thus, P = NC would imply that P is contained in a class of problems that can be solved in polylogarithmic

space by a sequential machine, which is considered very unlikely. This is why we believe that there exists problems which do not adapt well to parallelism. In fact, many problems have been proven to be in P-complete. For a list of P-complete problems see [59, 107]. If a problem is P-complete then the problem is unlikely to lie in NC. More formally, a problem  $L \in P$  is said to be P-complete if every other problem in P can be transformed into L by a deterministic Turing machine using only log space (such a transformation is said to be a log space reduction). It follows that, if  $L \in P$ -complete and  $L \in NC$  then P = NC. It turns out that some of the commonly used methods in sequential algorithms are likely inherently sequential methods. Thus the design of parallel algorithms requires new paradigms and techniques.

In this chapter we show that, the benefit from the PRAM model is not only in the extensive list of efficient and parallel algorithms that have been designed, but also fundamental paradigms and design techniques and tools have emerged. These are usually completely different from the best known sequential solutions to the same problems and indicate new paradigms for parallel algorithm design. Sections 2.3 and 2.4 describe the techniques and tools respectively. In section 2.5 we review some graph algorithms, and show that these are useful not only in their own right for the problems they solve, but also as common subroutines in many parallel algorithms. Note that in this chapter we consider only graph algorithms. Of course, the PRAM can be and has been used to solve problems in many other areas. For example, survey papers [38] and [65] list references for *computational geometry* and *pattern matching* respectively. Many other references can be found in [42, 52, 68, 76, 103, 166].

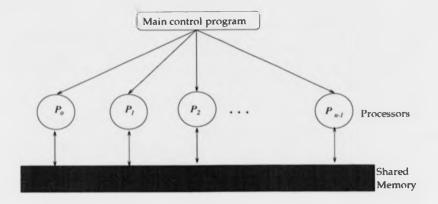

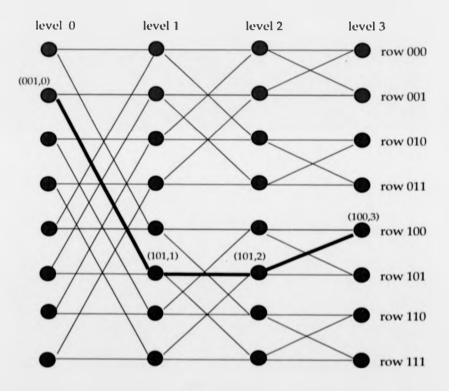

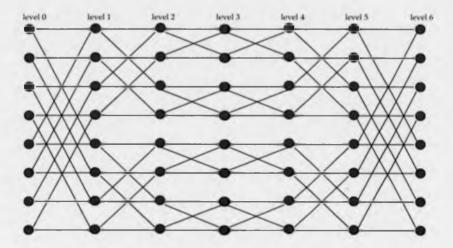

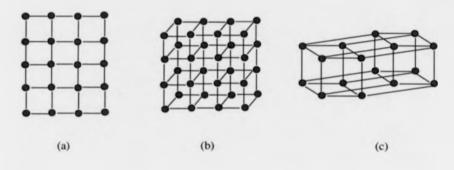

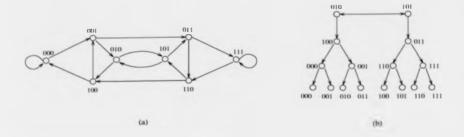

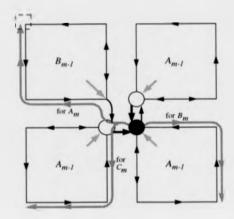

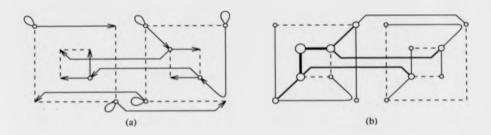

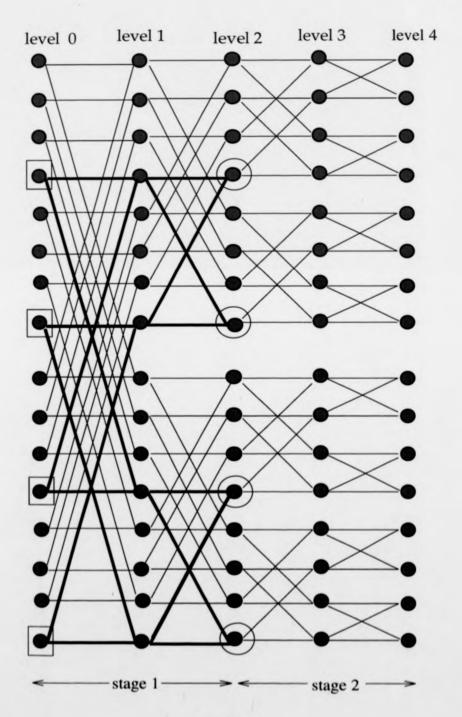

Figure 2.1:

#### 2.2 The PRAM model

The PRAM model is an abstract shared memory model. It was introduced in [43, 169]. There are a number of processors working together and communicating through the shared memory. The processors synchronously execute the same program through the central main control (see figure 2.1). Although performing the same instructions, the processors can be operating on different data. Hence, such a model is a Single-Instruction, Multiple-Data model, namely an SIMD model. Each processor is a uniform-cost random-access machine or RAM with usual operations and instructions. The cost of arithmetical operations (addition, subtractions, equality predicate and so on) is constant. In one step each processor can access (either reading from it or writing to it) one memory location or execute a single RAM operation.

Memory access leads to variants of the model which allow or do not allow more than one processor to read or to write to the same memory location. For example the EREW PRAM (exclusive read exclusive write parallel random access machine which allows no concurrent reads and no concurrent writes), the CREW PRAM (concurrent reads allowed but only exclusive writes) and the CRCW PRAM (in which both concurrent writes and concurrent reads are allowed). In general concurrent reads cause no logical errors. However, with concurrent writes additional rules are required to resolve the outcome. This leads to variants of the CRCW PRAM, namely the so-called *common*, *arbitrary* and *priority* variants. These resolves the write conflicts as follows: in the *common* variant all processors writing into the same location write the same value, in the *arbitrary* variant any one processor participating in a common write may succeed and the algorithm should work regardless of which one does, and in the *priority* variant there is a linear order on the processors and the minimum numbered processor succeeds in writing.

Any algorithm that works on an EREW PRAM works on a CREW PRAM, any algorithm that works on a CREW PRAM works on a common CRCW PRAM, and so on. Moreover, the list of variants of the PRAM model: EREW, CREW, common CRCW, arbitrary CRCW and priority CRCW, represents the PRAM models in increasing order of their power. But, they do not differ much in their power. The following theorem [164] indicates this. This justifies the class NC; the class remains unchanged regardless of variants of the PRAM model.

**Theorem 2.2.1** Any algorithm for a priority CRCW PRAM of p processors can be simulated by a EREW PRAM with the same number of processors and with the parallel time increased by a factor of  $O(\log p)$ .

#### 2.2.1 Concepts of efficient and optimal algorithms

In the PRAM model, the relevant complexity measure of an algorithm are the time for parallel computation and the number of processors used. The time-processor product of a PRAM algorithm is called the *work* of the algorithm.

Suppose a PRAM algorithm runs in time t(n) by employing p(n) processors for a problem size n, then the PRAM algorithm can be converted into a sequential algorithm of time equal to the work of the PRAM algorithm,  $t(n) \times p(n)$ . We can do this by simulating each parallel step of the PRAM algorithm on a sequential processor in p(n) time units. This justifies the definition for an *optimal* algorithm. A PRAM algorithm for the problem in NC is *optimal* if the work of the algorithm is asymptotically equal to the fastest sequential computation time for the problem.

An optimal parallel algorithm achieves a high degree of parallelism. Analogously, a PRAM algorithm for the problem in NC is *efficient* if the work of the algorithm is within a polylogarithmic factor of the fastest sequential computation time for the problem. Designing an optimal algorithm on a CRCW PRAM is easier than on a CREW or EREW PRAM. This is because more parallelism can be expressed on a CRCW PRAM than on a CREW or EREW PRAM. The class of problems which have *efficient* algorithms, remains unchanged regardless of the PRAM model used (for example, see theorem 2.2.1). Thus our notion of *efficiency* is more robust than the notion of *optimality*.

Concerning speed of computation, one might expect that it is possible to discover parallel algorithms that run in constant time. Research on lower bounds for parallel computation indicates that this goal is unachievable for almost any interesting

problems. This is because we require a lower bound of  $\Omega(\log n/\log\log n)$  time for the parity problem of n bits on a *priority* CRCW PRAM with a polynomial number of processors [14]. This is because the parity problem depends on all the inputs. But the problem of computing the OR or AND of n Boolean variables can be done in constant time on a CRCW PRAM. Because, the decision of this problem only depends on one input. However, this computation requires  $\Omega(\log n)$  on a CREW PRAM with no restriction on the number of processors [34]. Since any interesting problems such as the basic PRAM subcomputations of prefix computation and list ranking (described in section 2.4) are typically at least as hard as computing the parity of n bits or OR of n variables, we see that constant time parallel computation is not admissible for any interesting problems.

## 2.3 Basic PRAM techniques

A number of general techniques and principles of common use in the design of parallel algorithms are described in this section.

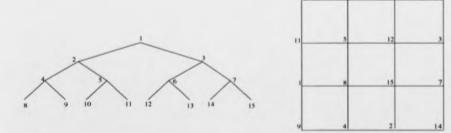

#### 2.3.1 Balanced tree

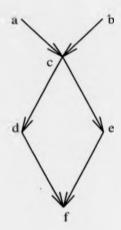

The balanced binary tree is a fundamental structure in parallel computation. A tree is a connected graph containing no circuits, in which one vertex is distinguished as a root. In a tree any vertex with of degree one, unless it is the root, is called a leaf. A node is said to be an internal node if the node is not a leaf. If (x, y) is an edge of a tree such that x lies on the path from the root to y, then x is said to be the parent of

y and y is the child of x. A tree is balanced if each internal node has same number of children. A balanced tree is called complete binary tree if each internal node has two children and the number of nodes is 2n - 1, where n is the number of leaves. The minimum distance between a leaf and the root in a complete binary tree is  $\log n$ , where n is the number of leaves.

It is precisely because such logarithmic depth structures are used (either explicitly or implicitly) that polylogarithmic time complexities are attained for many PRAM-algorithms. In the PRAM model, the balanced binary tree is employed as follows. Data for a problem are placed at the leaves, and each internal node corresponds to the computation of a subproblem. The sub problems are solved in bottom-up order (or in one or more sweeps up and down the tree), with those at the same level in the tree being computed in parallel.

For example, consider the problem of adding n numbers. Let  $n=2^m$  and A be an array of length 2n. The numbers whose sum is to be found can be placed at the leaves of a tree, i.e. we store the n numbers in the locations  $A(n), A(n+1), \ldots, A(2n-1)$ . At each level of the tree, numbers are added together in pairs by different processors in parallel and the result sent to the next level as follows [52].

for

$$k\leftarrow m-1$$

step -/ to  $0$  do

$${\rm for}\ all\ j,\ 2^k\le j\le 2^{k+1}-1,\ {\rm in}\ {\rm parallel}\ {\rm do}\ A(j)\leftarrow A(2j)+A(2j+1)$$

A processor assigned to an internal node reads the values of the left child and the right child from the corresponding locations, then writes the sum of the values in the location corresponding to the internal node. If the corresponding location of

an internal node is A(j) then the corresponding locations of its left child and right child are respectively A(2j) and A(2j+1). At the end of the computation A(1), the location corresponding to the root, stores the result. The depth of the tree is bounded by  $\lceil \log n \rceil$  and so the computation time is  $O(\log n)$  using n/2 processors. This problem clearly belongs to NC. It will be shown later how to reduce the number of processors to achieve optimal work measure.

#### 2.3.2 Doubling

This technique is normally applied to an array or to a list of elements. Each element knows the location of the next element in the data structure. The computation proceeds by a recursive application of the calculation in hand to all elements over a certain distance (in the data structure) from each individual element. This distance doubles in successive steps. Thus after k stages the computation has been performed (for each element) over all elements within a distance of  $2^k$ .

For example, consider an array A of n elements which specifies a set of rooted directed trees, a forest F. A location of the array A(i) = j if j is the parent of i in a tree of F, for  $1 \le i \le n$ , and if i is a root then A(i) = i. Suppose, for each i,  $1 \le i \le n$ , we want to determine the root of the tree containing the node i. Let s(i) be the successor of node i, i.e initially s(i) = A(i), for  $1 \le i \le n$ . The successor of each node, s(i), is replaced by the successor's successor, s(s(i)), in successive steps. If a processor is assigned to each array location then  $O(\log h)$  steps are sufficient for this computation. Here h is the maximum height of any tree in the forest. Sometimes this technique is referred to as pointer jumping.

The doubling technique is not only applicable to arrays and lists. For example, it can be used to compute  $A^n$  of a Boolean matrix A. The computation can be performed in at most  $2\lfloor \log_2 n \rfloor$  matrix multiplications. First we compute  $A^2, A^4, A^8 \dots A^k$  by squaring the matrix successively, where k is the largest number such that  $k \leq n$  and k is a power of 2. Now we can compute  $A^n$  by multiplying together appropriate matrices of the form  $A^{2^l}$ ,  $0 \leq l \leq \lfloor \log_2 n \rfloor$ .

#### 2.3.3 Divide-and-conquer

The divide-and-conquer technique involves partitioning a problem into subproblems, solving the subproblems, and then combining the solutions to the subproblems to form the solution for the original problem. The methodology is recursive; that is, the subproblems themselves may be solved by the divide-and-conquer technique. This method is widely applicable in sequential computation. In a parallel setting the method requires that the subproblems at the same level of recursion can be independently computed in parallel and (in order to reduce the depth and therefore the computation time) are of similar size.

There are several examples of the divide-and-conquer technique applied in a parallel setting. Although the field of computational geometry is rather neglected in this thesis, we complete this description of divide-and-conquer with an application from this area. Given a finite set S of points in the plane, computing their convex hull, CH(S), is an important basic problem in computational geometry that arises in a variety of contexts [38]. CH(S) is the smallest convex polygon containing all the points of S. A polygon CH(U) is convex if, given any two points p and q in

CH(U), the line segment whose endpoints are p and q lies entirely in CH(U). A tangent of a convex polygon CH(U) is a line passing through a vertex of CH(U) such that CH(U) lies entirely on one side of the line. A tangent is called upper (lower) common tangent between two convex polygon, CH(U) and CH(V), if the tangent is the common tangent such that CH(U) and CH(V) are below (above) it. CH(S) can be constructed as follows:

- 1. Sort the set S in some fixed direction (eg. in the x or y-direction). Let U be the first |S|/2 points in this sorted order, and V the remainder.

- 2. Recursively construct CH(U) and CH(V) in parallel.

- 3. Compute the upper and lower common tangents of CH(U) and CH(V).

- Combine CH(U) and CH(V) by using the upper and lower common tangents

of CH(U) and CH(V), to form CH(S).

#### 2.3.4 Reducing the number of processors

Consider a computation A that can be done in t parallel steps. Let  $\alpha_i$  be the number of primitive operations at step i. To run A directly on a PRAM in t parallel steps, the number of processors required is the maximum of the  $\alpha_i$ , say m. Suppose we have p < m processors. The  $t^{th}$  step can be computed in time  $\lceil \alpha_i/p \rceil$ , by partitioning the  $\alpha_i$  operations into p groups and assigning a processor to each of the groups. For each of the p groups in parallel, each processor will be computing (in sequential style) for at most  $\lceil \alpha_i/p \rceil$  time. Hence the total parallel time is no more than  $t + \lceil \sum_{i=1}^t \alpha_i/p \rceil$

For example, consider the algorithm described earlier for computing the sum of nnumbers using the balanced binary tree method. This executes in  $O(\log n)$  time. Notice that n/2 processors are required for the first step. Suppose that we have p < n/2 processors. We can simulate the first step with p processors as follows. First we divide the n numbers into p groups, such that  $i^{th}$  group has elements indexed from  $(i \lceil n/p \rceil)$  to  $(((i+1)(\lceil n/p \rceil))-1)$  for  $0 \le i < p$ . The first (p-1) of these groups contain  $\lceil n/p \rceil$  elements and the remaining group contain  $n-(p-1)\lceil n/p \rceil$ elements. We assign a processor to each of the groups. For all of the p groups in parallel, each group now finds the sum in sequential style within its group, and the computation takes  $\lceil n/p \rceil$  time. We have reduced the original problem of size n to a problem of size p, and the problem can be solved as described before in  $O(\log p)$  time using the p processors. Thus, overall, we can find the sum of the n numbers in  $\lceil n/p \rceil + \log p$  time using  $p \le n/2$  processors. Notice that if we set  $p = n/\log n$  then we obtain a computation time of  $O(\log n)$  and we thus have an optimal algorithm. The work of the algorithm is O(n) and is same as the best known sequential algorithm.

This is an example of applying *Brent's scheduling principle* [20], and is often used in the design of efficient or optimal parallel algorithms. It should be noted that this simulation assumes that processor allocation is not a problem. We will see (in section 2.4.2) that this is sometimes a nontrivial task.

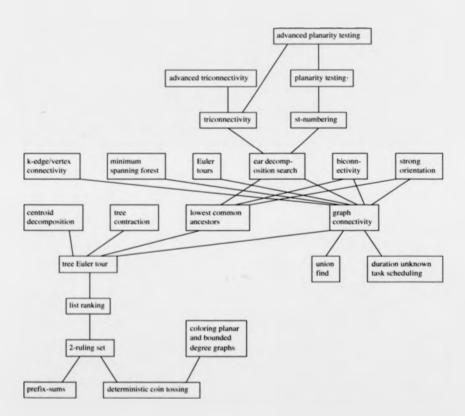

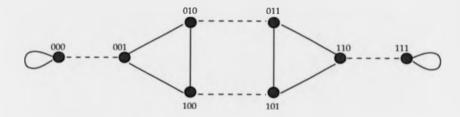

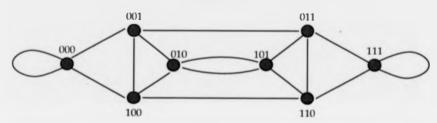

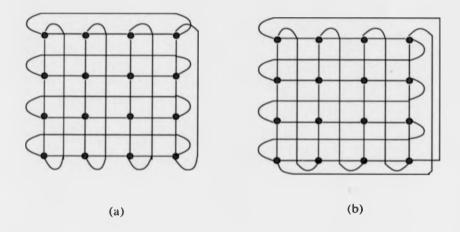

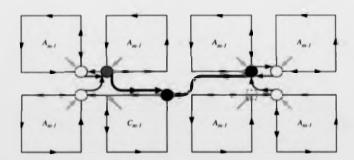

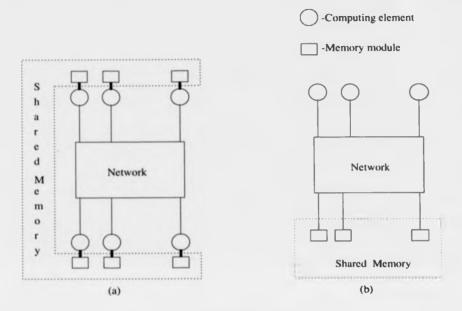

## 2.4 PRAM algorithmic tools

In this section we describe the algorithmic tools, known as *prefix computation* and *list ranking*, that have been found to be of wide use in the construction of many parallel algorithms. One can appreciate this from figure 2.2 [166], which illustrates how the solutions of some PRAM algorithms depend on the solutions of others. Such a diagram is an example of so-called *structural algorithmics*. Let  $P_1$  and  $P_2$  be the problems in figure 2.2 such that  $P_1$  is above  $P_2$ . If there is an edge between  $P_1$  and  $P_2$  then the NC algorithm that solves  $P_2$  is used to obtain an NC algorithm to solve  $P_1$ . Thus, if there is a path between  $P_1$  and  $P_2$  then all the solutions to the problems on the path are used to obtain an NC algorithm to solve  $P_1$ . As an example, the solution to the prefix sum problem is a subroutine in the solution to the list ranking problem, the solution to list ranking is a key subroutine to the so-called the Euler tour technique and so on.

### 2.4.1 Prefix computation

Given an array  $[x_0, x_1, \ldots, x_{n-1}]$  of n elements together with an associative operator \*, a prefix computation gives  $S_i = x_0 * x_1 * \cdots * x_i$ , for  $1 \le i \le n-1$ . There is a simple algorithm for performing prefix discovered by Ladner and Fisher [86]. The algorithm is perhaps easily understood with reference to the complete binary tree of the computation. Let n be a power of 2, otherwise we add a minimum number of dummy elements to achieve this. At the outset we store the n numbers at the leaves of the tree so that  $x_i$  is in the corresponding location of the i<sup>th</sup> leaf for  $0 \le i \le n-1$ . The leaves are numbered from 0 to n-1 from the left to the right. Levels are

Figure 2.2:

numbered from 0 to  $\log n$ , from the level of the leaves upwards. Let any node j of a complete binary tree cover the leaves from positions p to q (note if j is a leaf then p=q). Then let A(j) and B(j) be storage locations that will be used respectively to store the values of  $x_p*x_{p+1}*\cdots*x_q$  and  $x_0*x_2*\cdots*x_q$ . The following code performs the desired computation.

for level=1 to log n do

for  $all \ j \in level$ , in parallel do  $compute \ A(j)$   $B(root) \leftarrow A(root)$ for  $level = log \ n - 1$  to 0 do

for  $all \ j \in level$ , in parallel do  $compute \ B(j)$

At the end of computation  $x_1 * \cdots * x_j$  is stored in the corresponding location B(j) of the  $j^{th}$  leaf, for  $0 \le j \le n-1$ . For each node a processor can identify the level of the node and its children as in the computation of the sum of n numbers (see section 2.3.1). Moreover, the first phase of the computation from level 1 (one level above the leaves) to the root can be done as explained in section 2.3.1, by reading the values from left child and right child. In the second phase from the root to the leaves, B(i) for the node i can be computed as follows. If the node i is the right child then B(i) is A(i)'s parent), otherwise B(i) is (B(i)'s parent) \* (A(i)'s sibling)). The computation can be run in  $O(\log n)$  time on an EREW PRAM since there are no conflicts in memory accesses. At first it would seem that we need O(n) processors to achieve this time. Since the input is stored in an array as already described (i.e. in consecutive memory locations), we can easily achieve a optimal algorithm (i.e. the same time complexity with  $O(n/\log n)$  processors) using Brent's scheduling

principal as in section 2.3.4.

Given an array A of locations storing 0 or 1, the associated parity problem is to determine whether the number of 1s is even or odd in the array. This problem can be regarded as a special prefix computation problem. Performing such a computation on A will leave the result of the parity problem in the rightmost location of A. A lower bound of  $\Omega(\log n/\log\log n)$  time is known for the parity problem on a priority CRCW PRAM with a polynomial number of processors. To match this lower bound for the prefix computation, Cole and Vishkin [28] described an optimal algorithm (different from the one described above) which runs in time  $O(\log n/\log\log n)$  using  $n\log\log n/\log n$  processors on a CRCW PRAM.

The fact that the prefix-sums problem appears at the bottom of figure 2.2 is meant to convey the basic role of this problem. It appears in many guises. For example, consider compacting a sparse array. Given an array of n elements, many of which are zero, we wish to generate a new array only containing the non-zero elements in their original order. This problem can be solved by assigning a value 1 to the non-zero elements, and performing the prefix sums using arithmetic addition. Such a computation calculates, for each non-zero element of the array, the position that such a non-zero element would have in the new array.

#### 2.4.2 List ranking

Given a linked list, the list ranking problem is to calculate for each member of the list its relative position from the end of the list, i.e. its rank in the list. The importance of this problem was first identified by Wyllie [169]. An obvious solution to list ranking can be regarded as a prefix computation using addition of 1s within a pointer structure. A linked list is an alternative to an array in storing sequences of element in shared memory. In an array each element knows its address within the array whereas in a linked list an element does not know *a priori* its rank in the list.

Using the *pointer jumping* technique (as explained in section 2.3.2) we can solve the list ranking problem. Initially we set distance(k) = 1 for each element k except the last for which we set distance(k) = 0. The last element can be easily determined by looking at the pointer's address, s(i), because the last element uniquely points to itself. The algorithm is then described as follows [52].

repeat  $\lceil \log n \rceil$  times

for each element k in the list in parallel do

$s(k) \leftarrow s(s(k))$

if  $s(k) \neq s(s(k))$  then  $distance(k) \leftarrow distance(k) + distance(s(k))$

At the end of the computation distance(k) gives the rank of the element k in the list. By associating a processor with each element of the list we can solve the list ranking problem in  $O(\log n)$  time. However, the algorithm is not optimal, since the work of the algorithm is  $O(n \log n)$  and the sequential time to rank the list is O(n). In attempting to get an optimal algorithm for this problem using *Brent scheduling technique* as in the prefix computation we run into a problem. Because the elements are not initially indexed (as in an array) we can not assign processors to begin subcomputation at defined positions on the list.

A substantial amount of effort has been put into finding a optimal algorithm for the list ranking. The key step in one optimal algorithm is to cleverly splice out elements from the list so that  $O(n/\log n)$  elements remain in  $O(\log n)$  time with  $n/\log n$  processors [26]. Then we can solve the list ranking on the reduced list as described above taking  $O(\log n)$  time using  $n/\log n$  processors. The original list then reconstructed by reinserting the elements that were spliced out. This step can also be done in  $O(\log n)$  time with  $n/\log n$  processors. The total work of this algorithm is O(n) which is the best sequential time to rank the list.

Wyllie conjectured that it is impossible to find an optimal parallel algorithm for this problem [169]. Cole and Vishkin [26] were able to invalidate Wyllie's conjecture by describing all details of the above algorithm which runs on an an EREW PRAM. The drawback to their algorithm is that it is complicated and has very large constant factors, and they rely on an expander graph construction to solve a scheduling problem that arises. Anderson and Miller [8] gave an another optimal algorithm that runs in  $O(\log n)$  time and uses  $n/\log n$  processors on an EREW PRAM, which is much simpler and has reasonable constant factors. Moreover, this algorithm does not rely on an expander graph construction, although it is still fairly intricate for practical purposes.

## 2.5 Graph algorithms

Graphs play an important role in solving real-world problems. Specifically they play a major role in important problems in combinatorial optimisation. For example, in graph colouring we assign colours to a graph such that no two adjacent edges or vertices have the same colour. Edge colouring and vertex colouring can be used to solve time-tabling problems. Another important graph problem is to decide whether a given graph is planar. For example, in the layout of printed circuits one is interested in knowing if a particular electrical network is planar. Other important problems are concerned with the so-called connectivity of the graph in question. A graph is said to be connected if there is a path between any two vertices. A graph is k-vertex (or edge) connected if k is the minimum number of vertices (or edges) whose removal will disconnect the graph. If we think of a graph as representing a communication network, the vertex connectivity (or edge connectivity) becomes the smallest number of communication stations (or communication links) whose breakdown would jeopardise communication in the system. The higher the vertex connectivity and edge connectivity, the more reliable the network.

The design of efficient parallel algorithms for graph problems has presented a challenge since traditional sequential graph search techniques have proved not readily to admit parallelisation. Sequential optimal algorithms for many graph problems commonly use one of two methods to search a graph: depth-first search (dfs) or breadth-first search (bfs) [49]. At present, neither of these methods has an efficient parallel algorithm, and the most useful of these methods (dfs) is P-complete. Thus new tools are needed to replace dfs or bfs. One such tool is the process of ear decomposition search (described in section 2.5.3). We need to avoid dfs or bfs in the parallel algorithm. For example, computing connected components is often considered a basic problem and the best sequential algorithm for this problem uses dfs. Two nodes of a graph are in the same component if there is a path from one to another in the graph. An efficient parallel algorithm for connected components on a

CRCW PRAM was described in [70, 73, 144] and the algorithm avoids dfs. Another example is concerned with finding a topological ordering of directed acyclic graph, i.e. assigning a number to each of the vertices such that there is no path from a vertex to lower numbered one. This can easily be done in linear time sequentially, but the algorithm does not obviously lend itself to parallelism. Kucera [85] described an *NC* algorithm for this problem using the transitive closure technique (as explained in section 2.5.4).

The following sections briefly describe algorithmic techniques which can be used as building blocks for graph algorithms. These exemplify new paradigms for parallel algorithm design.

#### 2.5.1 Euler tour on trees

The construction of a rooted spanning tree, and the computation of various tree functions (for example, preorder and postorder numbering of vertices in the tree, distances of each vertex from the root of the tree, and the number of descendants of each vertex in the tree) are common features in many efficient parallel graph algorithms. It is often the case for particular algorithms that polylogarithmic efficiency is obtained simply because the algorithm has been contrived to perform certain functions on a tree. These functions can be computed by finding a so-called Euler tour of the tree and performing list ranking on the Euler tour. The Euler tour of a tree reduces the computation of many tree problems to some form of list ranking. The Euler tour technique was introduced by Tarjan and Vishkin [152].

An Eulerian circuit is a circuit in a graph which traverses every edge precisely once.

Given an undirected and unrooted tree, by replacing each edge of the tree by two anti-parallel directed edges an Eulerian circuit (or Euler tour) can be constructed optimally by a clever use of the adjacency lists of the tree vertices and the optimal list ranking algorithm (see for example [52], pages 21-24). If we break the Eulerian tour at an arbitrary edge, fixing some edge (i, j) as a first edge of the list so formed, then it is easy to see that the tour represents a depth-first traversal of the tree with i as the root. Tarjan and Vishkin called such a list a traversal list of the tree. The parent-child relation, preorder and postorder numbering, number of descendants of each vertex can be determined by ranking the traversal list using appropriate weights [152]. Hence, all these tree functions can be computed in  $O(\log n)$  time using  $O(n/\log n)$  processors on an EREW PRAM.

We can also use the traversal list to compute the distance of each vertex from the root of the tree. This proved to be key subroutine used to compute the biconnected components of a graph [152]. A graph is biconnected if there is no vertex whose removal leaves the graph disconnected. Using the Euler tour in trees, Schieber and Vishkin [140] solved another problem on trees, that of finding the lowest common ancestor of each pair of vertices. This was then used as part of optimal algorithms for computing strong orientations of sparse graphs. Given an undirected graph, the strong orientation problem is to assign a direction to each edge so that the resulting graph is strongly connected. A graph is strongly connected if for any pair of vertices u and v, there exist directed paths from u to v and from v to u.

#### 2.5.2 Tree contraction

Tree contraction is an efficient parallel method of evaluating an expression given the associated tree. The method transforms the input tree in stages using local operations in such a way that an n-node tree is contracted into a single node by local contractions in  $O(\log n)$  stages, each of which takes constant time on a PRAM. Optimal algorithms for tree contraction are described by Gibbons and Rytter [53] and others in [29, 47], that run in  $O(\log n)$  time on an EREW PRAM.

In addition to expression evaluation, tree contraction has been applied to a wide variety of problems. The technique easily generalises to arbitrary (nonbinary) trees, and has been used to drive parallel algorithms for various graph-theoretic computations on trees such as maximum matching, minimum vertex cover and maximum independent set [62]. Other applications of tree contraction can be found in [105].

#### 2.5.3 Ear decomposition

An *Ear decomposition* of a graph is an ordered collection simple paths called *ears*, such that the end points of each ear appear in previous ears but such that the interior vertices of each ear appear for the first time in that ear. *Ear decomposition search* has been developed for undirected graphs and was suggested as a replacement for dfs to search undirected graphs. This method provides efficient parallel algorithms for several graph problems on the PRAM model. This can be seen in figure 2.2. Several of these parallel algorithms convert to entirely new and optimal sequential

algorithms. This is an example of a new emerging discipline enriching an existing one. Surveys of these results can be found in [42, 76, 128, 166].

#### 2.5.4 Matrix computations

Matrix computation provides a fundamental tool for placing many graph problems in NC, using the strategy of repeated matrix multiplication. Let  $A=(a_{ij})$  and  $B=(b_{ij})$  be  $n\times n$  boolean matrices. Let C=AB be the product of A and B; that is, the (i,j) entry of C is defined by  $c_{ij}=\bigoplus_{k=0}^n(a_{ik}\otimes b_{kj})$ , where  $\oplus$  and  $\otimes$  are two binary operators. This can be done in  $O(\log n)$  time using  $n^{2\cdot376}$  processors on a CRCW PRAM [35]. However, the algorithm is of theoretical interest only because it quite complicated and the big-oh notation hides a large constant factor in the running time, and the algebraic structure with the binary operates  $\oplus$  and  $\otimes$  requires to be a ring. The standard method of multiplication in  $O(\log n)$  time with  $n^4$  processors on a EREW PRAM, still remains the algorithm of practical choice.

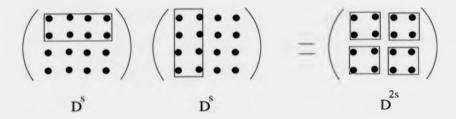

The transitive closure of A (denoted by  $A^*$ ) is  $\bigoplus_{k=0}^{\infty} A^k$ , where  $A^0 = I$  (identity matrix) and  $A^k = A^{k-1} \otimes A$  for  $k \ge 1$ . Let matrix D be the matrix  $I \oplus A$ . It can be shown that  $A^* = D^{2\lceil \log_2 n \rceil}$  [68]. Hence, the straightforward method of computing the transitive closure of an  $n \times n$  matrix is to compute the  $2\lceil \log_2 n \rceil^{th}$  power of the matrix D using repeated squaring as we explained in section 2.3.2.

We can solve several (directed) graph problems by taking powers of the *adjacency* matrix as in the transitive closure problem. For a given graph G(V, E) of n vertices, the adjacency matrix of the graph is the  $n \times n$  matrix,  $M = (m_{ij})$  (say) such that

$$m_{ij} = \begin{cases} 1 & \text{if edge } (i,j) \in E \\ 0 & \text{otherwise} \end{cases}$$

The transitive closure of a graph G(V,E) is the graph (denoted by  $G^*$ ) with nodes V and edges  $E^* = \{(i,j) \mid \text{there is path from } i \text{ to } j \text{ in } G\}$ . Let  $M^*$  be the adjacency matrix of  $G^*$ . To find  $M^*$  it is sufficient to compute the transitive closure of M here  $\oplus$  and  $\otimes$  are replaced by logical operators or and and respectively. Hence, by this computation we can find whether one vertex is reachable from another in a directed graph.

As a second example consider finding the shortest path between each pair of vertices in the weighted graph. Here the operators  $\oplus$  and  $\otimes$  are replaced by **min** and + respectively [85], and the input matrix is the edge-weight matrix (i.e.  $m_{ij}$  is weight of the edge (i,j)).

Several other problems on directed graphs can be solved using this strategy of repeated matrix multiplication. These include topological sorting and strong components [128].

# **Chapter 3**

# **Parallel Approximation Algorithm**

A major part of this chapter is the description of an efficient parallel approximation algorithm for finding minimum weight perfect matching in graphs. This represents joint work with A.M. Gibbons and N. W. Holloway, which was published in the proceedings of the 19<sup>th</sup> International Workshop on Graph Theoretic Concepts in Computer Science [136]. Preliminary sections of the chapter provide essential background material.

## 3.1 Introduction

In sequential complexity theory, it has been the consensus view that the so-called *NP-complete* problems (which includes literally hundreds of computationally important problems, many in the area of combinatorial optimisation) are computationally intractable [3, 46, 49]. Although there is no proof of this fact, so much effort has been fruitlessly expended in the search for polynomial time algorithms that

most theoreticians now believe that none exist. The absence of polynomial time algorithms for the *NP-complete* problems has spawned the development of many approximation algorithms which run in polynomial time but which provide an approximation (within guaranteed bounds) to the required result [46]. In a similar vein, *NC* approximation algorithms for *P-complete* problems have been developed recently [102, 141].

For many problems in P, not much is known concerning their parallel complexity. For example, although the problem of constructing a minimum weight perfect matching is known to be in RNC it is not known if it belongs to NC. A problem is said to belong to the class RNC if the problem can be solved in polylogarithmic parallel time by a randomised parallel algorithm, using a polynomially bounded number of processors. A matching in a graph is a set of edges M, so that no two elements of M have a common vertex. If every vertex of a graph is an end-point of some element of M then M is a perfect matching. Not every graph contains a perfect matching. Given a weighted graph, a minimum-weight perfect matching is a perfect matching whose sum of edge weights is a minimum.

In this chapter an NC approximation algorithm is described for finding a minimumweight perfect matchings in complete weighted graphs satisfying the *triangle in*equality. In a graph satisfying the triangle inequality, the weight of any single edge forming a triangle with two other edges is less than or equal to the sum of the weights of these other two edges. Such an inequality is satisfied in many natural problems. The problem that we address is an important sub-task for many problems of combinatorial optimisation and features, for example, in solutions to Chinese Postman Problems (CPP) and in Approximations to the Traveling Salesman Problem (TSP) [49]. Given a graph (directed or undirected) and a weight for each edge, the CPP is the problem of finding a circuit of minimum total weight which contains each edge at least once. The TSP requires to find a minimum weight circuit of a weighted graph which visits every vertex at least once.

## 3.2 Performance ratios of approximation algorithms

We can measure the performance of an approximation algorithm by comparing the optimal solution and the (approximate) solution produced by the approximation algorithm [46]. If Q is an optimisation problem and I a particular instance of that problem, then the performance ratio of an approximation algorithm A on I is given by  $R_A(I)$  defined as follows:

$$R_A(I) = \begin{cases} \frac{A(I)}{Op(I)} & \text{if } Q \text{ is a minimisation problem} \\ \frac{Op(I)}{A(I)} & \text{if } Q \text{ is a maximisation problem} \end{cases}$$

Here A(I) and Op(I) are respectively the approximate solution produced by the algorithm A on I and the optimal solution for I. It is clear from this definition that  $R_A(I) \geq 1$  always. However, a useful performance ratio is a ratio that is known never to exceed some constrained value for any instance of the problem. Let  $R_A$  denotes the worst-case performance ratio, for all problem instances. Then generally we require to prove that  $R_A$  is always constrained for any input.

# 3.3 Minimum weight perfect matching

As [88] has emphasised, matching problems have played an important role in the foundations of sequential algorithmic complexity theory. This is because they are important problems that arise in many guises that can be solved in polynomial time, but for which all naive algorithms take exponential time. In fact, it was in Edmonds' celebrated paper [41] on matching algorithms that the connection between *tractable problems* and *polynomial time solvable problems* was first made. It is likely that matching problems will play a similar role in the development of parallel algorithmic complexity theory.

There are practically no extant algorithms placing matching problems in NC with the notable exception of the maximal matching problem [67] and certain algorithms for special classes of graphs. The class of problems which can be solved in polylogarithmic expected time using a polynomial number of processors is called RNC (see, for example, [148]and section 2.5.5. of [88]). Most matching problems can be solved in parallel using randomness [77, 110] and so belong to the class RNC. It has been stated [88] that whether a modern definition of a tractable problem in parallel computation is one can that can be solved rapidly with randomisation or one that can be solved rapidly without randomisation may ultimately depend upon whether fast parallel algorithms for matching require randomisation.

Even with restrictions on the graph such as completeness and triangle inequality satisfaction, the problem seems very difficult to place in NC. We have therefore addressed the problem of finding an NC approximation algorithm. Specifically, we describe an NC approximation algorithm for the minimum-weight perfect matching

problem for graphs satisfying triangle inequality for which  $R_A=2\log_3 n$ . This is the first such deterministic algorithm with a sub-linear performance ratio. Previously, it was known (see [148]) that there is an NC approximation algorithm for the maximum- (equivalently, minimum-) weight perfect matching problem such that  $R_A=n$ .

Karp, Upfal and Wigderson [77] described an RNC algorithm for the minimum weight perfect matching problem, which runs in  $O(\log n \log^2(Wn))$  time (after the improvements of [45]) using  $O(Wn^{3.5})$  processors, where W is the maximum weight of any edge. A faster RNC algorithm was obtained in [110] which runs  $O(\log^2 n)$  time using  $O(mWn^{3.5})$  processors, where m is the number of edges. These algorithms are in RNC only if W is relatively small (that is,  $W = n^{O(1)}$ ).

Although finding a NC algorithm for minimum weight perfect matching seems to be hard, there are NC algorithms for finding a perfect matching in special classes of unweighted graphs. Examples are dense graphs [37], bipartite graphs with a bounded permanent [60], complements of transitive oriental graphs [63] and line graphs [111]. However, there is no known deterministic NC algorithm for minimum weight perfect matching for complete graphs. The best known deterministic parallel algorithm for complete graphs runs in  $O(n^3/p + n^2 \log n)$  polynomial time using p ( $\leq n$ ) processors [115].

An exact solution for minimum weight perfect matching can be computed in  $O(n^3)$  sequential time by the intricate algorithm of Edmonds [41] and this provides a target for the work measure of parallel algorithms. There are sequential approximation algorithms for special graphs [66, 121, 137, 151]. The algorithms of [121] find an

approximate minimum-weight perfect matching for graphs satisfying the triangle inequality. However, it is not clear that these algorithms can be effectively parallelised. Even if they could be, they would provide a much more intricate solution to the problem solved in the following section. One of the virtues of the algorithm described here is its simplicity.

# 3.4 Approximate minimum weight perfect matching in a complete weighted graph

We start by providing an overview of the algorithm whose input is a complete weighted graph G=(V,E) with edge set E and vertex set V, where |V|=n and n is even. The first part of the algorithm concerns the construction of a graph F=(V,E') where  $E'\subset E$ , thus F may be obtained from E by a set of edge deletions. The essential properties of F will be that each component contains an even number of vertices and the total sum of its edge weights will be less than  $(2\log_3 n)M$ , where M is the sum of edge weights of a minimum weight perfect matching in G. The second part of the algorithm first constructs, for each component of F, a Hamiltonian circuit which will be even length. The sum of the edge weights over all such circuits is less than  $(4\log_3 n)M$ . A perfect matching in G is then obtained by taking alternate edges on each such circuit and such that (of the two possibilities presented by each circuit) the lightest weight possibility is chosen. The weight, M', of the perfect matching constructed in this way satisfies the inequality:  $M' \leq 2M\log_3 n$ . We now consider the two parts of the algorithm in more detail.

Afterwards we consider precise details of its parallel execution, justify the bounds on the approximation and consider the complexity parameters.

#### The Algorithm

#### 1. Construction of F.

The construction is performed over at most  $\log_3 n$  phases. At the beginning of each phase, the vertices of G have been partitioned into disjoint subsets whose union is V. Each such subset is called a *super-vertex*. If such a super-vertex contains an even number of vertices of G, then it is an *even* super-vertex, otherwise it is an *odd* super-vertex. Before the first phase, every vertex of G is a super-vertex.

Now, the action of each phase is as follows. In the  $i^{th}$  phase, first construct the weighted complete graph  $G_i$  which is the graph whose vertex set is the set of supervertices and the edge  $(V_j, V_k)$  between super-vertices  $V_j$  and  $V_k$  has weight equal to the weight of the lightest edge in G that connects a vertex in  $V_j$  to a vertex in  $V_k$ . Note that  $G_i$  does not hold the triangle inequality. Now construct the complete weighted graph  $G_i'$  from  $G_i$  as follows. The vertices of  $G_i'$  are the odd super-vertices of  $G_i$  and the weight of the edge  $(V_j', V_k')$  between the super-vertices  $V_j'$  and  $V_k'$  of  $G_i'$  is the weight (that is, the sum of the weights of the edges) of a shortest path between these super-vertices in  $G_i$ . We now construct a weighted digraph  $G_i''$ , whose underlying graph (that is, the graph obtained by removing the edge orientations) is a subgraph of  $G_i'$ . The vertex set of  $G_i''$  is the vertex set of  $G_i''$ . We choose precisely one edge to be directed from each vertex of  $G_i''$ . If e is an edge of least weight with such a vertex as an end-point in  $G_i'$ , then the edge chosen from the vertex in  $G_i''$  is directed towards the vertex corresponding to the other end-point of e in  $G_i''$ . This directed

edge has weight equal to the weight of  $\epsilon$ . Each such directed edge of G'' corresponds to a path and so to a set of subset of edges (the edges on the path) of  $G_i$  and, for all such directed edges, we now add to F these corresponding subsets of edges. As we shall see later (Lemma 3.4.1), the sum of weights of these edges does not exceed  $2M \log_3 n$ . To complete the description of what happens within each phase, it remains to say how the super-vertices are constructed for the next phase. Those super-vertices belonging to the same component of  $G''_i$  are coalesced into larger super-vertices. Provided all the super-vertices are not even super-vertices, we enter another phase of the construction of F.

#### 2. Construction of the matching from F

The input to this stage of the algorithm is the graph F. We are interested in the partition of the vertices of G that is implied by the components of F. Each component  $F_i$  of F has an even number of vertices of G. We find a minimum weight spanning forest of F, that is, a minimum weight spanning tree  $T_i$  for each  $F_i$ . For each  $T_i$  we then find a preorder numbering of the vertices. Now, for each  $T_i$ , such a numbering defines an even-length circuit in G obtained by visiting the vertices in the order of their pre-order indices. For each such circuit, we take alternative edges (of the two possible subsets that can be chosen in this way, we choose that of the smallest weight) to be edges of the approximate minimum-weight perfect matching. The total weight (Lemma 3.4.2) of edges chosen to belong to the approximate weight perfect matching is less than  $2M \log_2 n$

#### end of the algorithm

#### 3.4.1 Validity of the approximation ratio claim

We now prove that the total weight of the edges of the graph F is less than  $2M \log_3 n$ . First notice that within each iterated phase employed in the construction of F, each odd super-vertex is coalesced with at least one other so that the number of odd super-vertices reduces by a factor of at least two within each phase. However, we continue to iterate only if there are odd super-vertices remaining and this only happens if at least three odd super-vertices are coalesced. Thus  $\log_3 n$  repetitions are sufficient to remove all the odd super-vertices (notice that by an elementary theorem of graph theory, there will always be an even number of odd super-vertices). All we now need for our proof is the following Lemma.

**Lemma 3.4.1** The sum of the edge weights of the edges added to F in each iterated phase of its construction is less than or equal to 2M.

**Proof** In any of the iterated phases used in the construction of F, the edges added to F are those belonging, for every odd super-vertex, to a shortest path from such a super-vertex to another. We first show that, in  $G_i$ , there exists a path from any odd super-vertex to some other odd super-vertex only using edges of a minimum-weight perfect matching. Consider then any odd super-vertex V of  $G_i$ . Now because there are an odd number of vertices of G in V, not all these vertices can be matched by edges of a minimum-weight perfect matching of G which connect pairs of vertices contained in V. There must therefore be an edge of a minimum-weight perfect matching connecting V to some other super-vertex that is a vertex of  $G_i$ . This is the first edge of the path whose existence we wish to prove. If this edge takes us to a

vertex corresponding to an odd super-vertex then we have finished. If it takes us to a even super-vertex, then it will match one of its constituent vertices and there will be an odd number remaining to be matched by a minimum-weight perfect matching. The implication is that there is another edge from this vertex corresponding to an even super-vertex which takes us on to yet another vertex of  $G_i$ . Continuing in this way, we see that there must exist a path from every vertex of  $G_i$  corresponding to an odd super-vertex to a similar vertex and that in  $G_i$  such a path only uses edges of a minimum-weight perfect matching. Notice, of course, that any two such paths may have edges in common. Let  $S_k$  be the sub-set of edges defining the shortest path from vertex k (which corresponds to some odd super-vertex) to some other similar vertex which uses edges of a minimum-weight perfect matching only and let  $S'_k$  be the subset defining the path from vertex k to some odd super-vertex as constructed by the algorithm.

We need to obtain a worst case bound on the weight of the *union* of the  $S_k'$  in terms of the weight of the union of the  $S_k$ . This is because we already have a worst case bound on the weight of the union of the  $S_k$  provided by M, the weight of a minimum-weight perfect matching of G. Notice that for all k,  $weight(S_k') \leq weight(S_k)$  because the algorithm chooses minimum-weight paths; however, it does not follow that the weight of the *union* of the  $S_k'$  will be less than the weight of the *union* of the  $S_k$  because there may be an entirely different sharing of edges between paths in the two cases. To obtain a worst bound, we need to consider the cases in which the  $S_k'$  have a minimum union and the  $S_k$  have a maximum union. By maximum (minimum) union we mean that the number of shared edges of paths between the odd super-vertices is maximum(minimum). In the latter case, notice that no two of the  $S_k$  may share

edges whose combined weight is more than half the weight of the lightest set of the two, otherwise the  $S_k$  would not be shortest paths of their type. The situation of a maximum weight union of the  $S_k$  corresponds to every path sharing half its weight with every other path. The case of minimising the weight of the union of edges of the  $S'_k$  is essentially that of practically no sharing (although the detail is a little more subtle, this observation suffices to achieve the bound we seek). Thus, the weight of the union of the  $S'_k$  is bounded, in the worst case, by twice the weight the union of the  $S_k$ , but the weight of the union of the  $S_k$  is bounded by M and so the lemma follows.

We have proved that the sum of the weights of the edges of F is bounded by  $2M \log_3 n$ . The following Lemma provides a similar bound on the approximation ratio of the algorithm.

**Lemma 3.4.2** The weight, M', of the perfect matching found by the algorithm is bounded as follows:

$$M' \leq 2M \log_3 n$$

where, M is the weight of a minimum-weight perfect matching and n is the number of nodes of G. The input G is a complete weighted graph satisfying the triangle inequality.

**Proof** The total weight of the edges of the graph F is, by Lemma 3.4.1, bounded by  $2M \log_3 n$ . For each component  $F_i$  of F, the total weight of the edges of  $T_i$  is less than the total weight of the edges of  $F_i$ , because  $T_i$  is a minimum weight spanning tree of  $F_i$ . Hence, the total weight of all the trees edges is less than  $2M \log_3 n$ .

For each  $T_i$ , consider the standard *twice-around-the-spanning-tree* circuit (see, for example, [49]),  $C_i$ , obtained by visiting the nodes in pre-order and making shortcuts to avoid re-visiting nodes that have already been visited. Such short-cuts are always possible because G is complete and they will be *short-cuts* because we have triangle-inequality holding. Thus, for each i, the weight of  $C_i$  is bounded by twice the weight of  $T_i$ 's edges. However, the weight of the edges chosen for the matching from  $C_i$  constitute at most half the weight of the circuit and so at most weight of  $T_i$ . Thus, over all such circuits, we choose a weight of edges for the matching which is less than or equal to the weight of F and the lemma is proved.

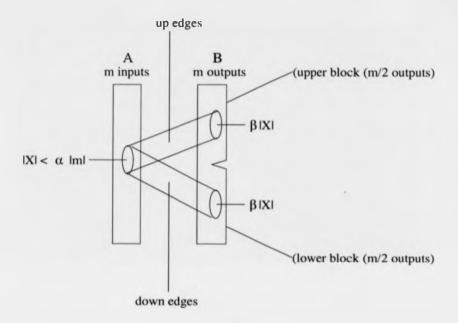

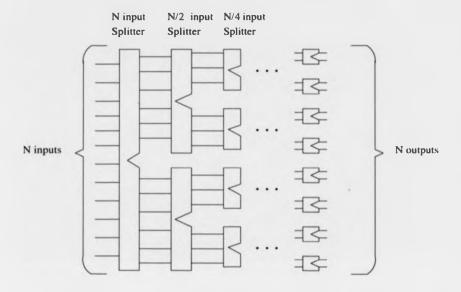

#### 3.4.2 Parallel execution and complexity of the algorithm

Consider first the construction of the graph F. There are  $\log_3 n$  phases and within each, the activities dominating the computation time are the construction of all shortest paths and the coalescing of super-vertices which can be achieved by an algorithm for finding connected components of a graph. As we cite later, there are well known polylogarithmic time parallel algorithms performing these tasks using a polynomial numbers of processors. Other tasks are trivially solved by more efficient parallel algorithms. Thus, we may express the time-complexity for constructing F as  $O((SP(n) + CC(n)) \log n)$  using  $max(p_{SP(n)} + p_{CC(n)})$  processors, where SP(n) is the parallel time for the all shortest paths problem using  $p_{SP(n)}$  and CC(n) is the parallel time for the connected components problem using  $p_{CC(n)}$  processors. Now consider the construction of the approximate minimum-weight perfect matching from the graph F. The dominating activity from the point of view of the