A Thesis Submitted for the Degree of PhD at the University of Warwick

**Permanent WRAP URL:**

http://wrap.warwick.ac.uk/147144

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Fabrication and Analysis of 4H-SiC Diodes

Yeganeh Bonyadi

Dissertation Submitted for the Degree of  $Doctor\ of\ Philosophy$

School of Engineering

October 2019

## Content

| List o | f Figu  | res                                           | v          |

|--------|---------|-----------------------------------------------|------------|

| List o | of Tabl | es                                            | xii        |

| Decla  | ration  | 1                                             | xiii       |

| Ackno  | owledg  | gement                                        | xiv        |

| Publi  | cation  | List                                          | XV         |

| Abstr  | act     |                                               | xvi        |

| List o | of Abbr | reviations                                    | xvii       |

| 1      | Intro   | oduction                                      | 1          |

|        | 1.1     | Introduction                                  | 1          |

|        | 1.2     | Background and Motivation                     | 3          |

|        | 1.3     | Contribution of Knowledge                     | 5          |

|        | 1.4     | Thesis Outline                                | 7          |

| 2      | Pow     | er Electronic Devices and Silicon Carbide     | 10         |

|        | 2.1     | Background                                    | 10         |

|        | 2.2     | Requirements for Power Electronics Device     | es13       |

|        | 2.3     | Silicon Carbide for Power Electronics         | 16         |

|        | 2.4     | Crystal Structure and Polytypes of Silicon    | Carbide17  |

|        | 2.5     | Physical & Electrical Properties of Silicon ( | Carbide21  |

|        | 2.6     | Bulk Growth of Silicon Carbide and Its Ch     | allenges29 |

|        | 2.7     | Extended Defects in SiC                       | 32         |

|        | 2.      | 7.1 Dislocations in SiC Boule Crystal         | 34         |

|        | 2.8     | Point Defects                                 | 37         |

|        | 2.8     | 8.1 Major Deep Levels in SiC Epitaxial La     | yers37     |

|        | 2.9     | Present Status of Silicon Carbide Power De    | evices42   |

|        | 2.9     | 9.1 Schottky Barrier Diodes (SBDs)            | 43         |

|        | 2.9     | 9.2 Junction Barrier Schottky Diodes (JBS     | 3)46       |

|        | 2.9     | 9.3 Merged PiN-Schottky Diodes (MPS)          | 47         |

|        | 2.9     | 9.4 PiN Diodes                                | 50         |

| 3      | Theo    | ory of High Voltage Power Diodes              | 54         |

|        | 3.1     | Power Diode Operation Principle               | 54         |

|          | 3.2  | P-N   | Junction                                                                                     | 58  |

|----------|------|-------|----------------------------------------------------------------------------------------------|-----|

|          | 3.3  | Sch   | ottky Diode                                                                                  | 63  |

|          | 3.3  | 3.1   | Current Transport Processes                                                                  | 67  |

|          | 3.3  | 3.2   | Schottky Diode Operation                                                                     | 71  |

|          | 3.4  | PiN   | V Diode                                                                                      | 76  |

| 4        | 4H-S | SiC D | Device Fabrication Technology                                                                | 85  |

|          | 4.1  | 4H    | -SiC Processing Techniques                                                                   | 85  |

|          | 4.   | 1.1   | SiC Wafer Dicing                                                                             | 86  |

|          | 4.   | 1.2   | SiC Wafer Surface Cleaning Process                                                           | 87  |

|          | 4.   | 1.3   | Surface Passivation                                                                          | 89  |

|          | 4.   | 1.4   | 4H-SiC Oxidation Techniques                                                                  | 90  |

|          | 4.   | 1.5   | Etching of 4H-SiC                                                                            | 99  |

|          | 4.   | 1.6   | Ohmic Contacts to 4H-SiC                                                                     | 100 |

|          | 4.2  | Dev   | vice Packaging Process                                                                       | 103 |

| 5        |      |       | risation Techniques for High Voltage 4H-SiC PiN and Schottky                                 |     |

| Dio      | des  |       |                                                                                              |     |

|          | 5.1  | Ele   | ctrical Characterisation                                                                     | 115 |

|          | 5.   | 1.1   | Forward I-V Measurements                                                                     |     |

|          | 5.   | 1.2   | I-V Measurement at Varying Temperature                                                       | 116 |

|          | 5.   | 1.3   | Reverse Breakdown Characterisation                                                           | 120 |

|          | 5.   | 1.4   | Clamped Inductive Switching Test                                                             | 122 |

|          | 5.2  | Phy   | ysical Characterisation                                                                      | 124 |

|          | 5.2  | 2.1   | Scanning Electron Microscopy                                                                 | 124 |

|          | 5.2  | 2.2   | Transmission Electron Microscopy                                                             | 128 |

|          | 5.2  | 2.3   | Atomic Force Microscopy                                                                      | 137 |

|          | 5.2  | 2.4   | Photoluminescence                                                                            | 139 |

| 6<br>Per |      | _     | act of Triangular Defects on Electrical Characteristics and Switch of 3.3kV 4H-SiC PiN Diode | _   |

|          | 6.1  | Bac   | ekground                                                                                     | 142 |

|          | 6.2  | Exp   | perimental Details and Results                                                               | 143 |

|          | 6.5  | 2.1   | Material Characteristics                                                                     | 144 |

|          | 6.5  | 2.2   | Scanning Electron Microscopy                                                                 | 147 |

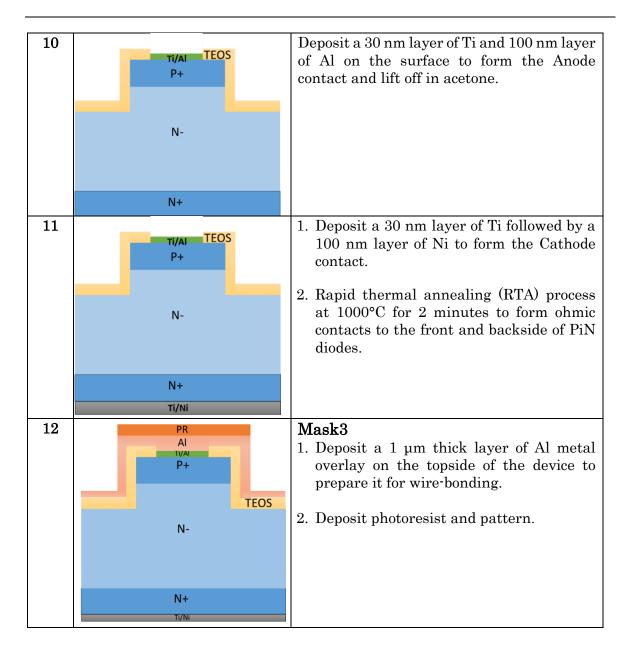

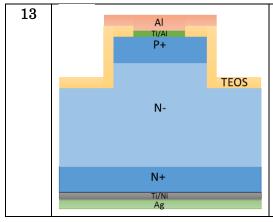

|           | 6.2          | .3 Device Fabrication                                                                      | 151         |

|-----------|--------------|--------------------------------------------------------------------------------------------|-------------|

|           | 6.3          | Electrical Results and Discussion                                                          | 156         |

|           | 6.3          | .1 I-V Characteristics                                                                     | 157         |

|           | 6.3          | .2 Clamped Inductive Switching Test                                                        | 173         |

|           | 6.4<br>Micro | Verification of the Electrical Results Using Transmission Electron                         | 178         |

|           | 6.5          | Summary                                                                                    | 184         |

| 7<br>Oxio |              | me Enhancement of 4H-SiC PiN Diodes Using High Temperature Treatment                       | 188         |

|           | 7.1          | Background                                                                                 | 189         |

|           | 7.2          | Device Fabrication                                                                         | 194         |

|           | 7.3          | Forward and Reverse I-V Characterisation Results                                           | 196         |

|           | 7.4          | Reverse Recovery Behaviour of PiN Diodes                                                   | 204         |

|           | 7.5          | Clamped Inductive Switching Characterisation Results                                       | 211         |

|           | 7.6          | Summary                                                                                    | 218         |

| 8<br>Met  |              | vestigation into the Impact of Surface Passivation Techniques Using niconductor Interfaces | .222        |

|           | 8.1          | Background                                                                                 | 223         |

|           | 8.2          | Experimental Details                                                                       | 225         |

|           | 8.2          | .1 Device Fabrication                                                                      | 226         |

|           | 8.3          | Results and Discussion                                                                     | 231         |

|           | 8.3          | .1 Electrical Characterisation                                                             | 231         |

|           | 8.3          | .2 Inhomogeneity of the Diodes                                                             | 240         |

|           | 8.3          | .3 Physical Characterisation                                                               | 246         |

|           | 8.4          | Summary                                                                                    | 262         |

| 9         | Conc         | usion and Further Work                                                                     | 265         |

|           | 9.1          | Conclusion                                                                                 | 265         |

|           | 9.2          | Suggestions for Future Work                                                                | 273         |

| 10        | Appe         | ndix A                                                                                     | 276         |

|           | Alter        | native SiC Schottky Devices                                                                | 276         |

| 11        | Appe         | ndix B                                                                                     | 282         |

|           | Deriv        | ration of Capacitance-Voltage Equations                                                    | 282         |

| 10        |              | 1: 0                                                                                       | 00 <b>-</b> |

| Carrier Recombination and Generation | 287 |

|--------------------------------------|-----|

| References                           | 291 |

## List of Figures

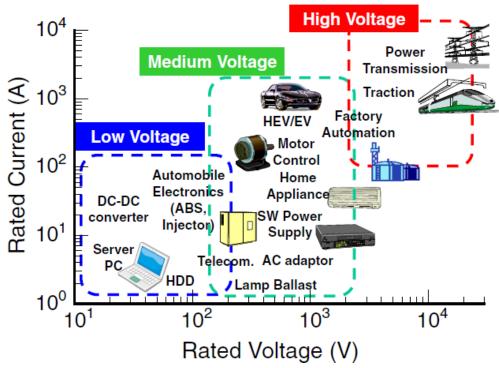

| Figure 1-1: Main application area of power electronic devices as a function of rated          |

|-----------------------------------------------------------------------------------------------|

| voltage [1]3                                                                                  |

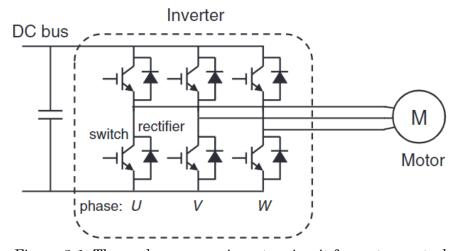

| Figure 2-1: Three-phase power inverter circuit for motor control13                            |

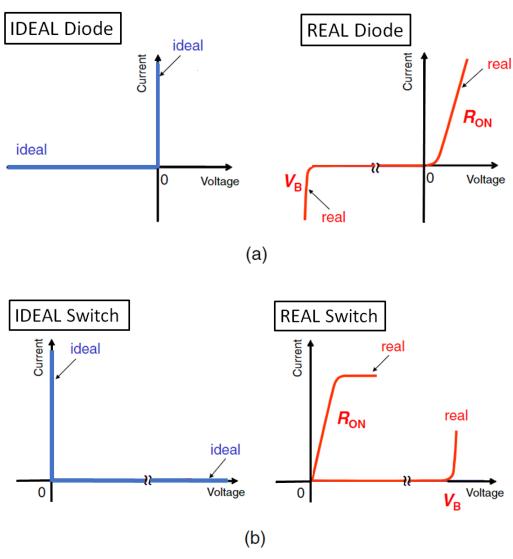

| Figure 2-2: Current–voltage characteristics of (a) power diode and (b) power switching        |

| device, showing the comparison between the ideal and real I-V characteristics15               |

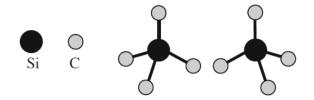

| Figure 2-3: Two types of tetrahedrons creating the basis of all SiC crystals where each       |

| Si atom in the tetrahedron is covalently bonded to four adjacent C atoms. Each type           |

| must be rotated around its c-axis (vertical here) by 180° to obtain the other type18          |

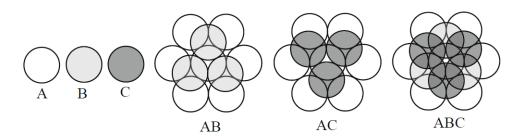

| Figure 2-4: In the hexagonal packing system, the Si-C pairs can reside in three               |

| different locations labelled A, B, and C18                                                    |

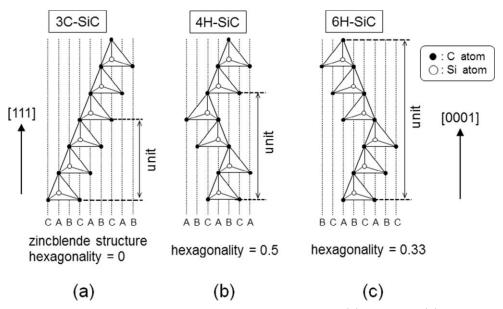

| Figure 2-5: Three most common polytypes of SiC (a) 3C-SiC, (b) 4H-SiC and (c) 6H-             |

| SiC where the c-axis denotes the stacking direction. The letters A, B, and C refer to         |

| the three potential locations of a closely-packed structure. Si and C atoms are               |

| indicated by open [28]19                                                                      |

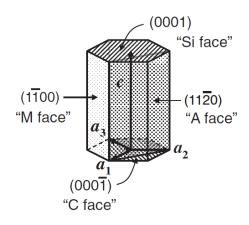

| Figure 2-6: Hexagonal cell of SiC showing the major crystal faces labelled as (0001),         |

| (0001 <sup>¬</sup> ), (112 <sup>¬</sup> 0), and (11 <sup>¬</sup> 00)20                        |

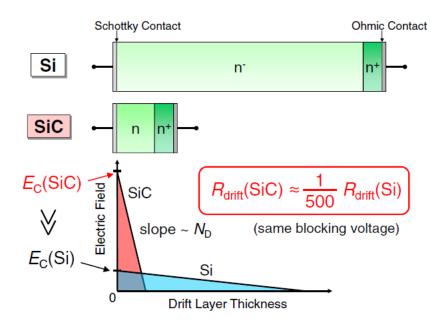

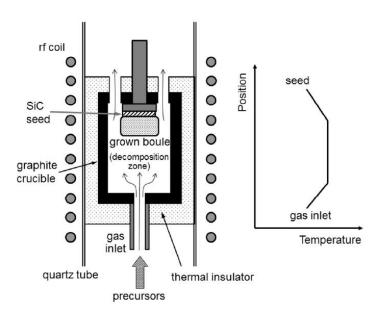

| Figure 2-7: Electric field distribution in a one-sided junction for Si and SiC at the         |

| same voltage [1]23                                                                            |

| Figure 2-8: Relationship between on-resistance and breakdown voltage for Si and SiC           |

| unipolar devices25                                                                            |

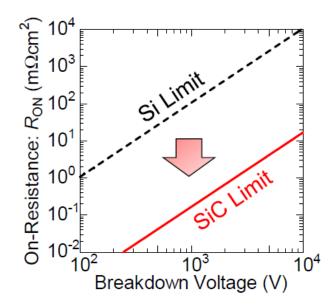

| Figure 2-9: Voltage rating of Si and SiC power devices                                        |

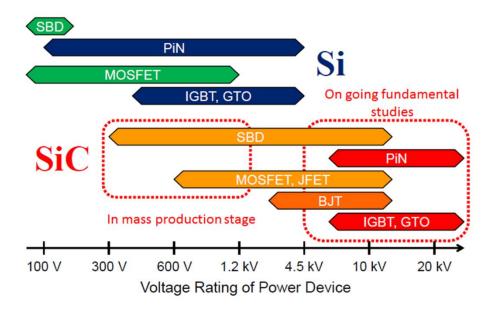

| Figure 2-10: Core part of reactor and temperature profile used for SiC bulk growth by         |

| HTCVD31                                                                                       |

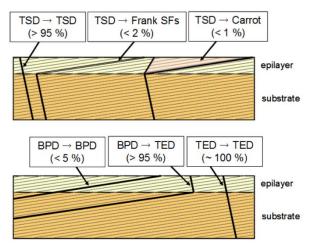

| Figure 2-11: Schematic illustration of dislocation propagation in 4H-SiC epilayers            |

| grown on off-axis by chemical vapour deposition [24]34                                        |

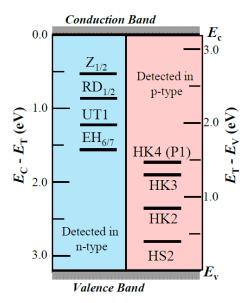

| Figure 2-12: Energy levels of the main deep levels seen in as-grown n-type and p-type         |

| 4H-SiC epilayers [24]38                                                                       |

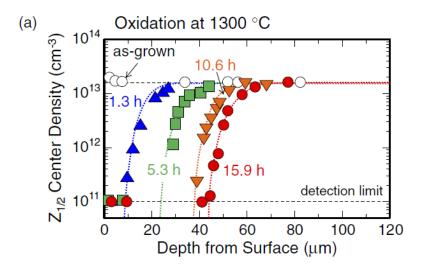

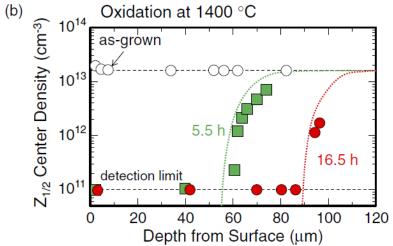

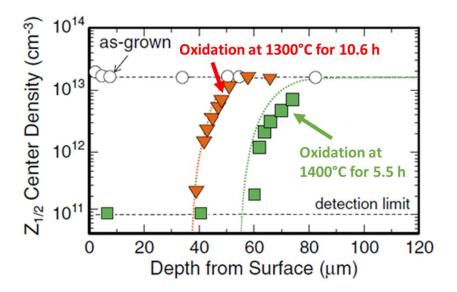

| Figure 2-13: (Colour online) Depth profile of the Z $_{1/2}$ density for SiC epilayers after  |

| thermal oxidation at (a) 1300 and (b) 1400 °C for various periods. By increasing the          |

| oxidation time or the oxidation temperature, the " $Z_{1/2}$ -free" region spreading from the |

| surfac [1]41                                                                                  |

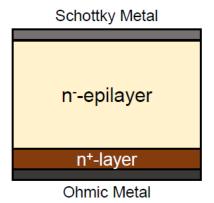

| Figure 2-14: Schematic cross-section a Schottky barrier diode                                 |

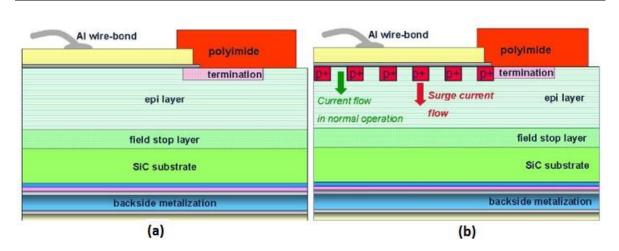

| Figure 2-15: (a) Schematic cross section of conventional SiC Schottky diode, (b) SiC          |

| diode with merged p-doped islands (MPS diodes) [112]49                                        |

| Figure 2-16: Schematic drawing of $1200\mathrm{V}$ MPS with current spreading layer $[113]50$ |

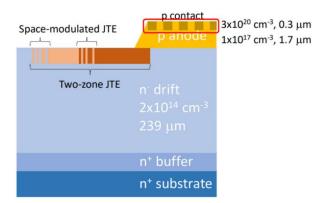

| Figure 2-17: Schematic structure of PiN diode51                                               |

| Figure 2-18: Device structure of developed UHV 4H-SiC PiN diode with two-zone                 |

| and space-modulated JTE. The active area of the diode is 5.75 mm2 [119]52                     |

| Figure 3-1: Cross-section view of a Schottky diode55                                          |

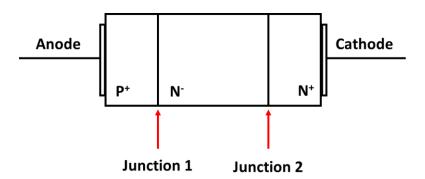

| Figure 3-2: Cross section view of a PiN diode                                          | 56   |

|----------------------------------------------------------------------------------------|------|

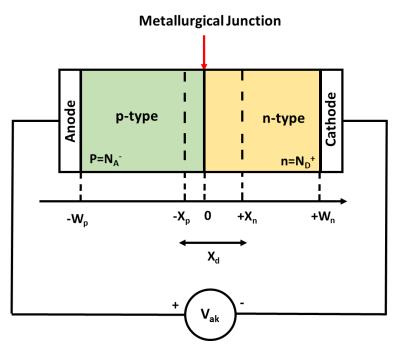

| Figure 3-3: A diagram of P-N junction structure                                        | 58   |

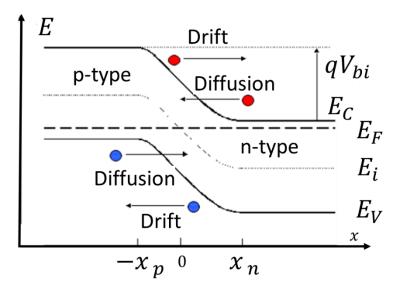

| Figure 3-4: Energy band diagram of a p-n junction in thermal equilibrium               | 60   |

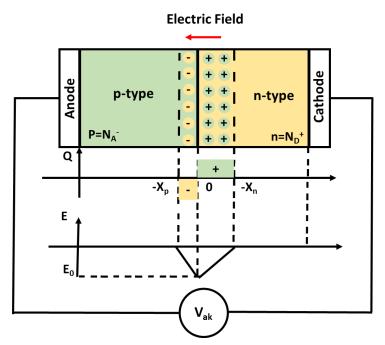

| Figure 3-5: Built-in potential at P-N junction when no voltage is applied to the       |      |

| structure                                                                              | 61   |

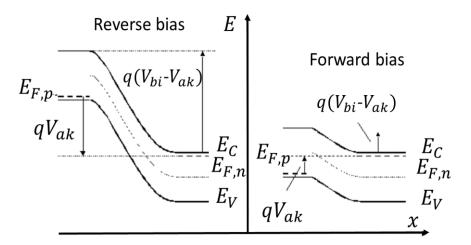

| Figure 3-6: Energy band diagram of a p-n junction under forward and reverse bias       | 62   |

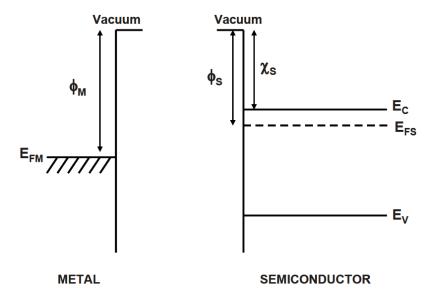

| Figure 3-7: Energy band diagram for a metal and semiconductor when they are            |      |

| isolated from each other                                                               | 63   |

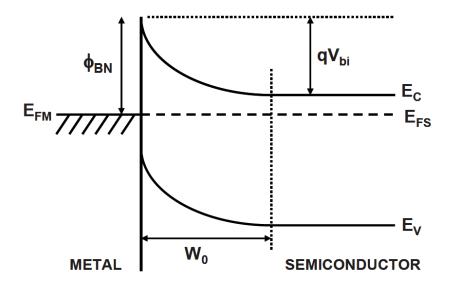

| Figure 3-8: Energy band diagram for a metal and a semiconductor after the contact      | t is |

| made                                                                                   | 66   |

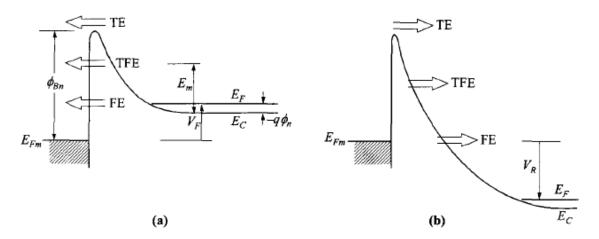

| Figure 3-9: Energy-band diagram showing tunneling currents in a Schottky diode         |      |

| under (a) forward biad and (b) reverse bias. TE= thermionic emission, TFE,             |      |

| thermionic field emission, FE= field emission [42]                                     | 70   |

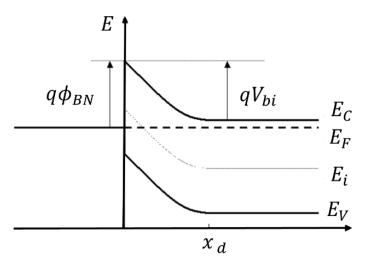

| Figure 3-10: Energy band diagram of a metal-semiconductor contact in thermal           |      |

| equilibriumequilibrium                                                                 | 71   |

| Figure 3-11: A non-rectifying Schottky barrier formed by a non-rectifying metal-       |      |

| semiconductor junction.                                                                | 72   |

| Figure 3-12: Energy band diagram of a metal-semiconductor junction under forwar        | ď    |

| bias                                                                                   | 73   |

| Figure 3-13: Forward biased Schottky diode structure                                   |      |

| Figure 3-14: Energy band diagram of a metal-semiconductor junction under reverse       | e    |

| bias                                                                                   | 75   |

| Figure 3-15: One dimensional device structure under reverse bias                       | 75   |

| Figure 3-16: PiN diode structure and the electric field across the device              | 76   |

| Figure 3-17: Formation of charge storage region in a PiN diode [126]                   |      |

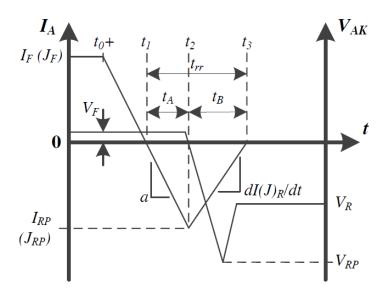

| Figure 3-18: Extraction of charge from the drift region during turn-off of PiN diode   |      |

| [126]                                                                                  | 79   |

| Figure 3-19: A typical PiN diode (IRF HF50D120ACE) current and voltage turn-off        |      |

| switching waveforms measured at Warwick.                                               | 82   |

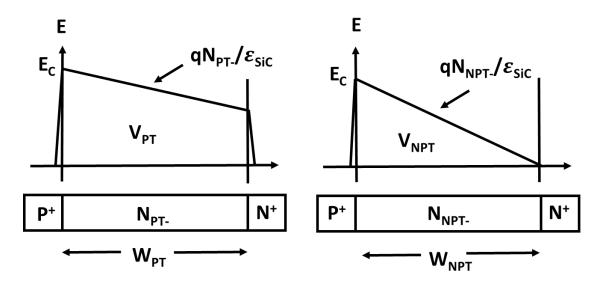

| Figure 3-20: Electric filed profile at breakdown for punch-through (left) and non-     |      |

| punch-through (right) PiN diode structure with equal drift region length               |      |

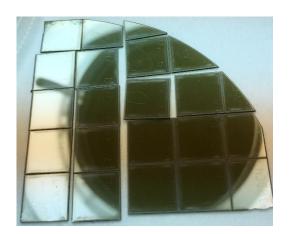

| Figure 4-1: The results of laser cutting the 4H-SiC wafer into $10 \times 10$ mm chips |      |

| Figure 4-2: 4H-SiC PiN diodes after thermal oxidation process. The variation in col    |      |

| is due to surface contamination.                                                       |      |

| Figure 4-3: High temperature oxidation furnace in the clean room                       |      |

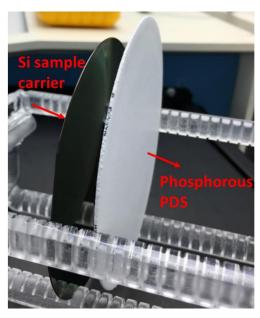

| Figure 4-4: Samples mounted on a Si carrier wafer placed in front of the phosphore     |      |

| PDS on a carrier boat                                                                  |      |

| Figure 4-5: Annealing furnace used for phosphorous treatment                           |      |

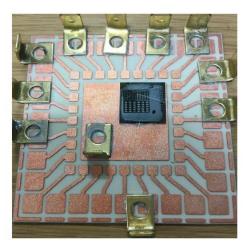

| Figure 4-6: Layout of the designed DBC substrate used for packaging the fabricate      |      |

| dies                                                                                   |      |

| Figure 4-7: Al stencil used for soldering process with a thickness of 6 thou           | 107  |

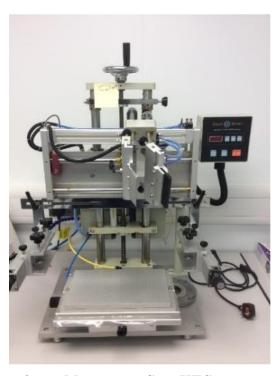

| Figure 4-8: Bench-top Mascoprint S200HFC semi-automatic solder screen printing machine with stencil holder at the University of Warwick power device packaging |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| facility                                                                                                                                                       |

| Figure 4-9: Cammax Precima EDB65 Eutetic pick and place die bonder, including N2                                                                               |

| cover gas at the University of Warwick power device packaging facility109                                                                                      |

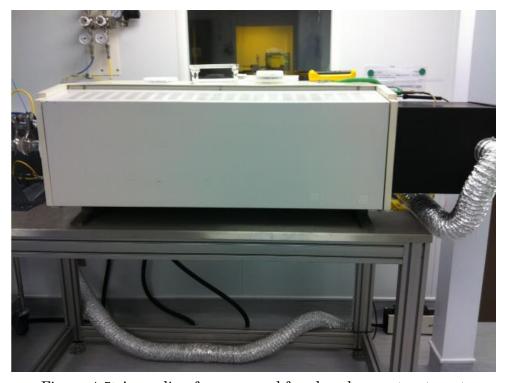

| Figure 4-10: ATV SRO-704 programmable solder reflow/thermal processing, rapid                                                                                  |

| thermal annealing (RTA) oven with 950°C processing capability at the University of                                                                             |

| Warwick power device packaging facility110                                                                                                                     |

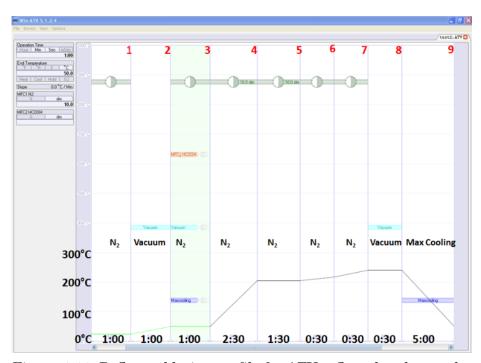

| Figure 4-11: Reflow soldering profile for ATV reflow chamber.at the University of                                                                              |

| Warwick power device packaging facility111                                                                                                                     |

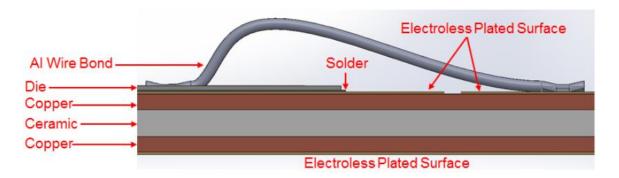

| Figure 4-12: A cross section view of a conventional power module packaging showing                                                                             |

| stack of different materials on top of each other [126]                                                                                                        |

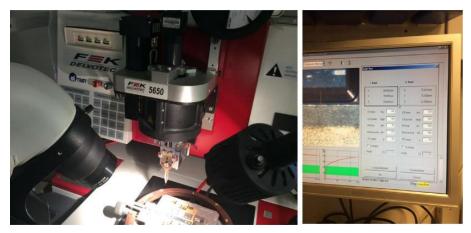

| Figure 4-13: Semi-automatic Orthodyne model 20heavy wire bonder114                                                                                             |

| Figure 4-14: FEK Delvotec 5650 heavy automatic wire bonder                                                                                                     |

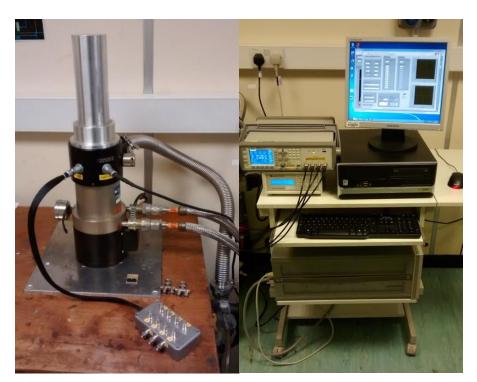

| Figure 5-1: Cryostat chamber, electrical measurement and control setup117                                                                                      |

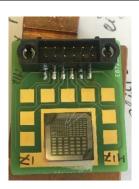

| Figure 5-2: The die under test wire bonded to a PCB.                                                                                                           |

| Figure 5-3: Disassembled chamber and the cold head assembly                                                                                                    |

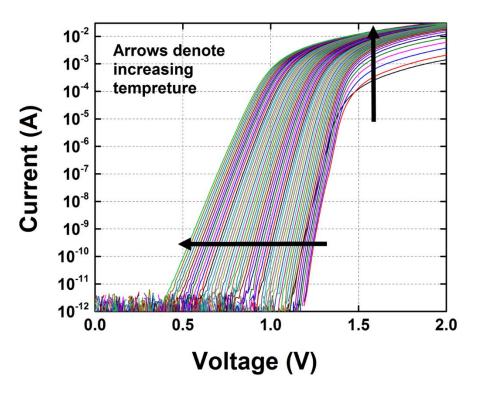

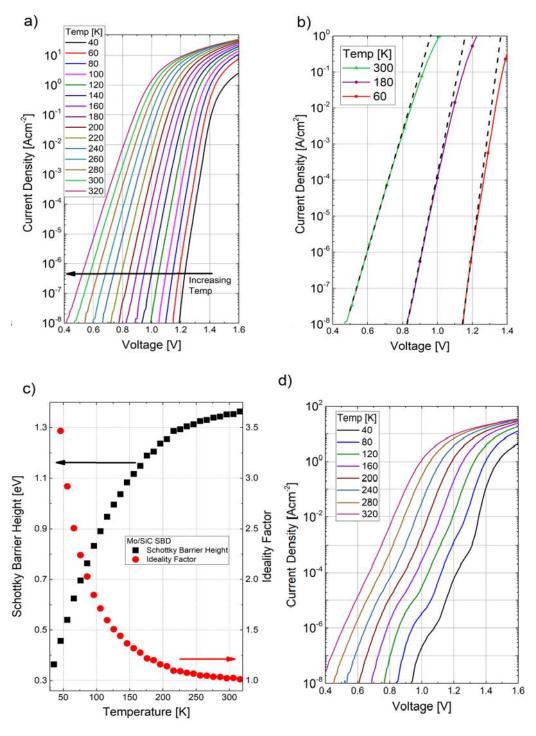

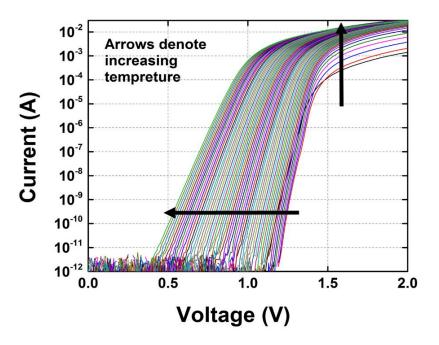

| Figure 5-4: I-V-T curves of 4H-SiC Schottky diodes taken at temperature range of 25K                                                                           |

| to 320K with 2K intervals                                                                                                                                      |

| Figure 5-5: High voltage breakdown test rig capable of testing up to 10kV reverse                                                                              |

| voltages                                                                                                                                                       |

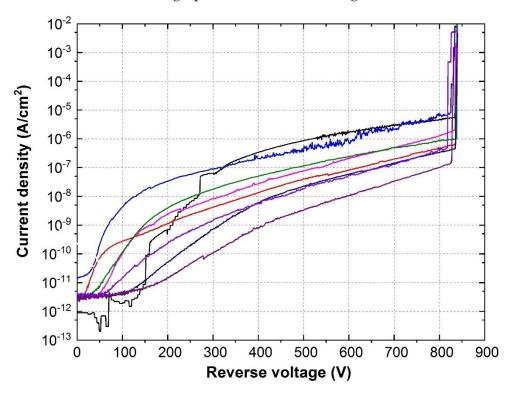

| Figure 5-6: Reverse breakdown testing of fabricated 4H-SiC Schottky diodes with 35                                                                             |

| μm drift region thickness (no junction termination implemented in the device                                                                                   |

| structure)                                                                                                                                                     |

|                                                                                                                                                                |

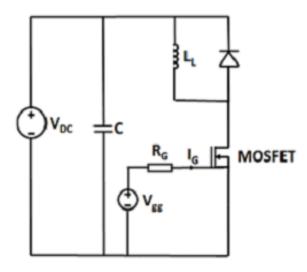

| Figure 5-7: Clamped inductive switching circuit.                                                                                                               |

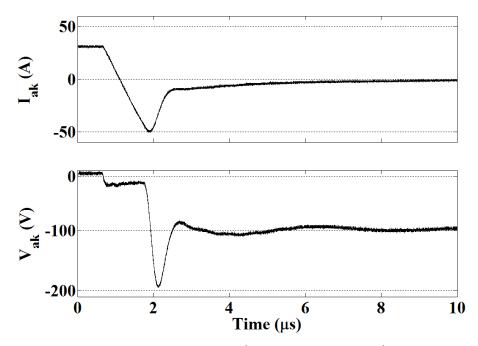

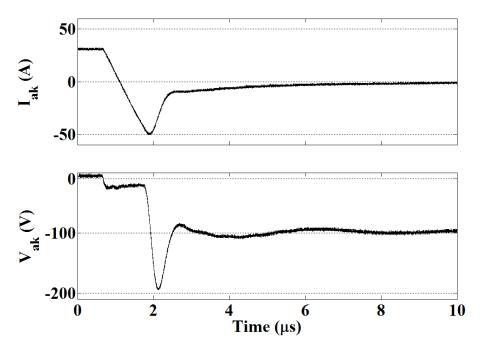

| Figure 5-8: Reverse recovery waveform of the fabricated 4H-SiC PiN diode                                                                                       |

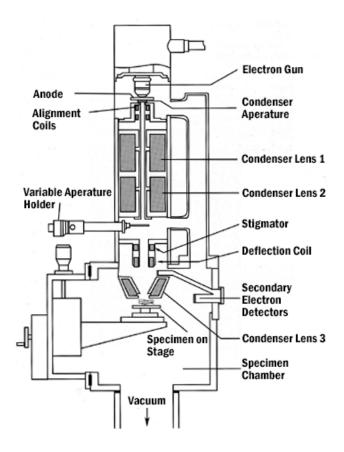

| Figure 5-9: Schematic of a scanning electron microscope [165]                                                                                                  |

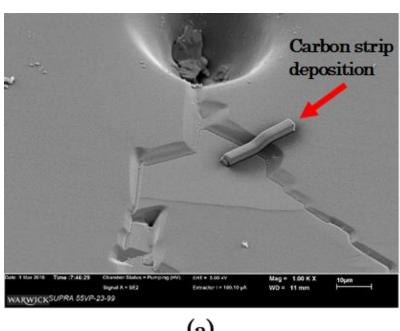

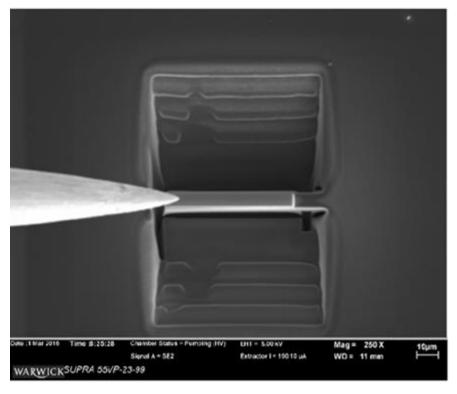

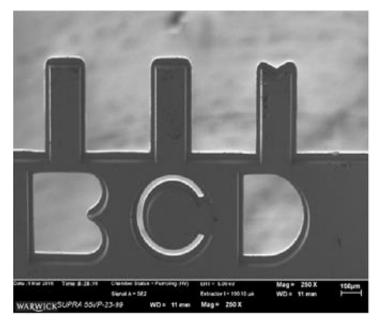

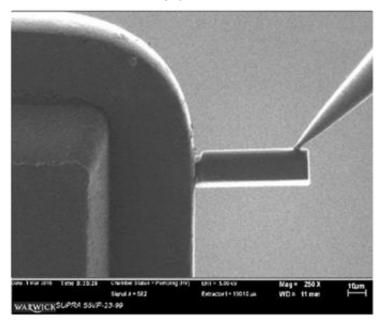

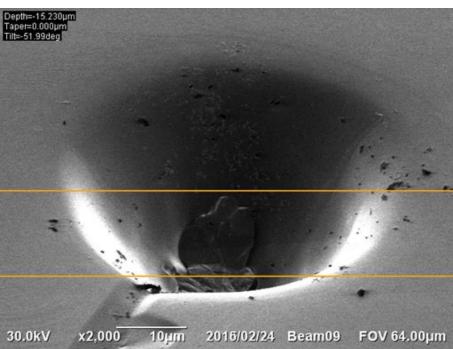

| Figure 5-10: TEM sample preparation using FIB-SEM (a) strip of carbon deposited to                                                                             |

| protect the surface (b) trenches milled using FIB on either side of the area of interest.                                                                      |

| 131                                                                                                                                                            |

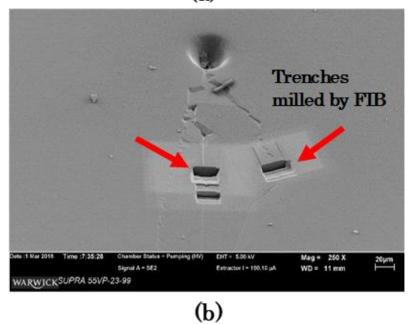

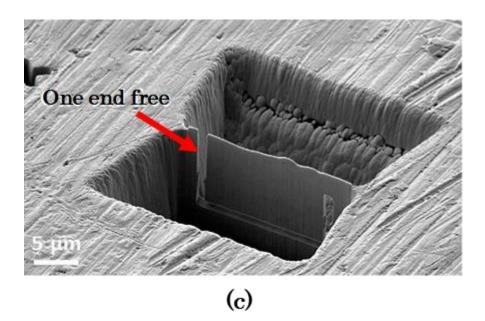

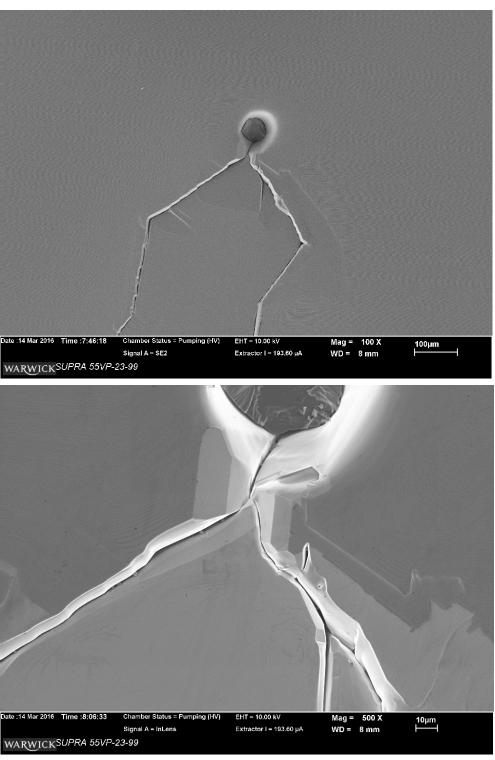

| Figure 5-11: TEM sample preparation using FIB-SEM (c) the specimen is detached                                                                                 |

| from the substrate from one end using FIB (d) the manipulator is attached to the                                                                               |

| specimen to lift it out.                                                                                                                                       |

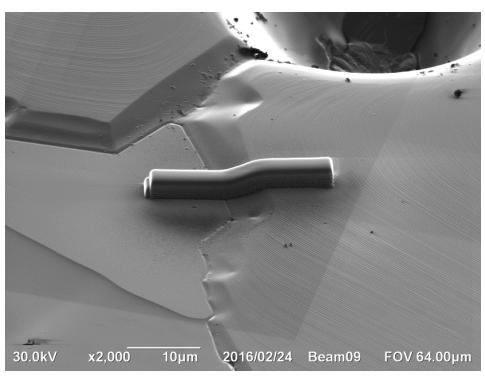

| Figure 5-12: TEM sample preparation using FIB-SEM (e) TEM sample grid for                                                                                      |

| holding the specimen in place (f) the specimen is attached to the grid by carbon                                                                               |

| deposition. FIB is then used to separate the manipulator from the specimen. The                                                                                |

| specimen needs to be thinned                                                                                                                                   |

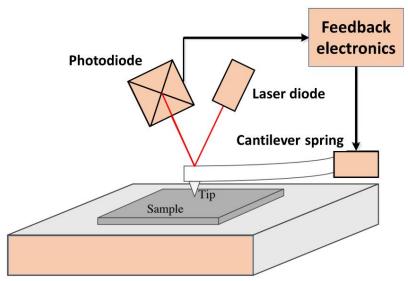

| Figure 5-13: Schematic of an atomic force microscope showing the basic components of                                                                           |

| an AFM137                                                                                                                                                      |

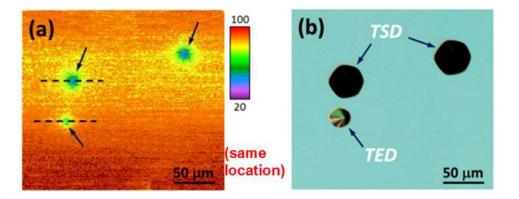

| Figure 5-14: (a) Micro PL intensity mapping at 390 nm (near band-edge emission) at                                                                             |

| room temperature obtained from a 72µm thick n-type 4H-SiC epilayer intentionally                                                                               |

| doped to 1×1015 cm <sup>-3</sup> . (b) Optical microscopy image of the sample surface (same                                                                    |

| location) after molten [166]140                                                                                                                                |

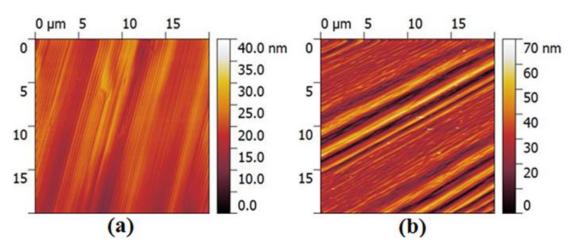

| Figure 6-1: 20 x 20 μm2 AFM image taken of SiC surface of samples with (a) 30 μm epitaxial layer with RMS surface roughness of 2.96 nm (PiN2) (b) 110 μm epitaxial |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| layer with RMS surface roughness of 13.43 nm (PiN3)                                                                                                                |

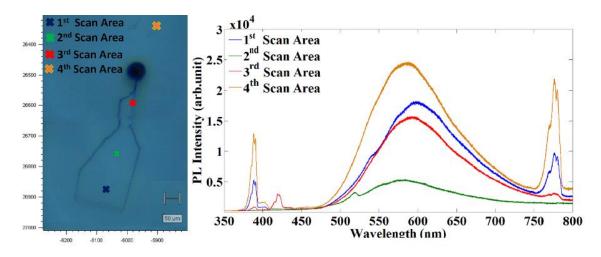

| Figure 6-2: PL images using 325 nm wavelength source at the defect (1st, 2nd, and                                                                                  |

| 3rd scan area) and bulk (4thscan area) area and the optical microscopic view of a 30                                                                               |

| μm (PiN2) epitaxial layer sample147                                                                                                                                |

| Figure 6-3: fabricated on triangular defects on PiN1 (left) and PiN3 (right)148                                                                                    |

|                                                                                                                                                                    |

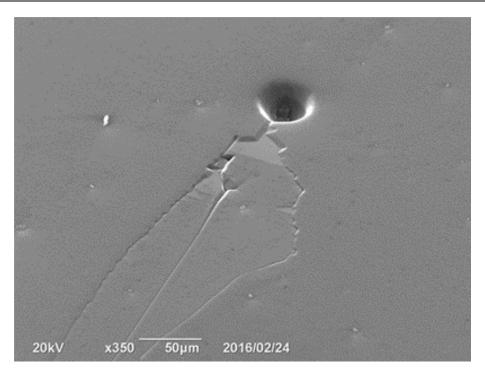

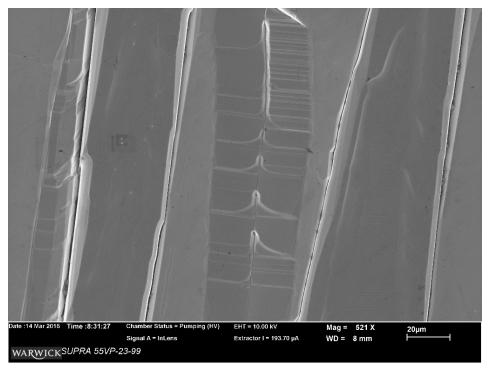

| Figure 6-4: High resolution SEM images of a triangular defect on PiN2 showing the                                                                                  |

| foreign particle which is the origin of the triangular defect                                                                                                      |

| Figure 6-5: High resolution SEM images of a triangular defect on PiN3                                                                                              |

| Figure 6-6: High resolution SEM image of PiN1, showing the step-bunching and                                                                                       |

| bending, wave shape lines on the surface                                                                                                                           |

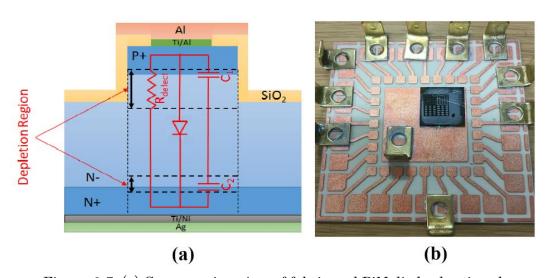

| Figure 6-7: (a) Cross-section view of fabricated PiN diode showing the triangular                                                                                  |

| defect on the device (b) Photograph of DCB-mounted 4H-SiC PiN diode die                                                                                            |

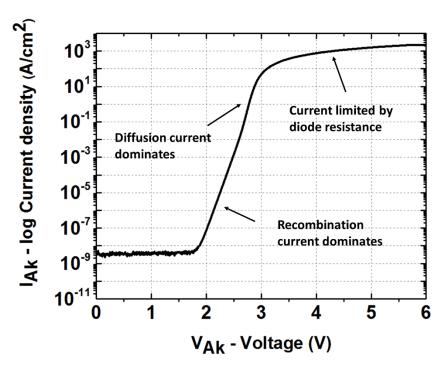

| Figure 6-8: Forward log(J)-V characteristic of a selected PiN diode fabricated off-                                                                                |

| defect for PiN 1 at 25°C, illustrating the dominant current conduction mechanism for                                                                               |

| each area of the J-V characteristic of the device.                                                                                                                 |

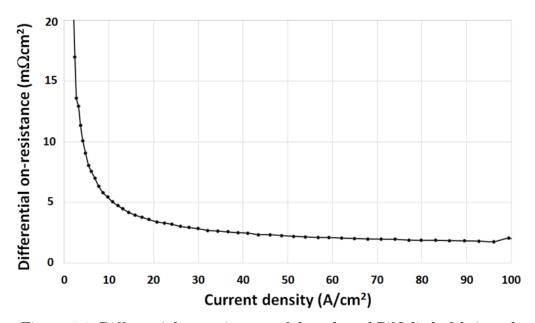

| Figure 6-9: Differential on-resistance of the selected PiN diode fabricated off-defect on                                                                          |

| PiN1 at 25°                                                                                                                                                        |

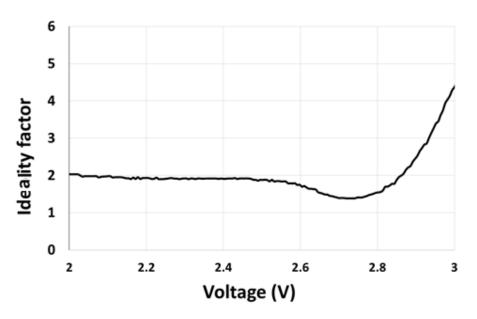

| Figure 6-10: Idelaity factor against voltage of the PiN diode fabricated off-defect on                                                                             |

| PiN1 at room temperature163                                                                                                                                        |

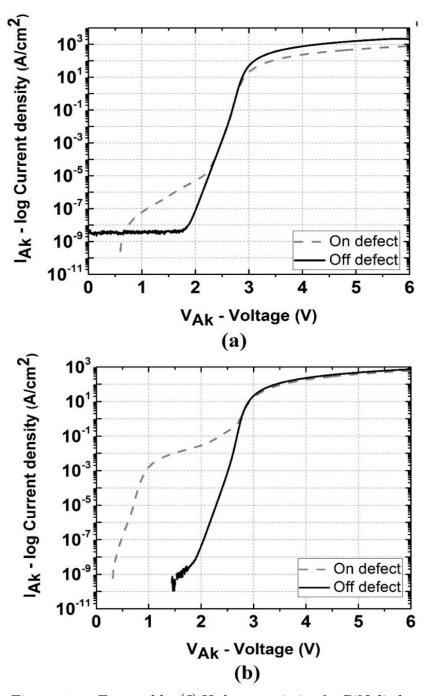

| Figure 6-11: Forward log(J)-V characteristics for PiN diodes fabricated on and off-                                                                                |

| defect on (a) PiN1 (35 $\mu$ m layer) and (b) PiN2 (30 $\mu$ m layer) at room temperature164                                                                       |

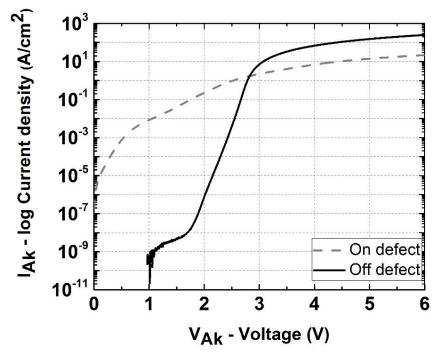

| Figure 6-12: Forward log(J)-V characteristics for PiN diodes fabricated on and off-                                                                                |

| defect on PiN3 (110 μm layer)165                                                                                                                                   |

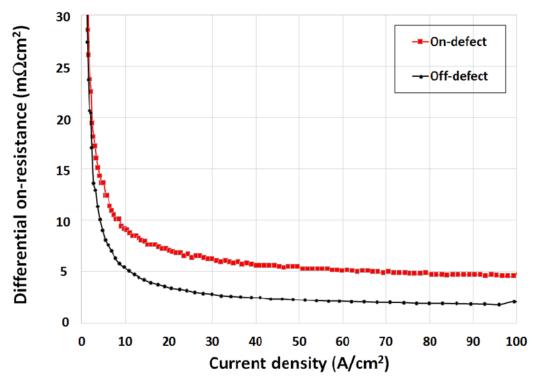

| Figure 6-13: Differential on-resistance of PiN diodes fabricated on and off-defect on                                                                              |

| PiN1 at 25°                                                                                                                                                        |

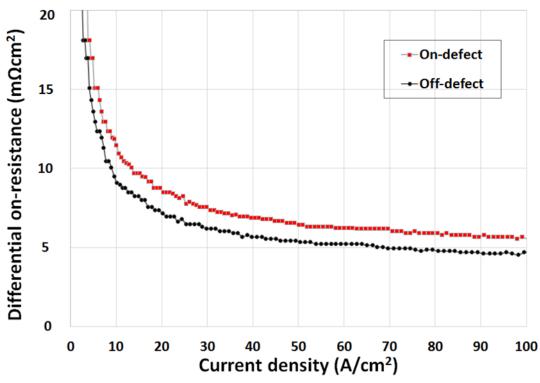

| Figure 6-14: Differential on-resistance of PiN diodes fabricated on and off-defect on                                                                              |

| PiN2 at 25°                                                                                                                                                        |

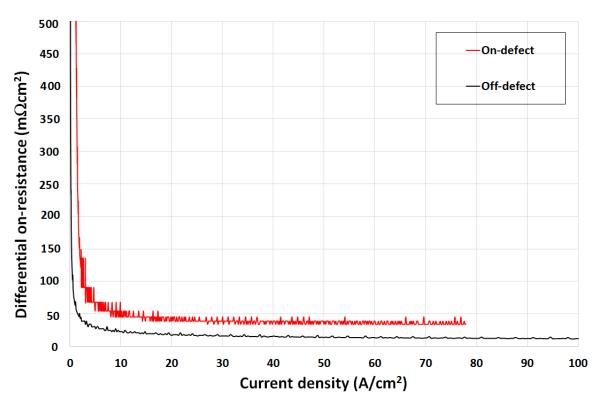

| Figure 6-15: Differential on-resistance of PiN diodes fabricated on and off-defect on                                                                              |

| PiN3 at 25°                                                                                                                                                        |

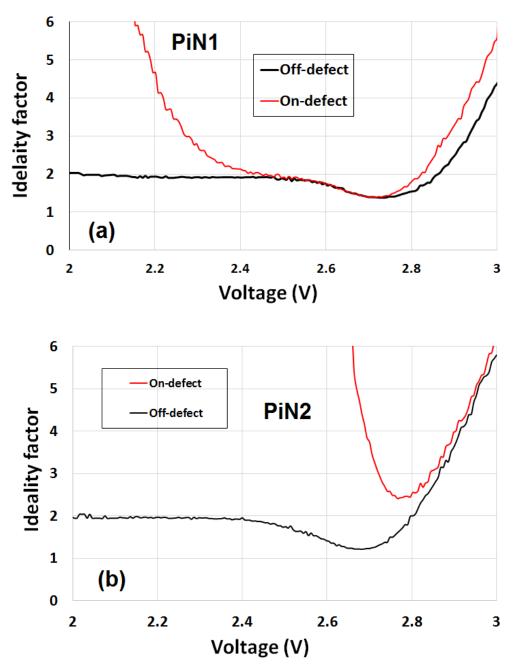

| Figure 6-16: Ideality factor against voltage for (a) PiN1 and (b) PiN2 devices, both on                                                                            |

| and off-defect at 25°170                                                                                                                                           |

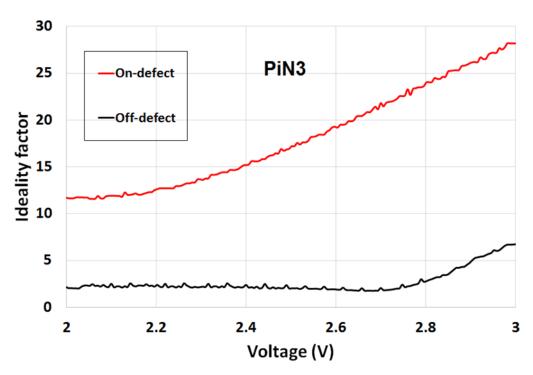

| Figure 6-17: Ideality factor against voltage for PiN3 devices both on and off-defect at                                                                            |

| 25°                                                                                                                                                                |

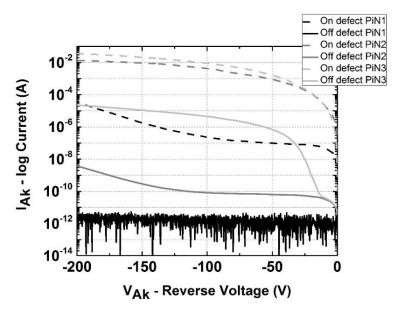

| Figure 6-18: Reverse leakage current of PiN diodes fabricated on-and off-defect on all                                                                             |

| substrates                                                                                                                                                         |

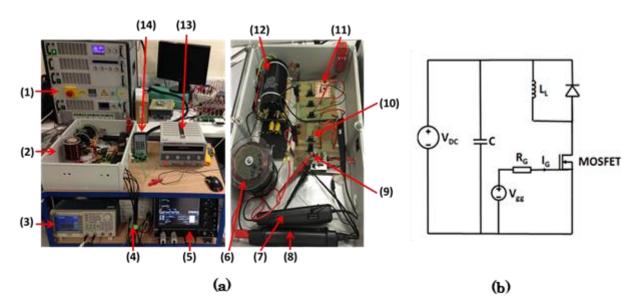

| Figure 6-19: Clamped inductive switching test rig (b) Circuit diagram of a clamped                                                                                 |

| inductive switching circuit.                                                                                                                                       |

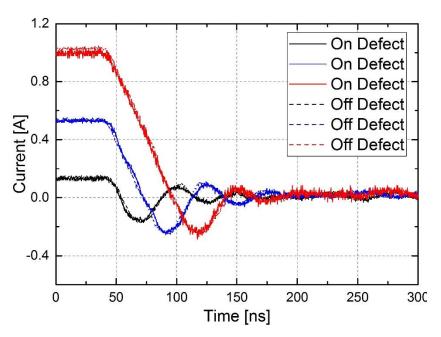

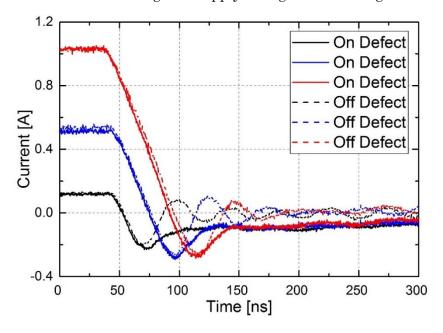

| Figure 6-20: Reverse recovery current waveform for devices fabricated on and off-                                                                                  |

| defect on PiN1 at room temperature conditions using 40V supply voltage and a 10 $\Omega$                                                                           |

| gate resistance                                                                                                                                                    |

| Figure 6-21: Reverse recovery current waveform for devices fabricated on and off-        |                |

|------------------------------------------------------------------------------------------|----------------|

| defect on (a) PiN1 and (b) PiN2 at room temperature conditions using 40V supply          |                |

| voltage and a 10 $\Omega$ gate resistance.                                               | ('1            |

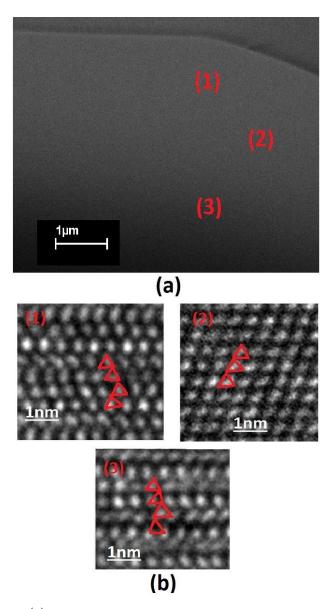

| Figure 6-22: (a) cross-sectional TEM image obtained from a 4H-SiC sample of the          |                |

| triangular defect showing (b) top, middle and bottom layer of the sample is shown        |                |

| where a thick 3C-SiC layer is grown in between two layers of 4H-SiC18                    |                |

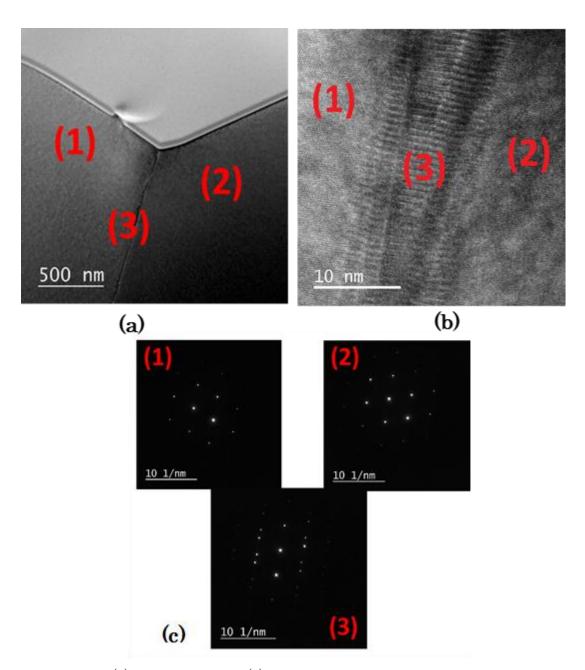

| Figure 6-23: (a) TEM image and (b) diffraction patterns of the triangular defect area    |                |

| showing the grain boundary and the leakage path18                                        |                |

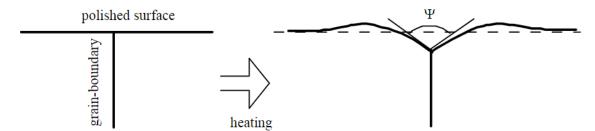

| Figure 6-24: Grain boundary grooving process                                             | 33             |

| Figure 6-25: TEM image of the triangular defect on PiN3, clearly showing the grain       |                |

| boundaries and multiple leakage paths18                                                  | 34             |

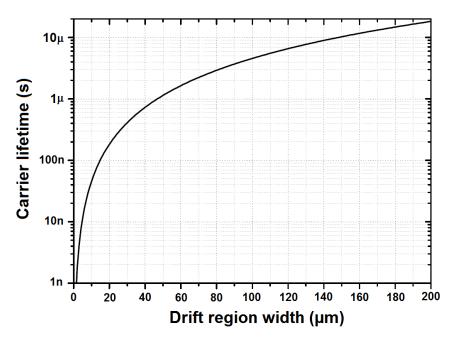

| Figure 7-1: Optimal carrier lifetime against various drift region widths in 4H-SiC. 19   | <del>)</del> 0 |

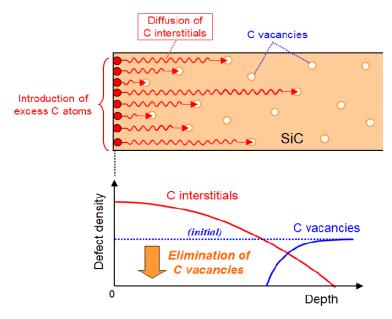

| Figure 7-2: Elimination of VC defects in SiC showing the introduction of excess C        |                |

| atoms from the outside followed by diffusion of carbon interstitials using thermal       |                |

| treatment [148]                                                                          | <del>)</del> 2 |

| Figure 7-3: Depth profile of $Z_{1/2}$ density obtained from a 240 $\mu m$ n-type 4H-SiC |                |

| epilayer after thermal oxidation at 1300°C and 1400°C temperatures19                     | <b>)</b> 4     |

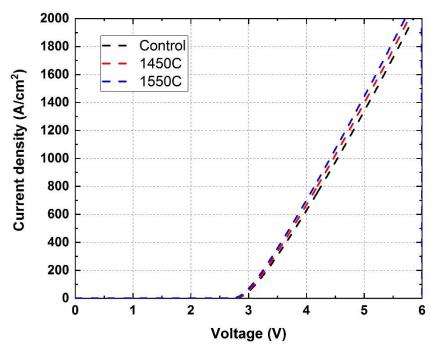

| Figure 7-4: Forward J-V characteristics of the small-area thermally oxidised PiN         |                |

| diodes and the control sample measured at 25°C.                                          | <b>}</b> 7     |

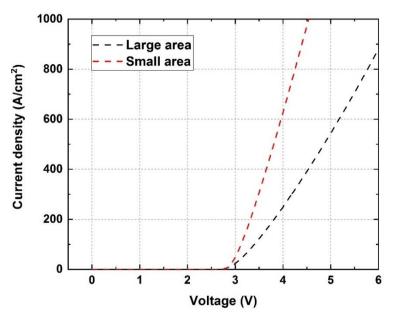

| Figure 7-5: Forward J-V characteristics for large-area and small-area control sample     |                |

| at 25°C.                                                                                 |                |

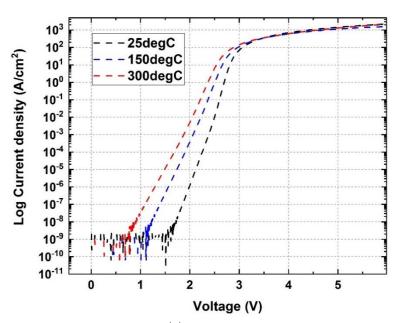

| Figure 7-6: Forward Log(J)-V characteristics of small-area diodes on sample2 at 25°C     |                |

| 150°C and 300°C                                                                          |                |

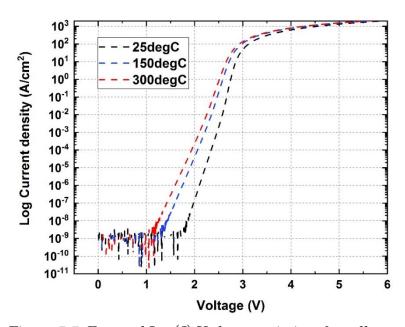

| Figure 7-7: Forward Log(J)-V characteristics of small-area diodes on control sample a    |                |

| 25°C, 150°C and 300°C                                                                    |                |

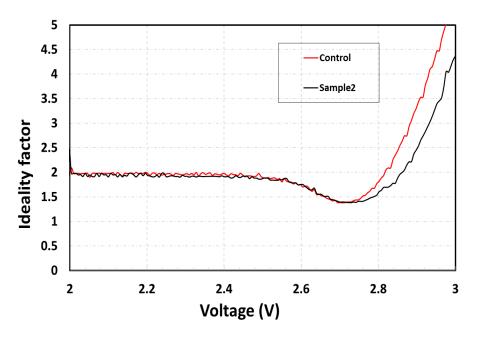

| Figure 7-8: Ideality factor against voltage characteristics for small-area diodes on th  | e              |

| control sample and Sample2 at 25°C20                                                     |                |

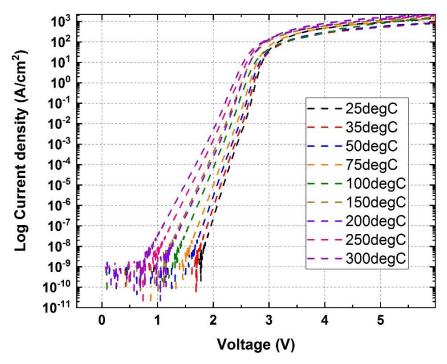

| Figure 7-9: Forward I-V-T characteristics of thermally oxidised sample at the            |                |

| temperature range of 25°C to 300°C                                                       | )2             |

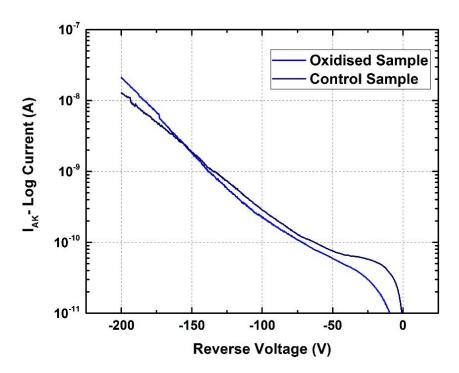

| Figure 7-10: Reverse I-V characteristics for both control and thermally oxidised PiN     |                |

| diodes at 25°C                                                                           | )3             |

| Figure 7-11: Forward I-V characteristics of PiN diodes at 25°C showing the non-idea      |                |

| I-V characteristic in the recombination region due to the existence of parasitic         | -              |

| Schottky diode in parallel with the pn junction.                                         | )4             |

| Figure 7-12: Reverse recovery approximation waveforms with inductive load                | _              |

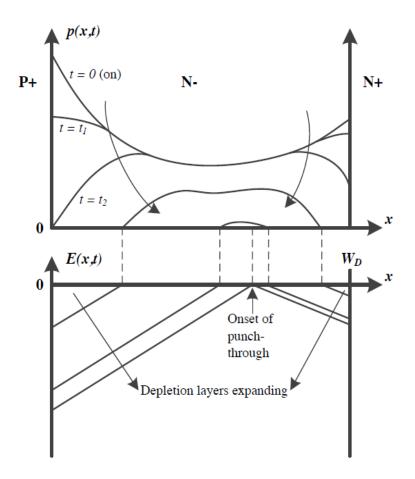

| switching                                                                                | )7             |

| Figure 7-13: Charge profile in the drift region during inductive load switching and th   |                |

| one-dimensional distribution of electric field.                                          |                |

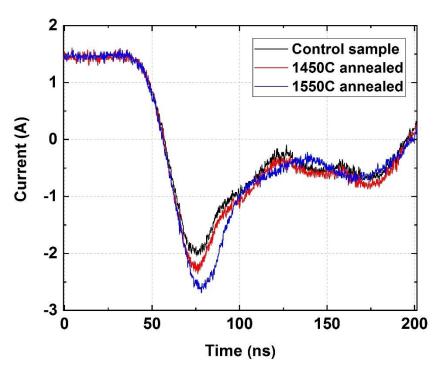

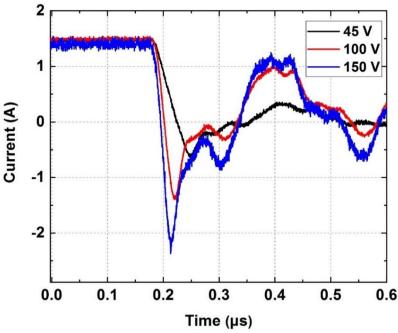

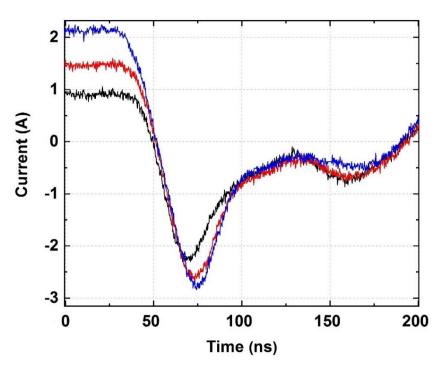

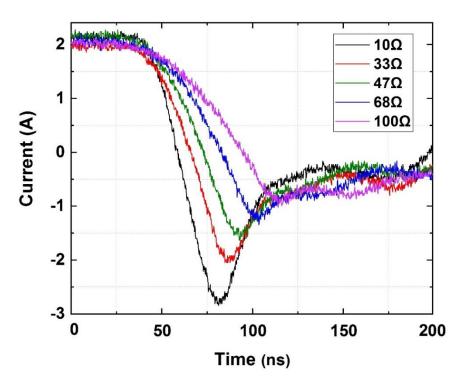

| Figure 7-14: Reverse recovery characteristics for control sample, 1450°C and 1550°C      |                |

| thermally oxidised PiN diodes at 25°C                                                    |                |

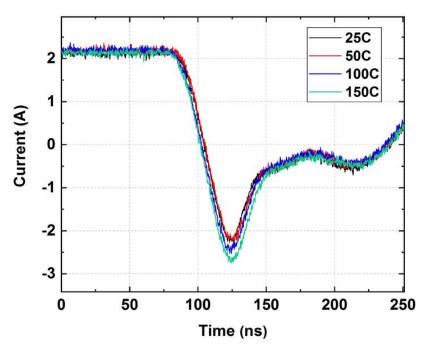

| Figure 7-15: Reverse recovery characteristics of the 1450°C oxidised / annealed SiC      | . 0            |

| PiN diode at different junction temperatures. DC link voltage=150 V                      | 15             |

| Figure 7-16: Reverse recovery waveform as a function of supply voltage for the 1550 annealed sample at 25°C, RG= 10 $\Omega$ .                                                                                                 | о°С<br>216  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 7-17: Reverse recovery waveform with different forward currents for the $1550^{\circ}$ C annealed sample at $25^{\circ}$ C, VDC= $150$ V, RG= $10$ $\Omega$                                                             |             |

| Figure 7-18: Reverse recovery waveform as a function of switching rate for the 1550                                                                                                                                            |             |

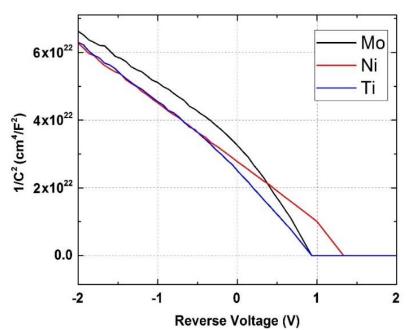

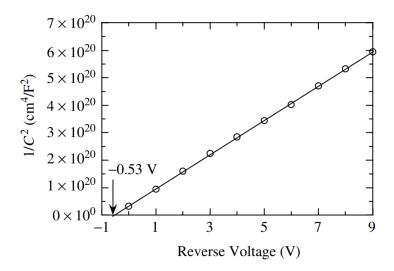

| Figure 8-1: The C-2-V used to extract the doping value (N2O treated diodes before                                                                                                                                              | 236         |

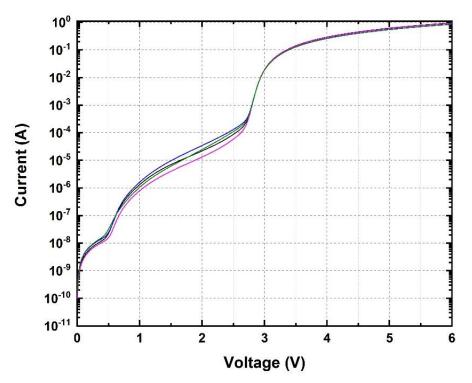

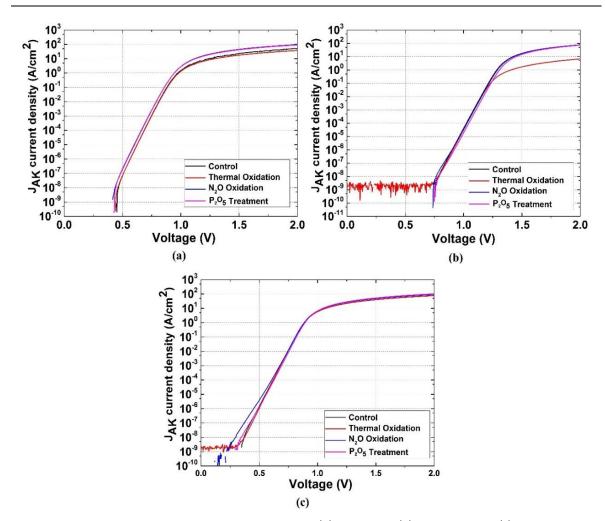

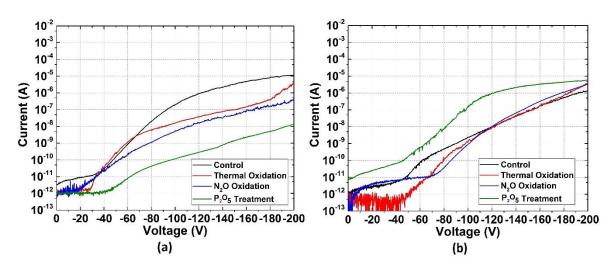

| Figure 8-2: Forward characteristics of (a) Mo/SiC, (b) Ni/SiC and (c) Ti/SiC SBDs                                                                                                                                              |             |

| using different surface passivation treatments                                                                                                                                                                                 |             |

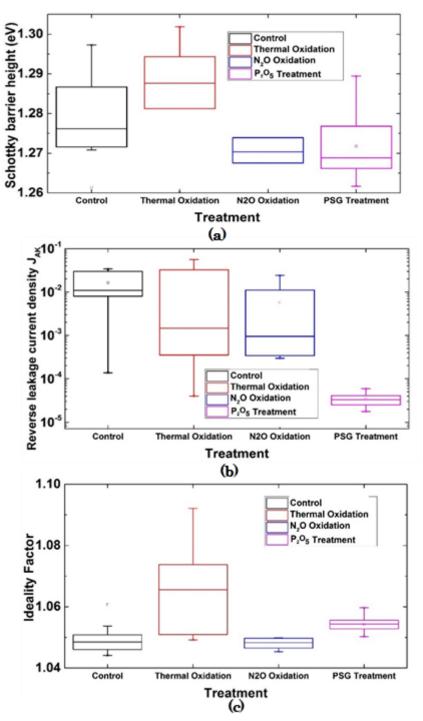

| Figure 8-4: (a) Schottky Barrier Height (SBH), (b) reverse leakage current density measured at 200 V and (c) ideality factor, all derived from I-V measurements on                                                             | <b>2</b> 00 |

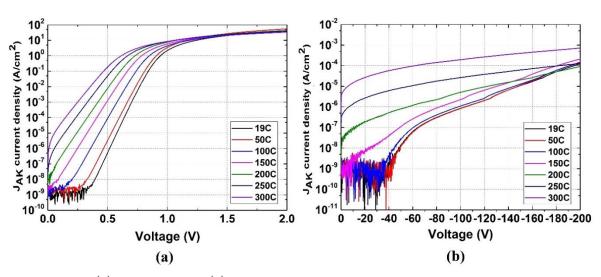

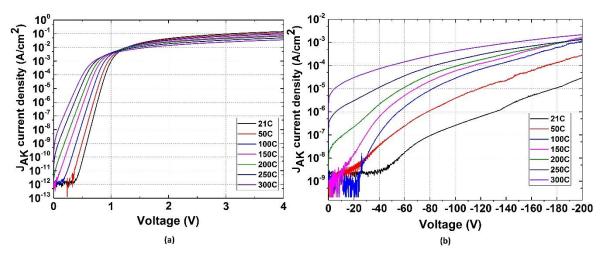

| Mo/SiC diodes, post-anneal. Each dataset contains at least 30 of each diode tested. 2 Figure 8-5: (a) Forward and (b) Reverse I-V-T characteristics of P <sub>2</sub> O <sub>5</sub> treated Mo/SiC at different temperatures. | С           |

| at different temperatures                                                                                                                                                                                                      | at          |

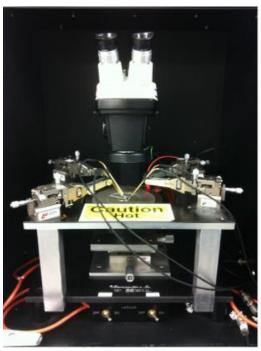

| Figure 8-7: Variable temperature probe station set up in the clean room                                                                                                                                                        |             |

| IVT characteristics of a single device. (b) Zooms in on three of the temperatures showing increasing voltage dependency at low temperature. (c) Extracted SBH and ideality factor acro                                         | 244         |

| Figure 8-9 Low temperature I-V-T characteristics of P2O5 treated Mo/SiC at differe                                                                                                                                             | ent<br>246  |

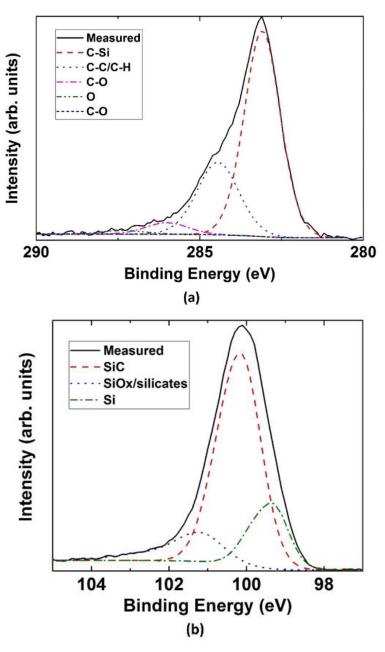

| Figure 8-10: XPS data for the (a) C 1s region and (b) Si 2p region without surface treatment                                                                                                                                   | 248         |

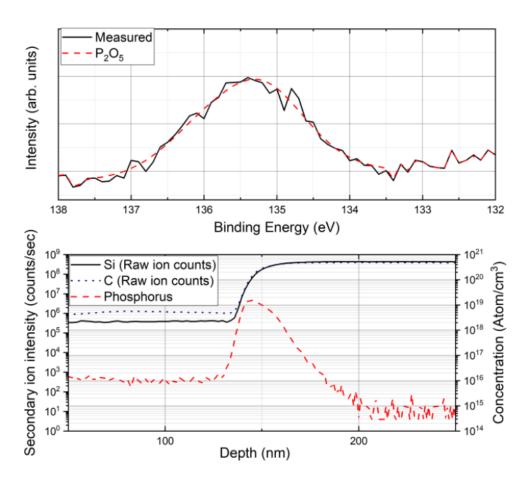

| Figure 8-11: (top) XPS data for P 2p region showing a P2O5 peak for P2O5 treated Mo/SBD sample and (bottom) SIMS result for the P2O5 treated sample                                                                            | 251         |

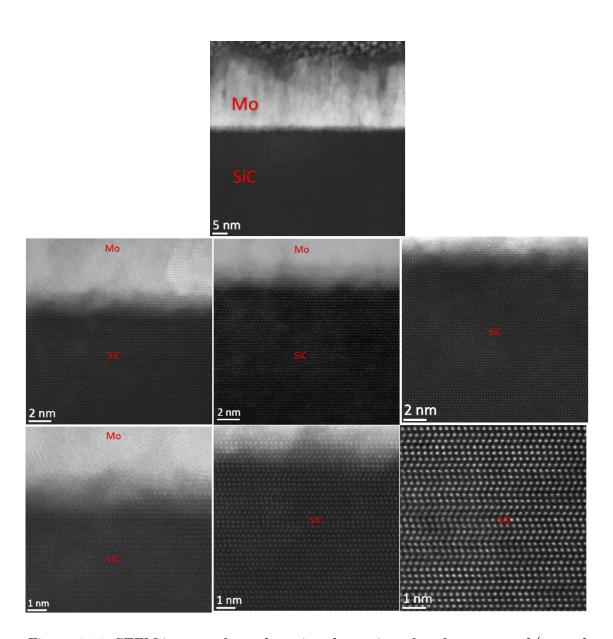

| Figure 8-12: STEM images of metal-semiconductor interface for untreated (control sample) 4H-SiC Mo Schottky diode.                                                                                                             |             |

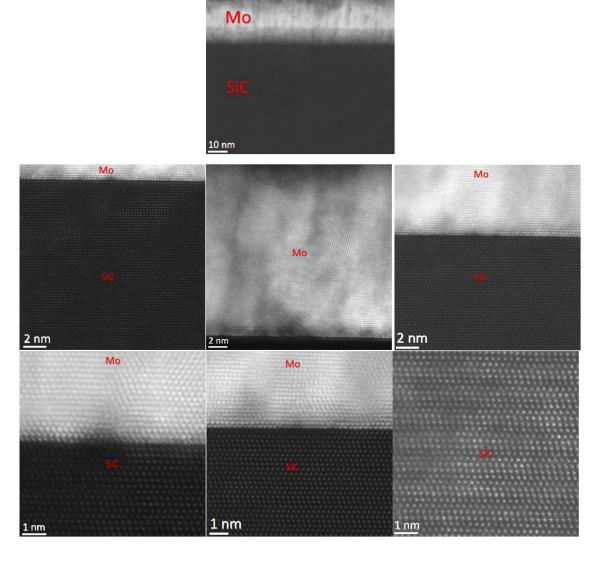

| Figure 8-13: STEM images of metal-semiconductor interface for P2O5 treated 4H-S Mo Schottky diode2                                                                                                                             | 254         |

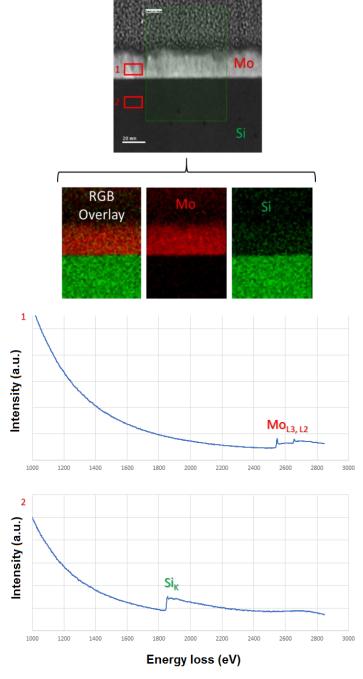

| Figure 8-14: EELS results of untreated 4H-SiC Mo/SBD sample                                                                                                                                                                    |             |

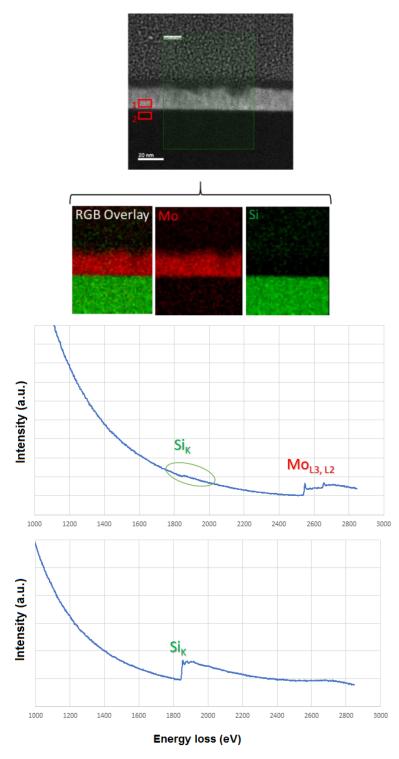

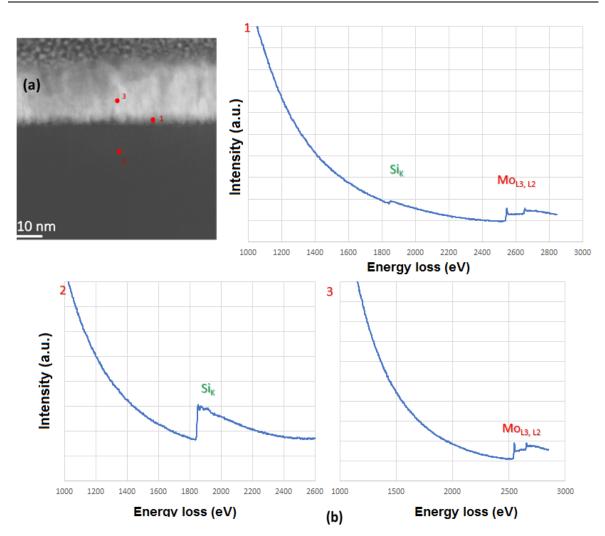

| Figure 8-16: EELS analysis of untreated Mo/SBDs at 3 different regions                                                                                                                                                         | 259         |

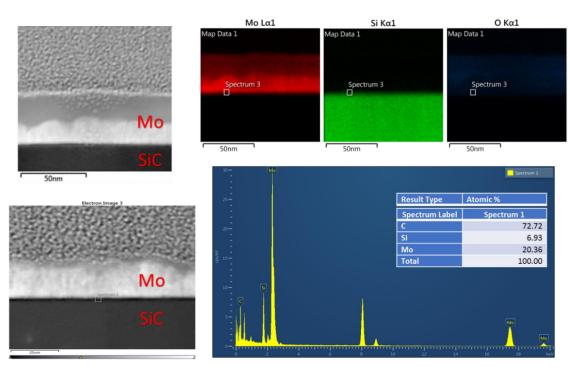

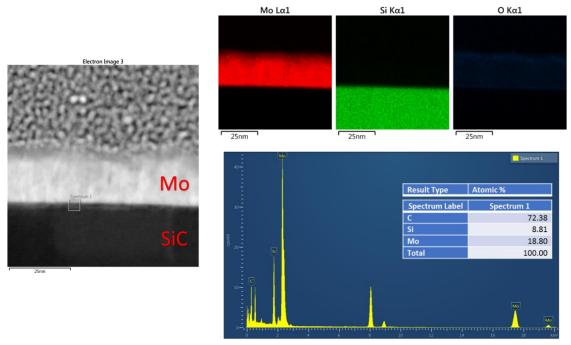

| Figure 8-17. EDX results for as deposited Mo/SiC Schottky diode sample                                                                                                                                                         | e.          |

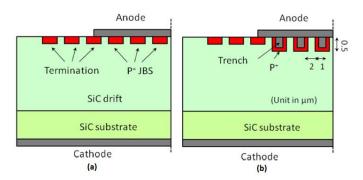

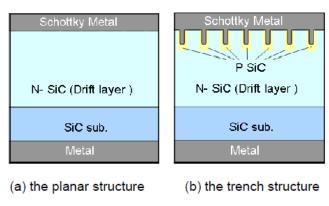

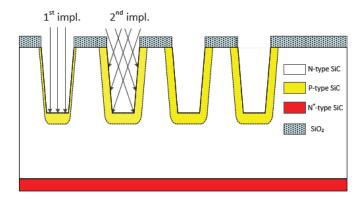

| Figure A-1: (a) Planar JBS structure, (b) Trench JBS structure used in simulations                                                                                                                                             |             |

| Figure A-2: Schematic cross section of the planar and trench structure Schottky    |       |

|------------------------------------------------------------------------------------|-------|

| diodes [119]                                                                       | 277   |

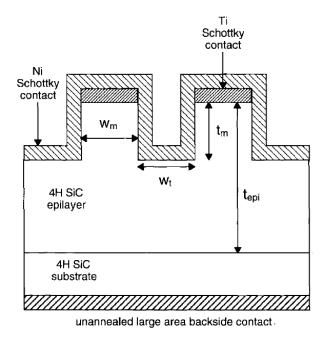

| Figure A-3: Device structure of Ti/Ni dual-metal-trench pinch rectifier [120]      | 278   |

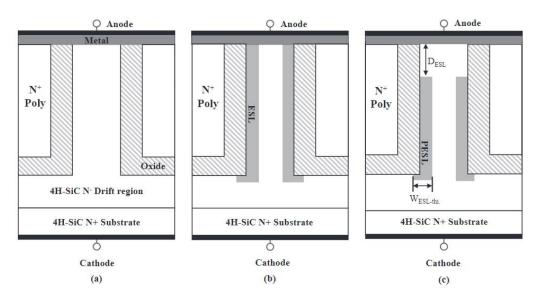

| Figure A-4: Cross sections of the (a) conventional 4H-SiC TMBS, (b) ESL-TMBS       | , and |

| (c) partial-ESL-TMBS rectifiers [121]                                              | 280   |

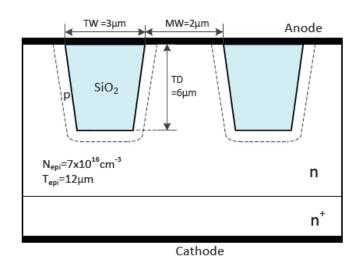

| Figure A-5: SiC SJ Schottky diode cell structure and basic dimension informatio    | n     |

| [129]                                                                              | 281   |

| Figure A-6: Key process step of the SiC SJ Schottky diode [129]                    | 281   |

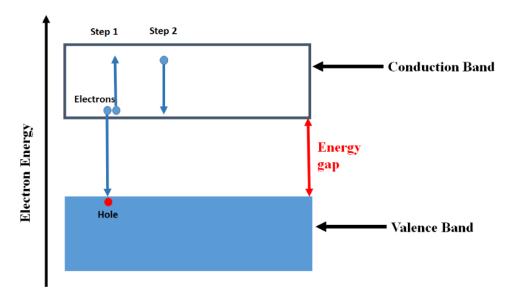

| Figure C-1: Auger recombination process, where an electron and hole recombine      | , the |

| electron release its energy to another electron (third electron) in the conduction | band. |

| This causes the third electron to move to a higher energy. It then releases its    |       |

| additional energy and moves back down to the edge of the conduction band           | 288   |

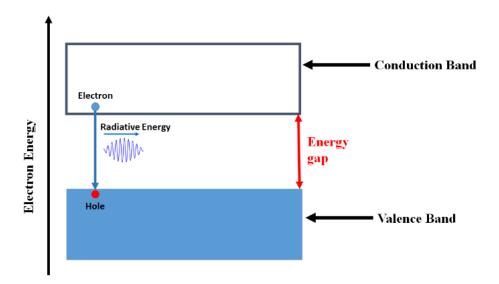

| Figure C-2: Band-to-band recombination process.                                    | 289   |

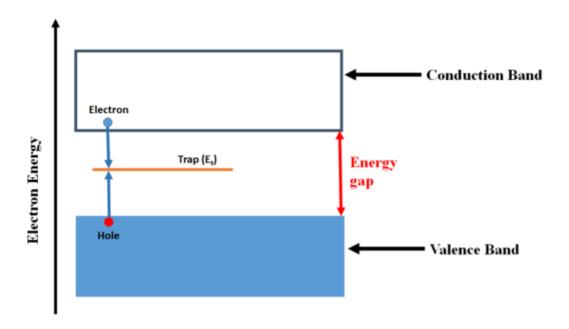

| Figure C-3:Schockley-Read-Hall recombination process                               | 290   |

## List of Tables

| Table 2-1: Key physical properties of 3C- and 4H-SiC polytypes together with oth   | er    |

|------------------------------------------------------------------------------------|-------|

| common semiconductor materials at room temperature [41]                            | 22    |

| Table 2-2: Major extended defects in SiC epilayers, TSD: threading screw dislocate | tion, |

| TED: threading edge dislocation, BPD: basal plane dislocation                      | 33    |

| Table 2-3: Commercial SiC Schottky diodes with reverse blocking voltage range o    | f 600 |

| V to 3300 V. VF (max) and IR (max) are measured at 25°C                            | 47    |

| Table 2-4: State of the art 4H-SiC PiN diode devices reported by device manufact   | urers |

| and research institutes                                                            | 53    |

| Table 4-1: Ceramic DBC substrate material properties                               | 105   |

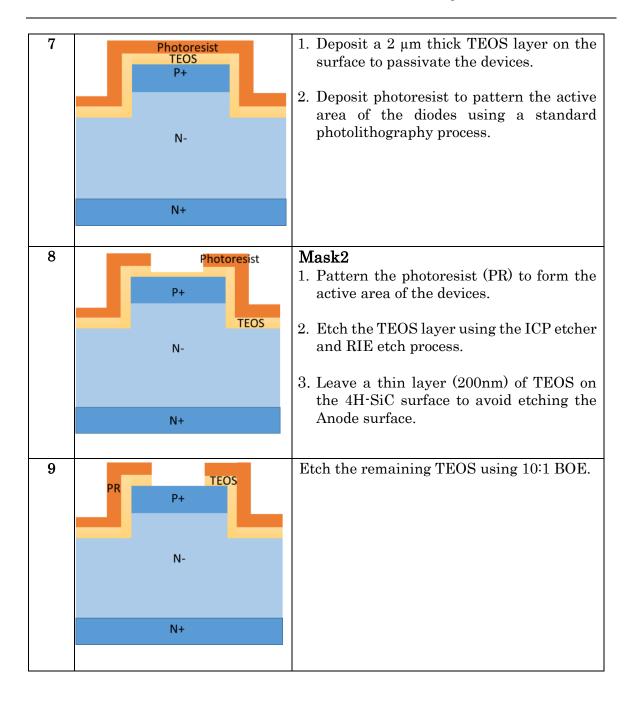

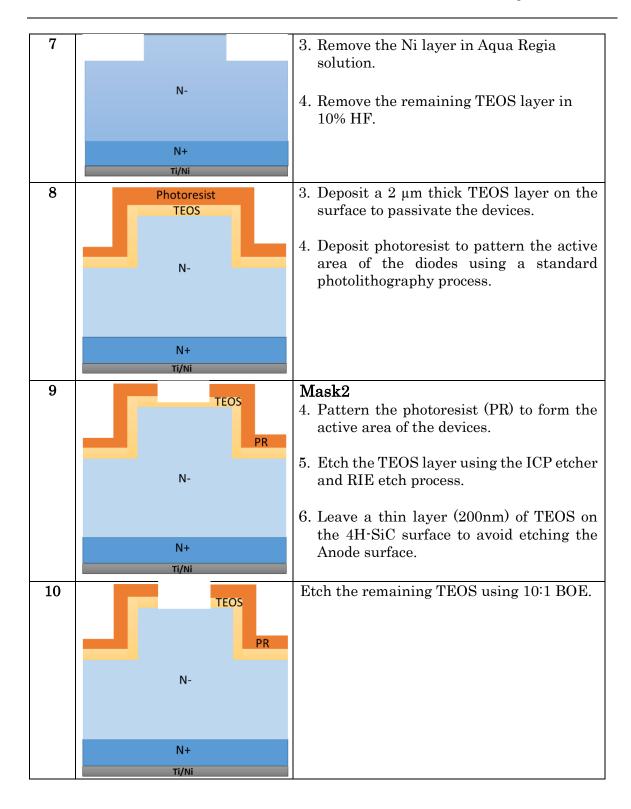

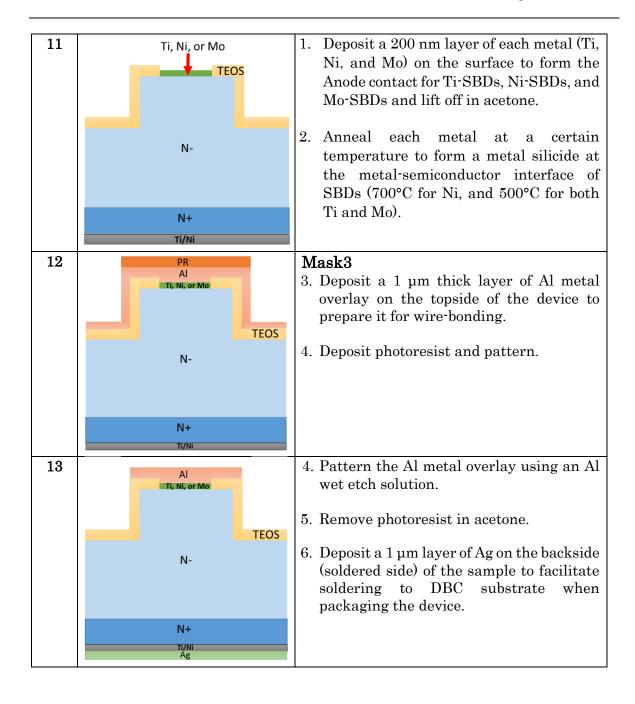

| Table 6-1: 4H-SiC PiN diode fabrication process flow                               | 152   |

| Table 8-1: 4H-SiC Schottky diode fabrication process flow                          | 227   |

| Table 8-2: leakage current, ideality factor and SBH derived from I-V measuremen    | nts   |

| before and after contact annealing, and SBH and doping profile from C-V            |       |

| measurements. Each result is the average of at least 20 of each diode tested       | 233   |

| Table 8-3: Ratio of SiC atomic percentage from the C 1s spectrum to SiC atomic     |       |

| percentage from the Si 2p spectrum for each surface treatment                      | 250   |

Declaration

This thesis is submitted to the University of Warwick in support of the application

for the degree of Doctor of Philosophy. It has not been submitted in part, or in whole,

for a degree or other qualification at any other University. Parts of this thesis are

published by the author in peer-reviewed research papers listed. Apart from commonly

understood and accepted ideas, or where reference is made to the work of others, the

work described in this thesis is carried out by the author in School of Engineering of

the University of Warwick.

Yeganeh Bonyadi

2014-2019

xiii

## Acknowledgement

First, I would like to thank my PhD supervisor, Prof. Phil Mawby, without whom this PhD would not have been possible. Thank you Phil, for your continued support and encouragement and for providing me with useful advice related to my studies and life. I am extremely grateful for the opportunity you gave me to undertake this PhD in the exciting field of power electronics and for always caring like a father.

Next, I would like to thank my second supervisor Dr. Peter Gammon for his support and guidance throughout my PhD studies. I really appreciate your insightful suggestions and enthusiasm about the research presented in this thesis. I would also like to thank Prof. Layi Alatise for your invaluable technical advice and suggestions on my research studies.

For their cleanroom wisdom, I must thank Dr. Mark Crouch and Corinne Maltby. For their technical support, I must thank Frank Courtney for his wire-bonding skills and Steven Hindmarsh for his SEM and TEM expertise. Special thanks also go to my colleagues and friends in the PEATER group.

In the end, unreserved thanks and gratitude must go to my lovely family. This thesis is dedicated to you. I can't find any words to thank my mum, Manijeh and dad, Siamak for their unconditional love and support throughout my life. Mum, thank you for always believing in me and encouraging me, even when you were not here with me anymore. I am forever grateful, I love you and I hope I have made you proud. I would also like to thank my sister, Roxanna and brother, Roozbeh for your endless love and support. I would also like to thank my brother in law Aydin and my sister in law Zarina for encouraging me and for always being there. Lastly, but obviously not least, I would also like to thank my fiancé, Siavash, who has never failed to support me in all that I have done, and who has been an inspiration to me. Thank you for being you.

#### **Publication List**

- 1. B. Renz, V. Shah, O. Vavasour, Y. Bonyadi, G. Baker, L. Fan, D. Tian, M. Walker, P. Mawby, P. Gammon, "Surface Effects of Passivation within Mo/4H-SiC Schottky Diodes through MOS Analysis," in Materials Science Forum, 2019, vol. 963: Trans Tech Publ, pp. 511-515.

- 2. Y. Bonyadi, P. M. Gammon, O. Alatise, R. Bonyadi, and P. A. Mawby, "Lifetime Enhancement of 4H-SiC PiN Diodes Using High Temperature Oxidation Treatment," in Materials Science Forum, 2018, vol. 924: Trans Tech Publ, pp. 440-443.

- 3. Z. Davletzhanova, O. Alatise, R. Bonyadi, J. Ortiz-Gonzalez, C. Chan, Y. Bonyadi, M. Jennings, P. Mawby, "Impact of Leakage Currents on Voltage Sharing in Series Connected SiC Power MOSFETs and Silicon IGBT Devices," in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018: IEEE, pp. P. 1-P. 10.

- 4. **Y. Bonyadi**, P. M. Gammon, Y. K. Sharma, G. Baker, and P. A. Mawby, "An investigation into the impact of surface passivation techniques using metal-semiconductor interfaces," in Materials Science Forum, 2017, vol. 897: Trans Tech Publ, pp. 443-446.

- 5. **Y. Bonyadi** et al., "The impact of triangular defects on electrical characteristics and switching performance of 3.3 kV 4H-SiC PiN diode," in 2016 IEEE Energy Conversion Congress and Exposition (ECCE), 2016: IEEE, pp. 1-5.

- 6. **Y. Bonyadi** et al., "Characterization of 4H-SiC PiN Diodes Formed on Defects Identified by PL Imaging," in Materials Science Forum, 2016, vol. 858: Trans Tech Publ, pp. 405-409.

- 7. C. Chan, Y. Bonyadi, P. A. Mawby, and P. M. Gammon, "Si/SiC substrates for the implementation of linear-doped power LDMOS studied with device simulation," in Materials Science Forum, 2016, vol. 858: Trans Tech Publ, pp. 844-847.

- 8. R. Bonyadi, O. Alatise, J. Hu, Z. Davletzhanova, **Y. Bonyadi**, J. Ortiz-Gonzalez, L. Ran, P. Mawby, "Compact electrothermal models for unbalanced parallel conducting Si-IGBTs," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), 2016: IEEE, pp. 253-260.

#### Abstract

Despite the excellent electrical and thermal properties of 4H-silicon carbide (SiC) and the advancements in the field of 4H-SiC epitaxial growth, the existence of defects in the material can considerably reduce the electrical performance of the SiC power devices. Defects can result in low carrier lifetime affecting the on-state resistance of bipolar devices, such as PiN diodes, and increased leakage current affecting the reverse blocking performance of power devices, such as Schottky diodes. A commonly found surface morphological defect in available 4H-SiC substrates is the triangular defect. In this thesis, the formation mechanism of this defect and its impact on the electrical performance of the fabricated 4H-SiC PiN diodes is discussed. 4H-SiC PiN diodes were intentionally fabricated on the triangular defects and in areas with no visible morphological defects. The devices were then packaged and tested to assess the impact of these defects on the resulting on state and reverse leakage characteristics. It was shown for the first time the impact of triangular defects on switching characteristics of 4H-SiC PiN diodes fabricated on and off-defects. Moreover, triangular defects were characterised using methods including AFM, SEM, Photoluminescence and HRTEM. Other complex structures were observed on the triangular defect using HRTEM such as double positioning boundary (DPB), which resulted in a leakage path through the drift region of the devices and increased the leakage current.

Furthermore, this thesis focuses on the fabrication and analysis of 4H-SiC power diodes for high voltage applications with particular focus on improving the performance of 4H-SiC SBDs using a novel metal-semiconductor interface treatment and 4H-SiC PiN diodes using high temperature processing techniques to improve the carrier lifetime, on-state resistance and conductivity modulation of the diode. Carrier lifetime enhancement in 4H-SiC PiN diodes in this thesis was achieved using a combined high temperature oxidation and successive argon annealing process at 1550°C for 1 hour. This resulted in an increase of nearly 45% of the reverse recovery current and approximately 40% of the carrier lifetime. The findings of this study could be potentially used for other 4H-SiC bipolar devices such as IGBTs, BJTs and thyristors.

This thesis has also investigated the impact of various surface passivation treatments to improve the quality of the 4H-SiC surface and the metal-semiconductor interface using Mo/Ti, and Ni-4H-SiC Schottky diodes. The most significant outcome of this investigation was the performance of P<sub>2</sub>O<sub>5</sub> treated Mo/SiC Schottky diodes which retained a barrier height equivalent to that of titanium, but with a leakage current lower than any Ni diode, seemingly combining the benefits of both a low- and high-SBH metal. Furthermore, P<sub>2</sub>O<sub>5</sub> treated Mo/SiC Schottky diodes were the only diodes to undergo any significant leakage current reduction after any of the pre-treatments exhibiting exceptionally low leakage, even at 300°C. XPS and SIMS analysis on all Mo/SiC SBDs revealed that the stoichiometry of the SiC underneath the contact was enhanced using P<sub>2</sub>O<sub>5</sub> treatment and that traces of P<sub>2</sub>O<sub>5</sub> were found after removal of the passivation layer and post-treatment metallisation. It was also found that the Mo-4H-SiC interface on the P<sub>2</sub>O<sub>5</sub> treated sample was very sharp and uniform compared to the untreated sample where Mo-SiC interface looks uneven and cloudy. The developed novel metal-semiconductor interface treatment can be potentially used for MOS interface improvements.

### List of Abbreviations

AFM Atomic Force Microscopy

BPD Basal Plane Dislocations

BJT Bipolar Junction Transistor

CRT Cathode Ray Display Tube

CVD Chemical Vapour Deposition

CTE Coefficient of Thermal Expansion

DLTS Deep Level Transient Spectroscopy

DUT Device Under Test

DBC Direct Bonded Copper

DPB Double Positioning Boundary

EV Electric Vehicle

EELS Electron Energy Loss Spectrometer

EDX Energy Dispersive X-ray

FEG Field Emission Gun

FIB-SEM Focused Ion Beam Scanning Electron Microscope

GaN Gallium Nitride

GTO Gate Turn-Off Thyristor

HRTEM High Resolution TEM

HTCVD High Temperature Chemical Vapour Deposition

HVDC High Voltage DC

HEV Hybrid Electric Vehicle

ICP Inductively Coupled Plasma

IGBT Insulated Gate Bipolar Transistor

JBS Junction Barrier Schottky

JTE Junction Termination Extension

MPS Merged PiN Schottky

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

MP Micropipes

NPT Non-Punch-Through

PSG Phosphosilicate Glass

PL Photoluminescence

PV photovoltaic

PDS Planar Diffusion Source

PT Punch-Through

RCA Radio Corporation of America

RIE Reactive Ion Etching

SEM Scanning Electron Microscopy

SRH Schockley-Read-Hall

SBD Schottky Barrier Diode

SBH Schottky Barrier Height

SIMS Secondary Ion Mass Spectroscopy

SM-JTE Space-Modulated JTE

TE Thermionic Emission

TFE Thermionic Field Emission

TED Threading Edge Dislocations

TSD Threading Screw Dislocations

TRPL Time Resolved Photoluminescence

TEM Transmission Electron Microscopy

UHV Ultra High Voltage

WBG Wide Band Gap

XPS X-Ray Photoelectron Spectroscopy

## List of Symbols

| Å                          | Lattice constant                                                |

|----------------------------|-----------------------------------------------------------------|

| A**                        | Richardson's constant (Am <sup>-2</sup> K <sup>-2</sup> )       |

| $\mathrm{D}_{\mathrm{a}}$  | Ambipolar diffusion constant                                    |

| $\mathbf{D}_{\mathbf{n}}$  | Electron diffusion constant                                     |

| $\mathrm{D}_{\mathrm{p}}$  | Hole diffusion constant                                         |

| $\mathrm{D_{it}}$          | Density of interface traps (cm <sup>-2</sup> eV <sup>-1</sup> ) |

| $\mathbf{E}$               | Electric field (V/cm)                                           |

| $\mathbf{E}_{\mathbf{C}}$  | Bottom of conduction band (eV)                                  |

| $\mathrm{E}_{\mathrm{F}}$  | Fermi energy level (eV)                                         |

| $E_{\text{FM}}$            | Fermi energy level in metal (eV)                                |

| $\mathrm{E}_{\mathrm{FS}}$ | Fermi energy level in semiconductor (eV)                        |

| $\mathbf{E}_{\mathbf{G}}$  | Bandgap energy (eV)                                             |

| Em                         | Peak electric field (V/cm)                                      |

| $\mathrm{E}_0$             | Vacuum energy level (eV)                                        |

| $E_{00}$                   | Characteristic energy (eV)                                      |

| h                          | Planck constant (Js)                                            |

| $I_{\mathrm{F}}$           | Diode forward current (A)                                       |

| ${ m I}_{ m RP}$           | Diode peak reverse current (A)                                  |

| $J_0$                      | Reverse saturation current density (A/cm²)                      |

| $J_{0,\mathrm{rec}}$       | Saturation recombination current density (A/cm²)                |

| $J_{\rm diff}$             | Diffusion current density (A/cm²)                               |

| $J_{\rm drift}$            | Drift current density (A/cm <sup>2</sup> )                      |

| $J_n$                      | Electron current density (A/cm <sup>2</sup> )                   |

| $J_{\rm p}$                | Hole current density (A/cm <sup>2</sup> )                       |

| L                          | Inductance (H)                                                  |

| La                         | Ambipolar diffusion length (cm)                                 |

| $m^*_{\mathrm{T}}$         | Tunneling effective mass (kg)                                   |

| $N_{\rm A}$                | Doping concentration (p-type) (cm <sup>-3</sup> )               |

| $N_{\mathrm{D}}$           | Doping concentration (n-type) (cm <sup>-3</sup> )               |

| $N_{\mathrm{DP}}$          | Doping concentration in the drift region (cm <sup>-3</sup> )    |

| $n_{\rm i}$                | Intrinsic carrier concentration (MV/cm)                         |

| $R_{\rm drift}$            | Drift layer resistance ( $\Omega$ -cm <sup>2</sup> )            |

| $R_{\text{on,diff}}$       | Differential on resistance ( $\Omega$ -cm <sup>2</sup> )        |

| Ron                        | Specific on resistance (Ω-cm <sup>2</sup> )                     |

| T                          | Temperature (K)                                                 |

| $\mathbf{t}_{\mathbf{rr}}$ | Reverse recovery time (s)                                       |

| $V_{ak} \\$                | Applied voltage (V)                                             |

| $V_{\mathrm{B}}$           | Blocking voltage (V)                                            |

| $V_{\rm bi}$               | Diode built-in voltage (V)                                      |

| $V_{\rm d}$                | Width of depletion region (cm)                                  |

| $V_{\mathrm{F}}$           | Forward voltage drop of overall PiN diode (V)                   |

|                            |                                                                 |

$V_{R}$ Reverse clamping voltage (V)  $V_{\rm M}$ Forward voltage drop of modulated PiN diode drift region (V)  $V_{\rm sat}$ Electron saturation velocity (cm)  $V_{\mathrm{T}}$ Thermal voltage (V) Width of the drift region (cm)  $W_{\rm d}$ Electron affinity for the semiconductor (V)  $\chi_{S}$ Vacuum permittivity (F/m) 03 Relative dielectric constant  $\epsilon_{\rm r}$ **Ideality factor** η λ Wavelength of light (cm) Electron mobility (cm<sup>2</sup>/Vs)  $\mu_n$ Hole mobility (cm<sup>2</sup>/Vs)  $\mu_p$ Carrier lifetime (s) τ Schockley-Read-Hall lifetime (s)  $\tau_{SRH}$ Metal-semiconductor barrier height (eV)  $\Phi_{\rm B}$ Work function of metal (eV)  $\Phi_{\mathrm{M}}$  $\Phi_n$ Fermi potential measured from the conduction band (eV)

Fermi potential measured from the valance band (eV)

Work function of semiconductor (eV)

$\Phi_{p}$

$\Phi_{\rm S}$

Chapter

Introduction

1

#### 1.1 Introduction

Nowadays, the improvement of energy efficiency is one of the most critical problems due to limited non-renewable fuel resources and an increased consciousness regarding climate change. Climate change is due to the significant increase of greenhouse gas emissions. One of the means to reduce greenhouse emissions is by employing renewable energy generation solutions such as wind and photovoltaic (PV) solar cells. In 2010, the world average ratio of electrical energy consumption to total energy usage was around 20% [1]. This ratio is estimated to increase rapidly in the future as the global energy demand is continuously increasing. It is expected that over 50% of all electrical power is converted so that it can be supplied to the loads in an optimal form [1].

Generally, the performance of semiconductor devices are the main limiting factor of power electronics efficiency. Therefore, the development of high-voltage and low-loss

power devices is vital. Figure 1-1 shows the main application areas of power electronic devices as a function of rated voltage, such as power supplies, power transmission systems, Hybrid Electric Vehicle (HEV), Electric Vehicle (EV may also be referred to as BEV or battery electric vehicles), motor control, traction, and robotics. In addition to efficiency, cost and reliability are also crucial. Silicon (Si) is the most commonly used semiconductor in power electronics devices. Although the performance of Si power devices has been substantially improved, they are at their practical limit due to increasing demand of power devices in high power applications where higher power density (higher current handling capability and higher blocking voltage), higher operating temperature and substantially higher switching frequency is required. Therefore, to realise such requirements, research has shifted towards looking at using Wide Band Gap (WBG) semiconductor materials due to their superior material properties, including Silicon Carbide (SiC), Gallium Nitride (GaN) and diamond. At the moment, SiC is the most promising candidate for high voltage, high power applications with commercial devices already on the market. The work carried out in this thesis intends to further develop 4H-SiC high voltage power electronics technology to meet the above-mentioned requirements of the future power network.

Figure 1-1: Main application area of power electronic devices as a function of rated voltage [1]

## 1.2 Background and Motivation

The aim of this thesis is to fabricate and characterise 4H-Silicon Carbide (4H-SiC) power diodes for high voltage applications with particular focus on improving the performance of 4H-SiC SBDs using novel metal-semiconductor interface treatment and 4H-SiC PiN diodes using high temperature processing techniques.

Despite the rapid development in the field of material growth over the past few years, reducing the defect densities of SiC substrate is still a critical challenge and is continuing to hinder the development of large area high current and high voltage devices, such as low carrier lifetimes. Macroscopic defects, such as triangular defects, that are generated during epitaxial growth can also considerably reduce the electrical performance of the power devices. Triangular defects can be found in almost all commercial 4H-SiC epitaxial wafers. This has provided motivation to study the impact of this surface morphological defect on the electrical performance of fabricated 4H-SiC PiN diodes.

A critical issue in high-voltage bipolar devices is improving the carrier lifetime. Material defects in 4H-SiC result in low carrier lifetimes. In order to improve the electrical characteristics of bipolar devices such as PiN diode, sufficient carrier lifetime of 4H-SiC material is crucial for realising low forward conduction losses and reducing the on-resistance. As reported by Hiyoshi and Kimoto [1-3] high temperature oxidation treatments can be used to enhance the carrier lifetime in the semiconductor material by 'repairing' carbon-vacancy related defects in high voltage PiN diodes. This is due to the removal of extra carbon atoms at the oxidising surface, which diffuse into the semiconductor bulk and reside on the vacant carbon locations. Therefore, the capability of performing high temperature oxidations is of great interest. In the study by Hiyoshi and Kimoto, they only explored thermal oxidation up to 1400°C, though, reassuringly, this was found to be significantly more effective at enhancing the carrier lifetime in the material for a certain oxidation time. The thermal oxidation Hitech furnace at Warwick enable research of thermally grown oxides at temperatures up to 1550°C which provided the motivation into further enhancing the carrier lifetime in high voltage 4H-SiC power devices as part of this thesis.

In addition to the above, further improvements to SiC SBDs are being sought by re-examining the Schottky metal contact. It has also been shown that [4] surface passivation treatments prior to metal deposition improve the electrical characteristics of the fabricated diode. There has been a recent increase in interest into molybdenum (Mo) Schottky contact [5, 6]. These have provided motivation for further research into the impact of various surface passivation techniques on Mo, Ni, and Ti based SiC Schottky diodes including the novel phosphorus pentoxide (P<sub>2</sub>O<sub>5</sub>) deposition treatment in order to enhance the electrical performance of the diodes [7]. The findings of this investigation can be potentially employed for MOS interface improvement.

## 1.3 Contribution of Knowledge

- It was shown for the first time the impact of triangular defects on switching characteristics of 4H-SiC PiN diodes fabricated on- and off-defects. Moreover, triangular defects were characterised using methods including AFM, SEM, Photoluminescence and HRTEM. Other complex structures were observed on the triangular defect using HRTEM such as double positioning boundary (DPB), which resulted in a leakage path through the drift region of the devices and increased the leakage current.

- Another particular novel contribution of this thesis is on improving the performance of 4H-SiC SBDs using a novel metal-semiconductor interface treatment and 4H-SiC PiN diodes using high temperature processing techniques to improve the carrier lifetime, on-state resistance and conductivity modulation of the diode. Carrier lifetime enhancement in 4H-SiC PiN diodes in this thesis was achieved using a

combined high temperature oxidation and successive argon annealing process at 1550°C for 1 hour. This resulted in an increase of nearly 45% of the reverse recovery current and approximately 40% of the carrier lifetime. The findings of this study could be potentially used for other 4H-SiC bipolar devices such as IGBTs, BJTs and thyristors.

Another contribution of knowledge in the work presented in this thesis is improving the quality of the 4H-SiC surface and the metal-semiconductor interface using Mo/Ti, and Ni-4H-SiC Schottky diodes. The most significant outcome of this investigation was the performance of P<sub>2</sub>O<sub>5</sub> treated Mo/SiC Schottky diodes which retained a barrier height equivalent to that of titanium, but with a leakage current lower than any Ni diode, seemingly combining the benefits of both a low- and high-SBH metal. Furthermore, P<sub>2</sub>O<sub>5</sub> treated Mo/SiC Schottky diodes were the only diodes to undergo any significant leakage current reduction after any of the pre-treatments exhibiting exceptionally low leakage, even at 300°C. XPS and SIMS analysis on all Mo/SiC SBDs revealed that the stoichiometry of the SiC underneath the contact was enhanced using P<sub>2</sub>O<sub>5</sub> treatment and that traces of P<sub>2</sub>O<sub>5</sub> were found after removal of the passivation layer and post-treatment metallisation. It was also found that the Mo-4H-SiC interface on the P<sub>2</sub>O<sub>5</sub> treated sample was very sharp and uniform compared to the untreated sample where Mo-SiC interface looks uneven and cloudy. The developed novel metal-semiconductor interface treatment can be potentially used for MOS interface improvements.

#### 1.4 Thesis Outline

Chapter 2 gives a background on the application areas of the power devices being developed in this work and provides an insight into performance benefits that 4H-SiC can offer over existing technologies. In addition to the material advantages of 4H-SiC, its crystal structures, bulk growth challenges and the material defects are also discussed here. Then, finally, a discussion on the present status of SiC power diodes is given.

Chapter 3 provides an introduction into the physics of operation of PiN and Schottky diodes and the physics of the semiconductor. The fundamental operating principles of these devices are outlined which are important for design and optimisation of device structures. This includes the analysis of the on-state, switching, and reverse blocking behaviour of the diodes.

Chapter 4 presents the 4H-SiC fabrication technology for the fabrication of 4H-SiC PiN diodes and Schottky diodes in this thesis. Following this, the device packaging process of the fabricated devices is presented. Chapter 5 outlines the characterisation techniques that have been employed when characterising the high voltage 4H-SiC PiN and Schottky diodes. First, the electrical characterisation techniques are discussed including on-state characteristics and reverse blocking at a range of temperatures as well as switching behaviour of the PiN diodes. Subsequently, the physical characterisation techniques of the 4H-SiC wafers are discussed.

In Chapter 6, the impact of a surface morphological defect, the triangular defect, on fabricated 4H-SiC PiN diodes is explored. This Chapter provides a background on macroscopic defects in Silicon Carbide material and the importance of this study. This Chapter first discusses the electrical performance of devices fabricated in areas with no visible defects. It then uses the device fabrication process as a benchmark for characterising the devices with the same active area and fabrication process that are intentionally fabricated on the triangular defect. Following this, the Chapter provides detailed results on the material characterisation, and electrical performance of the fabricated 4H-SiC PiN diodes on and off-defects and clamped inductive switching tests results.

The optimised PiN diode fabrication process in Chapter 6 is then used in Chapter 7 to study the application of a combined high temperature thermal oxidation and annealing process to 4H-SiC PiN diodes with 35 µm thick drift regions, the aim of which was to increase the carrier lifetime in the 4H-SiC and improve their electrical performance. Diodes were fabricated using 4H-SiC material and underwent a thermal oxidation and argon anneal process. Reverse recovery tests indicated a significant carrier lifetime enhancement due to increase of minority carriers in the drift region. The switching results illustrate that the use of this process is a highly effective and efficient way of enhancing the electrical characteristics of high voltage 4H-SiC bipolar devices.

In Chapter 8, the impact of surface passivation treatments on both the SiC surface and the metal-semiconductor interface prior to the device fabrication is

investigated. The findings of this investigation can be potentially employed for MOS interface improvement. To do so, SBDs were fabricated on treated SiC surfaces, so that metal-semiconductor junctions could be used to evaluate the quality of this surface, using a range of metals including Mo, Ni, and Ti. Various surface passivation treatments were performed on 4H-SiC surface, including a novel surface passivation process. SBDs developed after the removal of these passivating layers were compared to those on untreated (control) surfaces and analysed physically using XPS, SIMS, TEM, and SEM, and electrically using I-V and I-V-T characteristics as well as inhomogeneity characterisation familiar to Schottky analysis.

Finally, Chapter 9 presents the conclusions of this thesis as well as suggestions for further work.

Chapter

2

## Power Electronic Devices and Silicon Carbide

## 2.1 Background

The first power rectifier was invented in 1902 by Peter Cooper Hewitt which was a mercury-vapour rectifier used to rectify AC power into DC power. This device was used to drive industrial motors as well as high voltage DC (HVDC) lines used in electric railways in London. After the development of solid-state semiconductor technology, diodes in the form we know today replaced mercury-arc rectifiers. Nowadays, power diodes are used in almost all high voltage applications, such as, transportation and automotive applications, specifically in hybrid and electric vehicles as well as public transportation such as buses and trains, marine, aviation, motor drive applications and

in renewable energy such as on-shore and off-shore wind turbines, photovoltaic solar cells and in power lines such as HVDC, and so on. To improve the performance of a power converter system it is critical to enhance the performance of the power semiconductor devices within the system. The viability of HVDC systems is highly dependent on the performance of the required power electronics to convert between voltage levels. These can include rectifiers or switches that control the electric power (voltage, current, frequencies, etc.)[8].

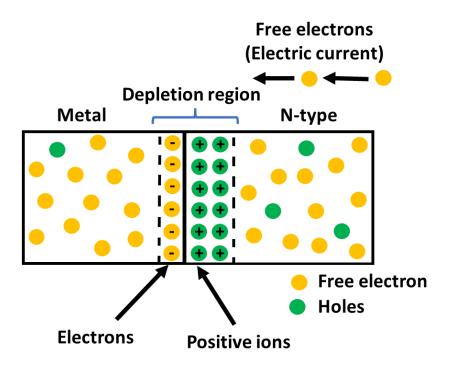

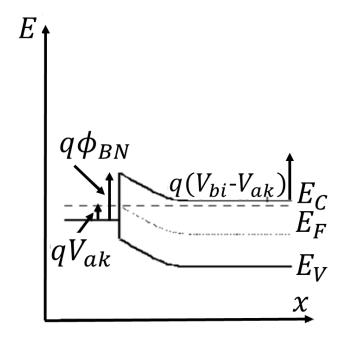

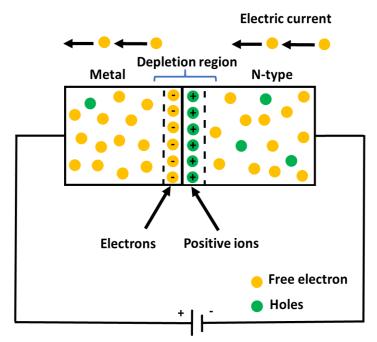

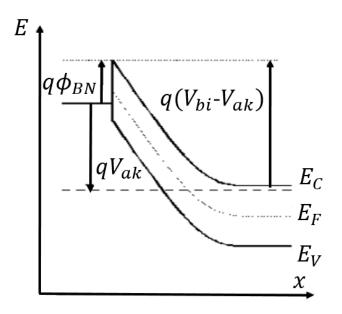

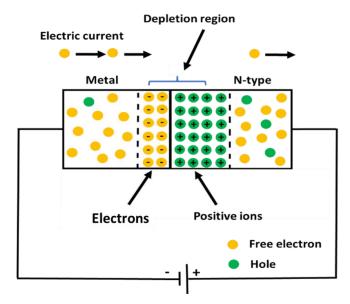

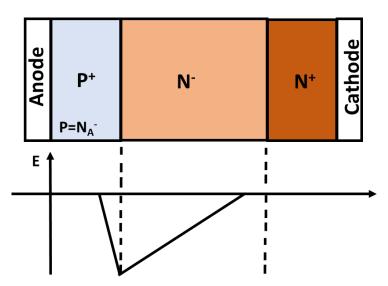

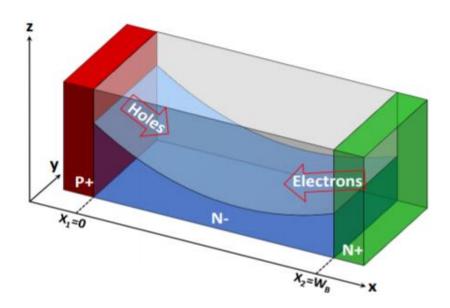

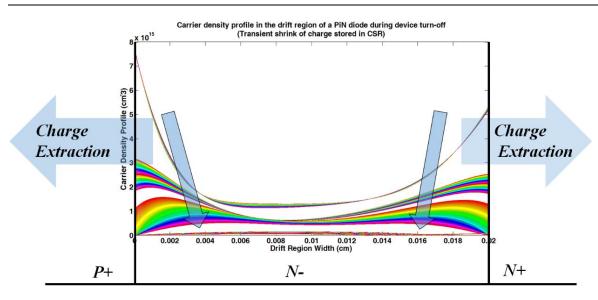

Advancements in the processing of Silicon (Si) semiconductor technology has resulted in robust and cost-effective power electronic devices, which are the basis of the power industry today. The low defect density, high yield and large sizes of Si wafers have resulted in the high quality and low cost material that currently drives the power electronics industry. Since 1947, when the transistor effect was discovered by Bardeen and Brattain [9], an enormous number of fundamental studies were carried out focusing on material physics and process technologies in Si. Applications of Si power devices started in the mid-1950s using bipolar junction transistors (BJTs) [8] in medium power systems applications. This was followed by the development of thyristors [10] or Gate Turn-Off thyristors (GTOs) [11] in the 1960s for high power systems applications. Power Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) were presented in the 1970s to substitute the low voltage BJTs offering fast switching speed [12, 13]. Later on, the Insulated Gate Bipolar Transistor (IGBT), which is the combination of BJT and MOSFET, was designed for high power applications [14]. Intrinsically, the oxidation of Si, forming silicon dioxide (SiO<sub>2</sub>), results in promising