A Thesis Submitted for the Degree of PhD at the University of Warwick

**Permanent WRAP URL:**

http://wrap.warwick.ac.uk/149978

## **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# A Fast-acting Protection Scheme for Series Compensators in a Medium-Voltage Network

Erfan Bashar School of Engineering University of Warwick

Dissertation submitted for the degree of

Doctor of Philosophy

January 2020

# **Contents**

| List of Figures                                              | iv  |

|--------------------------------------------------------------|-----|

| List of Tables                                               | ix  |

| Acknowlegement                                               | хi  |

| Declarationx                                                 | αii |

| Abstractx                                                    | αii |

| Publication Listx                                            | iv  |

| List of Acronymsx                                            | ΚV  |

| List of Variables and Symbolsx                               | vi  |

|                                                              |     |

| 1 INTRODUCTION                                               | . 1 |

| 1.1 UTILITIES VULNERABLE TO THE FAULT IN THE NETWORK         |     |

| 1.2 PROTECTION TECHNIQUE BY USING THYRISTORS AND A VARISTOR  |     |

| 1.3 TEMPERATURE ISSUE AND HEATSINK SYSTEM1                   |     |

| 1.4 CONTRIBUTIONS                                            |     |

|                                                              |     |

| 1.5 THESIS OUTLINE                                           |     |

| 1.6 REFERENCES                                               | 17  |

|                                                              |     |

| 2 POWER COMPENSATORS AND PROTECTION SCHEMES                  |     |

| 2.1 INTRODUCTION                                             |     |

| 2.2 POWER FLOW AND VOLTAGE CONTROL BY COMPENSATORS           |     |

| 2.2.1 Combined Series-Shunt/Series Compensation Technologies |     |

| 2.2.2 UPFC (Unified power flow controller)                   |     |

| 2.2.3 Static Synchronous Series Compensator (SSSC)           |     |

| 2.2.4 Back to Back System                                    |     |

| 2.3 COMPARISON BETWEEN A B2B VSC-LINK AND A SSSC2            |     |

| 2.3.1 A B2B VSC-LINK and a SSSC                              |     |

| 2.3.2 Disadvantages of Series Compensators                   |     |

| 2.3.3 Comparison between Different Compensator Systems       |     |

| 2.4 PROTECTION SCHEMES4                                      |     |

| 2.4.1 Fast-Breaking Mechanical Devices4                      |     |

| 2.4.2 Basic Solid-State/Hybrid Circuit Breakers              |     |

| 2.4.3 CL-CBs with Ordinary Resistor                          |     |

| 2.4.4 CL-CBs with Superconductors4                           | 12  |

| 2.4.5 CL-CBs with Inductive Components                  | 43  |

|---------------------------------------------------------|-----|

| 2.4.6 CL-CB with Semiconductor Power Switches           | 44  |

| 2.4.7 MOV- Spark Gap Mechanism                          | 45  |

| 2.4.8 Comparing the Protection Mechanisms               | 47  |

| 2.5 DC OFFSET                                           | 48  |

| 2.6 PHASE CHANGE MATERIAL HEATSINK                      | 50  |

| 2.7 CONCLUSION                                          | 53  |

| 2.8 REFERENCES                                          | 54  |

| 3 A FAST-ACTING PROTECTION SCHEME FOR MV SERIES COMPENS |     |

| 3.1 INTRODUCTION                                        |     |

| 3.2 STATIC SYNCHRONOUS SERIES COMPENSATOR               | 69  |

| 3.2.1 Without the SSSC                                  |     |

| 3.2.2 With using the SSSC                               |     |

| 3.2.3 Closed-Loop Control System                        |     |

| 3.2.4 Clarke Transformation                             |     |

| 3.2.5 Dq0 Transformation                                | 76  |

| 3.2.6 PI Control and Closed-Loop system                 |     |

| 3.3 THYRISTOR-BASED PROTECTION SCHEME WITH VARISTOR     | 82  |

| 3.3.1 Protection system design                          | 83  |

| 3.3.2 Timing Diagram                                    |     |

| 3.4 THERMAL MODELS AND DEVICE LIMITS                    | 86  |

| 3.4.1. Thermal Model                                    | 86  |

| 3.4.2 Device Limits                                     |     |

| 3.5 GENERAL SELECTION PROCEDURE FOR THE THYRISTOR AND   |     |

| VARISTOR                                                | 91  |

| 3.6 SIMULATION RESULTS                                  | 93  |

| 3.6.1 Conventional Protection Method                    | 93  |

| 3.6.2 Proposed Protection Method                        | 98  |

| 3.7 EXPERIMENTAL RESULTS                                | 106 |

| 3.7.1 Conventional Protection Method                    | 107 |

| 3.7.2 Proposed Protection Technique                     | 109 |

| 3.8 CONCLUSION                                          | 112 |

| 3.9 REFERENCES                                          | 113 |

|                                                         |     |

| 4 INVESTIGATING THE DC OFFSET PHENOMENA IN MEDIUM VOLTA | AGE |

| NETWORKS                                                |     |

| 4.1 INTRODUCTION                                                                                              | 117 |

|---------------------------------------------------------------------------------------------------------------|-----|

| 4.2 FUNDAMENTALS & MATHMATICS                                                                                 | 120 |

| 4.2.1 Synchronous Machines                                                                                    | 120 |

| 4.2.2 Induction Machines                                                                                      | 135 |

| 4.3 EFFECT OF LOCATION AND NUMBER OF MACHINES                                                                 | 141 |

| 4.4 CONCLUSION                                                                                                | 143 |

| 5 A METHOD TO CONTAIN THE TEMPERATURE RISE OF A PRES<br>THYRISTOR DURING A SHORT CIRCUIT PROTECTION OPERATION |     |

| 5.1 INTRODUCTION                                                                                              | 147 |

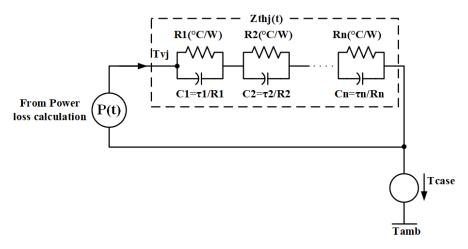

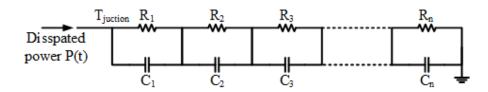

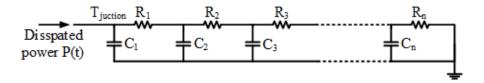

| 5.3 THERMAL MODEL                                                                                             | 152 |

| 5.3.1 Transforming the Foster Model to the Cauer Model                                                        | 154 |

| 5.4 METHODOLOGY                                                                                               | 157 |

| 5.5 SIMULATION RESULTS                                                                                        | 160 |

| 5.6 EXPERIMENTAL RESULTS                                                                                      | 166 |

| 5.7 SIMULATION RESULTS IN THE MEDIUM VOLTAGE LEVEL                                                            | 171 |

| 5.8 CONCLUSION                                                                                                | 176 |

| 6 CONCLUSION                                                                                                  | 170 |

| 6.1 CONTRIBUTIONS                                                                                             |     |

|                                                                                                               |     |

| 6.2 FUTURE WORK                                                                                               | 181 |

| Appendix I                                                                                                    | 182 |

# **List of Figures**

| Figure 1.1: A schematic of a medium voltage network                                                            |

|----------------------------------------------------------------------------------------------------------------|

| Figure 1.2: A schematic of a static synchronous series compensator 4                                           |

| Figure 1.3: A schematic of a medium voltage network                                                            |

| Figure 1.4: The fault current passing through SSSC without protection                                          |

| Figure 1.5: A protection method                                                                                |

| Figure 1.6: An MV circuit breaker [9]10                                                                        |

| Figure 1.7: A thyristor crowbar [10]10                                                                         |

| Figure 1.8: A Varistor [11]                                                                                    |

| Figure 1.9: A damaged thyristor during a failure due to the temperature rise [12]                              |

| Figure 1.10: The conventional heatsinks [13]                                                                   |

| Figure 2.1: Configuration of UPFC: shunt and series converters are on substation and ending sides respectively |

| Figure 2.2: A Schematic diagram of the SSSC                                                                    |

| Figure 2.3: A Schematic of the Back to Back Coveter system                                                     |

| Figure 2.4: A schematic of the case study                                                                      |

| Figure 2.5: a) A schematic of B2B VSC b) A schematic of SSSC30                                                 |

| Figure 2.6: Voltage magnitudes at each feeder end before and after                                             |

| compensation by SSSC and B2B VSC - link                                                                        |

| Figure 2.7: Power losses of B2B VSC - link                                                                     |

| Figure 2.8: Power losses of SSSC                                                                               |

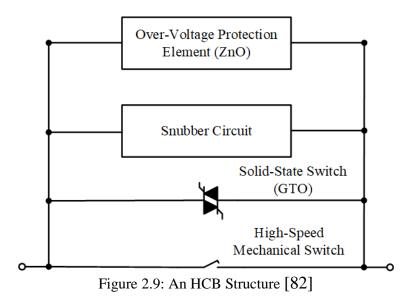

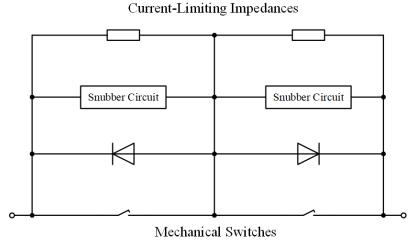

| Figure 2.9: An HCB Structure [82]                                                                              |

| Figure 2.10: Hybrid CL-CB with separated current-limiting path [82] 42                                         |

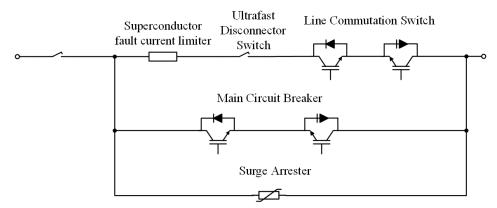

| Figure 2.11: A superconducting HCB [82]43                                                                      |

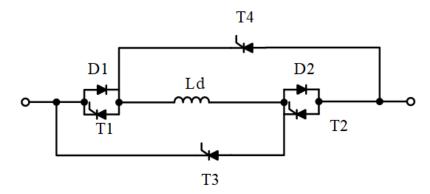

| Figure 2.12: A solid-state CL-CB with an AC inductor and a DC inductor [82]                                    |

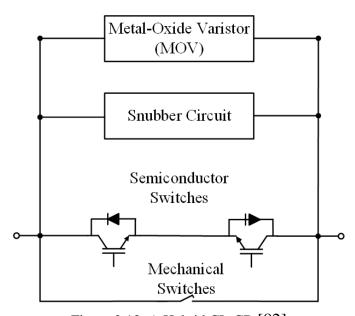

| Figure 2.13: A Hybrid CL-CB [82]                                                                               |

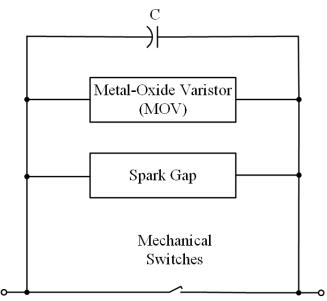

| Figure 2.14: A MOV-GAP mechanism45                                                                             |

| Figure 2.15: A MOV-GAP mechanism [92]                                                                          |

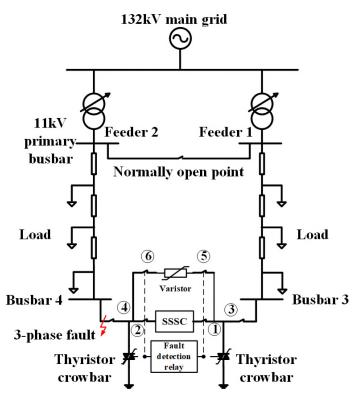

| Figure 3.1 : Typical MV network with multiple feeders including SSSC 67                                        |

| Figure 3.2: A schematic of SSSC                                                                                |

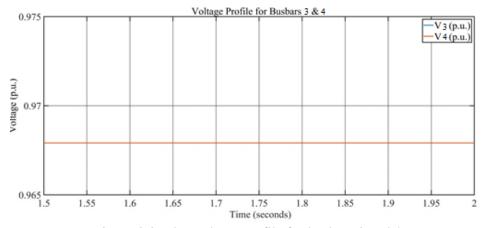

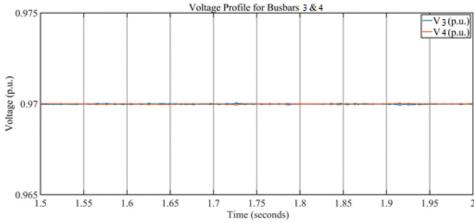

| Figure 3.3: The Voltage profile for busbars 3 and 4                                                                   | 1 |

|-----------------------------------------------------------------------------------------------------------------------|---|

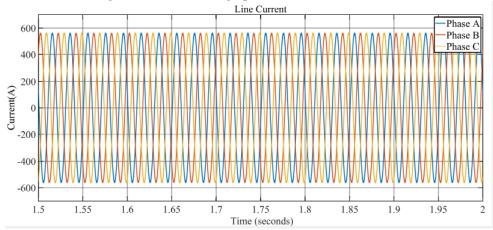

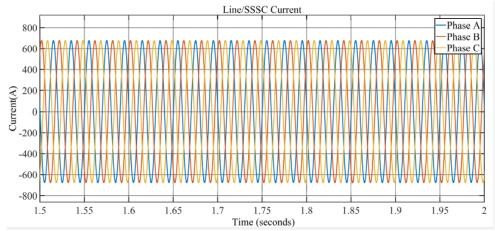

| Figure 3.4: The line current7                                                                                         | 1 |

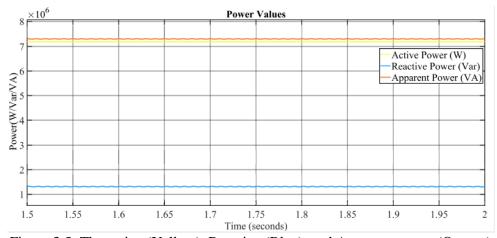

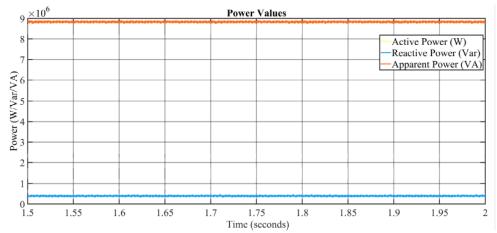

| Figure 3.5: The active (Yellow), Reactive (Blue), and Apparent power (Orange)                                         |   |

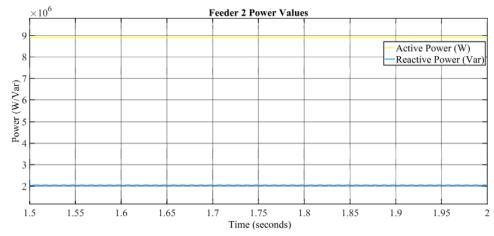

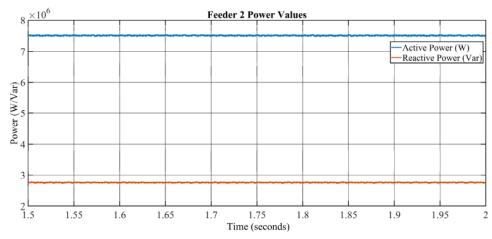

| Figure 3.6: The power values for Feeder 27                                                                            | 2 |

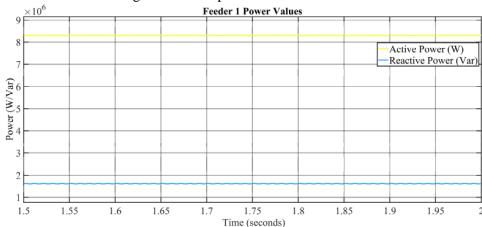

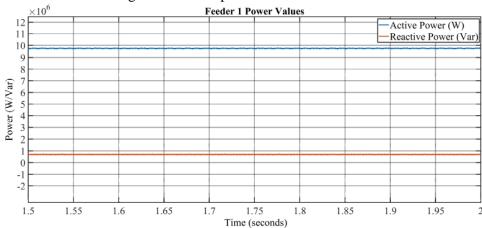

| Figure 3.7: The power values for Feeder 17                                                                            | 2 |

| Figure 3.8: The Voltage profile for Busbars 3 and 47                                                                  | 3 |

| Figure 3.9: The line current7                                                                                         | 3 |

| Figure 3.10: The active (Yellow), Reactive (Blue), and Apparent power (Orange)                                        | 3 |

| Figure 3.11: The power values for Feeder 2                                                                            |   |

| Figure 3.12: The power values for Feeder 17                                                                           |   |

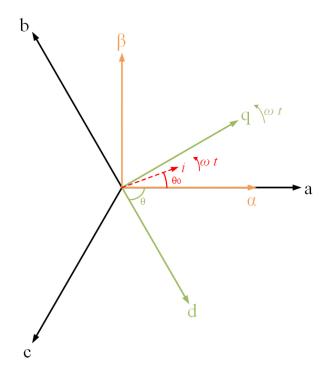

| Figure 3.13: Relationship between ABC, qdo and αβ coordinate reference frames                                         |   |

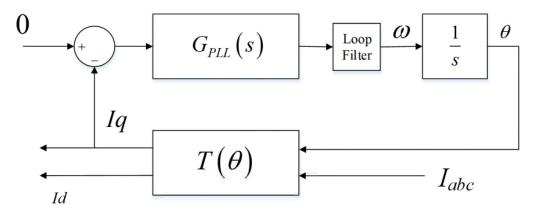

| Figure 3.14: A phase-locked loop control system7                                                                      | 8 |

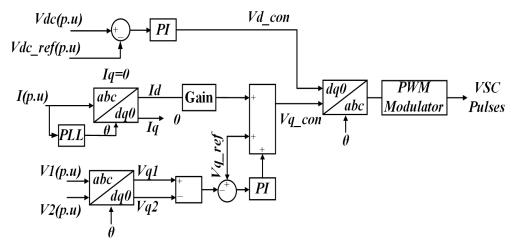

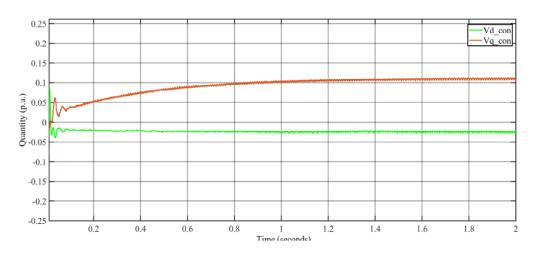

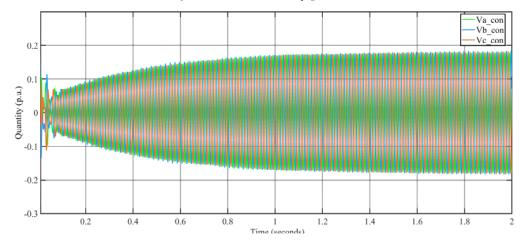

| Figure 3.15: Closed-loop controller for voltage-sourced converter (VSC) 7                                             | 9 |

| Figure 3.16: $V_d$ and $V_q$ quantities8                                                                              | 1 |

| Figure 3.17: PWM reference signals 8                                                                                  | 1 |

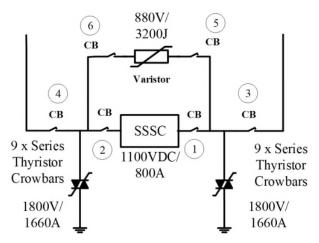

| Figure 3.18: Schematic of proposed method by using both thyristor crowbars and Varistor                               | 3 |

| Figure 3.19: Protection circuit schematic8                                                                            | 4 |

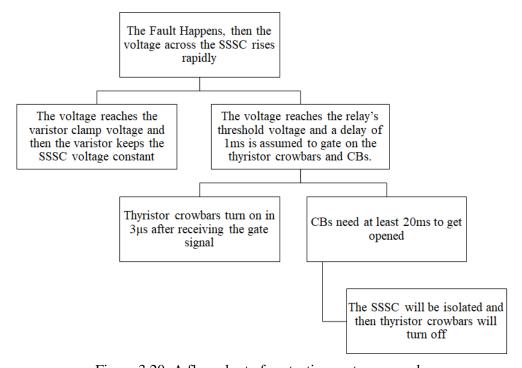

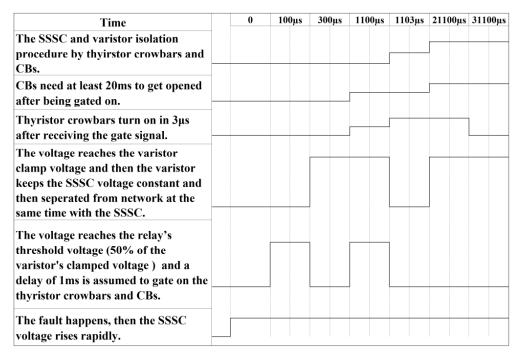

| Figure 3.20: A flow chart of protection system procedure                                                              |   |

| Figure 3.21: A timing diagram of the protection system procedure 8                                                    | 5 |

| Figure 3.22: A typical Foster thermal model for IGBT, PiN Diode and Thyristo                                          |   |

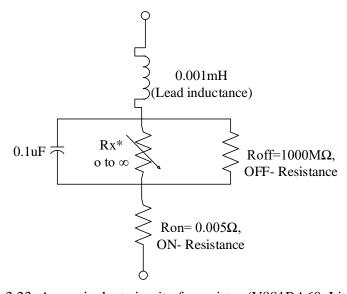

| Figure 3.23: An equivalent circuit of a varistor (V881BA60, LittleFuse)8                                              | 9 |

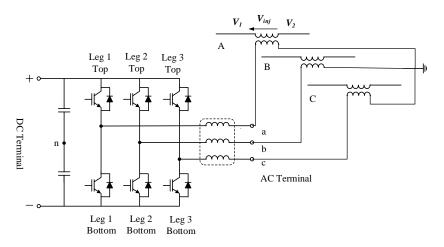

| Figure 3.24: A schematic of three phase VSC-SSSC connected to the network through a three-phase coupling transformer9 | 3 |

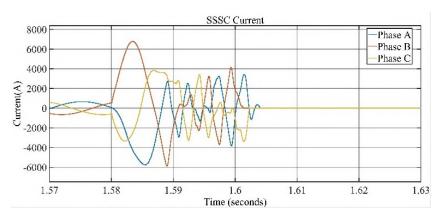

| Figure 3.25: The fault current passing through SSSC- Conventional Method . 9                                          | 5 |

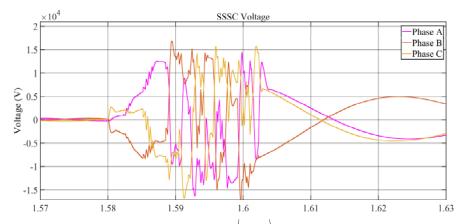

| Figure 3.26: The voltage of SSSC during the fault without protection- Conventional Method                             | 5 |

| Figure 3.27: The fault current level at fault point9                                                                  | 5 |

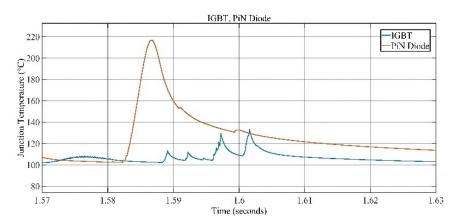

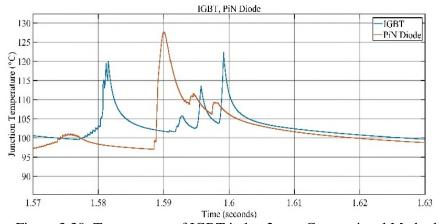

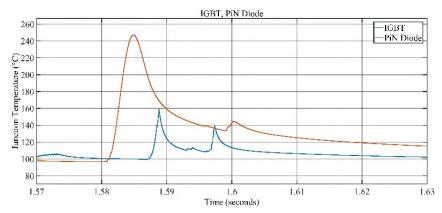

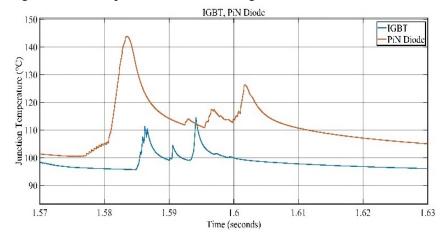

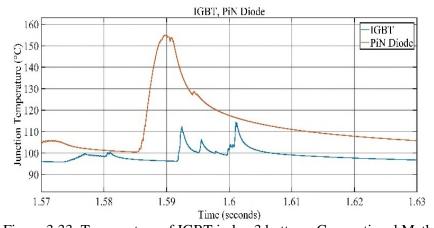

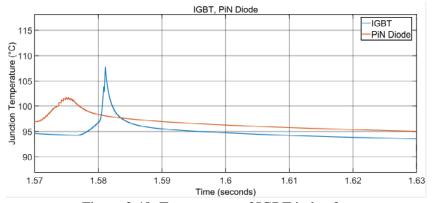

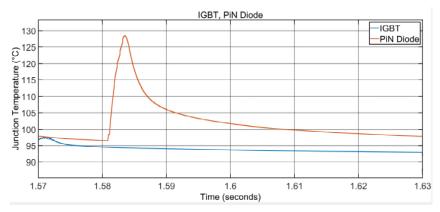

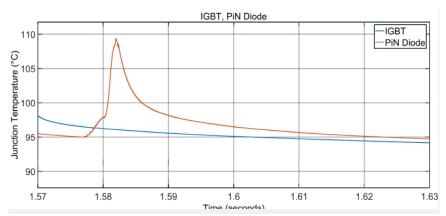

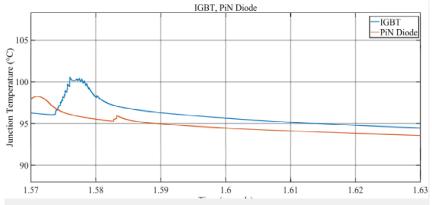

| Figure 3.28: Temperature of IGBT in leg 1 top- Conventional Method9                                                   | 6 |

| Figure 3.29: Temperature of IGBT in leg 1 bottom- Conventional Method 9                                               | 6 |

| Figure 3.30: Temperature of IGBT in leg 2 top- Conventional Method 96         |

|-------------------------------------------------------------------------------|

| Figure 3.31: Temperature of IGBT in leg 2 bottom- Conventional Method 97      |

| Figure 3.32: Temperature of IGBT in leg 3 top- Conventional Method 97         |

| Figure 3.33: Temperature of IGBT in leg 3 bottom- Conventional Method 97      |

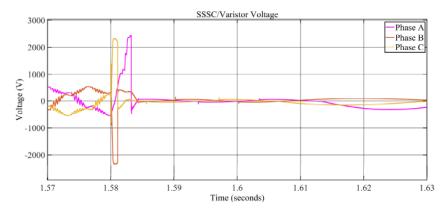

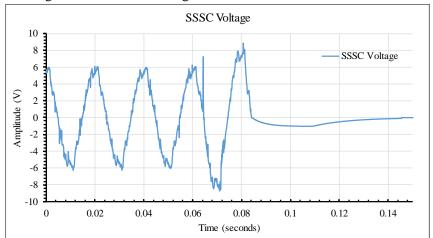

| Figure 3.34: Voltage of SSSC/Varistor- Proposed Method                        |

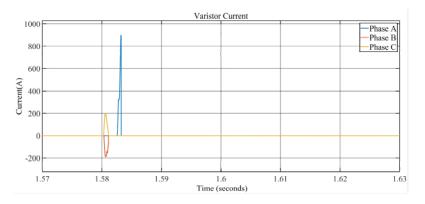

| Figure 3.35: Varistor current- Proposed Method                                |

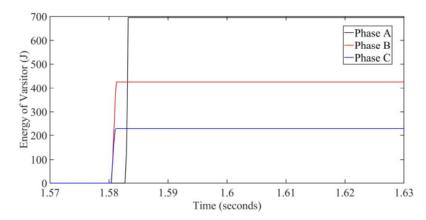

| Figure 3.36: Varistor's absorbed energy during fault                          |

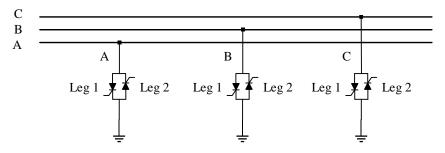

| Figure 3.37: Thyristor crowbars schematic of the connection to the network 99 |

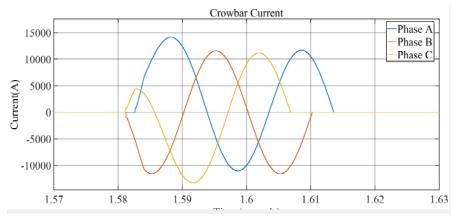

| Figure 3.38: Thyristor current during fault- Proposed Method 100              |

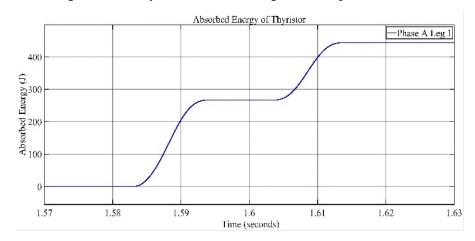

| Figure 3.39: Absorbed energy by thyristor in phase A leg 1 100                |

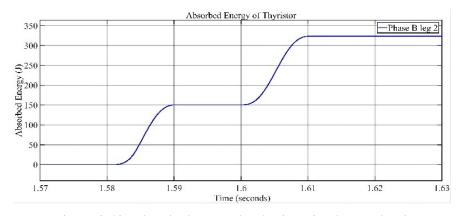

| Figure 3.40: Absorbed energy by thyristor in phase B leg 2 100                |

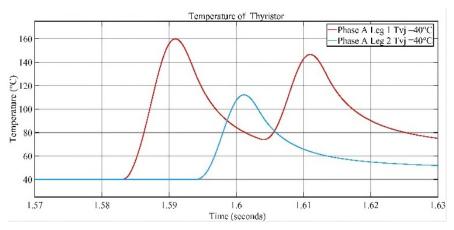

| Figure 3.41: Temperature of thyristor crowbar in phase A- Proposed Method     |

|                                                                               |

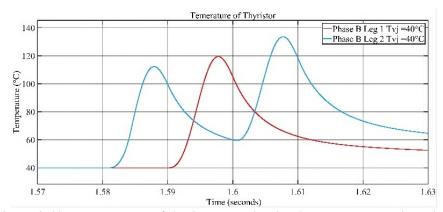

| Figure 3.42: Temperature of thyristor crowbar in phase B- Proposed Method     |

|                                                                               |

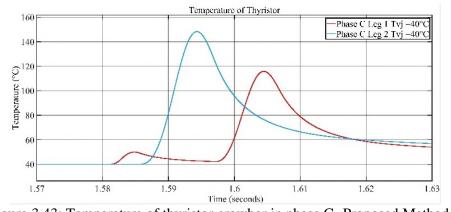

| Figure 3.43: Temperature of thyristor crowbar in phase C- Proposed Method     |

|                                                                               |

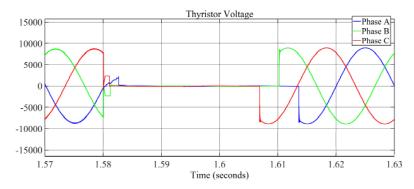

| Figure 3.44: Thyristor Voltage- Proposed Method 102                           |

| Figure 3.44: Thyristor Voltage- Proposed Method                               |

|                                                                               |

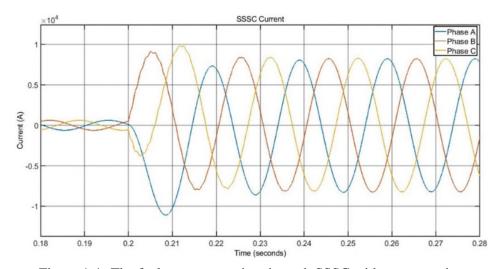

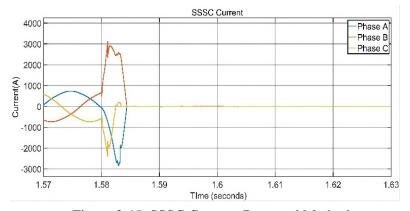

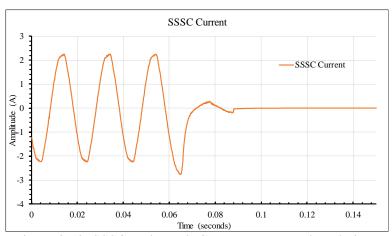

| Figure 3.45: SSSC Current- Proposed Method                                    |

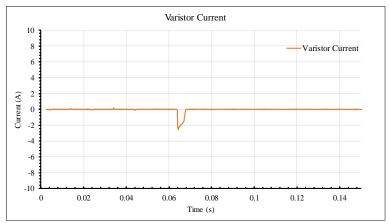

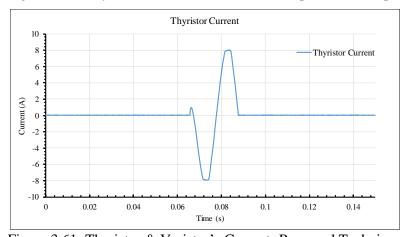

| Figure 3.60: Thyristor & Varistor's Current- Proposed Technique 110                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

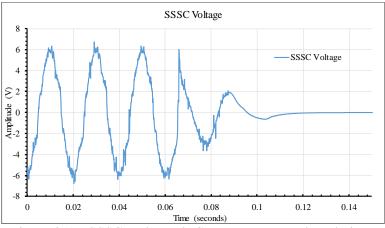

| Figure 3.61: Thyristor & Varistor's Current- Proposed Technique 110                                                                                                       |

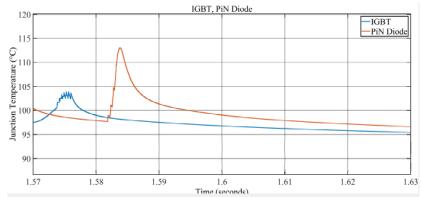

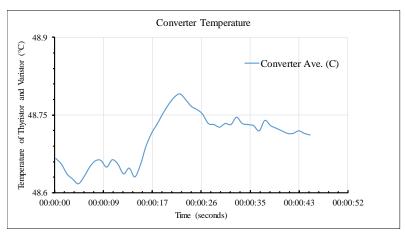

| Figure 3.62: Temperature variation of IGBT- Proposed technique                                                                                                            |

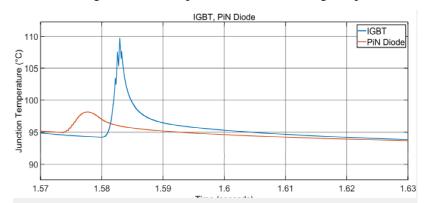

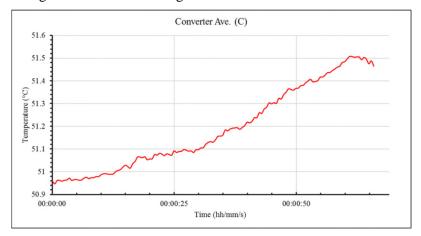

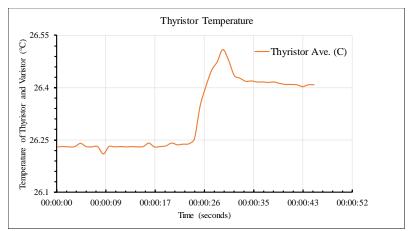

| Figure 3.63: Temperature variation of thyristor- Proposed technique 111                                                                                                   |

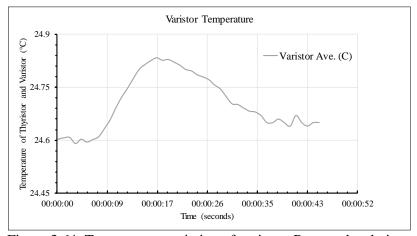

| Figure 3.64: Temperature variation of varistor- Proposed technique 111                                                                                                    |

| Figure 4.1: System diagram                                                                                                                                                |

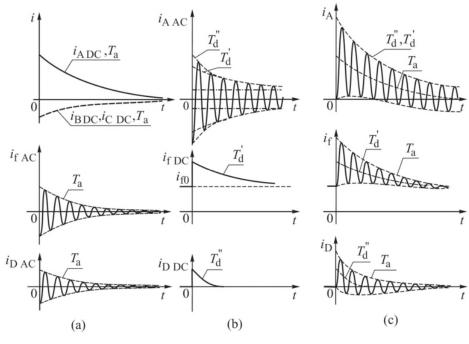

| Figure 4.2: Short-circuit currents in the round rotor generator [6] 121                                                                                                   |

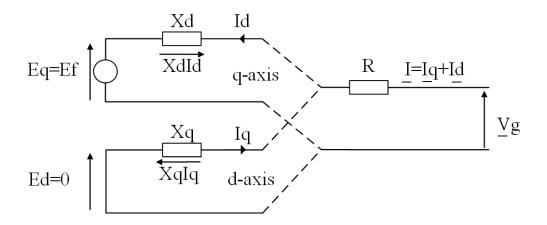

| Figure 4.3: The equivalent circuit of d-axis and q-axis of a synchronous machine in the steady state [6]                                                                  |

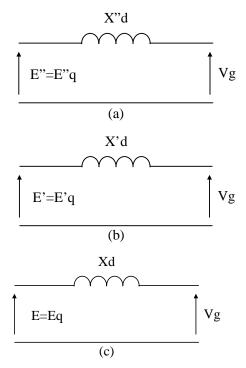

| Figure 4.4: Equivalent circuit for a synchronous generator on no load condition in (a) the subtransient state; (b) the transient state; (c) the steady state [6] 123      |

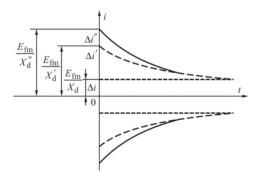

| Figure 4.5: Envelopes of the three characteristic AC components of the short-circuit current [6]                                                                          |

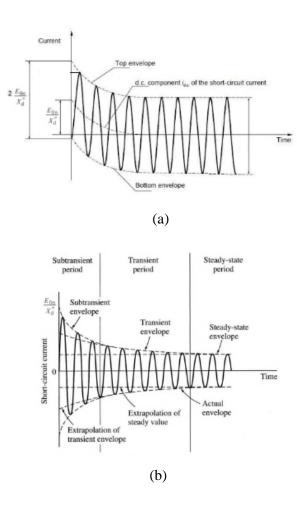

| Figure 4.6: Envelopes of the AC and DC components of the short-circuit current. (a) Phase current and corresponding DC component. (b)  Corresponding AC components [7, 8] |

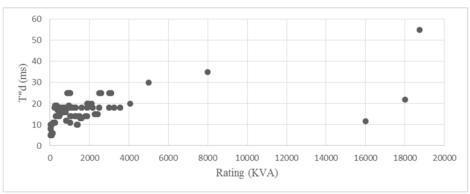

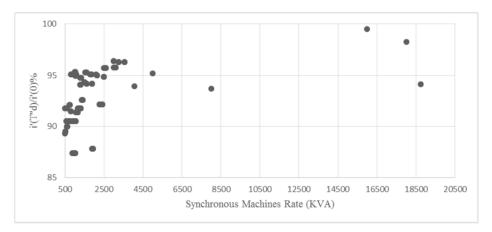

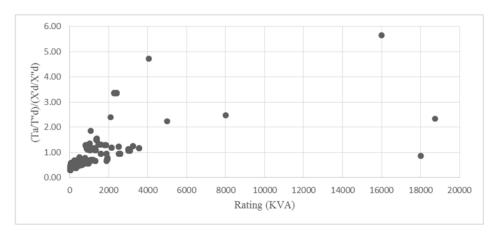

| Figure 4.7: Synchronous machine: T''d vs. rating                                                                                                                          |

| Figure 4.8: Synchronous machine: the ratio of transient current amount in subtransient time constant period to maximum value of transient current vs. rating              |

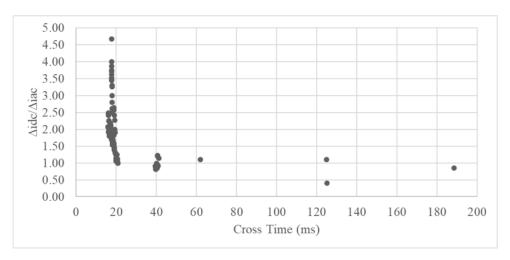

| Figure 4.9: Synchronous machine: Δidc/Δiac vs. cross time                                                                                                                 |

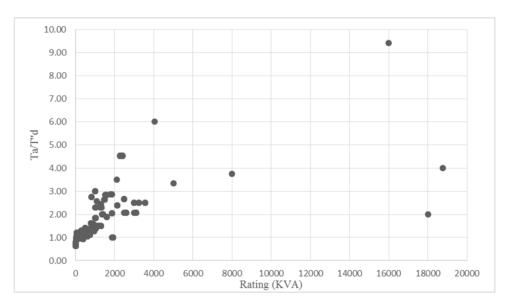

| Figure 4.10: Synchronous machine, Ta/T"d vs. machines rating                                                                                                              |

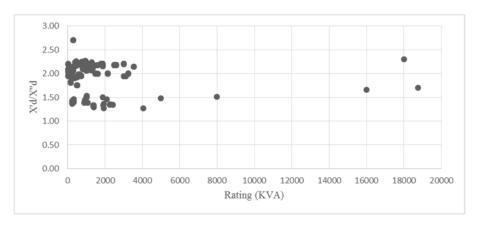

| Figure 4.11: Synchronous machine: X'd/X''d vs. rating                                                                                                                     |

| Figure 4.12: Synchronous machine: (Ta/T''d)/(X'd/X''d) vs. rating 134                                                                                                     |

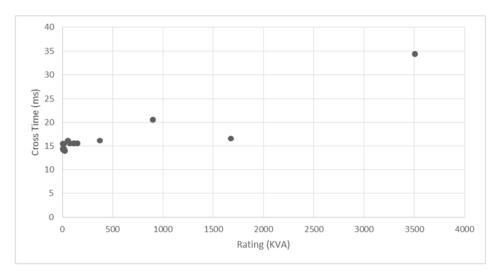

| Figure 4.13: Synchronous Machine: Cross time (ms) vs. rating (kVA) 134                                                                                                    |

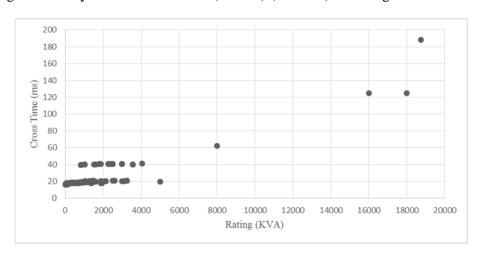

| Figure 4.14: Three-phase short-circuit fault at the terminals of a double-cage induction motor from no load: components of phase short-circuit current [13].              |

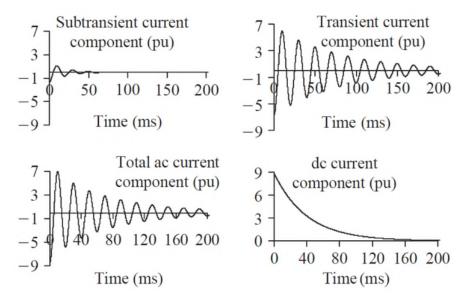

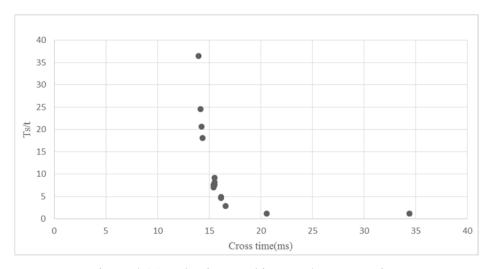

| Figure 4.15: Induction machines, Ts/t vs. cross time                                                                                                                      |

| Figure 4.16: Induction machines, cross time vs. rating (kVA) 140                                                                                                          |

| Figure 5.1: Typical MV network with multiple feeders linked by SSSC 149                                                                                                   |

| Figure 5.2: The process of the phase changing for a PCM                                                                                                                   |

| Figure 5.3: Foster thermal equivalent circuit model                                                                                                                       |

| Figure 5.4: Cauer thermal equivalent circuit model                                                                                                                        |

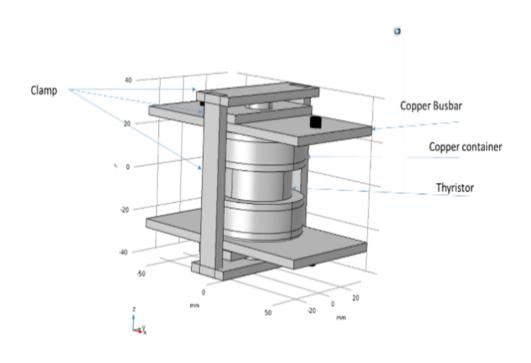

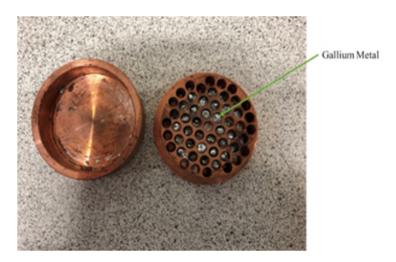

| Figure 5.5: Structure diagram of 600A/1600V PCM integrated press-pack                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| thyristor                                                                                                                                                                                                           |

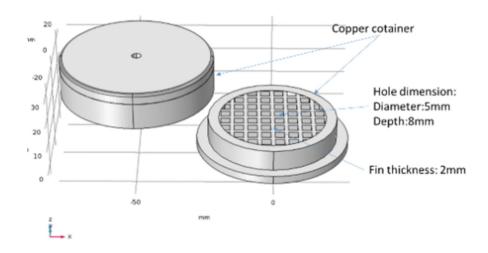

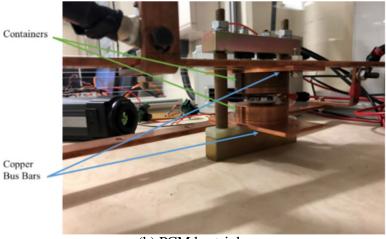

| Figure 5.6: Designed container for holding PCM                                                                                                                                                                      |

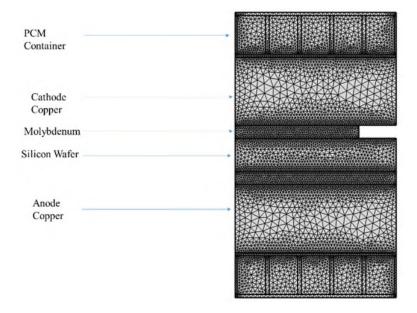

| Figure 5.7: FEM model in COMSOL Structure scheme in COMSOL, number of elements: 47400                                                                                                                               |

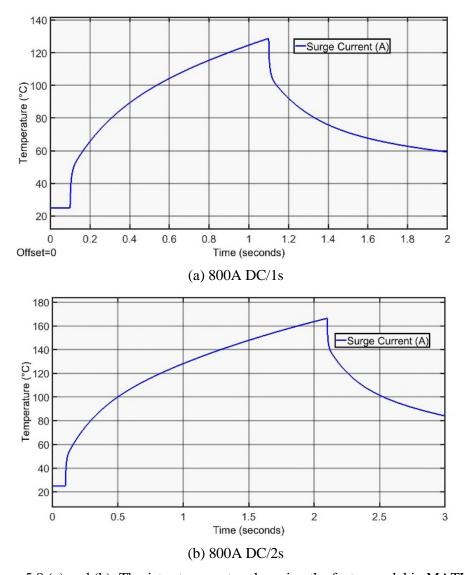

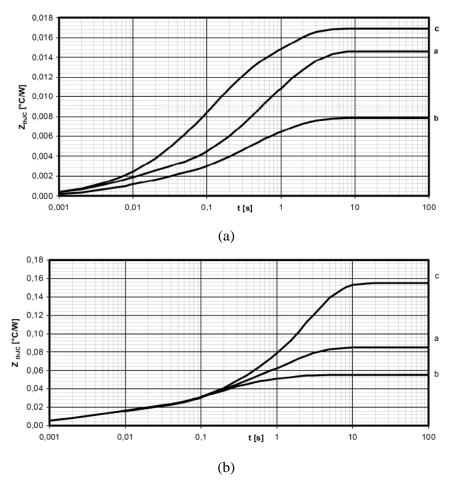

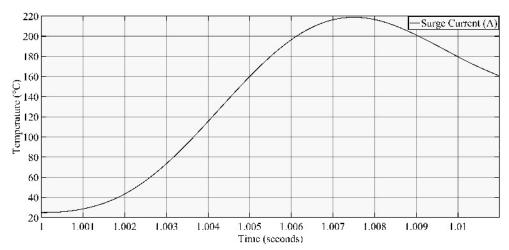

| Figure 5.8 (a) and (b): Thyristor temperature by using the foster model in MATLAB                                                                                                                                   |

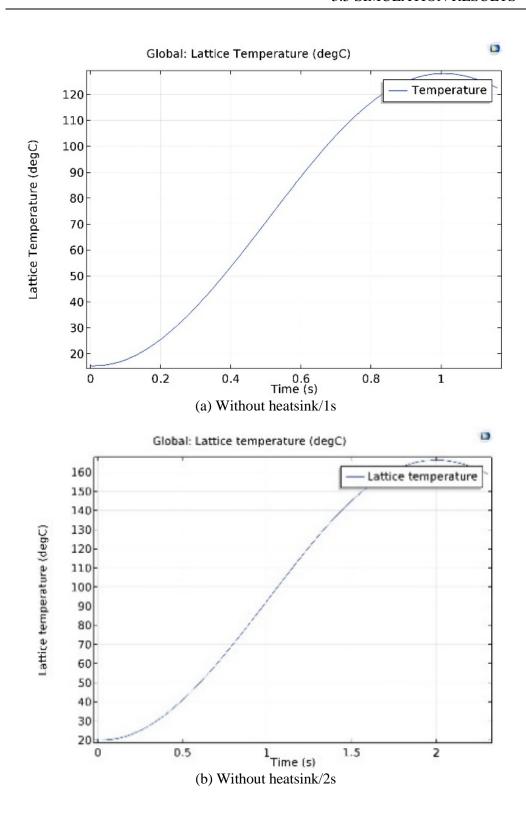

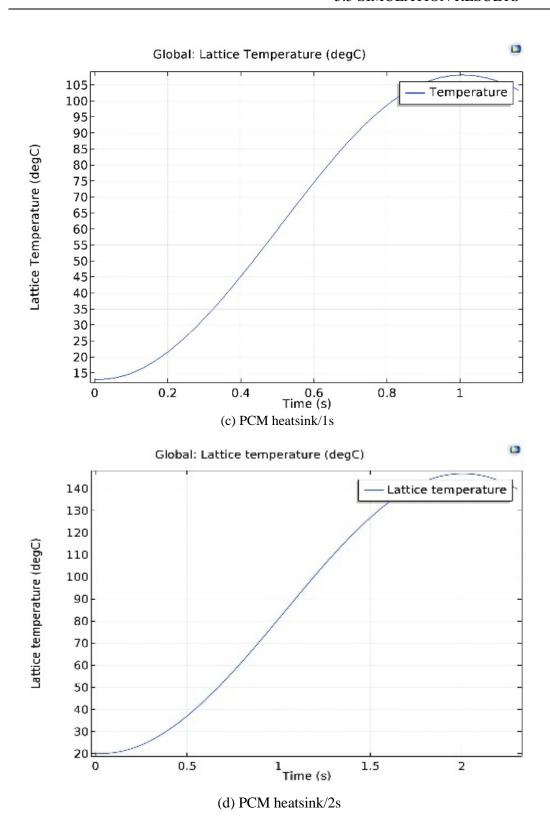

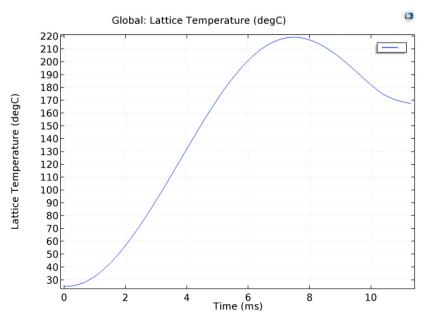

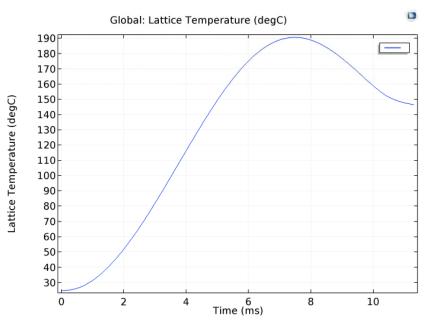

| Figure 5.9 (a)-(f): Thyristor temperature by using the COMSOL modelling . $164$                                                                                                                                     |

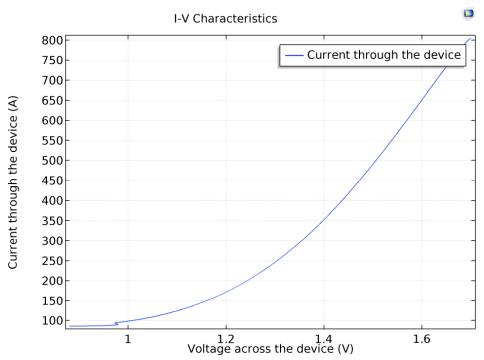

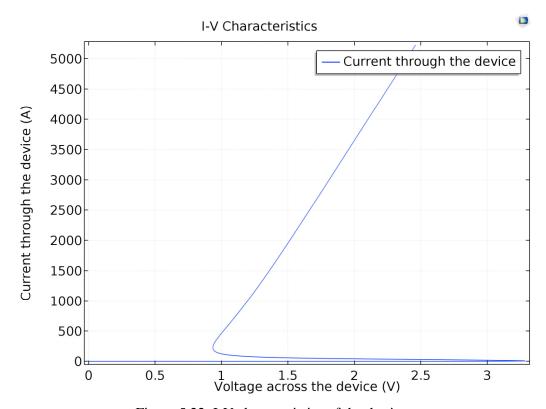

| Figure 5.10: I-V characteristics of the thyristor                                                                                                                                                                   |

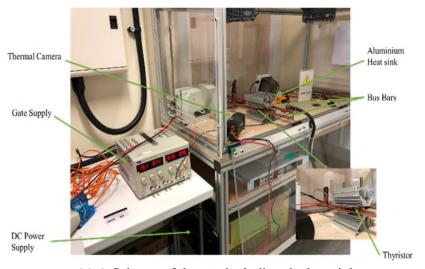

| Figure 5.11 (a) and (b): A schematic of the experiment by using the heat sink166                                                                                                                                    |

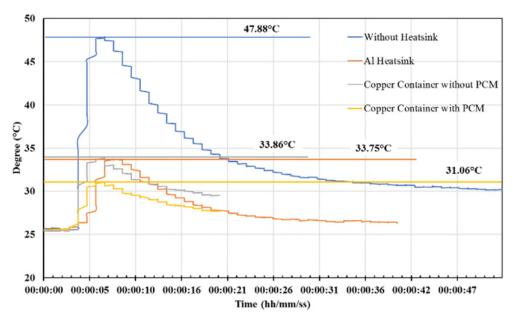

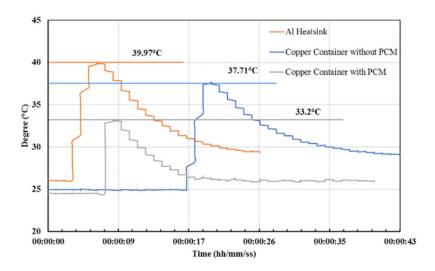

| Figure 5.12: The temperature behaviour of thyristor during applying 800A DC current for 1s for (1) without any heatsink (2) the conventional Aluminium heatsink (3) the proposed container without PCM (4) with PCM |

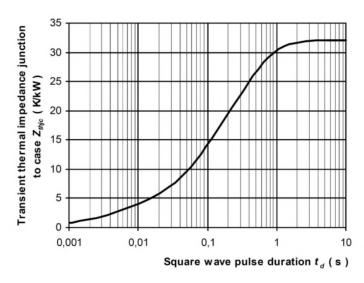

| Figure 5.13 (a) and (b): different thermal Impedance datasheets [10] 168                                                                                                                                            |

| Figure 5.14: The temperature behaviour of thyristor during applying 800A DC current for 2s for (1) the conventional Aluminium heatsink (2) the proposed container without PCM (3) with PCM                          |

| Figure 5.15: copper container with PCM                                                                                                                                                                              |

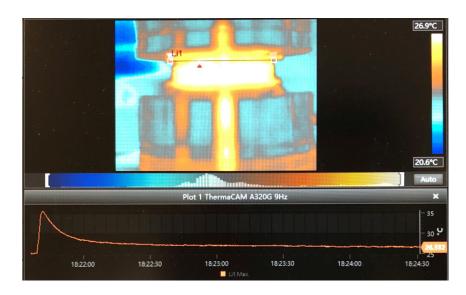

| Figure 5.16: measuring the "case" temperature of the press-pack thyristor by using the thermal camera                                                                                                               |

| Figure 5.17: Junction temperature for 10ms-15kA pulse, 50Hz half-sine wave in MATLAB                                                                                                                                |

| Figure 5.18: Junction temperature for 10ms-15kA pulse, 50Hz half-sine wave in Comsol, without heatsink                                                                                                              |

| Figure 5.19: Junction temperature for 10ms-15kA pulse, 50Hz half-sine wave in Comsol, with the proposed PCM heatsink                                                                                                |

| Figure 5.20: Thermal impedance of ABB thyristor for a DC pulse [11] 174                                                                                                                                             |

| Figure 5.21: I-V characteristics of ABB thyristor [11]                                                                                                                                                              |

| Figure 5.22: I-V characteristics of the thyristor                                                                                                                                                                   |

# **List of Tables**

| Table 1.1: A comparative performance of major FACTS controller [2], [3], [4] 5                                    |

|-------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Cost comparison of various facts device [5]                                                            |

| Table 1.3: Cost comparison of various facts device [6] 6                                                          |

| Table 1.4: HVDC Cost Estimation [5]6                                                                              |

| Table 1.5: Initial Cost [7]                                                                                       |

| Table 2.1: Overview of major FACTS-Devices [39]                                                                   |

| Table 2.2: Examples of use for FACTS [78]                                                                         |

| Table 2.3: Investment cost of asymmetric operation of three 400 kV, 150 km lines, using Conventional devices [79] |

| Table 2.4: Investment cost of asymmetric operation of three 400 kV, 150 km lines, using FACTS devices [79]        |

| Table 2.5: FACTS and HVDC: Overview of Functions [27]                                                             |

| Table 2.6: Comparison of Power Transmission Using B2B VSC HVDC and FACTS facilities [80]                          |

| Table 2.6: B2B VSC 2 terminals / STATCOM & SSSC cost comparison [81] 39                                           |

| Table 2.8: Comparison of different protection mechanisms                                                          |

| Table 3.1: Thermal impedance                                                                                      |

| Table 3.2: Network Properties                                                                                     |

| Table 4.1: Synchronous machine parameters                                                                         |

| Table 4.2: CHP electrical capacity in 2011[12]127                                                                 |

| Table 4.3: Ratio and cross time of synchronous machines for status 1 131                                          |

| Table 4.4: Ratios and cross time of synchronous machines for status 2 132                                         |

| Table 4.5: Induction machine parameters                                                                           |

| Table 4.6: Rating and fault current zero-crossing time for induction machines                                     |

| Table 4.7: Distance effect                                                                                        |

| Table 4.8: Number effect                                                                                          |

| Table 4.9: Distance and number effect 142                                                                         |

| Table 5.1: Features of used Thyristor158                                                                          |

| Table 5.2: Gallium metal properties 159                                                                           |

| Table 5.3: Thyristor thermal results                              | 161 |

|-------------------------------------------------------------------|-----|

| Table 5.4: Features of used Thyristor for medium voltage test [7] | 172 |

| Table 5.5: Thyristor thermal results-11kV                         | 173 |

### ACKNOWLEDGEMENTS

In this section, I would like to express my gratitude to all those who supported and helped me during my Ph.D.

First of all, I would like to thank Professor Li Ran, as my supervisor, who accepted me as his Ph.D. student and then supported me with his very helpful advices within my research and also this thesis.

Moreover, my appreciation to Professors Phil Mawby, Layi Alatise, Richard McMahon, Dr. Christos Mias and Dr. Dan Rogers for their priceless support and guidance during this long-term study.

I would also like to thank to Dr. José Ortiz González, Dr. Robert Wu, and Jonathan Meadows who helped me a lot with this research.

Furthermore, I would like to thank Arne Benjamin Renz, who is like my brother, and Guy Baker.

In addition, I would like to acknowledge the support from everybody in the School of Engineering, University of Warwick whom I did not mention from the office and lab people.

Also, I want to say thank you to my landlord who are like my family in the UK and supported me a lot.

Finally, I would like to dedicate this work to my family. However, they are not here physically, but they really supported me during my Ph.D. and they have always been with me there.

This work was supported by the UK Engineering and Physical Science Research Council (EPSRC).

**DECLARATION**

This thesis is submitted to the University of Warwick in support of my

application for the degree of Doctor of Philosophy. It has been composed

by myself and has not been submitted in any previous application for any

degree.

Parts of this thesis have been published by the author during the period

of study, from March 2017 to January 2020. They are given in full detail

in the Publication List section.

Erfan Bashar

January 2020

xii

## **ABSTRACT**

In recent 20 years medium voltage networks have been becoming one of the important interfaces between the power plants and loads due to the increasing load demand as well as number of distributed generators connected to the network. This is the reason, managing the power flow, and voltage profile of the network at the lowest possible power losses and also price are of the utmost importance.

The series compensators such as a static synchronous series compensator are of the most cost effective power compensators that also have the high efficiency in controlling the power flow and voltage profile. However, their drawback is their vulnerability against the short circuit. This thesis presents a new protection scheme for an SSSC in an MV network by using a varistor and thyristors to eliminate this weakness.

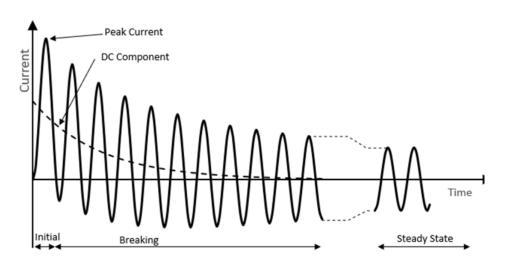

The DC offset phenomenon is one of the main uncertainties that has been studied in the thesis. This phenomenon could cause a delay in the circuit breakers' performance. In this thesis, the parameters of the machines that have most influence on the time when the fault current will pass the zero point have been analysed. Besides, the impact of the DC offset in the medium voltage network has been studied.

Furthermore, the thermal issues have always been one of the most challenging problems for the power electronics devices. This thesis investigates a new packaging style by using the phase change material to improve the thermal managing of a press-pack thyristor during a short circuit. This packaging style is able to absorb the heat as much as required and also could decrease the thermal resistance.

### **Publication List**

# Chapter 3

- Erfan Bashar, Dan Rogers, Ruizhu Wu, Li Ran, Mike Jennings, Timothy C. Green, and Philip Mawby, "A New Protection Scheme for an SSSC in an MV Network by Using a Varistor and Thyristors", in *IEEE Transactions on Power Delivery*, doi: 10.1109/TPWRD.2020.2982512.

- Erfan Bashar, Robert Wu, Weihua Shao, Li Ran, Han Qin," An Appraisal of Possible Protection Schemes of Static Series Compensators in Medium Voltage Power Networks", The 8th International Conference & Workshop, REMOO ENERGY 2018, 29–31 May 2018, VENICE / ITALY.

# Chapter 4

E. Bashar, Q. Han, R. Wu, L. Ran, O. Alatise and S. Jupe, "Analysis of DC offset in fault current caused by machines in a medium voltage distribution network," in *The Journal of Engineering*, vol. 2019, no. 17, pp. 3494-3499, 6 2019. doi: 10.1049/joe.2018.8221

# Chapter 5

2. Erfan Bashar, Ruizhu Wu, Li Ran, Jose Ortiz Gonzalez, Arne Benjamin Renz, Guy Baker, Mike Jennings, Philip Mawby, Tim C. Green, Dan Rogers, "A Method to Contain the Temperature Rise of a Press-Pack Thyristor during a Short Circuit Protection Operation," accepted to publish in IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, 2019

# **List of Acronyms**

B2B VSC

Back To Back Voltage Source

Converter

GTO Gate Turn-Off Thyristor

HVDC High Voltage Direct Current

IGBT Insulated Gate Bipolar Transistor

MOSFET Metal Oxide Semiconductor Field

**Effect Transistor**

NPC Neutral Point Clamped

PWM Pulse Width Modulation

RMS Root Mean Square

SPWM Sinusoidal Pulse Width Modulation

SSSC Static Series Synchronous Compensator

STATCOM Static Synchronous Compensator

SVC Static Var Compensator

TCPAR Thyristor-Controlled Phase Angle

Regulator

TCR Thyristor-Controlled Reactor

TCSC Thyristor-Controlled Series Capacitor

TCSR Thyristor-Controlled Series Reactor

TSC Thyristor-Switched Capacitor

TSR Thyristor-Switched Reactor

TSSC Thyristor-Switched Series Capacitor

TSSR Thyristor-Switched Series Reactor

UHVDC Ultra High Voltage Direct Current

UPFC Unified Power Flow Controller

VSC Voltage Source Converter

# List of Variables and Symbols

ΔTj Junction Temperature Variation

A Area, Cross-Section

C Specific Heat Capacity

Cdc Dc Link Capacitor

D Thickness, Distance

di/dt Rate Of Change Of Current With Time

Dvth/dT Rate Of Change Of The Threshold

Voltage With Temperature

E<sub>f</sub> Excitation Flux

F Frequency

I RMS Current

Ibreak Fault Current, RMS

I<sub>ac</sub> AC Current, RMS

$I_{dc}$  DC Current

I<sub>d</sub> D-Axis Current

I<sub>q</sub> Q-Axis Current

I<sub>m</sub> Maximum Peak Current

I<sub>make</sub> Make Fault Current, RMS

L Inductance

P Active Power

Q Reactive Power

R Resistance, Resistor

Rth Thermal Resistance

Rth,J-C Thermal Resistance Junction To Case

X/R Reactance/Resistance Ratio

X<sub>d</sub>" Direct-Axis Subtransient Reactance

X<sub>d</sub> Direct-Axis Transient Reactance

X<sub>d</sub> Direct-Axis Synchronous Reactance

Xl Leakage Reactance

Xσs Stator Leakage Reactance

X<sub>m</sub> Magnetising Reactance

Xs Induction Machine Per Phase Stator,

Stator Winding Reactance

S Total Power

s Rotor Slip

T Temperature

T<sub>a</sub> The Armature/Stator Time Constant

Tamb Ambient Temperature

T<sub>d</sub>" The Subtransient Time Constant

T<sub>d</sub> The Transient Time Constant

Tj Junction Temperature

Tj-Max Maximum Junction Temperature

V Voltage

V1 Primary Busbar Voltage

V2 Load Busbar Voltage

Vabc Grid Voltage

Vl Nominal Line Voltage, RMS

Vn Nominal Voltage, RMS

V<sub>m</sub> Peak Value Of Stator Voltage

Vf Forward Voltage of a Diode

Vg Gate Voltage

Λ Specific Thermal Conductivity

| τ          | Time Constant                     |

|------------|-----------------------------------|

| $\Theta_0$ | The Initial Rotor Position        |

| Ω          | Angular Frequency of The Grid     |

| Δ          | Ratio of a Load to The Total Load |

| h          | Overall Efficiency                |

### 1 INTRODUCTION

The protection, and reliability of the distribution and transmission networks have always been one of the most critical and challenging issues of the system studies. Finding a cost-effective and reliable technique to protect the network, not only increases the system reliability but also prevents the future expenses that may apply on the system in case of using an improper protection system. Moreover, having a competent protection technique could make possible the utilisation of facilities that are no longer used due to their vulnerability to the faults. This advantage makes the operators enable to have more options in choosing the most cost-effective and optimised utilities in the network that it also can improve the system efficiency and decrease the network cost.

In terms of the protection, the response speed of the protection system has a great impact within the protection process. If the relays and circuit breakers can act faster, which means they can cut off the short circuit current flowing through devices faster, they may be able to prevent the devices' temperature from increasing. Faults like short-circuits are associated with thermal failures due to high temperatures. This high temperature will have a negative impact on the device, especially if the maximum temperature of operation is reached.

In past 20 years, the utilization of medium voltage networks has been gradually increasing. The medium voltage (MV) systems are typically defined as the range of 600-69,000 VAC [1]. These networks are an interface between the transmission lines (which are supplied from the power plant and called the high, extra-high and ultra-high voltages) and the low voltage (which are the final loads or destination). The aim of

medium voltage networks is distributing the power between low voltage systems and also feeding the medium voltages loads such as industrial loads, hospitals or commercial loads. Large industrial complexes and factories that require a substantial amount of power often utilize medium supply voltages. The electrical variational analysis dictates that the voltage is inversely proportional to amperage. This means that when the voltage is increased amperage is decreased to complete the operation. Motors and electrical equipment designed to operate with higher voltages use less electricity and are more economical to operate. Most primary substations do not receive more than 35,000 VAC from utility supply. The primary sub-station can supply stepped down power to secondary substation(s) or to a single building [1].

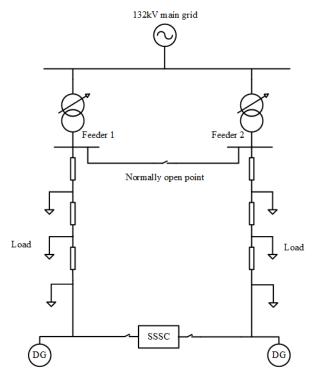

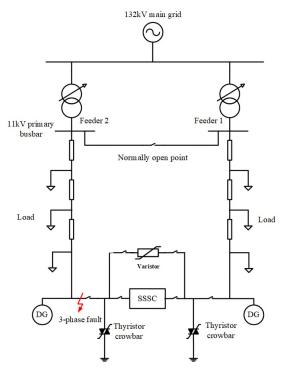

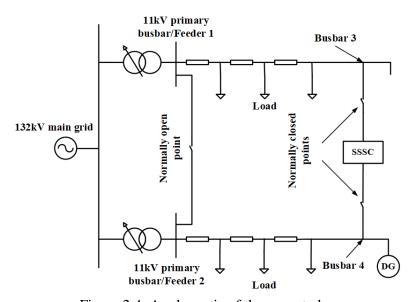

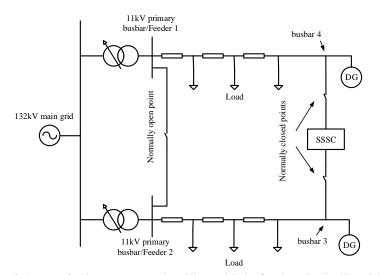

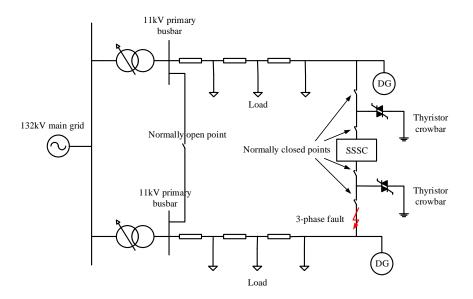

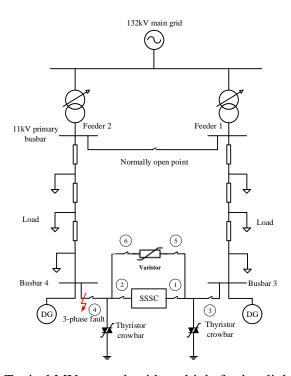

Figure 1.1 demonstrates a schematic medium voltage network. In this schematic two medium voltage feeders are connected to each other through a static synchronous series compensators. The aim of this compensator is improving the power flow and also voltage stability between these two feeders. As it can be seen in the Fig. 1.1, this kind of compensators are located in a series situation in the network. It means they will be highly vulnerable within a fault condition in the network. That is the reason, in spite of their low cost and power losses as well as high efficiency in improving the voltage profile and power flow, they are not utilised in the network.

Figure 1.1: A schematic of a medium voltage network

# 1.1 UTILITIES VULNERABLE TO THE FAULT IN THE NETWORK

The vulnerable utilities, in this thesis, are defined as devices installed in series or having a series compartments in the network such as static synchronous series compensators. These facilities are at a high risk during a short circuit, due to their series part.

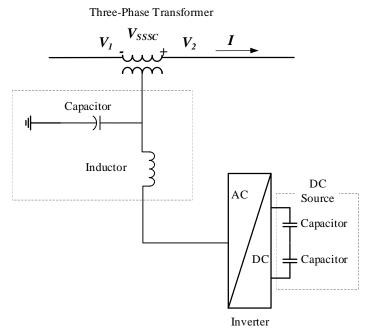

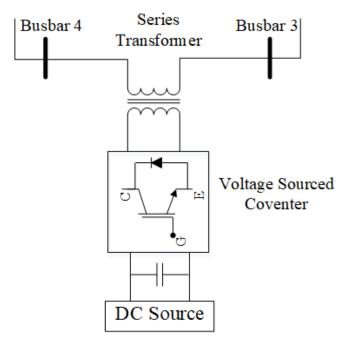

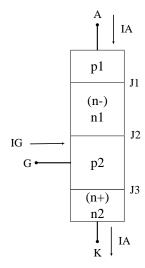

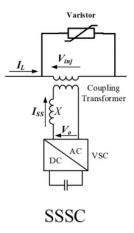

Static Synchronous Series Compensators (SSSCs), see Fig. 1.2, are of the important facilities that can improve the voltage profile, power flow, and reliability of the network in a significantly lower cost as well as lower power losses compared to other compensators while their efficiency is almost as high as those. But, their main drawback is their installation location in series with the power system. This position puts them into the risk of getting damaged during a short circuit. This is the reason, these utilities are not being usually used in the network. Therefore, a protection

Figure 1.2: A schematic of a static synchronous series compensator

scheme which can eliminate this issue could open a way to make the usage of these practical facilities reasonable.

The following tables show a comparison between different FACTS controllers and prove the SSSC is one of the economic and efficient ones.

Table 1.1: A comparative performance of major FACTS controller [2], [3], [4]

| FACTS<br>Controllers | Load<br>Flow<br>Control                     | Voltage<br>Control | Transient<br>Stability | Oscillation<br>Damping |

|----------------------|---------------------------------------------|--------------------|------------------------|------------------------|

| SVC/STATCOM          | X                                           | XXX                | XXX                    | XX                     |

| TCSC                 | XX                                          | X                  | XXX                    | XX                     |

| SSSC                 | XXX                                         | X                  | XXX                    | XX                     |

| TCPAR                | XXX                                         | XX                 | X                      | XX                     |

| UPFC                 | XXX                                         | XXX                | XXX                    | XXX                    |

| xxx-strong Influence | luence xx-average influence x-small influer |                    |                        | nall influence         |

Table 1.2: Cost comparison of various facts device [5]

| FACTS Devices                 | Cost (\$/kVar)                         |

|-------------------------------|----------------------------------------|

| Shunt Capacitor               | 8                                      |

| Conventional Series Capacitor | 20                                     |

| Conventional PAR Transformer  | 20                                     |

| SVC                           | 40- controlled part                    |

| TCSC                          | 40- controlled part                    |

| STATCOM                       | 50                                     |

| UPFC Series Portions/SSSC     | 50 ( <b>\$/kW</b> )- series power flow |

| UPFC Shunt Portions           | 50- controlled part                    |

Table 1.3: Cost comparison of various facts device [6]

| FACTS Devices | Capacity [MVA] (shunt, Series) | Initial Cost<br>(Million USD) |

|---------------|--------------------------------|-------------------------------|

| SVC           | (150,0)                        | 6                             |

| TCSC          | (0, 2.4)                       | 0.096                         |

| STATCOM       | (150,0)                        | 7.5                           |

| SSSC          | (0, 12.5)                      | 0.625                         |

| UPFC          | (100, 18.4)                    | 5.92                          |

Table 1.4: HVDC Cost Estimation [5]

| HVDC LINKS           | Cost (\$/kW/terminal) |

|----------------------|-----------------------|

| Back to Back, 200 MW | 108                   |

| ±250kV, 500MW        | 145                   |

| ±350kV, 1000MW       | 107                   |

| ±500kV, 3000MW       | 75                    |

Table 1.5: Initial Cost [7]

| HVDC Power Rated | Contracted Cost, Converters<br>(Million USD) |

|------------------|----------------------------------------------|

| 350              | 75.15                                        |

| 500              | 138.91                                       |

| 750              | 165.77                                       |

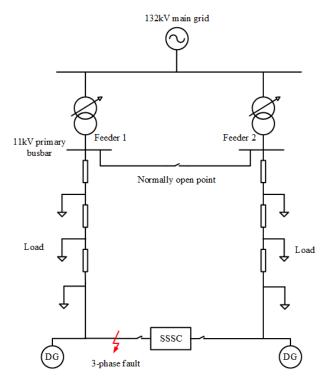

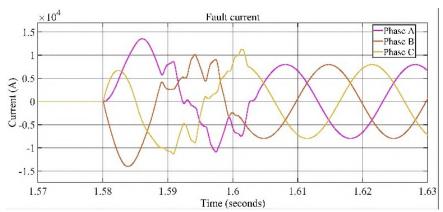

Figure 1.3 shows a location of a three-phase short circuit in the network. In order to show the fault current value passes through a SSSC during a short circuit condition, a simulation has been done. During this simulation, the SSSC works in a normal operation with a closed control system in an MV network. A simulation has been done in MATLAB Simulink in order to show the short circuit quantity in an MV network. As it can be seen in Fig. 1.4, if a short circuit happens in the point shown in Fig. 1.3, the current can rise to 12,000 A that passes through the SSSC. This fault current can severely damage the power electronics facilities used in the inverter.

Figure 1.3: A schematic of a medium voltage network

Figure 1.4: The fault current passing through SSSC without protection

# 1.2 PROTECTION TECHNIQUE BY USING THYRISTORS AND A VARISTOR

As it is known, the power electronics devices are the cutting-edge technology that have been using in many applications because of their unique abilities. In fact, these devices are able to withstand very high current and voltage and also their very fast operation speed makes them more efficient compared to devices containing the mechanical compartments. Also, Power electronics devices can be used to convert and control the flow of electrical power. Their benefits and drawbacks can be categorized as:

- ✓ High efficiency due to the low loss in the power semiconductor devices.

- ✓ High reliability of the power electronic converter system.

- ✓ Long life and less maintenance due to absence of any moving parts.

- ✓ Flexibility in the operation

- ✓ Fast dynamic response compared to the electromechanical converter system.

- ✓ Small size and less weight, thus low installation cost.

- x Generation of harmonics in the supply system as well as in the load circuit.

- x Having low overhead capacity

A protection technique like in Fig. 1.5 can be utilised to improve and expedite the protection process according to the power electronics devices' fast acting and high-current and voltage abilities. In this method,

Figure 1.5: A protection method

Thyristor crowbars and a varistor are the main devices to form this technique. In this technique, when a fault happens, first relay recognises the short circuit, then the varistor limits the voltage rise and decreases the current passing through the SSSC by allowing the current to pass through itself. After that, thyristors are triggered on to let the current pass through them rather than the SSSC. At the end, the circuit breakers will open to isolate the SSSC from the MV network.

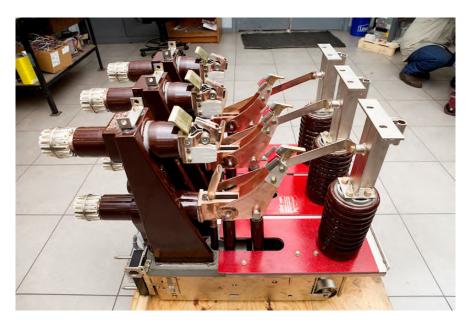

An MV circuit breaker has shown in Fig. 1.6. MV circuit breakers are conventional methods that are used to protect devices in the MV network. Their cost and dimensions depend on their voltage rate, break fault current and make fault current. Their opening time depends on different parameters such as arcing time and the their current rating [8].

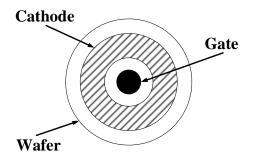

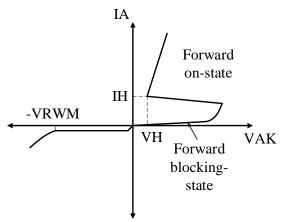

Thyristors, see Fig. 1.7, are still the best choice for high-current and high-power applications over the other semiconductors. Their PNPN

Figure 1.6: An MV circuit breaker [9]

structure which is made of a silicon wafer, is able to withstand several thousand amps in the normal operation that during the surge condition can even be several times more than its normal one. Regarding the voltage it also can tolerate several thousand volts that makes it a very practical and unique device for the high-power applications.

A varistor, see Fig. 1.8, acts like a surge arrester that can control the voltage surge during a fault or overload and its operation time is from some microseconds to a few milliseconds. The varistor acts like an open circuit when the voltage is very low, but by increasing the voltage value it will become like a short circuit and let the current pass through it. They

Figure 1.7: A thyristor crowbar [10]

can withstand very high current and voltage depending on their operation time.

The advantages of the proposed method could be summarised as follows:

- Very fast-response performance compared with Circuit Breakers (A few microseconds for thyristor compared to at least 3 cycle for CBs, more information in Chapter 3).

- Relegating the back-up circuit breaker's rate.

- Decreasing the arc level.

- Decreasing the maintenance cost.

- Cheaper compared to CB with the lower maintenance cost.

- Taking up a smaller room

Figure 1.8: A Varistor [11]

### 1.3 TEMPERATURE ISSUE AND HEATSINK SYSTEM

It definitely can be claimed that the temperature problem is the most challenging issue in terms of power electronics devices. Therefore, thermal management is a high priority topic in power electronics studies. As it is shown in the Fig. 1.9, a temperature rise during the thyristor operation can cause a failure and a severe damage to the thyristor wafer. That is why, managing the temperature during their operation especially during the surge condition is very important. Because within a short

Figure 1.9: A damaged thyristor during a failure due to the temperature rise [12]

circuit, the temperature rise happens within a very short time (up to 1 second), the heatsink has to be able to absorb the heat very fast.

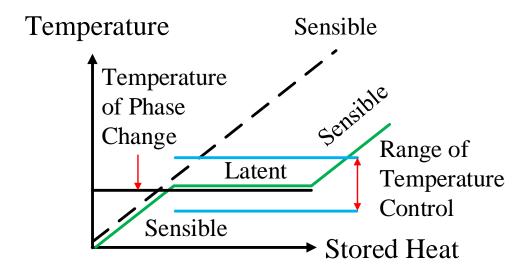

The conventional heatsinks, see Fig. 1.10, are mostly made of Aluminium material and they are designed to be used within the normal operation condition. It means, during the short circuit condition, they are neither capable nor enough capable of controlling the temperature and protecting the device against the temperature rise. Thus, having a heatsink system that can decrease the delay of heat transmission and also is capable of storing a huge heat within the fault will certainly be very useful.

Figure 1.10: The conventional heatsinks [13]

#### 1.4 CONTRIBUTIONS

This section presents contributions and motivation of carrying out this research. The main contributions of this thesis are defined as:

- 1. Increasing the reliability and protection level of the MV network, by introducing a new protection method for the SSSC. Using this technique will eliminate the SSSC vulnerability against the fault that makes the usage of the SSSC less challenging and risky.

- 2. Investigating the DC offset effect in the medium voltage networks to study its influence in the MV networks. In fact, this study consider the parameters can change the value of the DC offset. This phenomenon has a great impact during the turning-off process of power electronics devices such as thyristor.

- 3. Introducing a new heatsink based on the phase change material during the short circuit. The aim of this heatsink is limiting the temperature rise to protect the devices especially during a surge condition.

#### 1.5 THESIS OUTLINE

In this section, each chapter is introduced briefly to give a clear idea about the aims will have been investigated in this thesis.

**Chapter 2:** A literature review and comparison on different power compensators and also advantages and drawbacks of using the static series compensators have been carried out in this chapter. Then, a review on a thyristor and a Varistor structure has been done to give a clear understanding of their abilities and applications.

Chapter 3: In this chapter, a new fast-acting protection scheme in order to expedite the protection process of a static synchronous series compensator against a short circuit will have been presenting. Furthermore, the surge condition of the thyristor and varistor for using in the fault will be investigated as well. Also, a closed-loop control system for the static synchronous series compensator will be presented.

The results of this chapter have been published in IEEE Transactions on Power Delivery journal, and have been presented at the REMOO ENERGY Conference, 2018, Italy.

**Chapter 4:** The DC offset phenomena could always be a potential issue for the performance of the protection facilities in the network. Thus, this chapter discusses the effect of the DC offset in the network and also considers how much this phenomenon could influence the protection systems in a medium voltage network.

The results of this chapter have been published in IET journal of Engineering.

Chapter 5: The heatsink facilities are very important in the case of the power electronics system, especially during the short circuit when a huge current passes through the device, this issue is highlighted. This chapter presents a new heatsink style that is capable of absorbing more heat and also decreasing the thermal resistance of a press-pack thyristor from the junction to the case by using the phase change material.

The results of this chapter presented at the ECCE conference (2019 in Baltimore).

**Chapter 6:** At the end, a conclusion about the achievements obtained within this research is presented, and the aims of doing this research is summarised. Then, the future works that could be carried out in further of the research's objectives are introduced.

#### 1.6 REFERENCES

- 2. D. P. Kothari, K., I. J. Nagrath. "Modern Power System Analysis," in Tata McGraw-Hill, Electric power systems, September 2011, Third edition, ISBN13: 9780070494893, pp.556-574.

- 3. Mahdavi Tabatabaei, N., Jafari Aghbolaghi, A., Bizon, N., Blaabjerg, F., "Reactive Power Control in AC Power Systems," Springer; 1st edition, 24 April 2017, ISBN-13: 978-3319511177, pp-128.

- G.M. Vireshkumar, F.R.B., H.J. Suresh, Review on Comparison of FACTS Controllers for Power System Stability Enhancement, International Journal of Scientific and Research Publications, vol. 3, no. 3, pp. 57–58, 2013.

- R. Mohan Mathur, Rajiv K. Varma "Thyristor-Based FACTS Controllers for Electrical Transmission Systems" by A John Wiley & Sons, INC. Publication, IEEE Press, 2002, Third edition, ISBN: 0-471-20643-1

- Sode-Yome, Arthit, Mithulananthan, Nadarajah, Lee, Kwang Y.,

"Comprehensive comparison of FACTS devices for exclusive loadability enhancement", 2013, IEEJ Transactions on Electrical and Electronic Engineering, pp. 7-18, Vol. 8

- Härtel, Philipp & Vrana, Til & Hennig, Tobias & von Bonin, Michael

Wiggelinkhuizen, Edwin & Nieuwenhout, Frans. (2017). Review of investment model cost parameters for VSC HVDC transmission

- infrastructure. Electric Power Systems Research. 151. 419–431. 10.1016/j.epsr.2017.06.008.

- 8. <a href="https://r5.ieee.org/houston/wp-content/uploads/sites/32/2016/01/7-MV-Switchgear-Mar-24-25.pdf">https://r5.ieee.org/houston/wp-content/uploads/sites/32/2016/01/7-MV-Switchgear-Mar-24-25.pdf</a> [Access Data, 07/06/2020].

- 9. <a href="http://www.coastalpowersystems.com/medium-voltage-circuit-breakers/">http://www.coastalpowersystems.com/medium-voltage-circuit-breakers/</a>, [Access Data, 17/11/2019].

- 10. <a href="https://www.alibaba.com/product-detail/Best-price-MTC600A-1800V-semiconductor-thyristor\_60634998442.html">https://www.alibaba.com/product-detail/Best-price-MTC600A-1800V-semiconductor-thyristor\_60634998442.html</a>, [Access Data, 17/11/2019].

- 11. <a href="https://www.digikey.be/product-detail/en/littelfuse-inc/V321BA60/F4093-ND/485851">https://www.digikey.be/product-detail/en/littelfuse-inc/V321BA60/F4093-ND/485851</a>, [Access Data, 17/11/2019].

- 12. <a href="https://www.eng-tips.com/viewthread.cfm?qid=194283">https://www.eng-tips.com/viewthread.cfm?qid=194283</a>, [Access Data, 17/11/2019].

- 13. <a href="https://www.gdrectifiers.co.uk/products/aluminium\_heatsinks">https://www.gdrectifiers.co.uk/products/aluminium\_heatsinks</a>, [Access Data, 17/11/2019].

## 2 POWER COMPENSATORS AND PROTECTION SCHEMES

#### 2.1 INTRODUCTION

Nowadays, due to the increasing number of customers and load demand as well as adding new kinds of loads such as Electrical Vehicles (EV) charging stations to the network, the demand for power has been quickly rising. This means either the current power plants and generators have to produce more power or new generators such as distributed generators (DGs) have to be added to the grid. By adding more DGs and loads to the network, the power management/control, and voltage profile will become very important for the network. Since most of the protection devices which are used in networks (like circuit breakers), are controlled mechanically, thus managing the load changing and damping the transient oscillations, due to the slow and discrete switching response, are very difficult to be coped with.

Given the aforementioned issues, the use of compensators in grids is vital to deal with these difficulties for more security and enhance the power supply quality. In this case, series and shunt compensations are fundamental structures of all compensators or flexible AC transmission systems (FACTS) that are connected to the power system [1]. The main advantages are decreasing the network power losses, fast response, improved controllability and increased power transfer capability. There are different compensation devices/systems: capacitors, capacitors and inductors, and active voltage source (synchronous generator), which can be passive or active. Shunt inductors and capacitors as well as series

capacitors are passive compensators and those including a synchronous generator or using solid-state devices for switching off capacitors and inductors are known as active compensation. Therefore, it can be said that power compensators depending on their structure and compartments can implement power flow regulation, reasonably controlling line's active power and reactive power, improving the transmission capacity of power system; also, improving the system voltage stability, the damping of the system and the power angle stability.

Apart from compensating the power in MV networks, protecting them against faults, overload, overvoltage, and short circuits is very critical. Short circuits can severely damage the utilised facilities in the network, especially those utilities that are located in the path of the short circuit. The series devices are prone to get damaged within a short circuit because they have to tolerate a massive fault current (up to 20 times) passing through them. Conclusively, protecting the series compensators due to their sensitive location against a fault is very critical.

In terms of protecting the series devices, the protection mechanism needs to be very fast to limit or cut off the current before it exceeds the device's maximum withstanding current. In addition, the used facilities have to be able to absorb the energy and also release it after their action. The protection devices also have to be able to tolerate a high current and a great arc value depending on their structure.

This chapter presents a review and comparison of the most recent power compensators. The protections schemes used for series compensators are analysed/evaluated and a new protection mechanism is introduced.

# 2.2 POWER FLOW AND VOLTAGE CONTROL BY COMPENSATORS

Distributed generation (DG) systems such as Combined Heat and Power (CHP) units, Photovoltaic (PV) systems and wind power generation systems are on the rise due to the increase of the load demand. These facilities can compensate the required power during the peak time and then can be separated from the grid while they are not needed.

However, the increase of distributed generation systems has several side effects which have been intensively studied, including reverse power flows and voltage rises in power distribution networks [1]. Indeed, DGs have a great influence on distribution network stability, reliability and performance, which eventually restricts the DG penetration level. Furthermore, the penetration of DGs has also an impact on the amplitude and characteristics of the fault current depending on the network configuration [1].

The power quality, voltage stability and power flow in distribution networks and transmission lines have been drawn attention in recent years due to the increasing load demand and reactive power consumption. It could be said that the voltage control is one of the most used methods for enhancing the stability, reliability and power quality of the grid, with plenty of research activity in this area, finding the optimal, cost effective, fast response and simple method in order to achieve the mentioned objectives [2].

Different methods have been used for mitigating the voltage distortion and to enhance the power quality and reliability of networks such as improving the voltage profile, power flow control, voltage control, reactive power control etc. [1]-[3].

As mentioned before, the controlling voltage/VAR solution, e.g. Volt-VAR Control or VVC which refers to the process of managing voltage levels and reactive power (VAR) throughout the power distribution systems, is one of the conventional and most cost effective methods to enhance the voltage profile and power flow in networks. Power compensators due to their abilities in controlling the voltage can be very useful for improving the voltage stability. Unified Power Flow Controller (UPFC), Static Var compensator (SVC), Static Synchronous Compensator (STATCOM), Static synchronous series compensator (SSSC), shunt capacitors bank (fixed or CBs), on-load tap changer (OLTC), as well as the Back to Back Voltage control Converters (B2B-VSC) are of those facilities using this solution to control the voltage in the current networks [2].

A soft open point (SOP) is defined as a device, which creates an interconnection among feeders in place of normally open points (NOPs). The aim of using a SOP is to transmit the active/reactive power or regulate voltage. A voltage source converter, SSSC, STATCOM, or UPFC are of could be used in a SOP [3]-[6].

In comparison with conventional VAR devices such as a SVC, the SOP devices are more accurate, with a quicker response and more controllability. A coordinated VVC method based on SOP has been proposed in [7] that presents how to eliminate the voltage distortion and the operation cost by using VAR devices and VSC-based systems.

The next sections explain in more detail some of the recent technologies of power compensators in the transmission systems including a comparison of the different power compensators.

## 2.2.1 Combined Series-Shunt/Series Compensation Technologies

A series compensation is an important method to improve the grid voltage for increasing the power transfer capacity and controllability of the power delivery of networks in high transmission lines.

Voltage sags are of the remarkable industrial concerns in power networks. Faults in the network, a large motor starting, and heavy loads are some of the events will cause a voltage sag in a system. Using a series compensator is a conventional way for controlling the voltage to prevent the voltage sag happening in the grid.

There are different types of series compensators that use the different methods to control the voltage and VAR. Thyristor-controlled series capacitor (TCSC) and static synchronous series compensator (SSSC) use the equivalent reactance changing method for controlling the voltage. Phase shift transformer (PST) by controlling the phase angle improves the system stability [8]. However, some of series compensators such as sen transformer (ST) [9], rotary power flow controller (RPFC) [10] employing both magnitude and phase angle for the voltage control are based on mechanical on-load taps [11]-[14] and rotary transformers as well as special driving systems [15]-[17], respectively. Moreover, by using a combination of thyristor-converters and especially a winding-configured transformer one can build a series compensator capable of adjusting both magnitude and phase angle similar to ST and RPFC to control and inject the voltage. However, in spite of them, it does have their limitations such as being slow, capacity restricts. Also, it benefits of power semiconductor

advantages such as faster operation, frequent regulations and wide range of phase angle regulation for voltage injection [18].

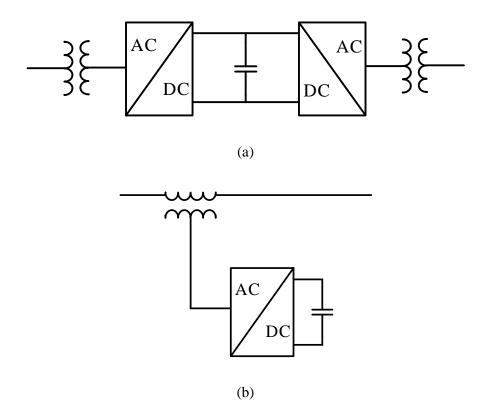

## 2.2.2 UPFC (Unified power flow controller)

The UPFC is one of the most used devices among other FACTS facilities due to its capability of controlling both active and reactive power and improving the stability of system makes it a proper choice for being used in transmission lines [19]. However, UPFC could have an impact on the admittance seen by an impedance relay or distance relay during power swing [20]. That can cause a wrong or a lately trip.

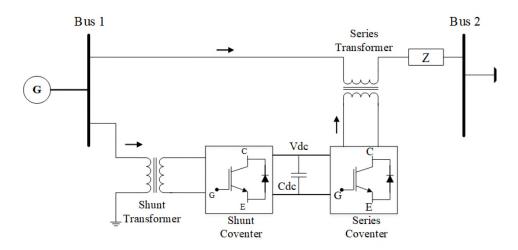

Figure 2.1: Configuration of UPFC: shunt and series converters are on substation and ending sides respectively

The most important aim of using the UPFC (see, Fig. 2.1) is controlling both active and reactive powers of the network. In this regard, the phase angle, Voltage and impedance of system are adjusted and optimised for achieving to this goal. Several control functions such as series or reactive compensations and phase shifting can be employed for this objective, and in this way boosting, e.g. series connection, and exciting transformers are used for injecting the voltage and reactive current, respectively. The AC

to DC voltage source converters are commonly used in a back to back structure with a DC capacitor for making a UPFC [21].

Despite its benefits for optimizing and managing the power in the network the UPFC has a complex structure. Thus, designing a UPFC creates several challenges in its power electronics section and also affects the power system. Besides, the ways of protection and controlling them shall be mainly and critically investigated and considered [22]. In the recent years it has been illustrated that the installation location of a UPFC has a great effect on its overall performance [23].

One of UPFC advantages is its capability in controlling the power flow even during the fault conditions. In fact, the UPFC ability in quelling or relieving the network disturbances by controlling current, voltage and, hereby, power flow could be considered for more studying about its effects on different system situations such as fault conditions, and/or even faster recovery of system to its normal condition after the fault [24].

## 2.2.3 Static Synchronous Series Compensator (SSSC)

A SSSC (see, Fig 2.2), also known as a series STATCOM, is a controllable voltage source that by employing a voltage-source converter (VSC) controls magnitude and phase of an injected voltage irrespective of the current in series with line. In fact, by inducing both capacitive and inductive voltage is capable of affecting the active and reactive power flow by either increasing or decreasing the reactive voltage/flow on the line. [25]-[28]

A SSSC can be used to improve the stability and damped out the oscillations. The subsynchronous resonance due to the series capacitor

Figure 2.2: A Schematic diagram of the SSSC

could be diminished by using the SSSC. Consequently, the subsynchronous oscillation will be damped out [29], [30]. In addition to the mentioned applications for the SSSC, in the recent years a lot of papers have studied the SSSC in networks in order to ease the simulation and analysing the SSSC performance in the network [31]-[33]. Some examples include presenting an energy function of the SSSC [34] and considering the dynamic respond of the SSSC by using a fuzzy controller [35].

Other applications of the SSSC that have been studied in recent years are: controlling the power flow by using the SSSC in a distribution network [36], control the voltage stability and the power flow in offshore wind plants [37], combining the distribution SSSC (D-SSSC) with fault current limiter (FCL) devices in distribution networks in order to limit the short-circuit as well as control the power flow [38].

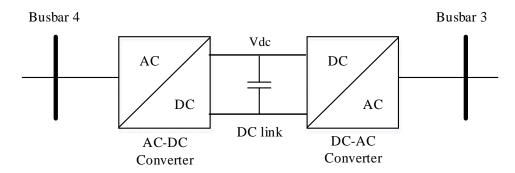

## 2.2.4 Back to Back System

In recent years, the Back to Back (B2B) (see, Fig 2.3) systems have received a great attention due to their ability of improving the full power flow controllability and limitation. Conventional HVDC systems, which employ thyristor converters, are utilised for either a coupled asynchronous network or a power transmission line over long distances. However, they are unable of controlling the reactive power and need a space for filters in order to mitigate the harmonic distortion [39].

B2B-VSCs can be used in synchronous networks in addition to synchronous network interconnections and back-to-back AC system linking [39]. In addition, they are capable of controlling both the reactive and active powers independently, power flow balancing, increasing the transmission capability, operating as two STATCOMS, as well as supporting a weak AC system or even a passive network.

In terms of the VSC-B2B structure, it consists of two converters with a short DC line between them that allows the system to interconnect two AC grids with either the same or a different frequency. The VSC-B2B system employs either a pulse-width modulation (PWM) strategy or a multi-bridge topology for both the rectifier and inverter components due to its symmetric converter configurations [39]-[44]. Studies on VSC-B2B

Figure 2.3: A Schematic of the Back to Back Coveter system

include modelling [45]-[47], control [48], protection [49], [50], application [50], [51], reliability and evaluation [52]-[54], power transfer into the modular multilevel converter (MMC) [55] and multiterminal VSC-B2B system [56], [57].

The B2B static synchronous compensator (B2B STATCOM), which is considered as a VSC-B2B system without the long DC transmission [58], in comparison with the conventional VSC-HVDC system has an asymmetrical structure. In fact, the rectifier using the PWM technology controls active and reactive powers and the inverter controls the reactive power by using the multi-pulse technology. Therefore, little space, low cost, less switching loss, and no harmonic frequency in the multi-pulse converter are of B2B STATCOM advantages over the VSC-HVDC [40]-[59]. Some researches on B2B STATCOM features have been conducted such as increasing the transmissibility of a line and the voltage stability [60]-[62], utilising the B2B STATCOM as a transfer switch [63], and for connecting a wind turbine to the grid [64].

Furthermore, other back to back technologies and topologies which in recent years have been studied and proposed for different purposes are medium voltage B2B topologies [65], [66], B2B converters [67], [68] could be used in distribution networks and microgrid systems, respectively.

#### 2.3 COMPARISON BETWEEN A B2B VSC-LINK AND A SSSC

In this section, the SSSC is specifically compared to the B2B VSC-LINK to prove its efficiency in an MV network where B2B VSC-LINK has usually been used. Then, a throughout comparison between different types of power compensators with SSSC has been presented.

#### 2.3.1 A B2B VSC-LINK and a SSSC

For these comparison studies, the network topology shown in Fig 2.4 is selected as the target system. Feeder 1 has 3 load groups evenly distributed along the 5 km cable and Feeder 2 has 3 load groups evenly distributed along the 10 km cable. The resistance and inductance of the cables are 0.06 ohm/km and 0.134 mH/km. A power electronic based device, B2B VSC - link or SSSC, is implemented between busbar 3 and 4 as the connection at the ends of two adjacent networks. The following extreme case is selected to evaluate the compensating performance of both methods: Feeder 2 is heavily loaded, 17 MW with the power factor of 0.98, and Feeder 1 is lightly loaded, 1 MW load with the same power

Figure 2.4: A schematic of the case study

Figure 2.5: a) A schematic of B2B VSC b) A schematic of SSSC

factor. In this case, ideally a load of 8 MW has to be transferred from Feeder 2 to Feeder 1 to balance the system.

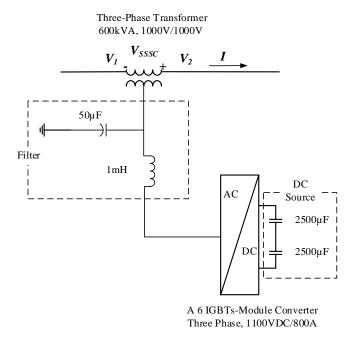

For the B2B VSC link (Fig. 2.5(a)), two three-phase 8 MW, 11 kV to 690 V transformers are used for implementing the device. To transfer the active power of 8 MW from one feeder to the other, at the converter side 690 V voltage level, the magnitude of current is about 9500 A. The ABB HiPak IGBT Module 5SNE 0800M170100 which has the rating of  $V_{ce}$ =1700 V and  $I_c$ =800 A' is selected for building the converters. Considering 100% current margin, the converter will be 2-level and consist of 144 modules.

The situation for an SSSC is different (Fig. 2.5(b)); the SSSC is a partially-rated device which by injecting a voltage orthogonal to the current can manipulate the power flow. The required injecting voltage is

determined by the network, in this study a 690 V converter is more than sufficient to control the power flow. The current flowing through the SSSC is much less than that in a fully-rated device like the B2B VSC - link. A three-phase 600 kVA, 2000 V to 2000 V transformer is used for implementing the device. When transferring the active power of 8 MW, the converter is at the maximum operating point and its output current magnitude is about 600 A. Therefore, with 100% current margin, two IGBT modules for each arm and 12 modules in total are sufficient.

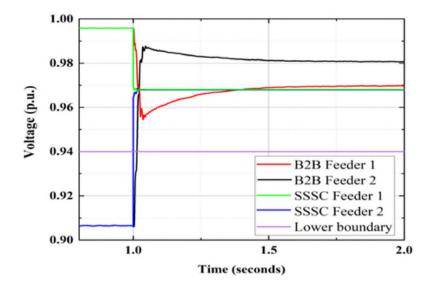

With compensation in the extreme case, the results are shown in Fig. 2.6. Before t=1 s, the two networks are operated separately and the voltage at the end of the heavily-loaded Feeder 2 is below the lower boundary of 0.94 p.u. At t=1 s when the B2B VSC - link or SSSC is enabled, the voltage at the end of Feeder 2 rises meanwhile the voltage at the end of Feeder 1 drops because of the 8 MW active power flows from Feeder 1 to Feeder 2. The voltages are within the limits and the B2B VSC - link gives higher voltage amplitudes because the converters not only transfer the active power but also compensate the reactive power to both feeders.

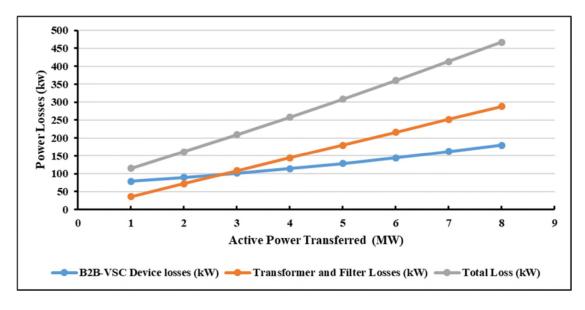

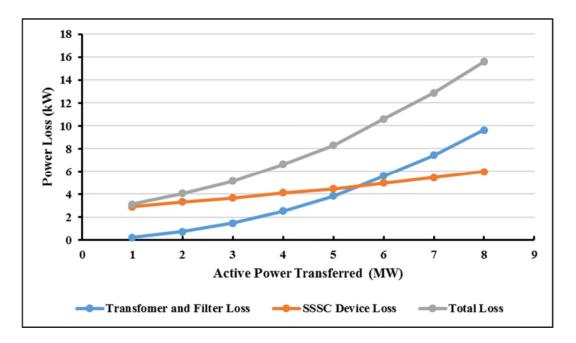

Figure 2.6: Voltage magnitudes at each feeder end before and after compensation by SSSC and B2B VSC - link

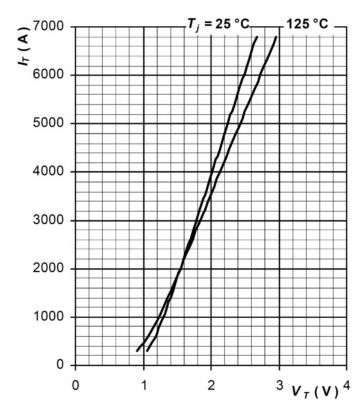

In terms of power losses, when an active power of 1 MW to 8 MW is transferred, the power losses of the B2B VSC - link and SSSC are calculated by simulation and shown in Fig. 2.7 and 2.8. The power losses on filters and transformers are assumed to be approximately 1.5% and 1.2%, respectively [71-73]. The device loss consists of the IGBT and diode conduction losses, the IGBT turn on and off losses and the diode reverse recovery loss. In the simulation, the junction temperature is assumed to be at 125 °C. Thus, the losses are functions of the current. The calculation is shown as below:

$$E_{total} = \int_{0}^{1} \left( v_{ce} \cdot i_{c} + v_{f} \cdot i_{f} \right) + \sum_{i} e_{on} + \sum_{i} e_{off} + \sum_{i} e_{rec}$$

(2.1)

where  $v_{ce}$ ,  $v_f$ ,  $e_{on}$ ,  $e_{off}$  and  $e_{rec}$  are the IGBT on-state voltage, diode forward voltage, IGBT turn on energy loss, turn off energy loss and the diode reverse recovery energy. Currents  $i_c$  and  $i_f$  are measured in simulation and the functions are obtained by curve fitting the characteristic plots from the product datasheets [90].

Figure 2.7: Power losses of B2B VSC - link

Figure 2.8: Power losses of SSSC

As shown in Figures 2.7 and 2.8, the power loss of SSSC is approximately 30 times lower compared to that of the B2B VSC link in all circumstances because it has significantly lower current rating. Thus, using an SSSC instead of a B2B VSC for power flow control in MV networks is potentially very attractive.

#### 2.3.2 Disadvantages of Series Compensators

Apart from their advantages such as increasing power transfer capability, system stability improvement, voltage regulation improvement, load division between parallel circuits, damping effect [39], they have some drawbacks.

A series compensation by using the series capacitors intends to reduce the series inductive reactance amount of the line in order to enhance the network power flow by increase the power transfer capability, reduction in power angle and improving the maximum loading capability. That will improve the system stability and the voltage regulation as well as the damping effect. But, series capacitor increases level of fault currents by decreasing the line reactance. Also, the possibility of the sub-synchronous resonance phenomena, ferro-resonance phenomena and maloperation of distance relays will rise. Moreover, due to the installation of protective devises and circuit breaker/ isolator and control circuit for series compensation, the cost of installation will increase as well. [25, 74-77]

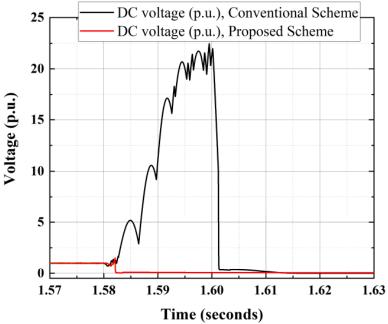

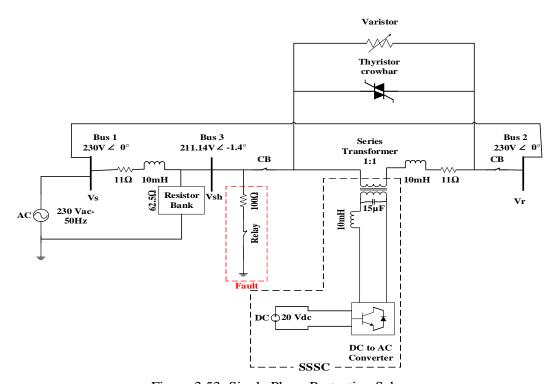

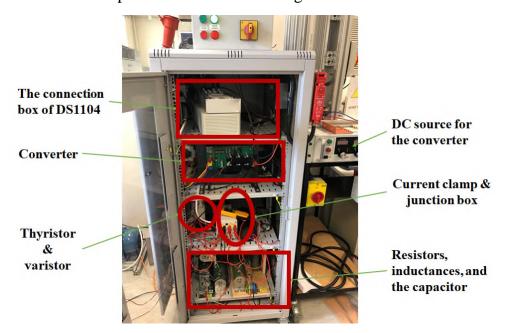

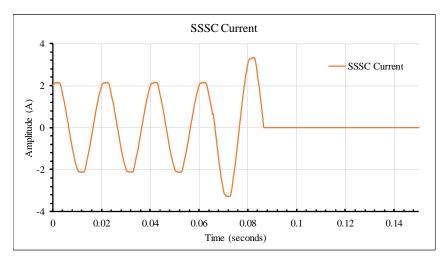

## 2.3.3 Comparison between Different Compensator Systems