#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/152664

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Modelling and Characterisation of Distributed Hardware Acceleration

by

### Ryan A. Cooke

#### Thesis

Submitted to the University of Warwick

for the degree of

Doctor of Philosophy

School of Engineering

July 2020

## Contents

| List of Tables  |         |                                                  |     |

|-----------------|---------|--------------------------------------------------|-----|

| List of Figures |         |                                                  |     |

| Ackno           | wledgr  | nents                                            | ix  |

| Declar          | ations  |                                                  | x   |

| Abstra          | act     |                                                  | xi  |

| ${f Abbre}$     | viatior | ıs                                               | xii |

| Chapt           | er 1 I  | Introduction                                     | 1   |

| 1.1             | Motiv   | rations                                          | 3   |

| 1.2             | Objec   | tives                                            | 4   |

| 1.3             | Contr   | ibutions                                         | 5   |

| 1.4             | Thesis  | s Roadmap                                        | 5   |

| 1.5             | Public  | cations                                          | 6   |

| Chapt           | er 2 I  | Background and Literature Review                 | 8   |

| 2.1             | Comp    | outing Platforms                                 | 9   |

|                 | 2.1.1   | Central Processing Units                         | 9   |

|                 | 2.1.2   | Field Programmable Gate Arrays                   | 11  |

|                 | 2.1.3   | FPGA Accelerator Design                          | 16  |

|                 | 2.1.4   | Graphics Processing Units                        | 21  |

|                 | 2.1.5   | Application Specific Integrated Circuits (ASICs) | 23  |

|                 | 2.1.6   | Summary                                          | 24  |

| 2.2             | Accele  | erator Integration                               | 24  |

|                 | 2.2.1   | PCIe                                             | 24  |

|                 | 2.2.2   | Network interface                                | 26  |

|     | 2.2.3  | Tightly coupled SoC                                      |

|-----|--------|----------------------------------------------------------|

|     | 2.2.4  | Interface overheads                                      |

| 2.3 | Summ   | nary                                                     |

| 2.4 | Netwo  | orked computing systems                                  |

|     | 2.4.1  | Edge Networks                                            |

|     | 2.4.2  | Datacentre Networks                                      |

|     | 2.4.3  | In-network computing                                     |

|     | 2.4.4  | Network elements                                         |

|     | 2.4.5  | FPGAs for network applications                           |

|     | 2.4.6  | Cloud Computing                                          |

|     | 2.4.7  | FPGAs in the cloud                                       |

| 2.5 | Mathe  | ematical Modelling                                       |

|     | 2.5.1  | Sensor network modelling                                 |

|     | 2.5.2  | Distributed Stream Processing Models                     |

|     | 2.5.3  | Summary                                                  |

| ~.· |        |                                                          |

| _   |        | Modelling distributed computing with heterogeneous hard- |

| wai |        | 45                                                       |

| 3.1 |        | luction                                                  |

| 3.2 |        | ibutions                                                 |

| 3.3 |        | ed Work                                                  |

|     | 3.3.1  | Edge/Fog Computing                                       |

| 2.4 | 3.3.2  | Hardware acceleration                                    |

| 3.4 |        | rio and Metrics                                          |

|     | 3.4.1  | Latency                                                  |

|     | 3.4.2  | Bandwidth                                                |

|     | 3.4.3  | Energy                                                   |

|     | 3.4.4  | Financial Cost                                           |

| 3.5 | •      | osed Model                                               |

|     | 3.5.1  | Tasks                                                    |

|     | 3.5.2  | Implementations                                          |

|     | 3.5.3  | Platforms                                                |

|     | 3.5.4  | Network                                                  |

|     | 3.5.5  | Sources and Data                                         |

|     | 3.5.6  | Allocation Variables                                     |

|     | 3.5.7  | Constraints                                              |

| 3.6 | Perfor | mance Metrics                                            |

|    |       | 3.6.1  | End-to-End Latency                                                                                                       |

|----|-------|--------|--------------------------------------------------------------------------------------------------------------------------|

|    |       | 3.6.2  | Throughput                                                                                                               |

|    |       | 3.6.3  | Data-rate                                                                                                                |

|    |       | 3.6.4  | Energy Consumption                                                                                                       |

|    |       | 3.6.5  | Financial Cost                                                                                                           |

|    |       | 3.6.6  | Combined Evaluation Metrics                                                                                              |

|    | 3.7   | Case S | $tudy \dots \dots$ |

|    |       | 3.7.1  | Network                                                                                                                  |

|    |       | 3.7.2  | Tasks                                                                                                                    |

|    |       | 3.7.3  | Platforms                                                                                                                |

|    |       | 3.7.4  | Centralised Software                                                                                                     |

|    |       | 3.7.5  | In-network software                                                                                                      |

|    |       | 3.7.6  | Centralised Hardware                                                                                                     |

|    |       | 3.7.7  | In-network hardware                                                                                                      |

|    |       | 3.7.8  | Optimal Placement                                                                                                        |

|    |       | 3.7.9  | Summary                                                                                                                  |

|    |       | 3.7.10 | Event Driven Simulation                                                                                                  |

|    | 3.8   | Furthe | er Analysis                                                                                                              |

|    |       | 3.8.1  | Relative Computing Capability                                                                                            |

|    |       | 3.8.2  | Task Data Reduction                                                                                                      |

|    |       | 3.8.3  | Network Structure                                                                                                        |

|    |       | 3.8.4  | Hardware Acceleration                                                                                                    |

|    | 3.9   | Genera | ating In-Network Task and Hardware Placement with Hetero-                                                                |

|    |       | geneou | ıs Hardware                                                                                                              |

|    |       | 3.9.1  | Objective function formulation                                                                                           |

|    |       | 3.9.2  | Case Study                                                                                                               |

|    |       | 3.9.3  | Evaluation with Synthetic Networks                                                                                       |

|    |       | 3.9.4  | Summary                                                                                                                  |

|    | 3.10  | Summ   | ary                                                                                                                      |

| Cl | hapte | er 4 Q | quantifying the Latency Overheads of FPGA Accelerators 92                                                                |

|    | 4.1   | Introd | uction                                                                                                                   |

|    | 4.2   | Contri | butions                                                                                                                  |

|    | 4.3   | Relate | d Work                                                                                                                   |

|    | 4.4   | Experi | ments                                                                                                                    |

|    |       | 4.4.1  | Latency                                                                                                                  |

|    |       | 4.4.2  | Throughput                                                                                                               |

|    |       |        |                                                                                                                          |

|              | 4.4.3         | Platforms                                                    | 96        |

|--------------|---------------|--------------------------------------------------------------|-----------|

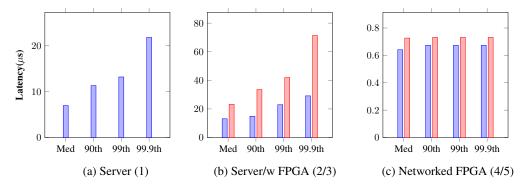

| 4.5          | Result        | ······································                       | 99        |

|              | 4.5.1         | Median Latency                                               | 99        |

|              | 4.5.2         | FPGA Latency Breakdown                                       | 100       |

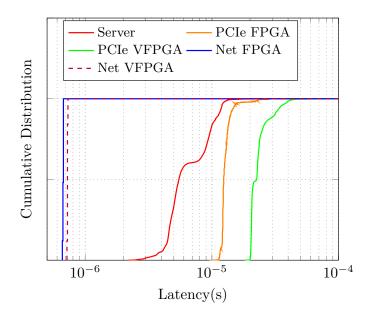

|              | 4.5.3         | Latency Distributions                                        | 101       |

|              | 4.5.4         | Tail Latencies                                               | 101       |

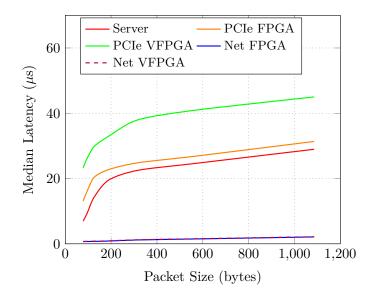

|              | 4.5.5         | Packet Size                                                  | 102       |

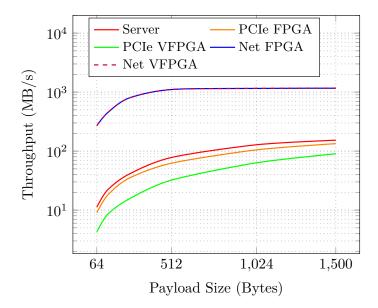

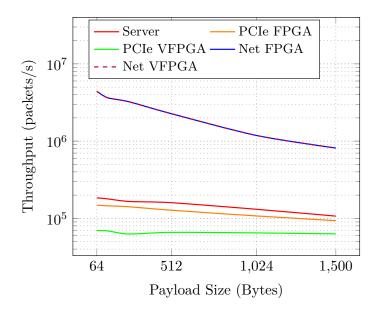

|              | 4.5.6         | Throughput                                                   | 103       |

| 4.6          | Discus        | ssion                                                        | 104       |

|              | 4.6.1         | PCIe Accelerators                                            | 104       |

|              | 4.6.2         | Network-attached Accelerators                                | 105       |

| 4.7          | Summ          | ary                                                          | 106       |

| Chapte       | on E N        | Near-Edge FPGA Acceleration for the Internet of Thing        | .c1 0.7   |

| опары<br>5.1 |               | uction                                                       |           |

| 5.2          |               | ibutions                                                     |           |

| 5.3          |               | ed Work                                                      |           |

| 5.4          |               | and Experiments                                              |           |

| 0.1          | 5.4.1         | Application                                                  |           |

|              | 5.4.2         | Measurements                                                 |           |

|              | 5.4.3         | Platforms                                                    |           |

| 5.5          | Result        | SS                                                           |           |

|              | 5.5.1         | Isolated Edge Node Measurements                              |           |

|              | 5.5.2         | Impact of Multiple Edge Devices                              |           |

|              | 5.5.3         | Discussion                                                   | 123       |

| 5.6          | Accele        | erator Location                                              | 124       |

|              | 5.6.1         | Results                                                      | 126       |

|              | 5.6.2         | Discussion                                                   | 129       |

| 5.7          | Summ          | ary                                                          | 131       |

| <b>C1</b>    |               | No. 10. 10. 10. 10. 10. 10. 10. 10. 10. 10                   | 100       |

| _            |               | Conclusions and Future Work earry of Contributions           | 132       |

| 6.1          | 6.1.1         | · ·                                                          | 132       |

|              | 0.1.1         | Mathematical representation of in-network and near edge com- | 199       |

|              | 6.1.2         | puting                                                       | 132 $133$ |

|              | 6.1.2 $6.1.3$ | Quantifying costs associated with FPGA accelerators          | 133       |

|              | 6.1.3         | Demonstration of in-network FPGA acceleration                | 133       |

| 6.2          |               | Research                                                     | 133       |

|              |               |                                                              |           |

|     | 6.2.1 | Practically validating the model                          |

|-----|-------|-----------------------------------------------------------|

|     | 6.2.2 | Improving optimisation runtime                            |

|     | 6.2.3 | Developing generalised in-network FPGA infrastructure 134 |

|     | 6.2.4 | Combination of model and FPGA infrastructure 135          |

|     | 6.2.5 | Defining accelerator communication protocols              |

| 6.3 | Summ  | ary                                                       |

## List of Tables

| 3.1 | Summary of symbols used in formulation             | 57  |

|-----|----------------------------------------------------|-----|

| 3.2 | Case study task values                             | 67  |

| 3.3 | Case study platform values                         | 68  |

| 3.4 | Case study SW results                              | 68  |

| 3.5 | Case study HW results                              | 70  |

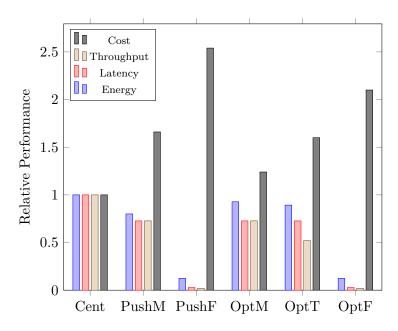

| 3.6 | Performance metrics for MILP optimisation of model | 71  |

| 3.7 | Different placement policies used in simulations   | 75  |

| 3.8 | Summary of task parameter values                   | 82  |

| 3.9 | Summary of available platforms                     | 83  |

| 4.1 | Latency results                                    | 99  |

| 4.2 | Network-attached FPGA delays                       | 100 |

| 5.1 | Experimental results                               | 19  |

| 5.2 | Network traversal times                            | 125 |

## List of Figures

| 2.1  | Representative modern FPGA architecture                            |

|------|--------------------------------------------------------------------|

| 2.2  | Xilinx 7 Series CLB arrangement                                    |

| 2.3  | Xilinx DSP48E1 architecture                                        |

| 2.4  | Partial reconfiguration example                                    |

| 2.5  | Example network infrastructure                                     |

| 2.6  | Example datacentre network                                         |

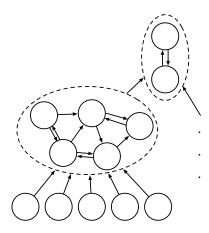

| 3.1  | Example networked system                                           |

| 3.2  | Network node abstraction                                           |

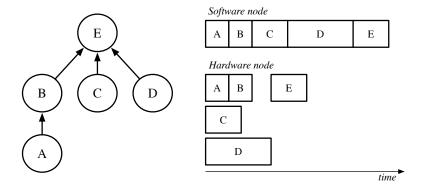

| 3.3  | Difference between software and hardware nodes 60                  |

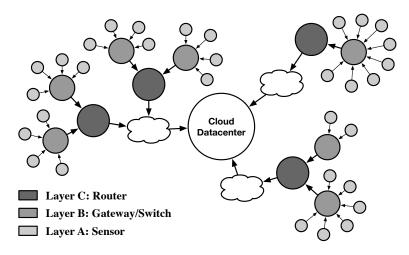

| 3.4  | Case study network structure                                       |

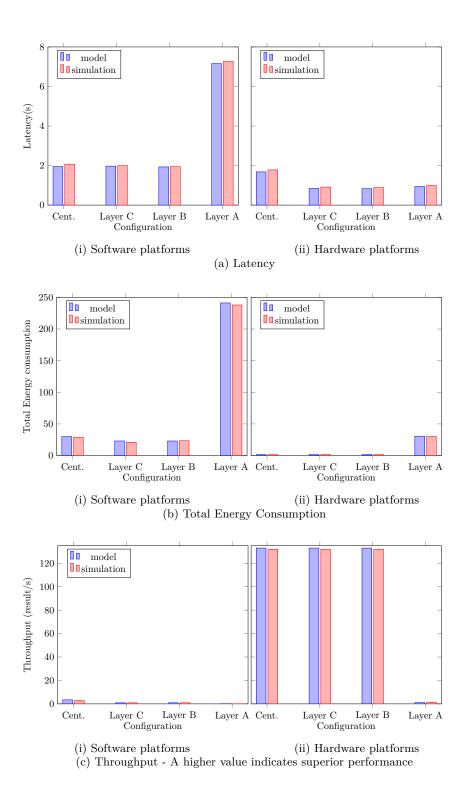

| 3.5  | Model vs simulation results                                        |

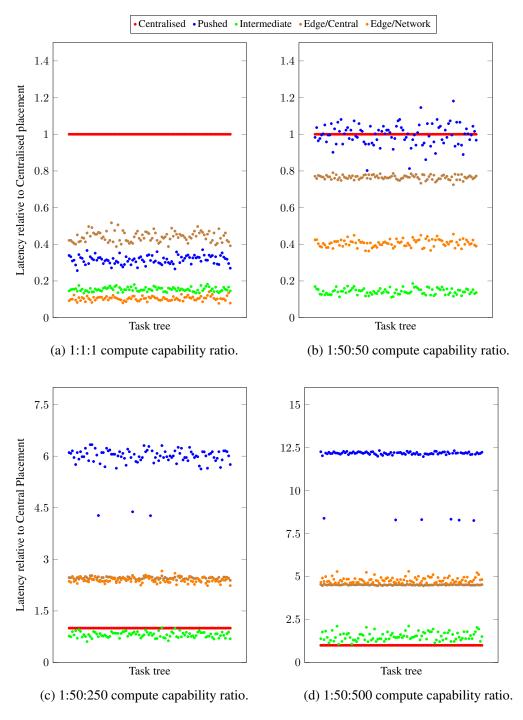

| 3.6  | Compute capability results                                         |

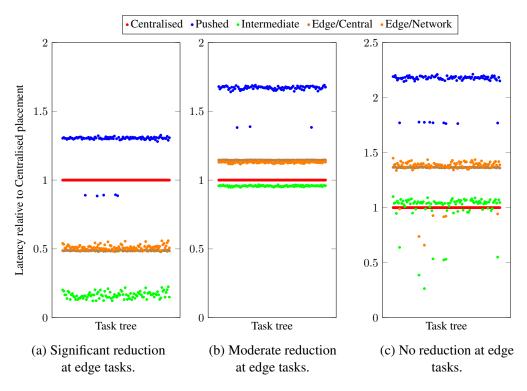

| 3.7  | Reduction factor results                                           |

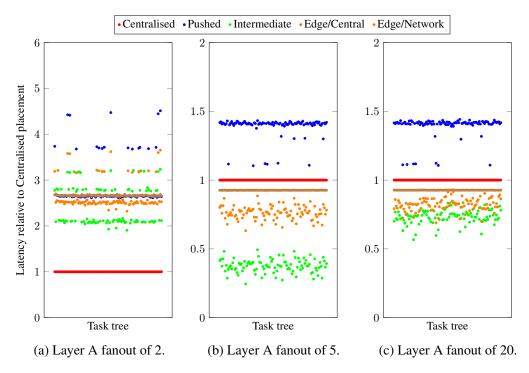

| 3.8  | Network fanout results                                             |

| 3.9  | Naive vs. model placement                                          |

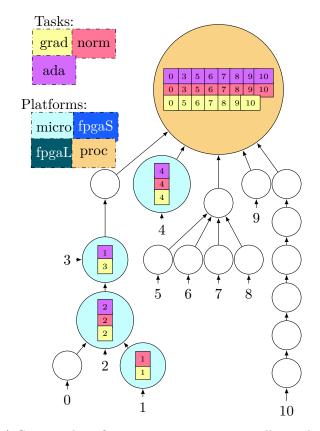

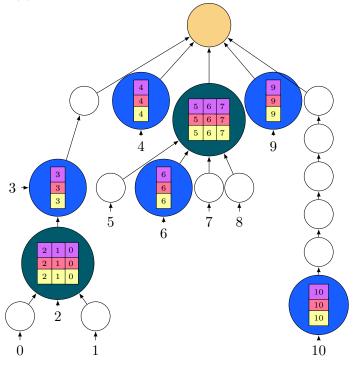

| 3.10 | Configurations generated by optimization                           |

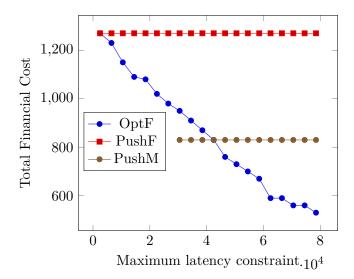

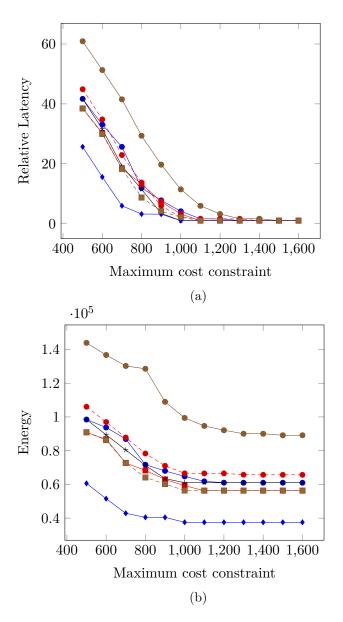

| 3.11 | Optimal cost with latency constraint                               |

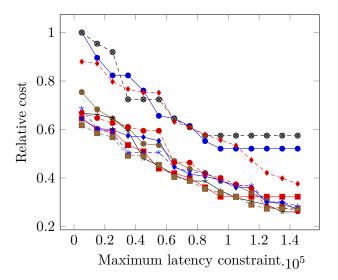

| 3.12 | Sythnthetic networks optimised for cost with latency constraint 86 |

| 3.13 | Synthetic networks optimised for energy and latency with cost con- |

|      | straint                                                            |

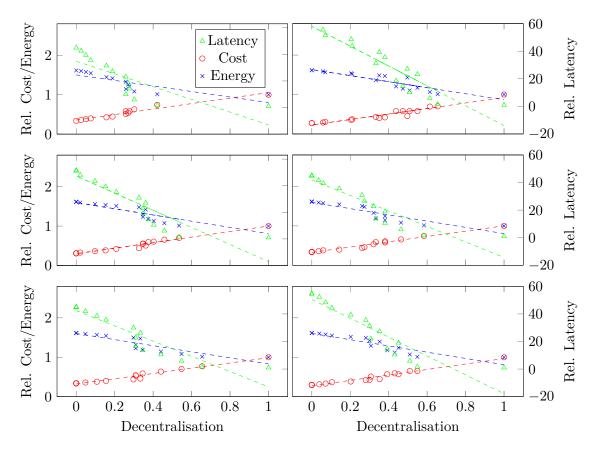

| 3.14 | Optimal vs pushed for varying task centralisation                  |

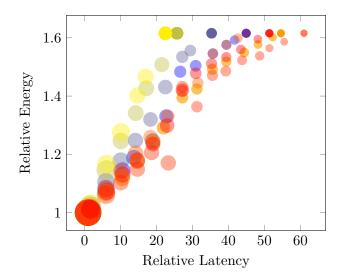

| 3.15 | Optimal latency and energy vs pushed down                          |

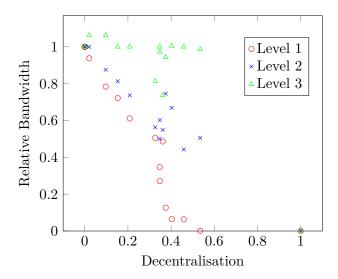

| 3.16 | Bandwidth consumtion for varying centralisation of tasks 90        |

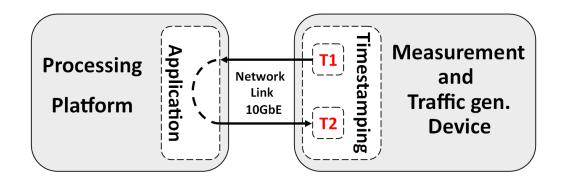

| 4.1  | Outline of the experimental setup                                  |

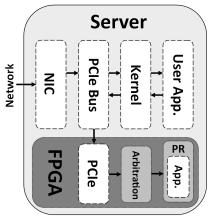

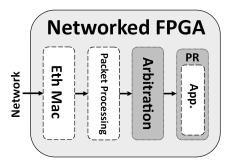

| 4.2  | Accelerator configurations                                         |

| 4.3  | Tail latency results                                               |

| 4.4  | CDF of latencies                                                   |

| 4.5  | Packet size differences                                                  | 102 |

|------|--------------------------------------------------------------------------|-----|

| 4.6  | Throughput results                                                       | 104 |

| 4.7  | Packet rate results                                                      | 105 |

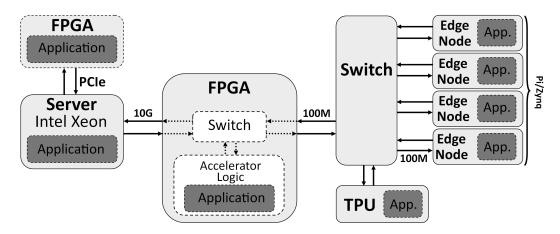

| 5.1  | Experimental testbed                                                     | 110 |

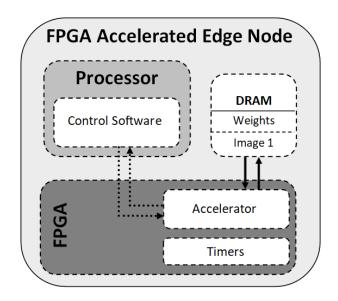

| 5.2  | Zynq accelerated edge node                                               | 113 |

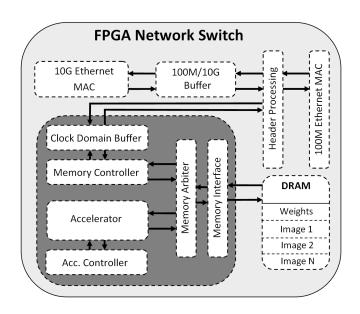

| 5.3  | FPGA network switch accelerator                                          | 116 |

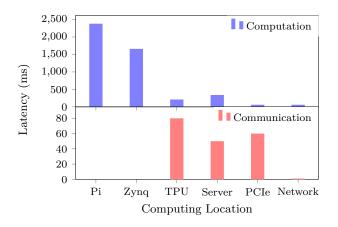

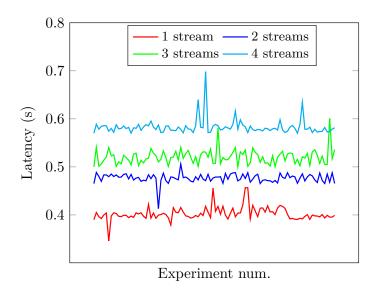

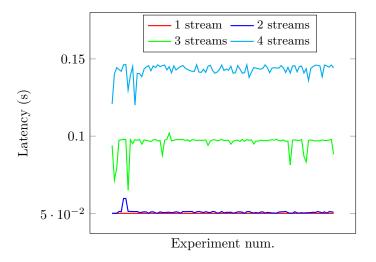

| 5.4  | Experimental results                                                     | 119 |

| 5.5  | Multiple edge nodes offloading to cloudlet $\ldots \ldots \ldots \ldots$ | 122 |

| 5.6  | Multiple edge nodes offloading to networked FPGA                         | 122 |

| 5.7  | Analysed network structure                                               | 124 |

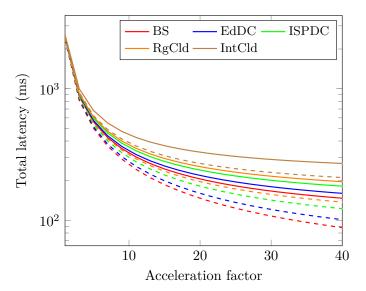

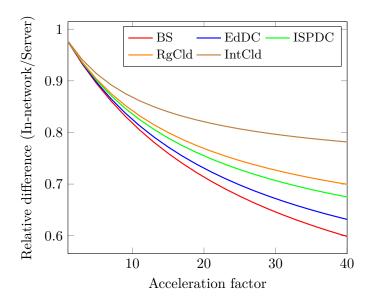

| 5.8  | Estimation results                                                       | 127 |

| 5.9  | Network-attacehd latency redcution                                       | 128 |

| 5.10 | Effects of 200ms base computation time                                   | 129 |

| 5.11 | Effect of 100ms base computation time                                    | 130 |

## Acknowledgments

I would like to thank my supervisor Suhaib Fahmy for giving me this opportunity. His guidance has been invaluable, and I am extremely grateful for all of the time he spent helping me.

I would also like to thank my friends Lenos and Alex, also part of the Connected Systems group, who at this point are still completing their PhDs. Their advice and company is much appreciated, and helped get through the day to day in the lab.

Lastly, I thank my partner Eleanor, whom I met for the first time shortly after beginning the PhD. Her patience, love, and kindness have kept me motivated and I wouldn't have been able to complete this thesis without her.

## **Declarations**

This thesis is submitted to the University of Warwick for the degree of Doctor of Philosophy. The work contained in this thesis comprises my own work. This thesis has not previously been submitted for a degree at another university.

Parts of this thesis have been published by the author:

- Ryan A. Cooke, Suhaib A. Fahmy, In-network online data analytics with FP-GAs, in Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), 2017 [1].

- 2. Ryan A. Cooke, Suhaib A. Fahmy, A model for distributed in-network and nearedge computing with heterogeneous hardware, in Future Generation Computer Systems (FGCS), vol. 105, 2020 [2].

- 3. Ryan A. Cooke, Suhaib A. Fahmy, Quantifying the latency benefits of near-edge and in-network FPGA acceleration, in Proceedings of the International Workshop on Edge Systems, Analytics and Networking (EdgeSys), 2020 [3].

- 4. Ryan A. Cooke, Suhaib A. Fahmy, Characterizing latency overheads in the deployment of FPGA accelerators, in Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), 2020 [4].

- 5. Ryan A. Cooke, Suhaib A. Fahmy, Exploring Hardware Accelerator Offload for the Internet of Things, submitted to: it Information Technology

## Abstract

Hardware acceleration has become more commonly utilised in networked computing systems. The growing complexity of applications mean that traditional CPU architectures can no longer meet stringent latency constraints. Alternative computing architectures such as GPUs and FPGAs are increasingly available, along with simpler, more software-like development flows. The work presented in this thesis characterises the overheads associated with these accelerator architectures. A holistic view encompassing both computation and communication latency must be considered. Experimental results obtained through this work show that networkattached accelerators scale better than server-hosted deployments, and that host ingestion overheads are comparable to network traversal times in some cases. Along with the choice of processing platforms, it is becoming more important to consider how workloads are partitioned and where in the network tasks are being performed. Manual allocation and evaluation of tasks to network nodes does not scale with network and workload complexity. A mathematical formulation of this problem is presented within this thesis that takes into account all relevant performance metrics. Unlike other works, this model takes into account growing hardware heterogeneity and workload complexity, and is generalisable to a range of scenarios. This model can be used in an optimisation that generates lower cost results with latency performance close to theoretical maximums compared to naive placement approaches. With the mathematical formulation and experimental results that characterise hardware accelerator overheads, the work presented in this thesis can be used to make informed design decisions about both where to allocate tasks and deploy accelerators in the network, and the associated costs.

## Abbreviations

API Application Programming Interface

AR Augmented Reality

**ASIC** Application Specific Integrated Circuit

**AXI** Advanced eXtensible Interface

**BRAM** Block Random Access Memory

**CLB** Configurable Logic Block

CNN Convolutional Neural Network

CPU Central Processing Unit

**DMA** Direct Memory

**DRAM** Dynamic Random Access Memory

**DSP** Digital Signal Processing

**DNN** Deep Neural Network

**FIFO** First In First Out

**FFT** Fast Fourier Transform

FPGA Field Programmable Gate Array

**GPU** Graphics Processing Unit

- **HDL** Hardware Description Language

- **HLS** High Level Synthesis

- IC Integrated Circuit

- **IoT** Internet of Things

- **ISP** Internet Service Provider

- **IP** Internet Protocol

- KNN K-Nearest Neighbour

- LAN Local Area Network

- LTE Long Term Evolution

- ${f LUT}$  Look Up Table

- MAC Media Access Control

- MILP Mixed Integer Linear Programming

- **NFV** Network Function Virtualisation

- NIC Network Interface Card

- NN Neural Network

- NoC Network on a Chip

- ${f NPU}$  Network Processing Unit

- **OFDM** Orthogonal Frequency Division Multiplexing

- PCIe Peripheral Component Interconnect Express

- ${f PL}$  Programmable Logic

- **PLL** Phase Locked Loop

PR Partial Reconfiguration

${f PS}$  Processing System

RAM Random Access Memory

**SDN** Software Defined Networking

SoC System on a Chip

SRAM Static Random Access Memory

${f SVM}$  Support Vector Machine

TCP Transmission Control Protocol

ToR Top of Rack

${f TPU}$  Tensor Processing Unit

**UDP** User Datagram Protocol

VM Virtual Machine

**WAN** Wide Area Network

## Chapter 1

## Introduction

Computational offloading is a term used to describe a scenario where one computing system transmits data to another, where computation is carried out, and the result transmitted back. The total computation latency of a task, the power consumed by the hardware, and the processing throughput can all be improved using this approach, when the target platform is more capable.

It can be used to describe a range of scenarios. Early implementations of this technique involved central processing units (CPUs) offloading to a co-processor such as separate floating point units, which were optimised for floating point arithmetic [5]. Computation latency could be drastically reduced, and in some cases the main processor would be free to carry out other tasks while waiting for the result. As processing tasks became more complex with the growth of applications such as graphics rendering, co-processors could begin to take the form of separate chips on the same board, or as chips hosted on a separate expansion board, connected through external interfaces such as peripheral component interconnect (PCI) [6]. Modern system-on-chip (SoC) architectures comprise multiple different hardware cores to accelerate particular tasks such as encryption, digital signal processing, or graphics rendering [7].

The growth of the Internet and networking technologies presented opportunities for computational offload to distinct machines over a network [8; 9; 10; 11; 12; 13]. As network bandwidth improved, it became more viable to transmit significant amounts of data to a remote computing resource. The platform carrying out the computation no longer had to be restricted to the same location as the data source. The arrival of data centre cloud computing allowed for computing resources to be centralised and shared across many clients [14]. There are numerous benefits to this approach. Computing resources can be scaled with much less friction and

hardware can be modified to enhance processing capability without disturbing the data source. This is particularly valuable in applications where the data source is in a hard-to-reach location.

Transmitting data to another processing platform has an associated communication cost, however [15]. The improvement to performance, whatever the metric may be, offsets this cost. Recently, there has been a surge of interest in low-latency, 'real-time' applications, driven by factors such as the internet of things (IoT) and a growing demand for responsive, complex web applications [15; 16; 17]. Industrial IoT systems rely on networked sensors and data acquisition systems, and have strict latency requirements on closed-loop control. Mobile applications requiring complex image processing such as augmented reality (AR) have to meet latency targets to provide an acceptable user experience [16]. Smart vehicles must process data and communicate with other vehicles in real-time to satisfy safety constraints [18].

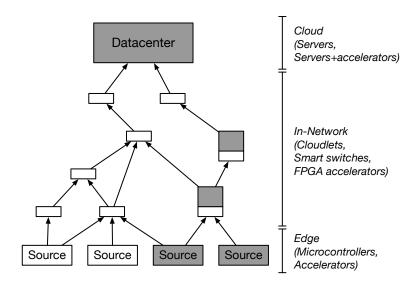

This presents a problem – processing may be too complex to perform at the data source in the required time interval, so must be offloaded. While transmitting data to the cloud can reduce the computation latency, the communication penalty may be too great, and thus the total latency would still violate the required constraints. This has led to the paradigm of 'edge computing', where computation is offloaded to resources closer to the data source. This could mean improved hardware at the data source itself - but this results in difficult management of hardware and increased cost. Alternatively, smaller data centres or servers could be placed on local networks with the data source, removing the need for data to be transmitted over the Internet. Processing could even be moved into the networking elements that facilitate the transfer of data between machines, resulting in even less communication time. This is known as 'in-network' computing [19]. The resultant scenario is one where there are a range of processing elements in different locations, with different capabilities and constraints, that all offer a target for computational offload. There is now an opportunity for improved processing times, with lower communication costs than when using computation entirely at the data source, or entirely in the cloud. A new set of key challenges must now be addressed to best make use of these systems.

One of these challenges is where in the network to offload tasks. An application may comprise many tasks, each with different requirements and dependencies on other tasks, and must be allocated across a set of heterogeneous offload platforms with varying computational properties. This is a complex decision, where the profile of the application and the available resources must be accounted for. As these networked systems increase in scale, this becomes even more challenging. Systems

can become large enough that manual evaluation of task placement can become impossible. Design decisions must be made to balance opposing performance metrics, and to make the best use of finite resources.

Another challenge is ensuring that the in-network or edge computing resources can provide adequate computational performance. Despite being closer to the data sources, this hardware must still reduce computation latency enough to justify offloading to them. Hardware must be able to be shared across multiple client devices, and be able to perform complex processing quickly. In the case of innetwork computing, networking elements are being extended to perform additional processing, so hardware that causes minimal disruption of the usual networking functions must therefore be used. The integration between the network flow and the computations datapaths can also influence latency significantly.

Hardware acceleration is necessary in order to fulfil these requirements. Devices called field programmable gate arrays (FPGAs) are particularly well suited to this. They comprise of an array of simple logic blocks and other computational resources, linked through a configurable interconnect, which can be used to implement accelerator architectures optimised to perform a particular task, providing a computational benefit compared to standard CPU architectures. Being reconfigurable means they can support a range of applications and be dynamically configurable at runtime. They are particularly useful for in-network computing as some network elements such as switches, base stations, and routers already utilise them to carry out networking tasks, and are good at packet processing. FPGAs offer a greater range of deployment and integration capabilities compared to other hardware accelerators such as GPUs [20], and are a key enabler in meeting performance requirements at the network edge as applications scale. In Chapter 2, the differences between accelerator platforms are discussed in more detail.

#### 1.1 Motivations

Computing is becoming increasingly connected. Networked computing systems are becoming more complex, larger in scale, and operate under greater performance constraints. Various factors, such as the growth of the IoT, commercial cloud computing and developments in hardware have been significant drivers of this.

A key challenge in effective use of networked systems for computational offload of tasks is the partitioning and placement of sub-tasks amongst computational nodes. Where computation is carried out is becoming more important. Ad-hoc placement of tasks may have been viable for smaller systems, but as the number of variables grows, finding solutions that meet required constraints is not viable. Not only are there systems with more connected devices, the devices within the system are becoming more capable. Network elements that were historically passive and simply passed data between nodes, can now be tightly coupled with compute, increasing the number of possible placement solutions. Additionally, edge nodes such as sensors and other data sources which typically just produced data, are also becoming more capable due to the greater availability of cheap microcontrollers and single board computers, such as the Raspberry Pi family of devices [21]. These platforms can handle data acquisition, networking, and computation, and have a small enough form factor that they can be deployed in a range of scenarios. Increased hardware heterogeneity, and the growing market for hardware accelerators such as FPGAs add even more variables to networked system deployment. Taking this into consideration, it becomes clear that a holistic view accounting for modern trends and advancements, must be used when making decisions regarding hardware deployment and task placement. There are such an abundance of options and implications that any ad-hoc or naive decision making is likely to lead to sub-optimal performance.

As more heterogeneous computing platforms become available for lower costs, and existing platforms improve their capabilities, the decision on what combinations of hardware to use becomes more important. FPGA acceleration provides an opportunity to increase processing capability at selected nodes, and unlike other accelerator platforms, allow for a greater flexibility in how they are integrated into the network. Unlike alternative accelerator platforms such as GPUs, FPGAs need no CPU host, and can be connected directly to the network [22].

A greater understanding of the implications of using this approach is needed. The costs and benefits of utilising these accelerators must be quantified, and generalisations for types of applications made. Understanding of the trade-offs between computation and communication is vital to making informed decisions regarding accelerator deployment.

### 1.2 Objectives

The objectives of this research are as follows:

1. To develop a methodology for exploring and evaluating heterogeneous networked systems used to offload complex applications, and to quantify key performance metrics.

- 2. To quantify the costs associated with the deployment of reconfigurable accelerators in alternative offload configurations.

- 3. To characterize the performance of emerging application types with different compute placement strategies, taking into account the variation in computing capability and connectivity of heterogeneous platforms.

#### 1.3 Contributions

The main contributions of this work are a set of tools, measurements, and investigations that can be used to evaluate the placement of offloaded tasks across a network of heterogeneous computing and networking elements. These can be summarised as follows:

- 1. A mathematical formulation of this scenario, which allows for the detailed description of a heterogeneous network, tasks, and accelerator hardware. The model, unlike other related works, is generalised to account for heterogeneous hardware accelerators, complex task structures, and is easily extensible to model a range of scenarios, capturing all the important metrics of interest.

- 2. Derived from this model, generalised insights into how computation should be offloaded across networked devices depending on various application and network characteristics.

- 3. This model can be used within a mixed integer linear programming optimisation to generate hardware and task allocations to meet various performance objectives typically used when considering computational offload.

- 4. Experiments used to determine inherent latency limits in the use of FPGA hardware accelerators in various deployment scenarios in a networked context.

- 5. The use of an FPGA network switch extended to perform additional computation in an edge computing case study, and show the resulting performance benefits against other competing strategies.

### 1.4 Thesis Roadmap

Chapter 2 is a comprehensive background and literature review. It contains background and comparisons of different computing architectures, how they are integrated into networked systems, and where they can be deployed. How this deployment has been modelled in other works is also discussed.

Chapter 3 details a mathematical model that can be used to describe and evaluate the deployment of hardware acceleration and the offload of computing tasks within a network of connected devices. It also demonstrates the usage of this model to generate optimal task and hardware placement for a given scenario and set of constraints. The optimisation is evaluated against naive placement strategies using a representative case study as well as synthetically derived scenarios.

Chapter 4 focuses on experiments designed and carried out to determine latency characteristics in the deployment of FPGA accelerators. Both hosted PCIe and server-less in-network deployments are characterised.

Chapter 5 is a case study comparing in-network FPGA acceleration with other offload strategies for a complex image processing application. The in-network approach uses an augmented FPGA network switch, and is compared to edge node and cloudlet offloaded computation. This chapter details the design of the experimental testbed, results, and general insights that can be derived from the experiments. Results show that the host ingestion latency is comparable to the network traversal time.

Chapter 6 discusses further work and conclusions drawn from the work presented in this thesis.

#### 1.5 Publications

Work presented in this thesis has featured in the following publications.

- 1. Ryan A. Cooke, Suhaib A. Fahmy, *In-network online data analytics with FP-GAs*, in Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), 2017 [1].

- 2. Ryan A. Cooke, Suhaib A. Fahmy, A model for distributed in-network and near-edge computing with heterogeneous hardware, in Future Generation Computer Systems (FGCS), vol. 105, 2020 [2].

- 3. Ryan A. Cooke, Suhaib A. Fahmy, Quantifying the latency benefits of near-edge and in-network FPGA acceleration, in Proceedings of the International Workshop on Edge Systems, Analytics and Networking (EdgeSys), 2020 [3].

- 4. Ryan A. Cooke, Suhaib A. Fahmy, *Characterizing latency overheads in the deployment of FPGA accelerators*, in Proceedings of the International Conference on Field Programmable Logic and Applications (FPL), 2020 [4].

5. Ryan A. Cooke, Suhaib A. Fahmy, Exploring Hardware Accelerator Offload for the Internet of Things, submitted to: it - Information Technology.

### Chapter 2

## Background and Literature Review

When considering modern networked computing systems, there are two primary considerations: the computing resource used to complete the processing, and where they are located in the network. As discussed in Chapter 1, these systems are increasingly heterogeneous, utilizing a variety of hardware architectures to perform the required computation. Each of these platforms have varying capabilities and trade-offs. Additionally, there are a growing number of network nodes capable of hosting these hardware platforms, increasing the deployment possibilities.

This means that there are a greater variety of deployment options when considering distributed hardware acceleration. It becomes more difficult to evaluate task placement, and to manually design these systems. Existing mathematical models don't take these recent trends into account, or are designed for runtime task allocation in an environment with heterogeneous hardware architectures.

How these architectures are integrated to distributed, networked processing systems is also a significant challenge, with implications on performance. There are now a greater variety of integration techniques, with little experimental evaluation.

This chapter first examines the variety of processing architectures available in modern systems. It then examines the various integration possibilities, and relationship with the supporting network infrastructure, highlighting the need for experimental comparisons between approaches. Finally, it contains a study of other modelling efforts, and how they aren't sufficient for modelling heterogeneous, distributed systems given modern advances.

#### 2.1 Computing Platforms

In this thesis, the term computing platform is used to define a hardware architecture capable of carrying out a computation. Historically, this processing would be carried out on a general-purpose processor, but as workloads have increased in scale and complexity, alternative accelerator platforms have seen a surge of interest.

#### 2.1.1 Central Processing Units

General-purpose central processing units (CPUs) are fundamental components of computing systems. While there is a significant variety of specifications and implementations, the general execution model is the same across most devices. The task to be carried out is expressed through a program, a set of instructions composed from the processor's instruction set – the set of fundamental operations that a CPU can perform. The program is stored in memory, and instructions are executed sequentially.

#### **Processing Model**

At the start of each cycle, the next instruction to be executed is fetched from program memory, pointed to by a special purpose register called the program counter (PC). The instruction typically comprises an opcode denoting the operation to be performed, and register and memory location references to the operands. After being fetched, it is decoded into signals that control the execution unit. The decoded instruction triggers a series of actions that execute the operation. These actions will vary depending on the operation required, but usually involve loading operands into registers, fast memory local to the processor. Arithmetic and logical operations are carried out between these registers.

#### Application Development

CPUs are designed for flexibility, and must be able to implement a wide range of applications. Users can define their programs at different levels of abstraction. At the lowest level, programs can be written in the assembly language for the target processor instruction set. Programs are written directly in terms of CPU instructions by the user. For most applications, this approach is impractical and tedious, and is not realistic to write anything more than simple code at this level. The resultant program is also only able to be executed by an architecture that uses the same instruction set. Most programs are expressed in higher level languages that allow

for architecture independent, complex functions to be expressed more succinctly than at the instruction level. For some languages, such as C or C++, the program is compiled from this higher level expression down to machine instructions that are directly executed by the processor. Other languages are compiled down to hardware independent bytecode, which runs on an intermediate virtual machine, which has hardware-specific implementations. This way the same executable can be executed on any hardware, given that it has a virtual machine implementation that can translate the bytecode to native processor instructions.

#### Types of CPU

Due to the general-purpose nature of CPU-based computation, there are many variants of the basic architecture that are used for difference application domains.

Server class processors such as the Intel Xeon family are designed to handle larger, more complex workloads, and many tasks at the same time. In comparison to other processors, they usually have many cores on the same silicon die. Each core is capable of independent concurrent operation, and is often also multi-threaded, which allows for the core to be rapidly switched between contexts. This effectively allows multiple software processes to be run concurrently on the same, time-shared physical core. These devices are expensive, and compared to processors used in other contexts, have high power consumption and heat dissipation.

The next class of processors are for use in general-purpose, desktop machines, such as the Intel Core series. Compared to server-class processors, these devices have fewer cores and are cheaper.

Processors not designed for use in a desktop or server environment can be classed as embedded CPUs. They are used in application specific deployments, often controlling or interfacing with external actuators or sensors. In comparison to the other classes, they are lower-power and cheaper. Single-board computers such as the Raspberry Pi are often used to control embedded applications, and utilise 32-bit multi-core embedded processors capable of running Linux. Micro-controllers integrate a processor, memory, and other peripherals onto the same die and are generally even more low power and low capability. Small 8-bit or 16-bit processors may be used in devices with severe power constraints such as remote sensor nodes.

In all cases, when offloading to or from processors, data must traverse a network interface and standard bus into processor memory space.

#### 2.1.2 Field Programmable Gate Arrays

Field programmable gate arrays (FPGAs) are silicon integrated circuits comprising an array of configurable logic resources. There are several primary vendors of these devices, the most notable being Xilinx and Intel. While these vendors hold a majority of the market, other vendors exist, such as Lattice, who specialise in small low-power solutions, and Microsemi, who offer specialized products such as radiation-hardened devices.

#### Architecture

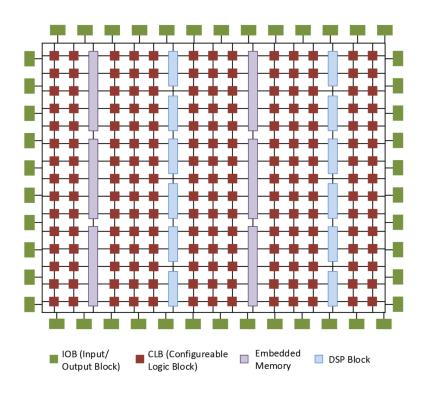

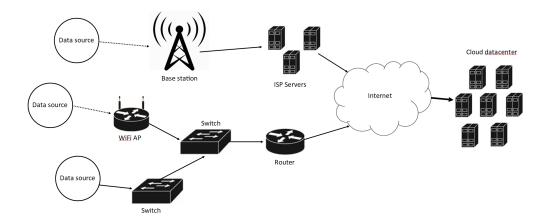

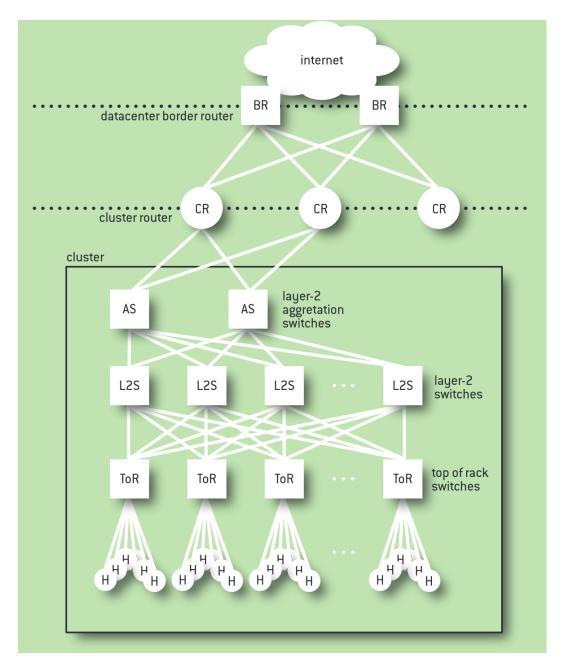

Figure 2.1: Representative modern FPGA architecture [23]

Modern FPGA architectures, regardless of vendor, are based around a generic design. Figure 2.1 shows a high-level overview of a Xilinx FPGA architecture. Users can express a digital circuit in a high-level abstraction, which goes through a flow of vendor tools to convert the circuit to be implemented using these logic resources on the FPGA fabric.

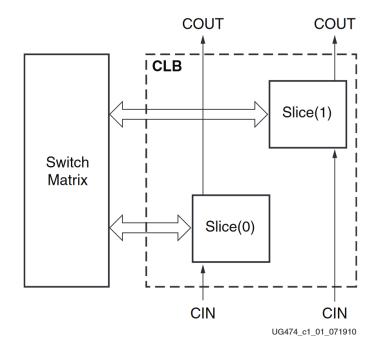

User logic is implemented via an array of configurable logic blocks (CLBs) [24], which are connected to other CLBs through a switching matrix. Each CLB comprises several slices, where each slice typically contains a look-up table (LUT) and

Figure 2.2: Xilinx 7 Series CLB arrangement [24]

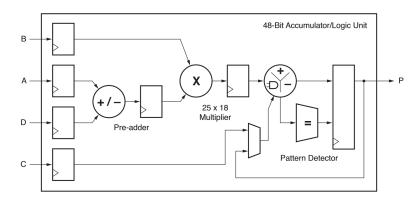

Figure 2.3: Xilinx DSP48E1 architecture [25]

storage elements like flip-flops or small amounts of RAM. For example Xilinx 7 series FPGAs use CLBs with 2 slices, as in Figure 2.2, with each slice having four 6-input LUTs, 16 flip flops and 256-bits of distributed RAM. The CLB LUTs can be configured to implement a large variety of logic functions, and chained together to implement even more complex operations. In addition to CLBs, most modern devices also have hardened blocks of logic optimised for digital signal processing, such as the DSP48 [25] blocks built into Xilinx FPGAs (Figure 2.3). DSP slices can be used to implement complex arithmetic functions with fewer resources.

Hardened Block RAM (BRAM) is also usually present in modern FPGA architectures. This provides storage within the fabric, reducing the need for costly off-chip memory transfers. IO-blocks (IOB) are configurable blocks that contain the appropriate signal conditioning to allow for signals to be brought into or out of the FPGA. Any signal on any pin must go through an IOB. IOBs are arranged into banks - for example, Xilinx 7 series banks contain 50 IOBs. high-speed transceivers are also commonly implemented, to allow the FPGA to interface with high-speed signals such as those used in PCIe and Ethernet. Implementing this functionality using CLBs would consume significant resources, or not meet required performance standards.

All resources are connected through a routing network that routes signals throughout the FPGA. Dedicated interconnect is used to route clock signals. Clocks can be introduced to the FPGA through IO pins. Global clock lines can be used to route the clock to multiple elements throughout the device. These lines ensure minimal skew in comparison to the general-purpose routing resources. Many FPGAs include built-in PLLs or DLLs to synthesise signals of a configurable frequency.

#### **Application Development**

The user can express their design at different levels of abstraction. As designs and FPGA devices are complex, it would not be viable to specify the design at the individual gate and wire level. The lowest level of abstraction typically used by designers is the register transfer level (RTL). This is a paradigm where digital circuits are modelled as combinational transformations on data as they move between registers. Designers write this RTL description in a hardware description language (HDL), the most popular being 'Verilog' and 'Very high-speed Integrated Circuit Description Language' (VHDL). All mainstream vendor tools accept these languages. Once a design has been described with a HDL at the RTL level, it is converted to a low-level description by vendor tools in a process called synthesis. The synthesised circuit is then mapped to the target FPGA resources by the vendor place-and-route tool, creating a device specific configuration that implements the desired circuit. This configuration is then encoded into a bitstream that can be loaded into the FPGA configuration memory.

Designing at the RTL level requires knowledge of HDL, digital logic design, and some knowledge of the target FPGA architecture. These present one of the main barriers to entry for developing for FPGAs, leading to the development of language and design flows that let users work at an even higher levels of abstraction, an approach commonly referred to as high-level Synthesis (HLS). Here, designers

describe the design at an algorithmic level using languages such as C++. Both Xilinx and Intel offer HLS tools for their platforms.

Vivado HLS is the commercial Xilinx HLS tool, where users express accelerator designs using C or C++ [26]. The user writes functions in these languages that are compiled into HDL descriptions. Features such as loop unrolling are available which allow for the user to control to what extent loop constructs are implemented spatially in parallel in the resulting FPGA design. This can increase the performance of the design with the penalty of it using more resources. Python-based HLS has also been demonstrated with the open source Migen framework [27]. The framework also includes a set of free IP cores written in python that can be instantiated into user designs. Testbenches can also be written in python.

The open computing language (OpenCL) framework is also utilised for FPGA HLS. This framework allows for cross-platform code to be written in general-purpose languages such as C++, which can then be targeted to heterogenous platforms such as GPUs and FPGAs. Intel offer this as part of their FPGA SDK [28], and Xilinx as part of their SDAccell platform[29]. The benefit of this approach is that it allows for side-by-side development of the base software application that will run on the host, tightly coupled, or soft-core processor and the hardware accelerator. These tools hide details regarding the software and hardware interfacing from the user. They represent a growing trend of heterogeneous computing system designs. Various academic works look to extend OpenCL FPGA integration for use with other languages. The work in [30] enables the coupling of Java programs with FPGA accelerators within th OpenCL ecosystem. This is useful for large-scale analytics applications as many of the frameworks used for this, such as Hadoop, utilise Java frontends. Another work [31] presents a similar strategy for accelerating python code with FPGAs using OpenCL.

In addition to using general-purpose languages for HLS, many works have examined using domain specific languages (DSL) to generate FPGA designs. These are languages designed to either simplify or enhance the development of applications for a specific domain. An early work in this area [32] mapped a network processing DSL called CLICK to an FPGA. The DSL was compiled to a HDL module that could then be synthesised with vendor tools. Network processing languages such as P4 have also had HLS integrations [33; 34]. Hipacc [35] is a DSL than can be used to create FPGA accelerators for image processing. It utilises OpenCL, and can also be used to target other platforms such as GPUs. The framework also allows for more image processing kernels to be added to the database of supported operations. Another image processing DSL, Halide, is adapted to generate FPGA accelerators

in [36]. An end-to-end flow is presented, and an evaluation the generated accelerators performed around  $4\times$  faster than CPU implementations. The framework presented in [37] allows for SQL queries to be compiled to FPGA accelerator blocks to be loaded into PR regions at runtime. SQL is a DSL used to interact with relational databases. A generic backend named FROST, capable of automatically adapting multiple different DSLs to HLS is demonstrated in [38]. It can extract an abstract representation of the functionality described by the DSL and then generate a C++ equivalent which can then be used with Xilinx HLS and SDAccel tools. The tool also exposes the same optimisations offered by Vivado HLS such as loop unrolling to the user.

One of the key barriers to the utilisation of FPGAs within networked computing systems is the considerable design effort required. This includes both datapath and system-level design. Advances to high-level development flows such as HLS simplifies accelerator designs that use standard interfaces, greatly reducing friction when deploying FPGAs as accelerators in networked systems.

#### Types of FPGA

FPGAs can vary in terms of the amount of available resources, hardened blocks, and IO. In general, more expensive devices will have a greater number of CLBs, DSP slices, and more available BRAM, as well as higher bandwidth I/O. Devices such as the Xilinx 7 or Ultrascale series are designed for high-speed networking or accelerating datacentre workloads, so have high-speed transceivers and large amounts of on-chip memory available.

FPGAs designed for smaller scale and even embedded applications also exist. The lattice ECP5 is a cheaper, mid-range device that's designed for automotive or embedded applications. The Lattice ICE40 is a very low density FPGA with few resources used for ultra-low-power embedded applications running on limited power supplies.

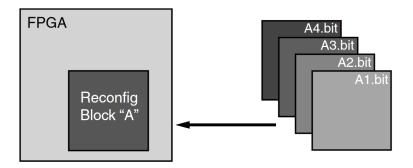

Many modern FPGAs can utilize partial-reconfiguration (PR). This feature allows for reconfiguration of selected regions of the FPGA at runtime, without having to reconfigure the whole device [39]. Hardware modules must be partitioned into partially reconfigurable regions, and then these regions mapped to the FPGA fabric through floorplanning. The vendor tool generates partial bitstreams that implement these modules with resources in the reconfigurable regions. These partial bitstreams can then be loaded at runtime to reconfigure these regions without affecting the rest of the design (Figure 2.4). PR has several benefits over full reconfiguration: resources can be time-shared, reducing the overall resources required, designs are

Figure 2.4: Partial reconfiguration allows for selected regions of the FPGA to be reconfigured using partial bitstreams [39]

more flexible and can be modified at runtime, and the same FPGA can be used to independently serve multiple applications in isolation.

#### 2.1.3 FPGA Accelerator Design

FPGAs can provide improvements to application performance through the deployment of computing logic optimised for a given task. This is in contrast to CPUs, which execute software on a general-purpose architecture. The task, algorithm or process is implemented using logical resources on the FPGA. This may be the entire algorithm, or only computationally intensive functions that act as a bottleneck when performed in software. Custom FPGA implementations achieve improvements over software through several avenues that will be discussed in this section.

#### Static Accelerators

Static accelerators are architectures that are designed to implement a single function. While these application specific architectures may be reconfigured through changing register values, there is no dynamic, device level reconfiguration. To change the core functionality of the accelerator, the entire FPGA must be reconfigured.

One of the key benefits of FPGA accelerators is the ability to implement architectures that exploit temporal parallelism. A sequence of operations can be 'pipelined', where each stage of the pipeline can operate concurrently – resulting in an improvement to throughput. Another of the key features of FPGA acceleration architectures is the exploitation of spatial parallelism. A function that may take many iterations of a loop in software can be 'unrolled', and multiple iterations of that loop can be implemented with independent FPGA logic, allowing them to execute in parallel. This property is exploited in many data mining and machine learning

algorithms, which often involve performing large quantities of the same operations on a large data set. Utilising a tiled design, of the same operations repeated spatially across the FPGA fabric, is commonplace. The SVM accelerator in [40] demonstrates an example of this approach. This design uses a set of tiles that operate on different parts of the dataset in parallel. Within each of these tiles is another tile structure. The outputs of these tiles are aggregated by additional logic that is in sequence with the tiles. This architecture outperformed a software implementation of the same algorithm by 2-3 orders of magnitude as a result. Decision tree algorithms also commonly use FPGA accelerators, and benefit from spatial parallelism. The architecture in [41] again uses a tiled design, where each comparison in the tree is implemented in parallel. An implementation of a random forest classifier takes this further in [42], implementing multiple trees operating on the same data, in parallel. The design had a greater performance per watt compared to CPUs and GPUs. The paper additionally highlights an issue with spatially parallel designs the finite resources in the fabric can limit performance gains, and the size of the algorithm that can be implemented. To extend the forest classifier beyond a given size for the available hardware, the authors had to use multiple FPGAs, while still needing only one unit for the GPU implementation.

These decision tree works use static tiles and tree structures. This means that to implement a different tree, the FPGA must be reconfigured. The work in [43] proposes a structure that uses generic, dynamically configurable tiles that use configuration data stored in on-chip RAM. The tree is converted into a rules table and written to RAM to reconfigure the accelerator without having to reconfigure the entire device. Utilisation of an array of flexible tiles is a technique often employed with convolutional neural network (CNN) accelerators. CNN inference requires many 3D convolutions, which include large sets of multiplications. The number of operations required means that unrolling the application in its entirety would be impossible due to resource limitations, therefore a set of processing elements that can be reconfigured dynamically is typically used, operating on chunks of data sequentially. The CNN accelerator in [44] uses an array of processing elements that are configured by a soft-core processor on the FPGA. Weights and data are fetched from off-chip memory. This accelerator improved processing time by  $7 \times$  compared to a CPU implementation, and had a 24× reduced power consumption. Data transfer from off-chip memory is a bottleneck for these systems, so on-chip BRAM is used for temporary buffering. This reduces the number of costly off-chip memory transfers, and allows for processing to be offset from data transfers temporally. Another CNN accelerator demonstrated in [45] attempts to optimise these on-chip buffers to take data re-use into account, greatly reducing the number of required off-chip transfers. They also develop a 3 dimensional array of processing elements as opposed to a traditional 2 dimensional one, allowing for greater re-use of processing resources.

In all, FPGAs can be used to accelerate a large variety of intensive tasks, reducing the computation latency in comparison to CPU architectures.

#### Dynamic Partial reconfiguration

Dynamically reconfigurable accelerators are desirable in a number of cases and can be achieved through partial reconfiguration (PR), a feature available on most modern FPGAs that allows for reconfiguration of only selected regions of the FPGA fabric.

Most PR accelerator designs use an architecture comprising a static shell that contains communication and control logic, and reconfigurable regions that can be loaded with different accelerator logic at runtime using PR. This allows the device to continue running and operating within a larger system while the accelerator is being modified.

One scenario where this technique is useful is when designing an accelerator for adaptive systems. These systems must alter accelerator properties at runtime to respond to external stimulus. In [46], an FPGA accelerator is deployed as part of a wireless sensor network application that can track points of interest. The application is too computationally intensive to use microcontrollers, and a static FPGA design would be unsuitable as full device reconfiguration would take too long, as well as sacrifice communication with the network. Different filters are swapped in to the reconfigurable region at runtime depending on the targets characteristics such as velocity, noise and priority. Deploying all filter datapaths on the device at once would not be possible due to limited resources. A PR-based accelerator is similarly deployed in [37], for database query processing. Acceleration of these queries is essential for large databases to ensure throughput targets are met. Implementing all possible query pipelines on the FPGA at once was not possible as it would have consumed too many resources. Reconfiguring the entire accelerator for each query would be too slow. This design therefore loads the appropriate query processing pipeline as they arrive using PR. Compared to a software solution, the FPGA accelerator achieved between  $1.4\times$  and  $6.15\times$  speedup depending on the query, with greater relative performance gains for more arithmetically complex queries.

An adaptive K-nearest neighbour (KNN) accelerator is developed in [47], where PR is used to modify the design based on user parameters. This allows for faster reconfiguration times for latency-sensitive workloads, and again allows the

accelerator to be integrated into a communication infrastructure mpre easily. The design provided a 68× speedup over a CPU implementation, and using PR instead of full-device reconfiguration resulted in around 5x faster reconfiguration. The user parameters for KNN applications are frequently changed, with users often experimenting and comparing results for different parameter values, making this faster reconfiguration time beneficial for this application. PR has been used in cognitive radio applications [48] to swap in different functions depending on the conditions such as the signal-to-noise ratio of the transmission channel, or available power. For example, a function performing the same function but with a lower power consumption can be loaded on to the FPGA if a more efficient implementation can be used. An OFDM cognitive radio is implemented in [49] to support different OFDM standards. This design uses PR only for modules that require significant changes to support a different standard, and parametrised modules for those requiring less change, and the additional resource overhead caused by the parametrisation is below a threshold. This was shown to give performance benefits compared to the traditional approach of making using PR modules for the entire pipeline, or a monolithic module containing the entire design.

PR-based accelerators are also used to time-multiplex FPGA resources, overcoming spatial constraints. The entire application may not fit within the FPGA at once, so PR is used to swap in different tasks at runtime. An example of such an accelerator can be found in [50]. The bio-informatics application examined benefits from comparing the outputs of different classifier algorithms. Using partial reconfiguration, classifiers can be loaded sequentially, saving FPGA resources, and can be loaded 8× faster than complete device reconfiguration. Similarly, this timemultiplexing technique can be seen in [51], for a KNN application. The accuracy of the algorithm can be improved by comparing the results of an ensemble of classifier configurations. Resources can be saved by loading classifiers with different parameters sequentially. This method has the benefit of making the design more scalable, and compatible with a greater number of devices with different resources available. For large FPGAs with an abundance of resources, more classifiers can be instantiated in parallel, while for smaller devices, more time-multiplexing can be utilised. Time-multiplexing using PR is exploited for a NN inference application in [52]. The results of each layer are dependent on the results of the layer before, so each layer is loaded sequentially using PR, saving resource consumption. This makes the design more compatible with smaller devices. Similarly, the video broadcasting decoder accelerator is demonstrated in [53], which again takes advantage of time-multiplexing using PR to save resources. Again, this is a highly sequential algorithm where the results of a given part are highly dependent on the previous parts.

Dynamically reconfigurable accelerator devices are beneficial for applications that must be flexible at runtime. Additionally, dynamic reconfiguration allows for time-sharing of resources and isolation of tasks, which are key enablers of device virtualisation. These properties are particularly advantageous in networked computing systems where resources are shared across multiple tasks, and process constantly changing workloads.

#### Overlays

Related to this design paradigm is the concept of overlays. This technique involves implementing an intermediate, coarse-grained architecture on an FPGA, quite often an array of generic processing elements, which can then be programmed without reconfiguring the FPGA. Designers express their requirements using a higher level of abstraction, and a custom compiler transforms and maps this design to an architecture pre-loaded onto the FPGA. This gives added flexibility in some scenarios, especially when fast reconfiguration is needed. It also has the added benefits of reducing the difficulty in designing an accelerator, and reduces the time taken to generate a design as no synthesis or place and route is needed.

An example of an overlay architecture can be found in [54]. This design resulted in a 140× speedup and an improved area-time product compared to a soft-core running on an FPGA. One issue with overlays is that they consume more area and can limit throughput and operating frequency compared to fine-grained designs optimised for a specific application. Some overlay architectures have attempted to solve this by designing overlays more closely around the underlying FPGA architecture [55; 56]. These works utilise functional units built around the DSP48E1 primitives found on modern Xilinx devices. As a result, there were large improvements to resource consumption, and improved throughput and reconfiguration time.

Overlay architectures can be targeted to specific domains in order to alleviate their performance penalty compared to hard logic implementations. Optimising the overlay for specific domains sacrifices flexibility for increased performance. The 'DLA' architecture presented in [57] is targeted at neural network inference acceleration. Using this overlay, the authors were able to achieve a throughput of 900fps for GoogleNet. One of the factors enabling this high throughput was the fast reconfiguration times offered by overlay architectures – layers' filters could be quickly loaded in ahead before they were needed. The overlay in [58] was similarly targeted specifically at NN inference, but expanded the overlay and supporting instruction set to be able to support a greater range of NN architectures, and allow for a more

fine-grained control of operator deployment - resulting in more efficient utilisation of overlay resources. Their platform showed significant improvements in performance per watt compared to both GPUs and FPGA implementations demonstrated in other NN inference works. They also demonstrated improvements over a GPU for a license plate detection applications, achieving  $3\times$  greater throughput. An overlay for accelerating DSP workloads is demonstrated in [59]. Fast reconfiguration is beneficial for workloads with variable parameters, or for devices that don't have the resources to allow for the entire application to be mapped onto the FPGA at once. It was evaluated using a 255 tap FIR filter implementation, where the accelerator implemented with the overlay resulted in  $10\times$  speedup compared to a CPU, compared to  $16\times$  speedup for a full custom design. However for larger data sizes, when reconfiguration time is taken into account, the overlay architecture begins to outperform the hard logic implementation.

While overlays can be used to implement dynamically reconfigurable accelerators, performance limitations exist as the architecture cannot be completely optimised for a given application, and the overlay architecture can limit what logic can be implemented, making it unsuitable for some applications. However they can simplify application development, enable fast reconfiguration, and abstracts away system design details.

# 2.1.4 Graphics Processing Units

Graphics processing units (GPUs) are another reprogrammable hardware accelerator platform, historically used to accelerate graphics rendering. Compared to a CPU, a GPU comprises large numbers of simpler compute units operating in parallel. Complex functions are decomposed and distributed amongst these cores, leading to reductions in processing time. This processing architecture can be used to accelerate non-graphics rendering applications. In [60] a GPU was used to accelerate quantum chemistry calculations, and resulted in a speedup of  $3.8\times$  compared to a CPU. GPUs have also been demonstrated to improve performance in neural network applications such as in [61] where a  $2-11\times$  speedup was achieved for a recurrent neural network.

# Processing model

GPUs comprise of a vast array of processing elements or cores. Each core has limited functionality compared to a CPU core, but is comparatively highly optimised to perform floating point arithmetic operations. Extraneous logic isn't implemented, which means a much higher density of processing cores can be implemented on the

same die. Instead of computation being carried out sequentially, it is decomposed and distributed to a larger number of cores in parallel, increasing throughput and reducing computation time for tasks with large data sets. Cores are also often gathered into processing groups, that all only execute the same instruction. This removes the need for the CPU fetch, decode, execute cycle.

### **Application Development**

Applications are usually written for GPUs using standard software-based programming languages such as Python or C++, with an explicitly parallel GPU framework that abstracts low-level detail away from the user. CUDA is a framework developed by Nvidia for use with its GPU architectures. As previously mentioned, OpenCL is another framework that can be used. OpenCL allows for users to express applications independently of the target architecture.

### Types of GPU

GPUs are often connected to a host processor through the PCIe bus. Datacentre class GPUs have high densities of processing elements, and are hosted on boards with large amounts of GDDR5 memory.

Embedded GPUs are lower density and lower power solutions, often integrated onto SoCs used in mobile phones or single board computers.

### Comparison to FPGAs

There are several works comparing GPU to FPGA acceleration. Both were tested with a random forest classifier application in [42]. This study determined that for this application, the FPGA achieved a higher performance per watt, however the GPU produced the best performance per dollar. While the FPGAs were more power efficient, it was also noted that the FPGAs ran into resource comsumption issues for larger forest sizes, resulting in the need for additional FPGA boards. The GPU did not, however had a degrade in performance instead. A RNN application was evaluated with a Zynq SoC and Nvidia Tegra GPU development board in [62], platforms marketed towards embedded applications. The Zynq outperformed the GPU significantly in terms of performance per watt. This observation was mirrored in a K-means clustering application [63], where the FPGA accelerator was significantly more power efficient and energy efficient than the GPU.

An extensive review of FPGA and GPU comparison studies was carried out in [20], which looked at the relative performance of GPUs, FPGAs and CPUs for a variety of applications such as matrix multiplication, FFTs, and encryption/decryption. It was found that for algebraic operations and complex simulations that involved complex mathematics with floating point numbers, GPUs generally provided greater speedup. FPGAs were better at combinational logic applications like encryption, and for fixed-point or integer signal processing. FPGAs had a lower power consumption in most surveyed applications.

As both platforms excel at different tasks, some efforts have been made to produce heterogeneous systems utilising both. This technique has been used for a medical application requiring very high frame rate image processing [64]. An FPGA acting alone did not have the resources available for very large parallel operations and large buffers required for the application, and a lone GPU ran into issues with data flow bottlenecks. A combined solution led to double the frame-rate of a lone GPU and reduced latency. A hybrid GPU-FPGA architecture was used for a SVM image classifier application in [65], where the FPGA performs feature extraction and the GPU the classification. The FPGA provided low latency processing of the image feed as it could interface with the camera easier. The GPU allowed for highly parallel computation that made up the classification phase.

Overall, FPGAs have been demonstrated to have greater power efficiency than GPUs. Another main difference is that FPGAs allow for more integration possibilities. GPUs rely on a PCIe connection to a CPU host, while FPGAs can be connected directly to the network as standalone devices.

# 2.1.5 Application Specific Integrated Circuits (ASICs)

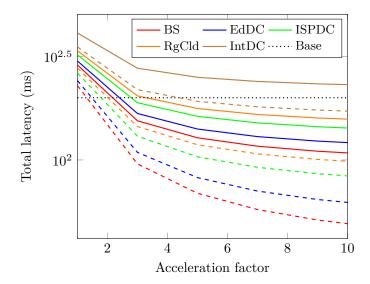

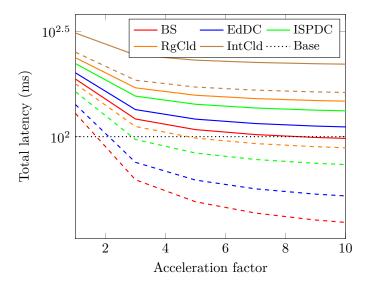

Application specific integrated circuits are devices designed and fabricated to carry out a specific group of tasks. Unlike FPGAs, the architecture is fixed at manufacture, and unlike CPUs or GPUs, they offer limited programmability. The benefit of this rigid architecture is it can be completely optimised to perform these tasks. While FPGAs require flexible interconnect which limits the achievable clock rate, ASICs do not. There is also no redundant logic or unused resources.