#### Manuscript version: Author's Accepted Manuscript

The version presented in WRAP is the author's accepted manuscript and may differ from the published version or Version of Record.

#### Persistent WRAP URL:

http://wrap.warwick.ac.uk/160524

#### How to cite:

Please refer to published version for the most recent bibliographic citation information. If a published version is known of, the repository item page linked to above, will contain details on accessing it.

#### **Copyright and reuse:**

The Warwick Research Archive Portal (WRAP) makes this work by researchers of the University of Warwick available open access under the following conditions.

Copyright © and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners. To the extent reasonable and practicable the material made available in WRAP has been checked for eligibility before being made available.

Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

### Publisher's statement:

Please refer to the repository item page, publisher's statement section, for further information.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk.

# **Current Sharing of Parallel SiC MOSFETs under Short Circuit Conditions**

Ruizhu Wu<sup>1</sup>, Simon Mendy<sup>1</sup>, Jose Ortiz Gonzalez<sup>1</sup>, Saeed Jahdi<sup>2</sup> and Olayiwola Alatise<sup>1</sup>

<sup>1</sup>UNIVERSITY OF WARWICK School of Engineering, Coventry, United Kingdom E-Mail: robert.wu.1@warwick.ac.uk, s.mendy@warwick.ac.uk, nereus.agbo@warwick.ac.uk, J.A.Ortiz-Gonzalez@warwick.ac.uk, o.alatise@warwick.ac.uk <sup>2</sup>UNIVERSITY OF BRISTOL Department of Electrical & Electronic Engineering Bristol, United Kingdom E-Mail: saeed.jahdi@bristol.ac.uk

## Acknowledgements

This work was supported in part by the UK Engineering and Physical Sciences Research Council (EPSRC) through the grant reference EP/R004366/1.

# Keywords

«Reliability», «Semiconductor Device», «Wide Bandgap Devices», «Short Circuits», «Paralleling»

## Abstract

Device-to-device parametric variations (e.g. threshold voltage  $V_{TH}$ , gate resistance  $R_G$  and junction temperature  $T_J$ ) can cause variations in the short-circuit currents conducted through parallel-connected devices. In this paper, the impact of variations in  $V_{TH}$ ,  $R_G$  and  $T_J$  on current sharing under short-circuits is investigated using measurements and electrothermal modelling. The results show that  $V_{TH}$  is the most critical parameter affecting short-circuit current sharing and directly impacts the peak short circuit current. Variations in gate resistance do not impact the short circuit current sharing unless the variation is over 400% thereby indicating catastrophic failure of the gate wirebond. Variation in the initial junction temperature is also not as critical as variations in  $V_{TH}$  since the higher temperature device takes less short circuit current. Electrothermal simulations of parallel connected SiC MOSFETs have been developed to analyze how  $V_{TH}$  mismatch impacts short circuit current sharing. These simulations allow for the investigation of the impact of  $V_{TH}$  mismatch on the electrothermal stresses of the parallel connected MOSFETs.

# Introduction

Uniform current sharing under short circuit conditions is critical for the short-circuit robustness of SiC power modules comprised of parallel connected SiC MOSFETs. Short circuits can occur in power converters either through gate misfiring or short circuits at the load. Although power converters are designed to have mitigation systems to protect the power devices from excessive electrothermal stresses due to short circuits, the devices are however required to withstand the short circuit for a given timeframe. SiC power MOSFETs have been reported to have reduced short circuit withstand times compared to similarly rated silicon devices [1, 2]. The reason for this has been cited as higher thermal resistances and reduced gate oxide reliability [3-7]. The higher thermal resistance, resulting from smaller die size in SiC, results in higher junction temperatures.

While the short circuit performance of devices is down to the individual robustness of the power device, in power modules comprised of parallel connected power devices, the SC performance will depend more on current sharing and electrothermal uniformity between the devices. Under ideal conditions, these devices should share short circuit currents equally. However, parametric differences between parallel

connected devices, (e.g. threshold voltage  $V_{TH}$ , gate resistance  $R_G$  and junction temperature  $T_J$ ) can cause variations in the short circuit currents conducted through each device [8-13]. Studies of short circuit performance in SiC power modules have shown poor current sharing to be the primary cause of reduced robustness [9, 14]. Even when devices are initially matched, phenomena like differential  $V_{TH}$  drift from different rates of charge trapping of parallel connected SiC MOSFETs can cause small differences in  $V_{TH}$  over the operational life of the device [15-18]. Furthermore, the short-circuit characteristics comprise of 2 phases namely (i) an initial rise in current (determined by the series inductance and threshold voltage) and (ii) the reduction of current due to resistive heating. The rate of current reduction during the 2<sup>nd</sup> stage of the short circuit will depend on the magnitude of the temperature coefficient of the short circuit resistance. Differences in  $V_{TH}$ , junction temperature, series parasitic inductance and gate resistance may impact these stages differently.

In this paper, the impact of variations in  $V_{TH}$ ,  $R_G$  and  $T_J$  between parallel connected SiC MOSFETs on current sharing under short circuit conditions is investigated. An electrothermal model that can accurately predict the short circuit current mismatch as a function of junction temperature difference and threshold voltage difference has been developed. By extending the model to more parallel devices, design guidelines for parallel connection of SiC MOSFETs are provided. Section II presents that experimental measurements of short circuits in parallel connected SiC MOSFETs with parametric variation. Section III presents the electrothermal model calibrated with datasheet parameters and matched with the experimental measurements. Section IV concludes the paper.

## **Experimental Set-up and Measurements**

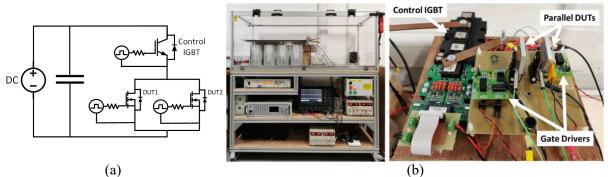

The circuit diagram of the experimental set-up for the short circuit measurements is shown in Fig. 1(a) while a picture of the test rig is shown in Fig. 1(b). The circuit comprises of a DC voltage source, a 90  $\mu$ F DC link capacitor, a control 1.7kV/1000A silicon IGBT module with datasheet reference FF1000R17IE4 and the devices-under-test (DUTs). The current through the parallel devices is measured using a Rogowski coil from Powertek. The current and voltage waveforms are captured using an oscilloscope from Teledyne LeCroy. The DUTs are 1.2kV/20A SiC MOSFETs from STMicroelectronics with datasheet reference SCT20N120 and 1.7kV/5A SiC MOSFETs from Cree with datasheet reference C2M1000170.

Fig. 1: (a) Circuit diagram of the test rig, (b) Picture of the test rig and close-up of the of the parallel DUTs circuit.

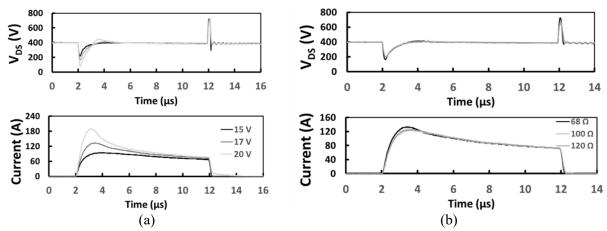

Fig. 2(a) shows the measured short circuit current and drain-source voltages measured with different gate-source voltages ( $V_{GS}$ ) for the 1.2kV/20A SiC MOSFET. As expected, the peak short circuit current and short circuit energy increases with increased  $V_{GS}$  due to the lower channel resistance [18, 19]. Fig. 2(b) shows short circuit measurements with different  $R_G$  where it can be seen that there is a marginal increase in the peak short circuit current as  $R_G$  is reduced. As the gate resistance is increased from 68  $\Omega$  to 100  $\Omega$  and 120  $\Omega$ , the short circuit energy decreases from 0.364 J to 0.363 J and 0.362 J respectively.

Fig 2: (a) Impact of gate voltage on SC transients of SiC MOSFET at  $R_G$ =100ohm, (b) Impact of gate resistance on SiC transients of SiC MOSFET at  $V_{GS}$ =17V.

To evaluate the role of  $V_{TH}$  imbalance, short circuit measurements have been performed on SiC MOSFETs with different threshold voltages. The ON-state resistance of a MOSFET is comprised of different elements including source-metal, channel, JFET resistance, drift resistance and substrate resistance, as described in [20], but the main components of the ON-state resistance of the MOSFET can be expressed by equation (1), where the first term accounts for channel resistance while the 2<sup>nd</sup> term accounts for the drift resistance. The presence of the  $V_{TH}$  parameter in the denominator results in increased short circuit current as  $V_{TH}$  is reduced.

$$R_{DSON} = \frac{L_{ch}}{W\mu C_{OX}(V_{GS} - V_{TH})} + \frac{L_{drift}}{q\mu N_D A}$$

(1)

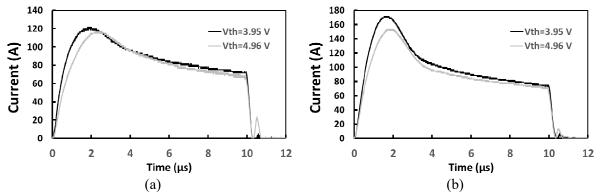

Fig. 3(a) shows the results for parallel connected SiC MOSFETs with 20% variation in threshold voltage with  $V_{GS}$  set to 15 V while Fig. 3(b) shows similar measurements with  $V_{GS}$  set to 17 V. As expected, the device with the lower threshold voltage conducts a higher short circuit current due to reduced channel resistance. The measured short circuit energy difference between the parallel MOSFETs is 5.1% at  $V_{GS}$ =15 V and 8.1% at  $V_{GS}$ =17 V.

Fig. 3: Measured Short circuit current for parallel 1.2kV/20A SiC MOSFETs with (a) 20% difference in  $V_{TH}$  and  $V_{GS}$ =15 V, (b) 20% difference in  $V_{TH}$  and  $V_{GS}$ =17 V.

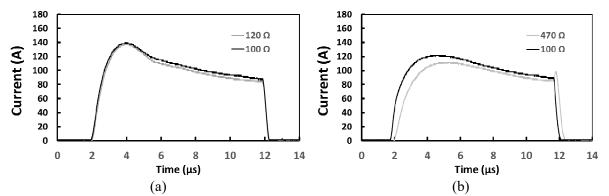

Measurements have also been performed on parallel 1.2kV SiC MOSFETs with different gate resistance. Fig. 4(a) shows measurements with a 20% difference in  $R_G$  while Fig. 4(b) shows measurements with over 300% difference in  $R_G$ . In Fig. 4(a), the difference in short circuit energy is 4.02% while in Fig. 5(b) it is 5.35% with the faster switching device dissipating more short circuit power in both cases. From the results presented here, differences in gate resistance do not contribute to significant variation in short circuit energy in the parallel pair if the differences in  $R_G$  do not exceed 50%. This is because the short circuit duration is much longer than the switching time constant of the devices, which is estimated to be 65 ns by  $\tau = R_G * C_{iss}$ .

Fig. 4: Measured Short circuit current for parallel 1.2kV/20A SiC MOSFETs with (a) 20% difference in  $R_G$ , (b) with 370% difference in  $R_G$ .

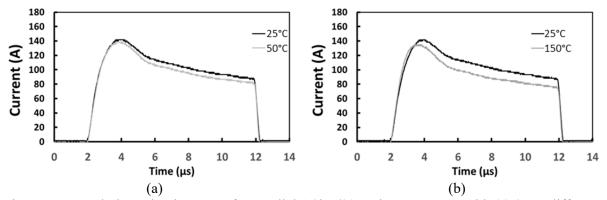

Measurements have also been performed on parallel SiC MOSFETs with different initial junction temperatures. Fig. 5(a) shows measurements on parallel devices with a junction temperature difference set at 25 °C while Fig. 5(b) shows similar measurements with the junction temperature difference set at 125 °C.

Fig. 5: Measured Short circuit current for parallel 1.2kV/20A SiC MOSFETs with (a) 25°C difference in  $T_{i}$ , (b) 125 °C difference in  $T_{i}$ .

In both cases, the device with the lower initial junction temperature conducts a higher short circuit current. The short circuit energy in the device with  $T_J$  set to 25 °C is 0.301 J while that of the device with  $T_J$  set to 50 °C and 150 °C is 0.283 J and 0.268 J respectively. The positive temperature coefficient of the short-circuit resistance means that the device with the initially higher junction temperature will conduct a smaller short circuit current.

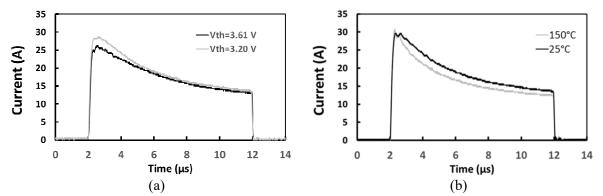

It is expected that  $V_{TH}$  difference becomes less important as the voltage rating of the devices increase, since channel resistance becomes dominated by the drift resistance i.e. the 2<sup>nd</sup> term in Equation (1) dominates the first term. Fig. 6(a) shows short-circuit measurements on parallel 1.7kV/5A SiC MOSFETs with 11.1% difference in  $V_{TH}$  while Fig. 6(b) shows similar measurements with 125°C difference in initial junction temperature. For the 1.7kV MOSFETs, an 11.1% difference in  $T_J$  results in a 9.98% difference in short circuit energy. These results presented correspond to different voltage and current rated devices from different manufacturers. Further results on more devices will give a fuller representation on how  $V_{TH}$  mismatch impacts different voltage ratings.

Fig. 6: Measured Short circuit current for parallel 1.7kV/5A SiC MOSFETs with (a) 11.1% difference in  $V_{TH}$ , (b) 125 °C difference in  $T_J$ .

### **Electrothermal Modelling of Short Circuits**

Electrothermal models could be fundamental to investigate the role of parameter mismatch in short circuits in parallel devices, allowing to easily investigate the role of mismatch in parameters like  $V_{TH}$ . In this section, an electrothermal model for parallel devices in short circuits is introduced and used to predict the short circuit performance of parallel connected SiC MOSFETs. The static and dynamic characteristics of the model are first developed so that there is good matching between the model and experimental measurements. The static characteristics of the SiC MOSFETs are modelled using equations for  $I_{DS}$  as a function of the overdrive voltage ( $V_{GS}-V_{TH}$ ) and temperature  $T_J$ . Equation 1 models that channel current in the ohmic region while equation 2 models the channel current in saturation.

$$I_{chi} = K_i \left[ (V_{GS} - V_{TH}) V_{DS} - (1 + \alpha) \frac{V_{DSi}^2}{2} \right] (1 + \lambda V_{DS}) \qquad V_{GS} \ge V_{TH} \text{ and } V_{DS} < \frac{(V_{GS} - V_{TH})}{(1 + \alpha)} \qquad (1)$$

$$I_{chi} = \frac{K_i}{2(1 + \alpha)} (V_{GSi} - V_{THi})^2 (1 + \lambda V_{DSi}) \qquad V_{GS} \ge V_{TH} \text{ and } V_{DS} \ge \frac{(V_{GS} - V_{TH})}{(1 + \alpha)} \qquad (2)$$

where  $I_{chi}$  is the channel current,  $K_i$  is the transconductance (or gain) parameter of the MOSFET (which depends on the oxide thickness, die area, effective mobility, and channel length),  $V_{GS}$  is the gate-source voltage,  $V_{TH}$  is the MOSFET threshold voltage,  $\alpha$  is a temperature dependent fitting parameter,  $\lambda$  is the channel length modulation factor.

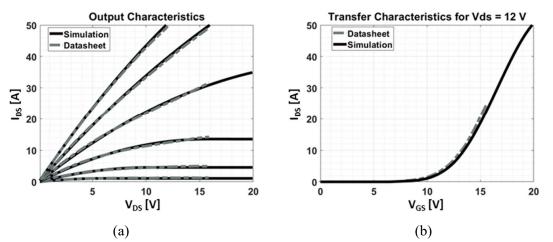

Using datasheet parameters and characteristics, the electrothermal model has been parameterized for the 1.2kV SiC MOSFET. The temperature dependency of the ON-state resistances and threshold voltage has been accounted for along with the non-linear inter-terminal capacitances. Fig. 7(a) shows the matched output characteristics between the model and the datasheet while Fig. 7(b) shows matched gate transfer characteristics.

Fig. 7: Simulated characteristics for the 1.2kV SiC MOSFET compared with datasheet (a) output characteristics, (b) transfer characteristics.

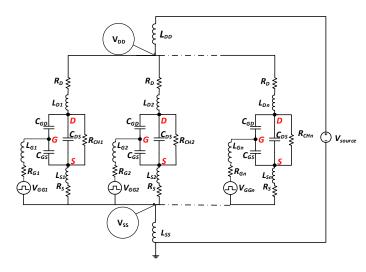

The dynamic section of the model is based on the derivation of current and voltage equations using KCL and KVL on the circuit shown in Fig. 8. Table 1 shows the parameters used in the model and the datasheet derived values.

| Parameter                           | Value  |

|-------------------------------------|--------|

| $C_{GD}$                            | 14 pF  |

| $C_{GS}$                            | 51 pF  |

| $C_{DS}$                            | 636 pF |

| $L_{D1}, L_{D2}$                    | 15 nH  |

| $L_{G1}, L_{G2}$                    | 0.1 nH |

| $L_{SI}, L_{S2}$                    | 15 nH  |

| $L_{DD}$                            | 400 nH |

| $L_{SS}$                            | 400 nH |

| $R_{G1}, R_{G2}$                    | 100 Ω  |

| V <sub>GG1</sub> , V <sub>GG2</sub> | 20 V   |

| $R_{D1}, R_{D2}$                    | 1 μΩ   |

| $R_{S1}, R_{S2}$                    | 1 μΩ   |

|                                     |        |

Fig. 8. Equivalent circuit of parallel connected SiC MOSFETs in short circuit set-up.

Table 1: Parameters used for dynamic modelling of short circuits.  $C_{GD}$ ,  $C_{GS}$ , and  $C_{DS}$  vary with  $V_{DS}$ .

Equations 3 to 8 below are generated from applying KCL and KVL to the equivalent circuits shown in Fig. 8.

$$(L_{Di} + L_{Si})\frac{di_{Si}}{dt} - L_{Di}\frac{di_{Gi}}{dt} + (L_{DDSS})\sum_{i=1}^{n}\frac{di_{Si}}{dt} - (L_{DDSS})\frac{di_{Gi}}{dt} + V_{DSi} + i_{Si}(R_{S} + R_{D}) - i_{Gi}R_{D} = V_{source}$$

(3)

$$R_{Gi}i_{Gi} + R_Si_{Si} + L_{Gi}\frac{di_{Gi}}{dt} + L_{Si}\frac{di_{Si}}{dt} + V_{GSi} = V_{GGi}$$

$$\tag{4}$$

$$C_{GS}\frac{dV_{GSi}}{dt} - C_{GD}\frac{dV_{DGi}}{dt} - i_{Gi} = 0$$

(5)

$$(\mathcal{C}_{GS} + \mathcal{C}_{DS})\frac{dV_{GSi}}{dt} + \mathcal{C}_{DS}\frac{dV_{DGi}}{dt} - i_{Si} = -I_{chi} \tag{6}$$

$$I_{Si} - I_{Gi} = I_{Di} \tag{7}$$

$$V_{DGi} + V_{GSi} = V_{DSi} \tag{8}$$

i is the phase number, from left to right according to Fig. 8, and n is the total number of devices connected in parallel. The short circuit model is fully electrothermal since the junction temperature is calculated using a thermal network. The thermal network is implemented as a 4-layer Foster network with the thermal resistances and capacitances derived from the transient thermal impedance characteristic given on the datasheet.

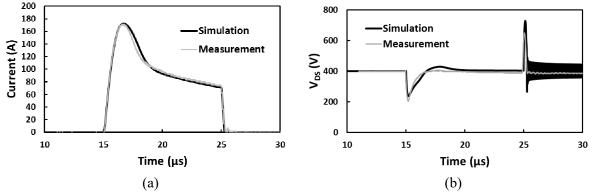

To check the accuracy of the models, the results of the simulations have been plotted together with the measurements. Fig. 9(a) shows the simulated and measured short circuit current while Fig. 9(b) shows the measured and simulated drain-source voltage across the device. In Fig. 9(b), the negative spike during the start of the short circuit is due to the voltage drop across the drain inductance during current rise while the positive spike at the end of the short circuit is due to the voltage across the drain inductance during the drain inductance during the short circuit is due to the voltage across the drain inductance during current rise while the positive spike at the end of the short circuit is due to the voltage across the drain inductance during the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit is due to the voltage across the drain inductance during the short circuit the short circuit is due to the voltage across the drain inductance during the short circuit the short c

during current fall. The simulated  $V_{DS}$  shows more oscillation than what is measured is attributed to the more temperature dependent resistive damping in the measurements.

Fig. 9: Comparison between simulated and measured short circuit transients in the 1.2kV SiC MOSFET (a) short circuit currents, (b) drain-source voltage.

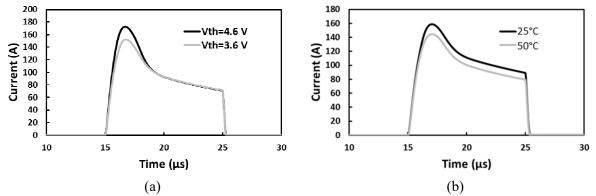

Short circuit characteristics have also been modelled and matched with the experimental measurements presented in Fig. 10 for parallel connected MOSFETs with different threshold voltages and initial junction temperatures. Fig. 10(a) shows the short circuit simulations and experimental measurements for parallel devices with different  $V_{TH}$  while Fig. 10(b) shows a similar plot for parallel devices with different initial junction temperatures. Comparing these modeled short circuit characteristics to the measurements in Fig. 3 and Fig. 5 for the 1.2kV devices, it can be seen that the short circuit behavior of the MOSFET is captured. When the difference between the parallel devices is in  $V_{TH}$ , there is convergence in the short circuit current whereas when it is in junction temperature, there is no convergence. This is apparent both in the measurements and simulations.

Fig. 10: Simulated Short circuit current for parallel SiC MOSFETs with (a) 20% variation in  $V_{TH}$ , (b) 25°C difference in  $T_{CASE}$

### Conclusion

In this paper, the impact of variation in threshold voltage ( $V_{TH}$ ), gate resistance ( $R_G$ ) and junction temperature ( $T_J$ ) between parallel SiC MOSFETs on short circuit robustness has been studied. It is shown that the most critical parameter is  $V_{TH}$ , with less impact from by  $T_J$  and  $R_G$ .  $V_{TH}$  mismatch plays a critical role in the first part of the short circuit where the peak short circuit current and its ramp rate is important. In the 2<sup>nd</sup> part of the short circuit characteristic, initial junction temperature is more important. Electro-thermal modelling is required for further investigation of how these parameters affect short circuit performance of parallel devices with regards to temperature distribution between the devices. The electrothermal model introduced allows for variation of  $V_{TH}$  between parallel devices and is capable of extension to any number of parallel devices.

### References

- G. Romano *et al.*, "A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 978-987, 2016, doi: 10.1109/JESTPE.2016.2563220.

- [2] G. Romano *et al.*, "Short-circuit failure mechanism of SiC power MOSFETs," in 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 10-14 May 2015 2015, pp. 345-348, doi: 10.1109/ISPSD.2015.7123460.

- [3] A. Agarwal, A. Kanale, K. Han, B. J. Baliga, and S. Bhattacharya, "Impact of Gate Oxide Thickness on Switching and Short Circuit Performance of 1200 V 4H-SiC Inversion-channel MOSFETs," in 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 29-31 Oct. 2019 2019, pp. 59-62, doi: 10.1109/WiPDA46397.2019.8998839.

- [4] X. Chen et al., "Investigation on Short-Circuit Characterization and Optimization of 3.3-kV SiC MOSFETs," *IEEE Transactions on Electron Devices*, vol. 68, no. 1, pp. 184-191, 2021, doi: 10.1109/TED.2020.3037262.

- [5] M. Okawa, R. Aiba, T. Kanamori, H. Yano, N. Iwamuro, and S. Harada, "Experimental and Numerical Investigations of Short-Circuit Failure Mechanisms for State-of-the-Art 1.2kV SiC Trench MOSFETs," in 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), 19-23 May 2019 2019, pp. 167-170, doi: 10.1109/ISPSD.2019.8757617.

- [6] P. D. Reigosa, F. Iannuzzo, and L. Ceccarelli, "Effect of short-circuit stress on the degradation of the SiO2 dielectric in SiC power MOSFETs," *Microelectronics Reliability*, vol. 88-90, pp. 577-583, 2018/09/01/2018, doi: <u>https://doi.org/10.1016/j.microrel.2018.07.144</u>.

- [7] J. Liu, G. Zhang, B. Wang, W. Li, and J. Wang, "Gate Failure Physics of SiC MOSFETs Under Short-Circuit Stress," *IEEE Electron Device Letters*, vol. 41, no. 1, pp. 103-106, 2020, doi: 10.1109/LED.2019.2953235.

- [8] F. Boige, A. Fayyaz, A. Castellazzi, F. Richardeau, and S. Vinnac, "Short-circuit robustness of parallel SiC MOSFETs and fail-safe mode strategy," in 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), 3-5 Sept. 2019 2019, pp. P.1-P.10, doi: 10.23919/EPE.2019.8914891.

- [9] A. Kadavelugu, E. Aeloiza, and C. Belcastro, "Short-circuit performance of multi-chip SiC MOSFET modules," in *2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA)*, 30 Oct.-1 Nov. 2017 2017, pp. 285-290, doi: 10.1109/WiPDA.2017.8170561.

- [10] D. H. Lu, H. Takubo, S. Takano, and Y. Suzuki, "Paralleling six 320A 1200V All-SiC Half-bridge Modules for a Large Capacity Power Stack," in 2018 International Power Electronics Conference (IPEC-Niigata 2018 - ECCE Asia), 20-24 May 2018 2018, pp. 3390-3395, doi: 10.23919/IPEC.2018.8507687.

- [11] L. Ceccarelli, P. D. Reigosa, A. S. Bahman, F. Iannuzzo, and F. Blaabjerg, "Compact electro-thermal modeling of a SiC MOSFET power module under short-circuit conditions," in *IECON 2017 - 43rd Annual Conference of the IEEE Industrial Electronics Society*, 29 Oct.-1 Nov. 2017 2017, pp. 4879-4884, doi: 10.1109/IECON.2017.8216842.

- [12] J. Ke, Z. Zhao, Q. Zou, J. Peng, Z. Chen, and X. Cui, "Device Screening Strategy for Balancing Short-Circuit Behavior of Paralleling Silicon Carbide MOSFETs," *IEEE Transactions on Device and Materials Reliability*, vol. 19, no. 4, pp. 757-765, 2019, doi: 10.1109/TDMR.2019.2949449.

- [13] Q. Zou, J. Ke, J. Peng, and Z. Zhao, "Effect of Parasitic Inductance Mismatch on Short-Circuit Characterization of Paralleled SiC MOSFETs," in 2019 4th IEEE Workshop on the Electronic Grid (eGRID), 11-14 Nov. 2019 2019, pp. 1-8, doi: 10.1109/eGRID48402.2019.9092772.

- [14] P. D. Reigosa, F. Iannuzzo, H. Luo, and F. Blaabjerg, "A Short-Circuit Safe Operation Area Identification Criterion for SiC MOSFET Power Modules," *IEEE Transactions on Industry Applications*, vol. 53, no. 3, pp. 2880-2887, 2017, doi: 10.1109/TIA.2016.2628895.

- [15] T. Aichinger, G. Rescher, and G. Pobegen, "Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs," *Microelectronics Reliability*, vol. 80, pp. 68-78, 2018/01/01/ 2018, doi: <u>https://doi.org/10.1016/j.microrel.2017.11.020</u>.

- [16] J. A. O. González and O. Alatise, "A Novel Non-Intrusive Technique for BTI Characterization in SiC mosfets," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5737-5747, 2019, doi: 10.1109/TPEL.2018.2870067.

- [17] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin, and H. Reisinger, "Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability," *IEEE Transactions on Electron Devices*, vol. 66, no. 11, pp. 4604-4616, 2019, doi: 10.1109/TED.2019.2938262.

- [18] J. O. Gonzalez and O. Alatise, "Bias Temperature Instability and Junction Temperature Measurement Using Electrical Parameters in SiC Power MOSFETs," *IEEE Transactions on Industry Applications*, vol. 57, no. 2, pp. 1664-1676, 2021, doi: 10.1109/TIA.2020.3045120.

- [19] M. Cui, J. Li, Y. Du, and Z. Zhao, "Behavior of SiC MOSFET under Short-Circuit during the On-State," *IOP Conference Series: Materials Science and Engineering*, vol. 439, p. 022026, 2018/11/05 2018, doi: 10.1088/1757-899x/439/2/022026.

- [20] B. J. Baliga, Springer, Ed. Fundamentals of Power Semiconductor Devices. Springer, 2008.