#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### Permanent WRAP URL:

http://wrap.warwick.ac.uk/161795

#### Copyright and reuse:

This thesis is made available online and is protected by original copyright. Please scroll down to view the document itself. Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Uneven Degradation and Condition Monitoring of Multi-Chip Power Modules for Wind Turbines

by

## **Borong Hu**

A thesis submitted for the degree of

Doctor of Philosophy

University of Warwick, School of Engineering

February 2021

## Contents

| List of Figures      | V     |

|----------------------|-------|

| List of Tables       | xi    |

| Acknowledgements     | xii   |

| Declaration          | xiii  |

| List of Publications | xiv   |

| Abstract             | xvii  |

| Nomenclature         | xviii |

| 1 | INT | TRODUCTION1                         |                                    |  |

|---|-----|-------------------------------------|------------------------------------|--|

|   | 1.1 | BACKO                               | GROUND                             |  |

|   | 1.2 | PACKA                               | GING OF HIGH-POWER SEMICONDUCTORS  |  |

|   | 1.3 | Ageing Mechanisms and Failure Modes |                                    |  |

|   |     | 1.3.1                               | Thermomechanical stress            |  |

|   |     | 1.3.2                               | Electrical stress                  |  |

|   |     | 1.3.3                               | Ageing characteristic parameters12 |  |

|   | 1.4 | Condi                               | tion Monitoring13                  |  |

|   |     | 1.4.1                               | Device terminal features           |  |

|   |     | 1.4.2                               | Built-in sensors                   |  |

|   |     | 1.4.3                               | Algorithm-based methods            |  |

|   | 1.5 | Μοτιν                               | ATIONS AND OBJECTIVES              |  |

|   | 1.6 | CONTR                               | IBUTIONS                           |  |

|   | 1.7 | THESIS                              | OUTLINE                            |  |

#### 2 INITIAL AGEING DEVELOPMENT OF POWER MODULES UNDER

| RE  | CALISTIC STRESS CONDITIONS | 26 |

|-----|----------------------------|----|

| 2.1 | INTRODUCTION               | 26 |

| 2.2 | Experiment Techniques      | 28 |

|     | 2.2.1 CT analysis          | 28 |

|   |                         | 2.2.2                                                                                                         | Power cycling test                                                                                                                                                                                                           | 29                                                                                      |

|---|-------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|   | 2.3                     | CT SCA                                                                                                        | ANNING RESULTS                                                                                                                                                                                                               |                                                                                         |

|   |                         | 2.3.1                                                                                                         | Statistical analysis of voids                                                                                                                                                                                                |                                                                                         |

|   |                         | 2.3.2                                                                                                         | Void growth and crack initialisation                                                                                                                                                                                         |                                                                                         |

|   | 2.4                     | FEA M                                                                                                         | IODEL                                                                                                                                                                                                                        |                                                                                         |

|   | 2.5                     | Void D                                                                                                        | DEFECTS                                                                                                                                                                                                                      | 41                                                                                      |

|   |                         | 2.5.1                                                                                                         | Internal void                                                                                                                                                                                                                | 42                                                                                      |

|   |                         | 2.5.2                                                                                                         | Void at solder-to-chip boundary                                                                                                                                                                                              | 43                                                                                      |

|   | 2.6                     | CRACK                                                                                                         | DEFECTS                                                                                                                                                                                                                      | 45                                                                                      |

|   |                         | 2.6.1                                                                                                         | Crack initialisation                                                                                                                                                                                                         | 45                                                                                      |

|   |                         | 2.6.2                                                                                                         | Crack growth                                                                                                                                                                                                                 | 46                                                                                      |

|   | 2.7                     | Experi                                                                                                        | IMENTAL VALIDATION                                                                                                                                                                                                           | 48                                                                                      |

|   | 2.8                     | Long-                                                                                                         | TERM LIFETIME ESTIMATION                                                                                                                                                                                                     | 51                                                                                      |

|   | 2.9                     | SUMMA                                                                                                         | 4RY                                                                                                                                                                                                                          | 53                                                                                      |

|   |                         |                                                                                                               |                                                                                                                                                                                                                              |                                                                                         |

|   |                         |                                                                                                               |                                                                                                                                                                                                                              |                                                                                         |

| 3 | LIF                     | ETIME                                                                                                         | AND UNEVEN DEGRADATION OF MULTI-CHIP POV                                                                                                                                                                                     | WER                                                                                     |

| 3 |                         |                                                                                                               | AND UNEVEN DEGRADATION OF MULTI-CHIP POV<br>S IN WIND TURBINES                                                                                                                                                               |                                                                                         |

| 3 |                         | DDULES                                                                                                        |                                                                                                                                                                                                                              | 54                                                                                      |

| 3 | MO                      | DDULES<br>Introe                                                                                              | S IN WIND TURBINES                                                                                                                                                                                                           | <b>54</b><br>54                                                                         |

| 3 | <b>M</b> (<br>3.1       | DDULES<br>Introe                                                                                              | S IN WIND TURBINES                                                                                                                                                                                                           | <b>54</b><br>54                                                                         |

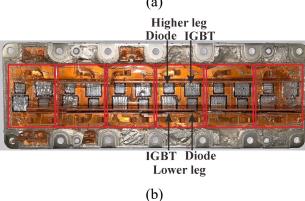

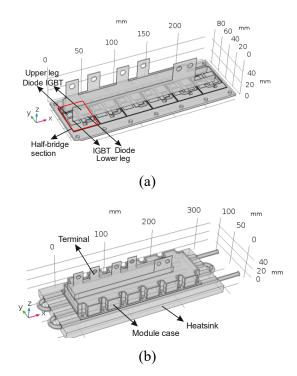

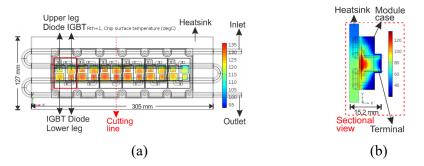

| 3 | <b>M</b> (<br>3.1       | DDULES<br>Introe<br>Multi•                                                                                    | S IN WIND TURBINES<br>DUCTION<br>-CHIP POWER MODULE                                                                                                                                                                          | <b>54</b><br>54<br>55<br>56                                                             |

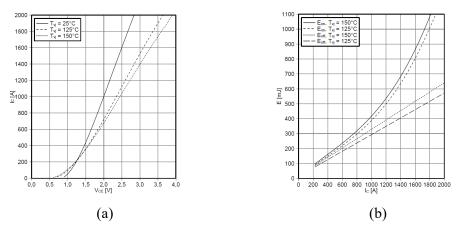

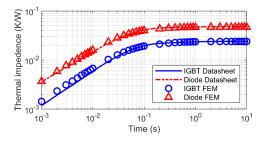

| 3 | <b>M</b> (<br>3.1       | DDULES<br>Introe<br>Multi-<br>3.2.1                                                                           | S IN WIND TURBINES<br>DUCTION<br>-CHIP POWER MODULE<br>Device electrical characteristics                                                                                                                                     | <b>54</b><br>54<br>55<br>56<br>58                                                       |

| 3 | <b>M</b> (<br>3.1       | DDULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3                                                         | S IN WIND TURBINES<br>DUCTION<br>-CHIP POWER MODULE<br>Device electrical characteristics<br>Finite element analysis                                                                                                          | <b>54</b><br>55<br>56<br>58<br>60                                                       |

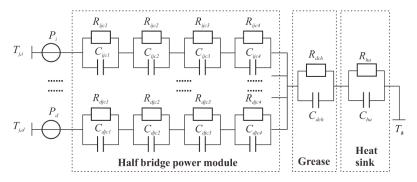

| 3 | <b>M(</b><br>3.1<br>3.2 | DDULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3                                                         | S IN WIND TURBINES<br>DUCTION<br>-CHIP POWER MODULE<br>Device electrical characteristics<br>Finite element analysis<br>Thermal network of power modules                                                                      | <b>54</b><br>55<br>56<br>56<br>58<br>60<br>61                                           |

| 3 | <b>M(</b><br>3.1<br>3.2 | DDULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3<br>ELECTH                                               | S IN WIND TURBINES<br>DUCTION<br>-CHIP POWER MODULE<br>Device electrical characteristics<br>Finite element analysis<br>Thermal network of power modules<br>ROTHERMAL MODELLING                                               | <b>54</b><br>55<br>56<br>58<br>60<br>61                                                 |

| 3 | <b>M(</b><br>3.1<br>3.2 | DULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3<br>ELECTH<br>3.3.1<br>3.3.2                              | S IN WIND TURBINES<br>DUCTION<br>-CHIP POWER MODULE<br>Device electrical characteristics<br>Finite element analysis<br>Thermal network of power modules<br>ROTHERMAL MODELLING<br>Wind turbines                              | <b>54</b><br>55<br>56<br>58<br>60<br>61<br>61<br>62                                     |

| 3 | M(<br>3.1<br>3.2<br>3.3 | DULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3<br>ELECTH<br>3.3.1<br>3.3.2                              | S IN WIND TURBINES<br>OUCTION<br>-CHIP POWER MODULE<br>Device electrical characteristics<br>Finite element analysis<br>Thermal network of power modules<br>ROTHERMAL MODELLING<br>Wind turbines<br>Electro-thermal modelling | <b>54</b><br>55<br>56<br>58<br>60<br>61<br>61<br>62<br>63                               |

| 3 | M(<br>3.1<br>3.2<br>3.3 | DULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3<br>ELECTH<br>3.3.1<br>3.3.2<br>LIFETIN                   | S IN WIND TURBINES                                                                                                                                                                                                           | <b>54</b><br>55<br>56<br>56<br>58<br>60<br>61<br>61<br>61<br>62<br>63<br>63             |

| 3 | M(<br>3.1<br>3.2<br>3.3 | DULES<br>INTROE<br>MULTI-<br>3.2.1<br>3.2.2<br>3.2.3<br>ELECTH<br>3.3.1<br>3.3.2<br>LIFETIN<br>3.4.1<br>3.4.2 | S IN WIND TURBINES                                                                                                                                                                                                           | <b>54</b><br>55<br>56<br>56<br>58<br>60<br>61<br>61<br>61<br>61<br>61<br>63<br>63<br>65 |

| 4 | CO                                                                   | NDITIC | ON MONITORING OF MULTI-CHIP MODULES WI          | TH UNEVEN |

|---|----------------------------------------------------------------------|--------|-------------------------------------------------|-----------|

|   | DE                                                                   | GRAD   | ATION                                           | 72        |

|   | 4.1                                                                  | Intro  | DUCTION                                         | 72        |

|   | 4.2                                                                  | CHAR   | ACTERIZATION OF UNEVEN DEGRADATION              | 73        |

|   |                                                                      | 4.2.1  | Electrical characterisation                     | 73        |

|   |                                                                      | 4.2.2  | Thermal characterisation                        | 76        |

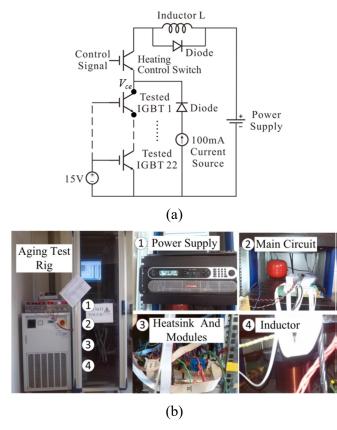

|   | 4.3                                                                  | Exper  | RIMENTAL TEST RIG                               |           |

|   | 4.4                                                                  | Two-S  | STAGE NEURAL NETWORK                            |           |

|   |                                                                      | 4.4.1  | First stage NNs                                 |           |

|   |                                                                      | 4.4.2  | Generalization and extrapolation                |           |

|   |                                                                      | 4.4.3  | Second stage NN                                 |           |

|   | 4.5                                                                  | Exper  | RIMENTAL RESULTS                                |           |

|   |                                                                      | 4.5.1  | Power loss estimation of first stage NNs        |           |

|   |                                                                      | 4.5.2  | Degradation level monitoring by second stage NN | 90        |

|   |                                                                      | 4.5.3  | Untrained conditions                            |           |

|   | 4.6                                                                  | SUMM   | IARY                                            | 95        |

| 5 | ADVANCED MEASURES FOR CONDITION MONITORING OF MULTI-<br>CHIP MODULES |        |                                                 |           |

|   | 5.1                                                                  | Intro  | DUCTION                                         |           |

|   | 5.2                                                                  | Data   | LABELLING FOR UNEVEN DEGRADATION LEVEL          | 97        |

|   |                                                                      | 5.2.1  | Data labelling platform                         | 97        |

|   |                                                                      | 5.2.2  | Electrical equivalence                          |           |

|   |                                                                      | 5.2.3  | Thermal equivalence                             |           |

|   | 5.3                                                                  | FBG F  | FOR TEMPERATURE MEASUREMENT                     |           |

|   |                                                                      | 5.3.1  | FBG sensor integration and calibration          |           |

|   |                                                                      | 5.3.2  | Temperature measurement results                 |           |

|   | 5.4                                                                  | DEEP   | Learning for Condition Monitoring               | 115       |

|   |                                                                      | 5.4.1  | Improved condition monitoring algorithm         | 116       |

|   |                                                                      | 5.4.2  | NN structure                                    | 117       |

|   |                                                                      | 5.4.3  | Condition monitoring results                    |           |

|   | 5.5                                                                  | SUMM   | IARY                                            | 121       |

| 6  | 6 CONDITION MONITORING OF WIND TURBINE CONVERTERS BASED |                          |                              |  |

|----|---------------------------------------------------------|--------------------------|------------------------------|--|

|    | ON SCADA DATA                                           |                          |                              |  |

|    | 6.1                                                     | Intro                    | DUCTION                      |  |

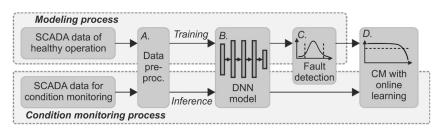

|    | 6.2 SCADA DATA BASED CONDITION MONITORING               |                          |                              |  |

|    |                                                         | 6.2.1                    | Data pre-processing          |  |

|    |                                                         | 6.2.2                    | Network model                |  |

|    |                                                         | 6.2.3                    | Fault detection              |  |

|    |                                                         | 6.2.4                    | CM with online learning      |  |

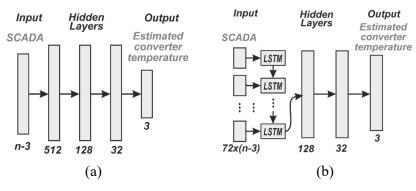

|    | 6.3                                                     | 6.3 Cost Function Design |                              |  |

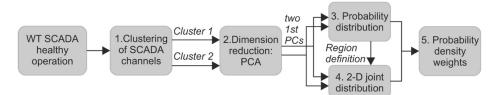

|    |                                                         | 6.3.1                    | Clustering of SCADA channels |  |

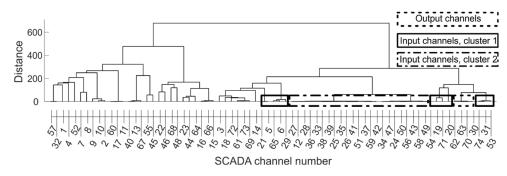

|    |                                                         | 6.3.2                    | Principal component analysis |  |

|    |                                                         | 6.3.3                    | Probability distribution     |  |

|    |                                                         | 6.3.4                    | 2-D joint distribution       |  |

|    |                                                         | 6.3.5                    | Probability density weights  |  |

|    | 6.4 CONDITION MONITORING RESULTS AND ANALYSIS           |                          |                              |  |

|    |                                                         | 6.4.1                    | SCADA data pre-processing    |  |

|    |                                                         | 6.4.2                    | Online learning results      |  |

|    |                                                         | 6.4.3                    | Fault detection              |  |

|    | 6.5                                                     | SUMM                     | IARY                         |  |

|    |                                                         |                          |                              |  |

| 7  | COI                                                     | NCLUS                    | SIONS AND FUTURE WORK        |  |

|    | 7.1                                                     | Conci                    | LUSIONS                      |  |

|    | 7.2                                                     | Futuf                    | re Work                      |  |

|    |                                                         |                          |                              |  |

| BI | BLIO                                                    | GRAPI                    | HY                           |  |

## **List of Figures**

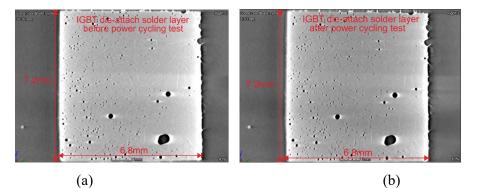

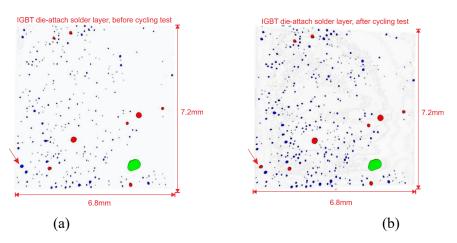

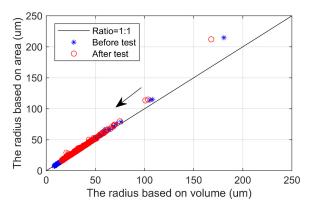

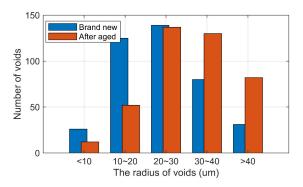

| Figure 2.10: Distribution of void radii                                                              |

|------------------------------------------------------------------------------------------------------|

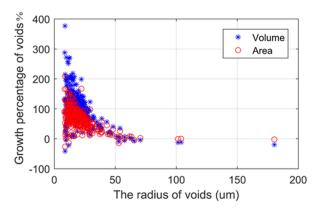

| Figure 2.11: Void growth after 35,000 low $\Delta T_j$ cycles                                        |

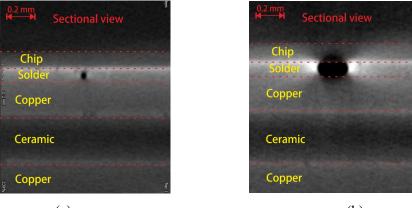

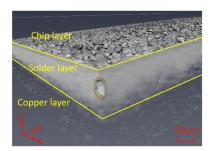

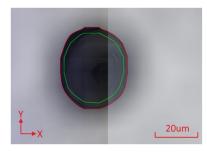

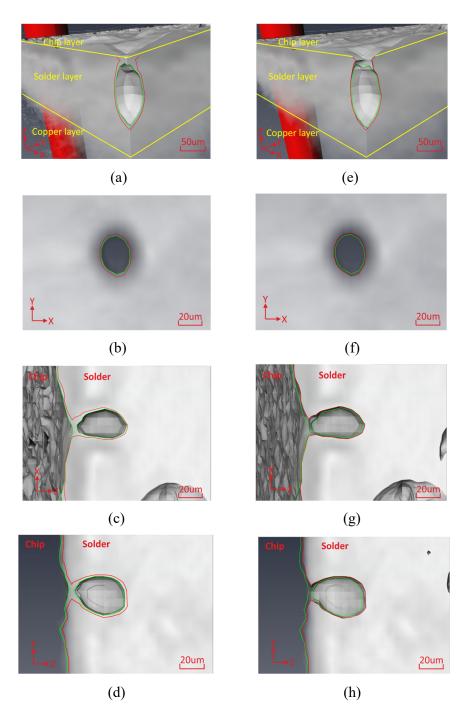

| Figure 2.12: Development of an internal void, $(a)/(b)/(c)/(d)$ before and $(e)/(f)/(g)/(h)$ after   |

| power cycling                                                                                        |

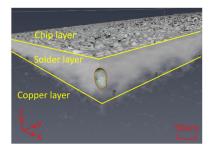

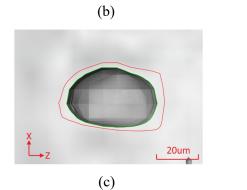

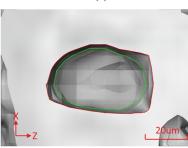

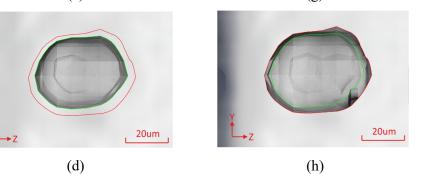

| Figure 2.13: Development of a void close to chip-solder boundary, (a)/(b)/(c)/(d) before and         |

| (e)/(f)/(g)/(h) after power cycling                                                                  |

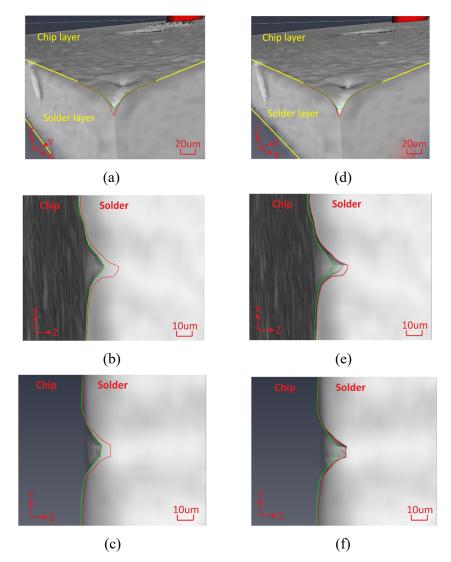

| Figure 2.14: The development of a small crack on the chip-solder boundary, (a)/(b)/(c)               |

| before and (d)/(e)/(f) after power cycling                                                           |

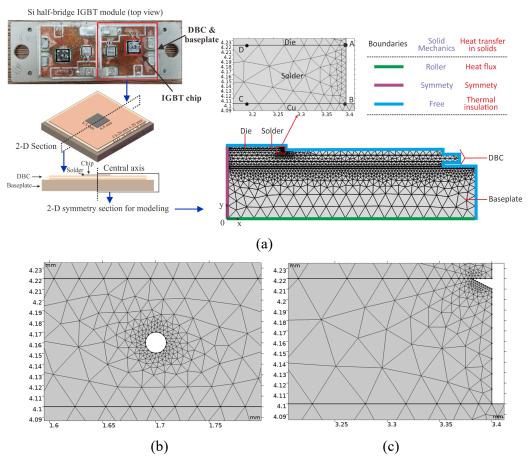

| Figure 2.15: (a) 2D symmetrical model and the boundary conditions and (b) mesh around a              |

| void of 10 $\mu m$ radius and a crack of 2 $\mu m$ length40                                          |

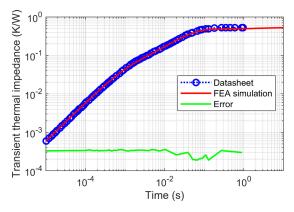

| Figure 2.16: Transient thermal impedance from simulation model and product datasheet.41              |

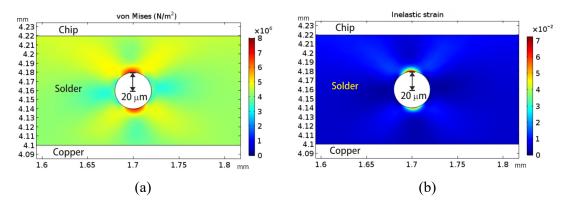

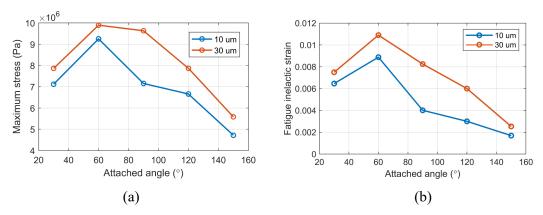

| Figure 2.17: (a) stress and (b) accumulated inelastic strain distribution around a 20 $\mu m$ radius |

| void42                                                                                               |

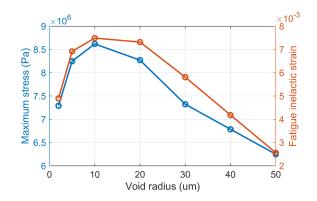

| Figure 2.18: Stress and fatigue inelastic strain on the top edge of voids                            |

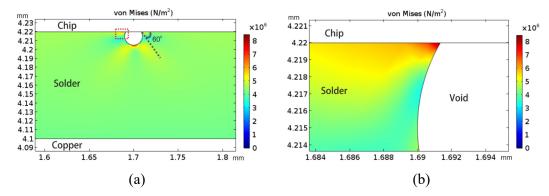

| Figure 2.19: Stress distribution (a) overall and (b) at the corner when a void of $10\mu m$ radius   |

| touches the chip-solder boundary44                                                                   |

| Figure 2.20: Accumulated inelastic strain distribution (a) overall and (b) at the corner when        |

| a void of $10 \mu m$ radius touches the solder-chip boundary44                                       |

| Figure 2.21: (a) maximum stress and (b) fatigue inelastic strain for voids with different            |

| attached angles44                                                                                    |

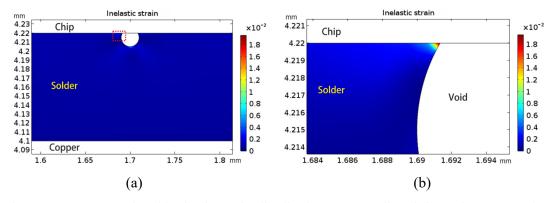

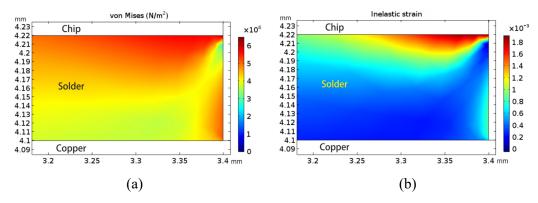

| Figure 2.22: (a) stress distribution and (b) accumulated inelastic strain distribution in the        |

| solder layer without defects45                                                                       |

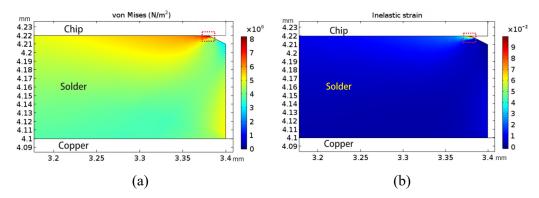

| Figure 2.23: (a) stress distribution and (b) accumulated inelastic strain distribution around a      |

| crack                                                                                                |

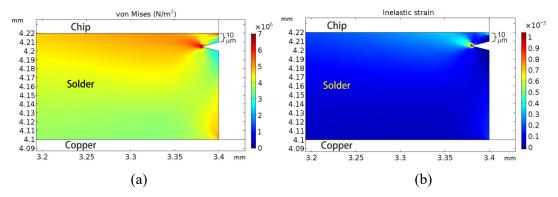

| Figure 2.24: (a) stress distribution and (b) accumulated inelastic strain round an initial crack     |

| 10 μm away from the boundary46                                                                       |

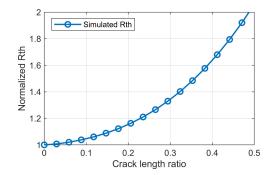

| Figure 2.25: The relationship between thermal resistance and crack length47                          |

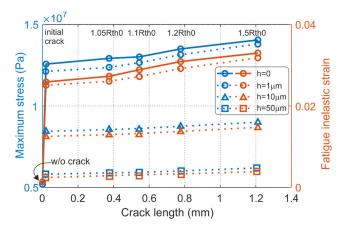

| Figure 2.26: Stress and fatigue inelastic strain on the tip of crack with different lengths48        |

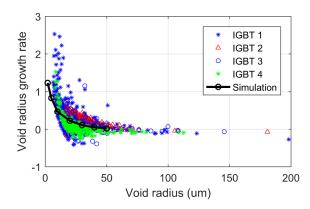

| Figure 2.27: The growth rate of voids with different initial sizes48                                 |

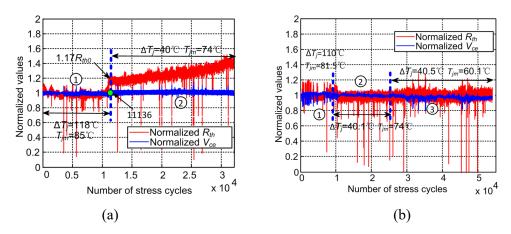

| Figure 2.28: Multi-stage power cycling test                                                          |

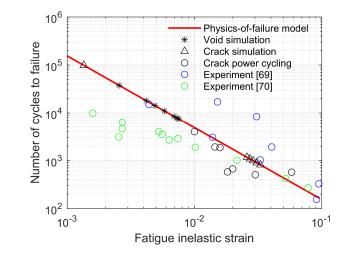

| Figure 2.29: Solder material lifetime results from physics-of-failure modelling and                  |

| experiments                                                                                          |

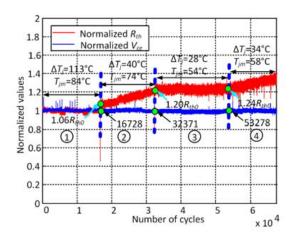

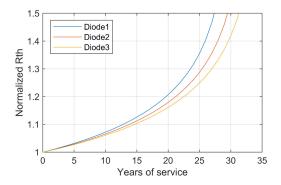

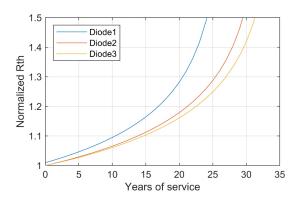

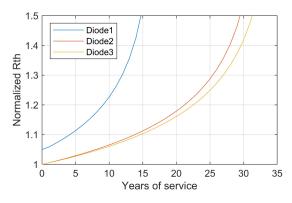

| Figure 3.18: The uneven degradation development of paralleled diodes with 5% $R_{th}$ incr | ease |

|--------------------------------------------------------------------------------------------|------|

| of diode 1                                                                                 | 70   |

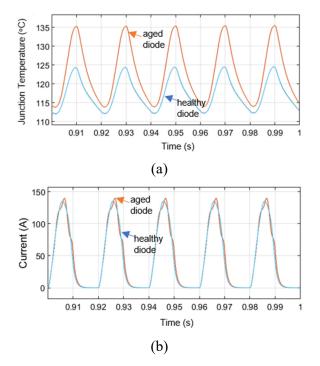

| Figure 4.1: Simulation results (a) junction temperature, and (b) current of the aged and      |

|-----------------------------------------------------------------------------------------------|

| parallel diodes74                                                                             |

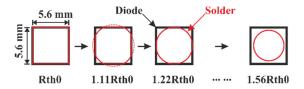

| Figure 4.2: The ageing process of the die-attach solder layer74                               |

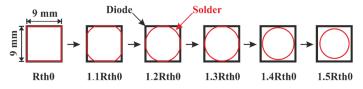

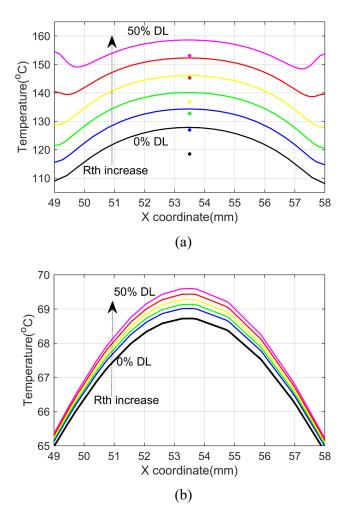

| Figure 4.3: (a) Electrical and (b) thermal features of parallel diodes under different DLs75  |

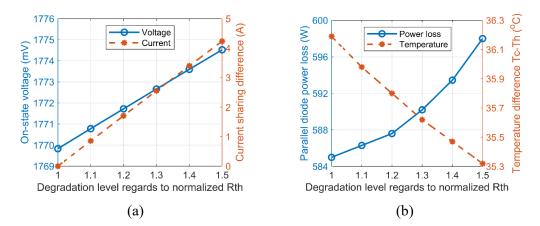

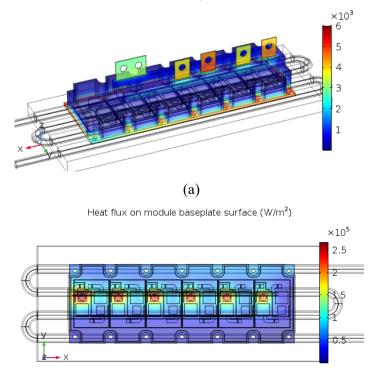

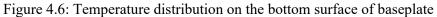

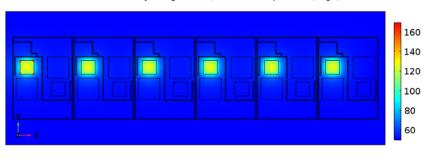

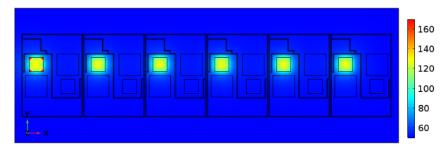

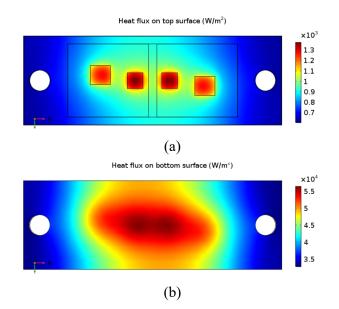

| Figure 4.4: Heat flux distribution on (a) external surfaces and (b) baseplate bottom surface  |

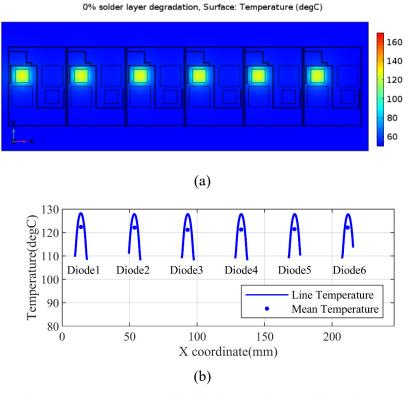

| of a healthy module                                                                           |

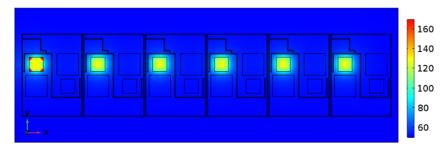

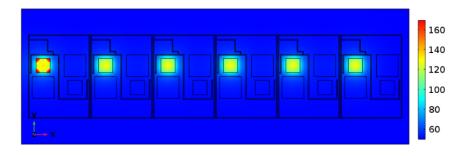

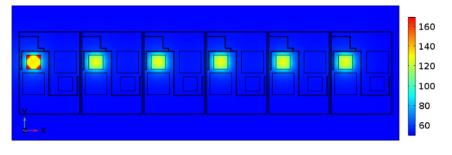

| Figure 4.5: Temperature distribution on the top chip surfaces77                               |

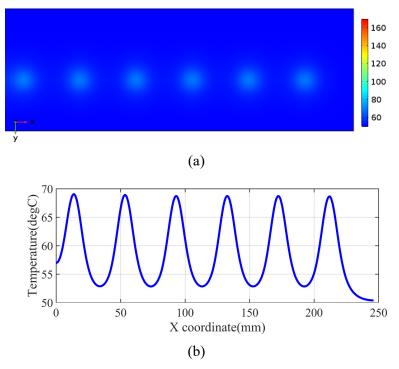

| Figure 4.6: Temperature distribution on the bottom surface of baseplate78                     |

| Figure 4.7: Temperature distribution on diode 1 top surfaces with different degradation       |

| levels (a)-(e) from 1.1 <i>R</i> <sub>th0</sub> to 1.5 <i>R</i> <sub>th0</sub>                |

| Figure 4.8: Temperature distribution on (a) top surface of diode 1 and (b) case surface       |

| beneath diode 180                                                                             |

| Figure 4.9: Instrumentation points in the power module system                                 |

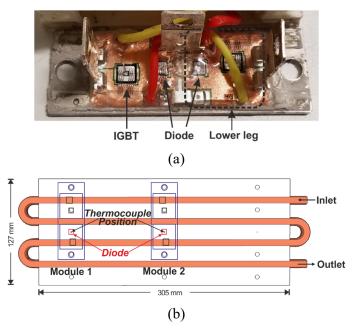

| Figure 4.10: Multi-chip experimental rig, (a) power module and (b) heatsink82                 |

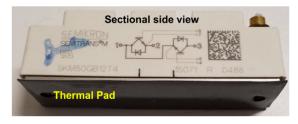

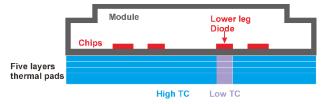

| Figure 4.11: Thermal pad attached on baseplate                                                |

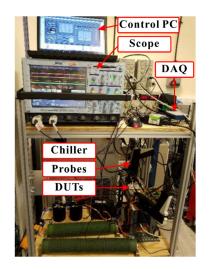

| Figure 4.12: Complete experimental rig                                                        |

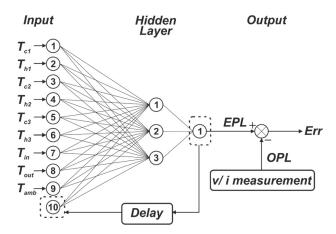

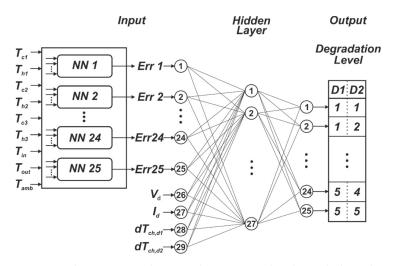

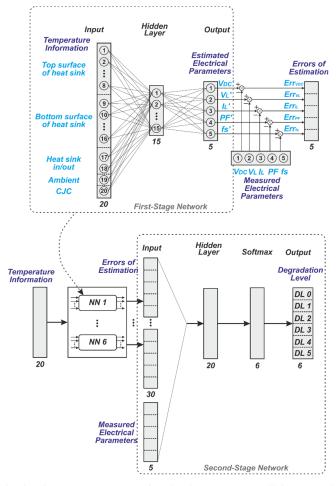

| Figure 4.13: Structure of a sub-NN in the first stage                                         |

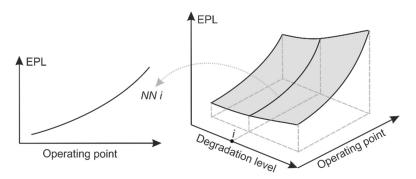

| Figure 4.14: Training of sub-neural networks with variable operating point                    |

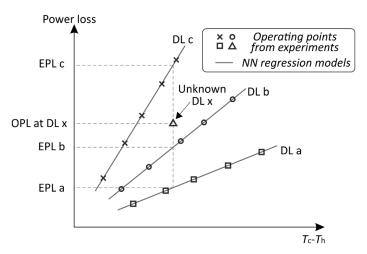

| Figure 4.15: Illustration of the method by the deviation between EPL and OPL87                |

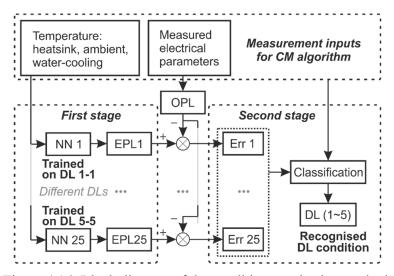

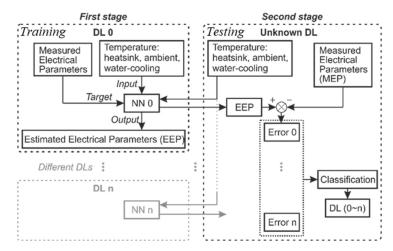

| Figure 4.16: Block diagram of the condition monitoring method                                 |

| Figure 4.17: Second stage neural network structure for degradation classification             |

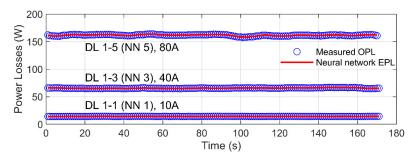

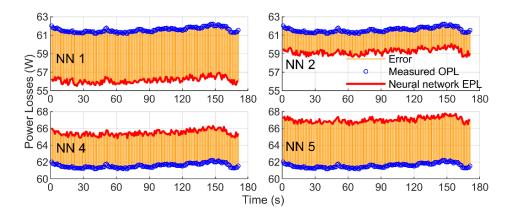

| Figure 4.18: Power loss estimation results by sub-neural networks with different degradation  |

| levels and operating points                                                                   |

| Figure 4.19: Power loss estimation from different sub-neural networks with degradation        |

| level DL1-3 and 40 A total current                                                            |

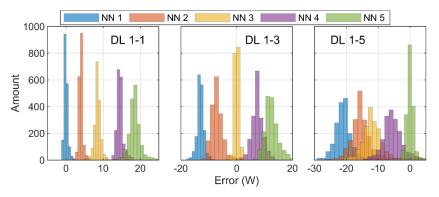

| Figure 4.20: Estimation error histograms for 5 sub-neural networks with 3 degradation levels: |

| DL1-1, DL1-3, and DL1-590                                                                     |

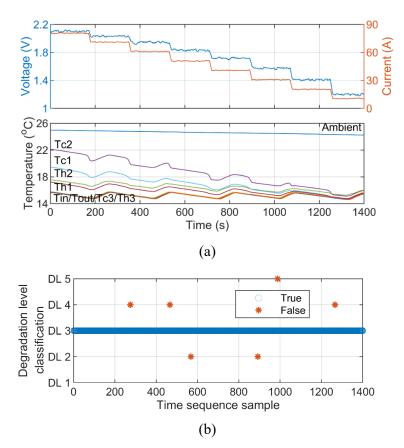

| Figure 4.21: (a) Measurements under DL 3-1 and (b) diode 1 degradation level monitoring       |

| results                                                                                       |

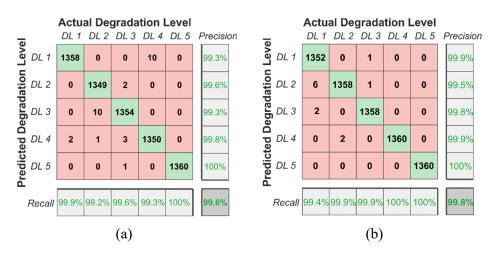

| Figure 4.22: Recognition results for single device aged conditions: (a) diode 1 degraded and   |

|------------------------------------------------------------------------------------------------|

| (b) diode 2 degraded92                                                                         |

| Figure 4.23: Recognition results for conditions with both devices aged: (a) diode 1            |

| classification and (b) diode 2 classification                                                  |

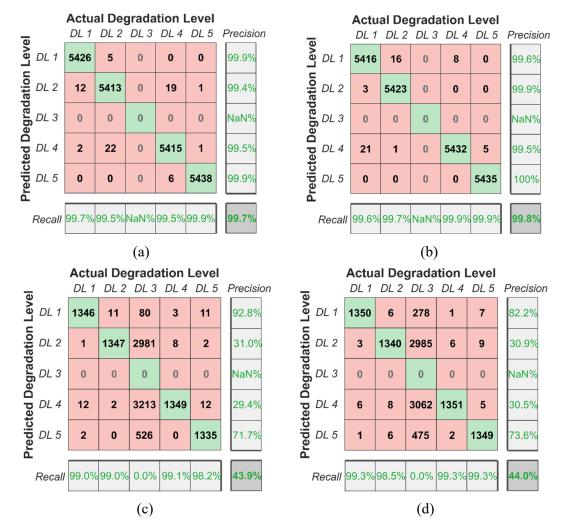

| Figure 4.24: Recognition of an intermediate degradation level: neural network training         |

| results for (a) diode 1 and (b) for diode 2 and, degradation recognition results for (c) diode |

| 1 and (d) diode 2                                                                              |

|                                                                                                |

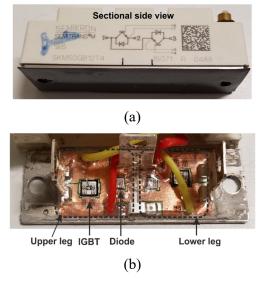

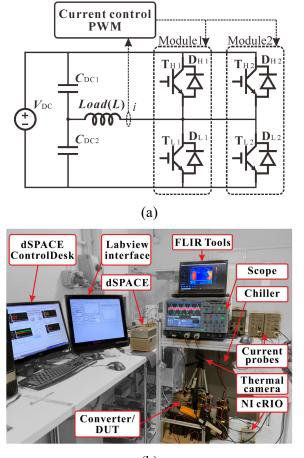

| Figure 5.1: The half-bridge inverter test, (a) circuit diagram and (b) test rig98                 |

|---------------------------------------------------------------------------------------------------|

| Figure 5.2: Temperature measurement positions on heatsink                                         |

| Figure 5.3: Thermal pad setup for DL 5                                                            |

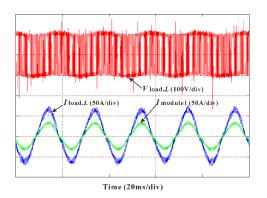

| Figure 5.4: Output of the test rig under 200V/40A100                                              |

| Figure 5.5: The layout of the uncased power module101                                             |

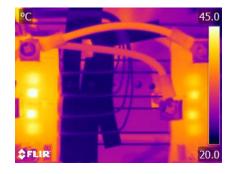

| Figure 5.6: Temperature distribution measured by thermal camera101                                |

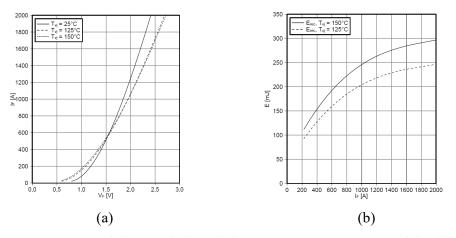

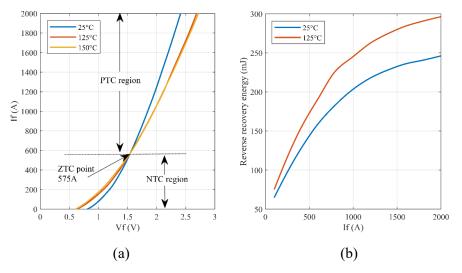

| Figure 5.7: (a) Forward characteristic and (b) reverse recovery energy of the multi-chip          |

| power module102                                                                                   |

| Figure 5.8: (a) The diode forward characteristic and (b) reverse recovery energy in different     |

| temperature102                                                                                    |

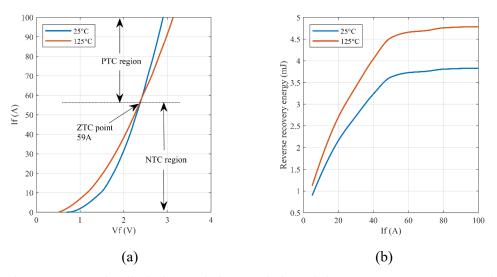

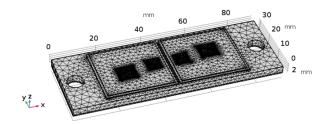

| Figure 5.9: The FEA model of the single-chip module103                                            |

| Figure 5.10: Outflow heat flux on (a) top surface and (b) bottom surface of the power module      |

|                                                                                                   |

| Figure 5.11: The ageing process of die-attach in FEA model105                                     |

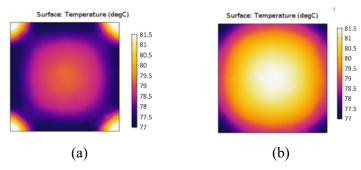

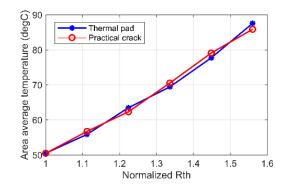

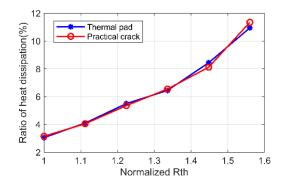

| Figure 5.12: The temperature distribution on diode surface with $1.2R_{th}$ , (a) practical crack |

| modelled and (b) with a thermal pad105                                                            |

| Figure 5.13: Average temperature on the chip surface under different DLs106                       |

| Figure 5.14: The ratio of the heat dissipating through top surface under different DLs106         |

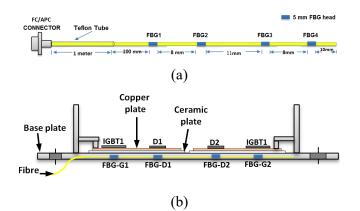

| Figure 5.15: (a) FBG thermal senor design and (b) FBG array sensor instrumentation in the         |

| DUT107                                                                                            |

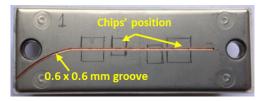

| Figure 5.16: Grooved power module108                                                              |

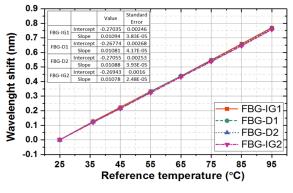

| Figure 5.17: FBG array thermal calibration109                                                     |

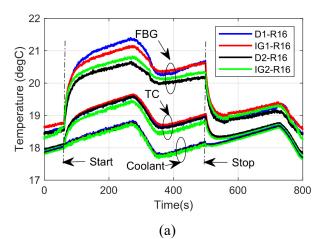

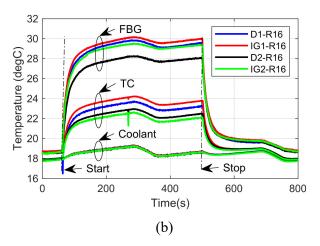

| Figure 5.18: FBG and TC temperature measurements under static conditions of load current          |

| (a) 10 A and (b) 50 A                                                                             |

| Figure 5.19: Test power module thermal network                                             |

|--------------------------------------------------------------------------------------------|

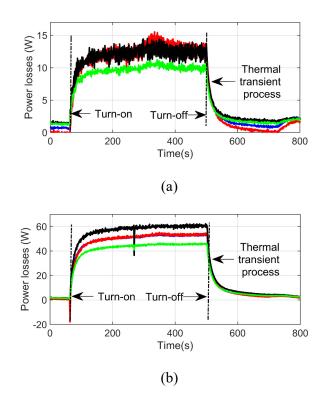

| Figure 5.20: Power losses calculation under (a) 10A and (b) 50A total current step-change  |

| conditions                                                                                 |

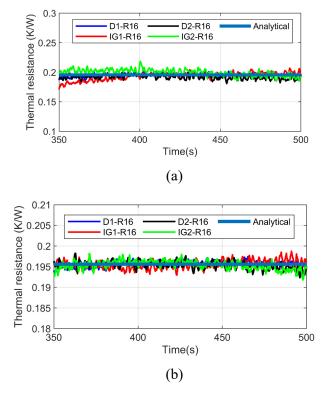

| Figure 5.21: Validation of temperature measurement based on the thermal resistance of TIM  |

| <i>R</i> <sub>th,TIM</sub> under (a) 10A and (b) 50A total current conditions              |

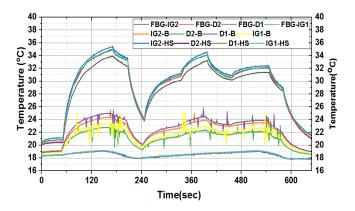

| Figure 5.22: Thermal measurement under dynamic condition115                                |

| Figure 5.23: Processing diagram of the condition monitoring method117                      |

| Figure 5.24: The basic two-stage NN for the improve condition monitoring method118         |

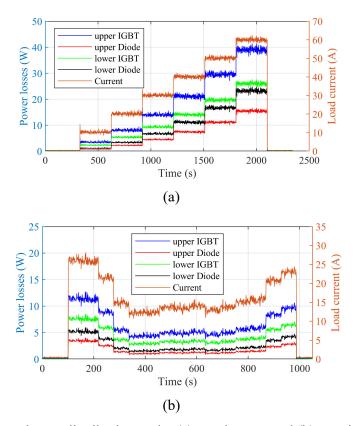

| Figure 5.25: The DNN structure in (a) first stage and (b) second stage118                  |

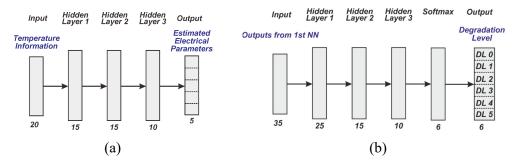

| Figure 5.26. Power losses distribution under (a) steady-state and (b) transient conditions |

|                                                                                            |

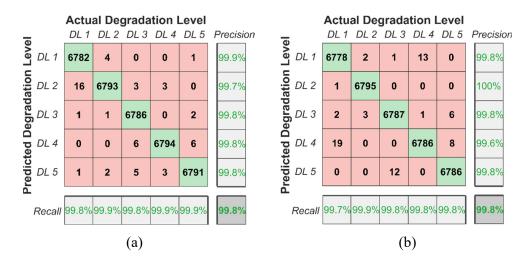

| Figure 5.27: Classification results of (a) basic NN and (b) deep learning architecture120  |

| Figure 6.1: Condition monitoring framework                                                           | 123   |

|------------------------------------------------------------------------------------------------------|-------|

| Figure 6.2: The network structure of (a) FCNN and (b) LSTM                                           | 124   |

| Figure 6.3: The flowchart of the PDW calculation process                                             | 127   |

| Figure 6.4: The hierarchical clustering dendrogram of SCADA channels                                 | 128   |

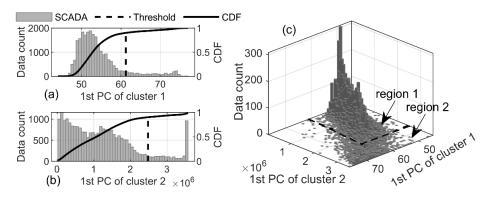

| Figure 6.5: The histogram and CDF of the 1 <sup>st</sup> PC for (a) cluster 1 and (b) cluster 2, and | l (c) |

| the joint probability distribution                                                                   | 130   |

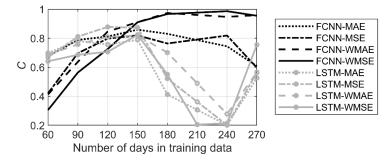

| Figure 6.6: The consistency $C$ of FCNN and LSTM with four cost functions on the diffe               | rent  |

| amounts of training data                                                                             | 131   |

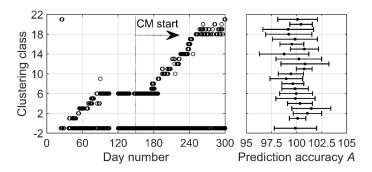

| Figure 6.7: The clustering results and corresponding error bar of each class                         | 131   |

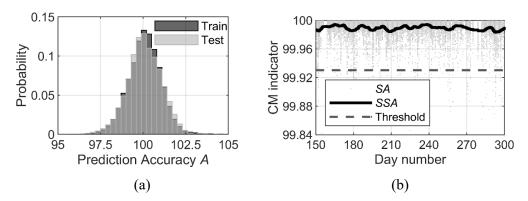

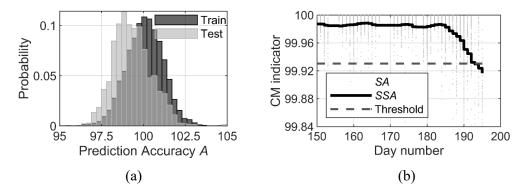

| Figure 6.8: (a) The prediction accuracy distribution and (b) condition monitoring result             | s of  |

| healthy WT No.1                                                                                      | 132   |

| Figure 6.9: The prediction accuracy distribution and (b) condition monitoring results of N           | Jo.5  |

| WT with converter fault reported on day 195                                                          | 133   |

### List of Tables

| Table 1.1: Failure mechanisms caused by thermomechanical stress                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Failure mechanisms caused by electrical stress [29]10                                                                                                  |

| Table 1.3: The ageing characteristic parameters of the high-power IGBT device12                                                                                   |

|                                                                                                                                                                   |

| Table 2.1: Average percentage growth of void area and volume                                                                                                      |

| Table 2.2: Packaging material parameters for FEA modelling                                                                                                        |

| Table 2.3: Parameters definition of Anand's model    40                                                                                                           |

| Table 2.4: Measured crack growth rate results and computed fatigue strain                                                                                         |

|                                                                                                                                                                   |

| Table 3.1: Packaging material properties for FEA modelling                                                                                                        |

| Table 3.2: The parameters of the power module thermal network                                                                                                     |

| Table 3.3: The parameters of Bayerer lifetime model                                                                                                               |

|                                                                                                                                                                   |

| Table 4.1: Diode thermal resistance at different degradation levels                                                                                               |

| Table 4.2: Neural network definition matrix based on combination of device degradation                                                                            |

| levels                                                                                                                                                            |

|                                                                                                                                                                   |

| Table 5.1: Operating conditions                                                                                                                                   |

| Tuese 511 operating conditions                                                                                                                                    |

| Table 5.2: Thermal resistance at different degradation levels    100                                                                                              |

|                                                                                                                                                                   |

| Table 5.2: Thermal resistance at different degradation levels    100                                                                                              |

| Table 5.2: Thermal resistance at different degradation levels100Table 5.3: Packaging material parameters for FEA modelling103                                     |

| Table 5.2: Thermal resistance at different degradation levels100Table 5.3: Packaging material parameters for FEA modelling103Table 5.4: Thermal pad parameters112 |

### Acknowledgements

First and foremost, I would like to express my sincere gratitude to my supervisor Professor Li Ran. His continuous guidance helped me in all the time, from Chongqing China to Coventry UK, from the first COMSOL model we built to the whole thesis finished. It is so lucky that I can work with him, who has always given me all the opportunities to drive myself in research. The most valuable thing is that he has shown me how a true researcher should have such enthusiasm for research and keep thinking all the time sharply.

I would like to thank Dr Chunjiang Jia, Dr Chong Ng and Paul McKeever, from Offshore Renewable Energy Catapult for sponsoring my PhD in Warwick. I am very grateful that they provided wind data, had me in the Blyth office and gave valuable suggestions on my research from the industrial perspective. I also thank Dr Nadia Kourra and Prof. Mark Williams from Warwick Manufacturing Group, who provided the CT equipment and pre-processed scanning data. My thanks also go to Dr Anees Mohammed and Dr Sinisa Djurovic from the University of Manchester for fabricating FBG sensors and the discussion about distributed temperature sensing scheme.

I would like to thank my colleagues in the PEATER group, especially thanks to Dr Jose Ortiz Gonzalez for revising my papers and helping me to solve experimental problems, and Dr Sylvia Konaklieva for working together on the solder scanning. It's also great to have my friends, Dr Fan Li, Dr Ruizhu Wu, Dr Tianxiang Dai, Xuan Guo, and Dan Luo, with the great time we had in the office, lab, restaurant, and even on Steam.

I would like to thank my friends and colleagues in Chongqing, where my research started and where we had a wonderful time. Especially thanks to Prof. Hui Li, Dr Zheng Zeng, Prof. Minyou Chen and Dr Wei Lai for teaching me loads of tools and rules that needed for researching.

I would like to express my gratitude to my parents for supporting me throughout and respecting my every choice. I especially thank my wife, who is such a precious treasure, accompanying me in the UK, supporting my work, and colouring my life.

### Declaration

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has been composed by myself and has not been submitted in any previous application for any degree. The work presented (including data generated and data analysis) was carried out by the author except in the cases outlined below:

The power module samples were scanned by using the X-ray CT equipment at Warwick Manufacturing Group. The scanning results were analysed by the author and presented in Chapter 2.

The FBG fibre used in Chapter 5 was fabricated and installed by collaborating with the University of Manchester. The author provided the design specification of the FBG fibre, performed the tests, and analysed the results.

Parts of this thesis have been published by the author. The details are given in the List of Publications.

### **List of Publications**

#### Chapter 2

- J1. B. Hu, S. Konaklieva, N. Kourra, M. A. Williams, L. Ran, and W. Lai, "Long-Term Reliability Evaluation of Power Modules with Low Amplitude Thermomechanical Stresses and Initial Defects," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 1, pp. 602-615, Feb. 2021, doi: 10.1109/JESTPE.2019.2958737.

- C1. B. Hu, S. Konaklieva, L. Ran, N. Kourra, M. A. Williams, W. Lai, and P. Mawby, "Long Term Reliability of Power Modules with Low Amplitude Thermomechanical Stresses and Initial Defects," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, 2018, pp. 5831-5838, doi: 10.1109/ECCE.2018.8558137.

#### Chapter 3

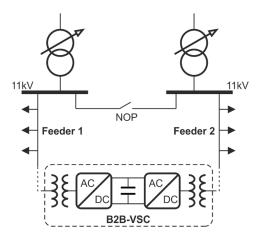

C2. B. Hu, X. Guo, S. Konaklieva, L. Ran, H. Li, C. Ng, and P. McKeever, "Lifetime Consumption of Wind Turbine Power Converter in the Whole Wind Speed Range," *The 9th International Energy Conference REMOO*, Hong Kong, 2019.

#### Chapter 4

- J2. B. Hu, S. Konaklieva, S. Xu, J. Ortiz-Gonzalez, L. Ran, C. Ng, P. McKeever, and O. Alatise, "Condition monitoring for solder layer degradation in multi-device system based on neural network," in *The Journal of Engineering*, vol. 2019, no. 17, pp. 3582-3586, 6 2019, doi: 10.1049/joe.2018.8025.

- J3. B. Hu, Z. Hu, L. Ran, C. Ng, C. Jia, P. McKeever, P. Tavner, C. Zhang, H. Jiang, and P. Mawby, "Heat-Flux Based Condition Monitoring of Multi-chip Power

Modules Using a Two-Stage Neural Network," in *IEEE Transactions on Power Electronics*, 2021, doi: 10.1109/TPEL.2020.3045604.

#### Chapter 5

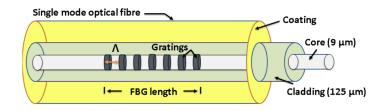

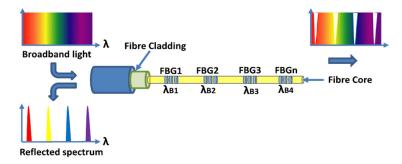

- J4. A. Mohammed, B. Hu, Z. Hu, S. Djurovic, L. Ran, M. Barnes, and P. Mawby, "Distributed Thermal Monitoring of Wind Turbine Power Electronic Modules Using FBG Sensing Technology," in *IEEE Sensors Journal*, vol. 20, no. 17, pp. 9886-9894, 1 Sept.1, 2020, doi: 10.1109/JSEN.2020.2992668.

- C3. B. Hu, Z. Hu, L. Ran, P. Mawby, C. Jia, C. Ng, and P. McKeever, "Deep Learning Neural Networks for Heat-Flux Health Condition Monitoring Method of Multi-Device Power Electronics System," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 2019, pp. 3769-3774, doi: 10.1109/ECCE.2019.8912666.

#### Chapter 6

J5. B. Hu, C. Jia, C. Ng, P. McKeever, S. Lakshminarayana, B. Chen, C. Zhang, and L. Ran, "Condition Monitoring of Wind Turbine Converters Based on Limited SCADA Data," ready to submit to *IEEE Transactions on Power Electronics*.

Other publications

- J6. B. Hu, J. Ortiz Gonzalez, L. Ran, H. Ren, Z. Zeng, W. Lai, B. Gao, O. Alatise, H. Lu, C. Bailey, and P. Mawby, "Failure and Reliability Analysis of a SiC Power Module Based on Stress Comparison to a Si Device," in *IEEE Transactions on Device and Materials Reliability*, vol. 17, no. 4, pp. 727-737, Dec. 2017, doi: 10.1109/TDMR.2017.2766692.

- J7. Z. Zeng, W. Shao, H. Chen, B. Hu, W. Chen, H. Li, and L. Ran, "Changes and challenges of photovoltaic inverter with silicon carbide device," in *Renewable and Sustainable Energy Reviews*, vol. 78, pp. 624-639, Oct. 2017, doi: 10.1016/j.rser.2017.04.096.

- C4. B. Hu, Z. Zeng, W. Shao, Q. Ma, H. Ren, H. Li, L. Ran, and Z. Li, "Novel cooling technology to reduce thermal impedance and thermomechanical stress for SiC application," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, 2017, pp. 3063-3067, doi: 10.1109/APEC.2017.7931133.

- C5. X. Li, H. Jiang, B. Hu, H. Chen, Z. Zeng, L. Ran, and P. Mawby, "Electro-Thermal Limited Switching Frequency for Parallel Diodes," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, 2018, pp. 4692-4698, doi: 10.1109/ECCE.2018.8557614.

(J for journal, C for conference)

### Abstract

The powertrain conversion system in state-of-the-art wind turbines has developed to a power rating of more than 10 MW. Due to the relatively low current rating of a single semiconductor chip, the large power module in turbine converters still adopts a multi-chip-in-parallel setup, counted as the most vulnerable component in the turbine system. Thus, this thesis focuses on evaluating the uneven degradation of multi-chip power modules under realistic conditions and developing field-deployable condition monitoring methods for wind turbine converters.

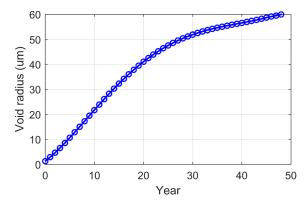

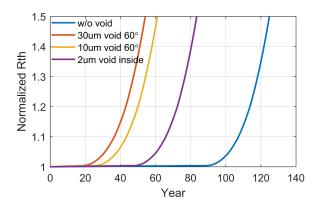

Two kinds of initial defects in power module solder layer, voids and cracks, indeed grow quietly under low-temperature stress cycles, illustrated by computed tomography scanning and finite element analysis. This thesis provides a physics-of-failure tool to estimate such dynamic of defect growth and finds that a void may first transform into a crack then grow more rapidly leading to device failure. At converter level, due to deep temperature cycling calculated from an electrothermal model, the machine side converters of fully and partially rated wind turbines, both consume a large amount of lifetime under the fundamental frequency. When looking inside the multi-chip module, an asymmetrical packaging layout and initial defects can cause years lifetime difference between paralleled devices while the weak one's further ageing progress will be significantly accelerated.

A condition monitoring scheme for detecting such uneven degradation in a multi-chip-inparallel system is proposed in this thesis, based on a core concept - train a network to represent the healthy state and then use its prediction deviation to distinguish faulty conditions. A two-stage neural network method based on only external measurements experimentally achieves a detection rate of over 98%. Furthermore, the feasibility of such a method is improved in three aspects. The labelled data for the network training is generated from an inverter test rig of equivalently emulating uneven degradation. The fibre Bragg grating multi-point sensing technique provides high temperature measuring precision with immunity to electromagnetic interference. The complex operating conditions is also generalised by a deep neural network structure, which achieves an overall accuracy of more than 95% under dynamic thermal conditions encountered in a practical wind speed profile.

Finally, based on the same concept, a field-deployable condition monitoring method is proposed to detect the early-stage fault of wind turbine converters using limited and unbalanced SCADA data. A deep neural network with optimised cost function is designed by an unsupervised approach and empowered by an online learning process for long-term real-time anomaly detection. The proposed method shows robust diagnosis results and would predict the converter fault a few days ahead of actual failure.

## Nomenclature

| ALT  | accelerated lifetime testing         |

|------|--------------------------------------|

| B2B  | back-to-back                         |

| CDF  | cumulative density function          |

| CJC  | cold junction temperature            |

| CM   | condition monitoring                 |

| CT   | computed tomography                  |

| CTE  | coefficients of thermal expansion    |

| DBC  | direct bonded copper                 |

| DFIG | doubly-fed induction generator       |

| DL   | degradation level                    |

| DNN  | deep neural network                  |

| DUT  | device under test                    |

| EEP  | estimated electrical parameters      |

| EMI  | electromagnetic interference         |

| EPL  | Estimated power loss                 |

| FBG  | fibre Brag granting                  |

| FBP  | filtered back projection             |

| FCNN | fully connected neural network       |

| FEA  | finite element analysis              |

| FRD  | freewheeling diode                   |

| HVDC | high voltage direct current          |

| IGBT | insulated gate bipolar transistor    |

| IGCT | integrated gate commutated thyristor |

| LSTM | long-short term memory               |

| MAE  | mean absolute error                  |

| MEP  | measured electrical parameters       |

| MPPT | maximum power point tracking         |

| MSE  | mean square error                    |

| MTBF | mean time between failures           |

|      |                                      |

- MTO metal-oxide-semiconductor turn-off thyristor

- NN neural network

- OPL measured operational power loss

- PC principal component

- PCA principal component analysis

- PDW probability density weight

- PMSG permanent magnet synchronous generator

- ReLU rectified linear unit

- SEM scanning electron microscope

- SCADA supervisory control and data acquisition

- TDDB time-dependent dielectric breakdown

- TIM thermal interface material

- TSEP temperature sensitive electrical parameter

- VSC voltage source converter

- WT wind turbine

| A                     | accuracy                                            |

|-----------------------|-----------------------------------------------------|

| С                     | consistency                                         |

| d                     | duty cycle, distance                                |

| D                     | bond wire diameter                                  |

| $D_a$                 | accumulated damage                                  |

| $\Delta arepsilon$ in | fatigue inelastic strain per cycle                  |

| F                     | cumulative density function                         |

| f                     | the fundamental cycle current frequency             |

| f <sub>sw</sub>       | switching frequency                                 |

| Ibw                   | current through each bond wire                      |

| <i>i</i> <sub>c</sub> | converter output phase current                      |

| $I_{g,leak}$          | gate leakage current                                |

| Ig,on                 | gate turn-on current                                |

| Isc                   | short circuit current                               |

| LChrs                 | the lifetime consumption per hour                   |

| LC <sub>MWhrs</sub>   | The lifetime consumption per MW hrs power generated |

| m                     | number of data                                      |

|                       |                                                     |

| Nf                 | the number of cycles to failure                      |

|--------------------|------------------------------------------------------|

| $P_{cond,S}$       | the conduction loss of switch device                 |

| $P_{cond,D}$       | the conduction loss of freewheeling diode            |

| Phrs               | the power generated per hour                         |

| $P_{toff}$         | turn-off losses                                      |

| Pton               | turn-on losses                                       |

| $R^2$              | coefficient of determination                         |

| $R_{Al}$           | metallization layer resistance                       |

| $R_{bw}$           | bond wire equivalent resistance                      |

| Ron                | on-state resistance                                  |

| $R_{on,S}$         | the on-state resistance of switch device             |

| $R_{on,D}$         | the on-state resistance of freewheeling diode        |

| Rth                | thermal resistance                                   |

| $\Delta R_{th,a}$  | increase of normalised thermal resistance to failure |

| $R_{th,c-h}$       | case-heatsink thermal resistance                     |

| $R_{th,j-c}$       | junction-to-case thermal resistance                  |

| $R_{th,TIM}$       | thermal resistance of the thermal interface material |

| σ                  | standard deviation                                   |

| SA                 | accuracy with squared error                          |

| size               | number of points in dataset                          |

| SSA                | smoothed accuracy with squared error                 |

| t                  | actual observation                                   |

| Т                  | principal component                                  |

| Tamb               | ambient temperature                                  |

| $T_c$              | case temperature                                     |

| $T_h$              | heatsink temperature                                 |

| Tin                | inlet coolant temperature                            |

| $T_j$              | junction temperature                                 |

| T <sub>j,min</sub> | minimum value of junction temperature                |

| Tj,mean            | mean value of junction temperature                   |

| $\Delta T_j$       | amplitude of junction temperature cycling            |

| Tout               | outlet coolant temperature                           |

| ton                | time of heating stage                                |

| и            | batch size                       |

|--------------|----------------------------------|

| v            | number of output channels        |

| Var          | variation                        |

| $V_{ce}$     | on-state voltage                 |

| $V_{ce,off}$ | turn-off voltage                 |

| Vce,sat      | on-state saturation voltage drop |

| $V_F$        | forward voltage drop             |

| $V_{ge}$     | gate-emitter voltage             |

| $V_{ge,off}$ | gate turn-off voltage            |

| $V_{ge,on}$  | gate turn-on voltage             |

| $V_{ge,th}$  | gate-emitter threshold voltage   |

| Vrated       | device rated voltage             |

| Vth          | threshold voltage                |

| w            | probability density weight       |

| W            | weight matrix                    |

| X            | standardized data                |

| Χ            | SCADA data                       |

| У            | prediction of the network        |

|              |                                  |

## **1** INTRODUCTION

#### 1.1 BACKGROUND

In large-scale power system applications such as wind energy and high voltage direct current (HVDC) transmission, the use of advanced high-power semiconductor devices can effectively simplify circuit topologies, reduce device failure rates and system maintenance costs. At present, the mature commercial high-power devices on the market mainly include thyristors and their derivatives: integrated gate commutated thyristors (IGCTs), metal-oxide-semiconductor turn-off thyristors (MTOs), and insulated gate bipolar transistors (IGBTs). Among them, the IGBT, as a type of fully controlled semiconductor device by gate voltage, has the advantages of a flexible control scheme and high-power density and has been regarded as the mainstream of high-power devices. With the growth of the power system's demand for power electronics, the proportion of high-power power electronic equipment continues to increase, so do the requirements for higher reliability, namely lower failure rate and longer mean time between failures (MTBF).

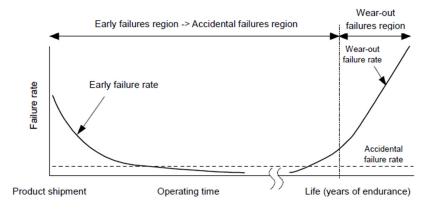

The traditional method of improving system reliability adopts redundant design, i.e., by adding hot spare devices, the system can still maintain normal operation after some components fail. Another method is to reduce the failure rate of core components and reduce the number of failures in the system. The failure rate of power semiconductor devices with time is generalised as "bathtub curve" as shown in Figure 1.1 [1]. According to the different stages of failure, it can be divided into early failure, accidental failure, and ageing failure. Devices have a high failure rate in the early and late stages of service. Early failures are affected by the yield of the device production process and can be resolved through device

screening and replacement. The failure rate will gradually decrease over time. In the later stages of service, the device will suffer internal damage and performance degradation caused by fatigue accumulation resulting in ageing failure rate gradually increasing with time. It can be seen that the failure of power semiconductor devices mainly occurs in the later stage of service, and the failure rate is closely related to the ageing development process. Therefore, studying the ageing failure mechanism and monitoring scheme of power semiconductor devices is of great significance for improving the reliability of power electronic equipment and reducing shutdown failure loss.

Figure 1.1: Change in the failure rate of a semiconductor device over time [1]

In order to reduce the ageing failure rate of power semiconductor devices, the currently regular maintenance is adopted as a countermeasure in industry. The ageing and failure of components are prevented through regular maintenance and replacement of long-term serviced components. Although regular maintenance can reduce the device failure rate to a certain extent, it costs relatively high and cannot completely prevent the occurrence of failures. Condition monitoring is a health state evaluation method that uses sensors and signal processing technology to collect and analyse the operating characteristic parameters of a power electronic system [2]. Condition monitoring can timely discover the performance degradation of the device in the later stage of service, so as to take targeted measures to prevent failure. Compared with regular maintenance, condition monitoring can further improve the reliability and effective utilisation of equipment and reduce overall system operation and maintenance costs.

Moreover, the bathtub curve shown in Figure 1.1 is a statistical result extracted from experimental tests of a large number of devices. For a specific single device, its ageing process is affected by system layout design, operating conditions, and initial microscopic defects, which would inevitably cause uneven degradation among devices. The power electronic system reliability depends on the weakest component, e.g., the failure of a single chip can result in the multi-chip power module burned out completely. The cost of maintenance and repair of wind turbines is a considerable large number, especially for offshore wind farms. Thus, the condition monitoring, as effective means to detect ageing and avoid sudden failures, can play a very important role in all stages of the device and system service life.

At present, there has been a lot of research on the ageing failure mechanism of power semiconductor devices, and the packaging-related ageing failure is one of the most critical areas needed to focus on. High-power devices can be divided into solder-bonding device and press-pack device according to their packaging types. The failure of the soldered device is mainly due to mechanical stress caused by the mismatch of coefficients of thermal expansion (CTEs) of packaging materials [3-6]. The press-pack device is highly reliable compared with soldered modules, but its failures are more due to the uniformity of paralleled semiconductor chips in terms of pressure, current, and temperature [7-10]. In addition, long-term electrical and thermal stress can also cause semiconductor chip-related ageing failures [1, 11]. On-line condition monitoring of power devices has become another research hotspot. From the perspective of device ageing characteristics, a variety of monitoring methods have been proposed [2, 4, 12-14]. However, the condition monitoring of high-power devices is still facing the challenges: the interaction of multiple ageing mechanisms, the insensitivity of ageing characteristic parameters, and the difficulty of signal acquisition, which need further research.

#### **1.2 PACKAGING OF HIGH-POWER SEMICONDUCTORS**

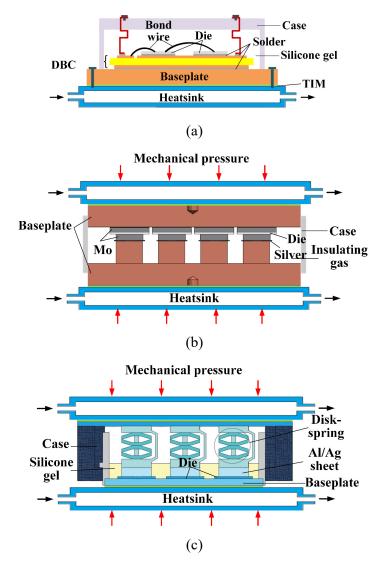

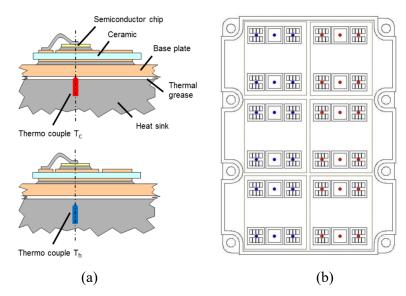

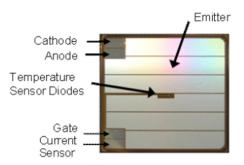

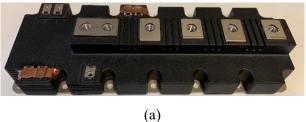

The high-power semiconductor device adopts modular packaging, and its packaging forms include solder-bonding and press-pack. The internal packaging structure of the two types of IGBT packaging is shown in Figure 1.2.

Figure 1.2: The packaging of high-power IGBT devices, (a) solder-bonding IGBT module, (b) full press-pack IGBT, and (c) disk-spring press-pack IGBT

The devices with two types of packaging have different post-failure manifestations. The solder-bonding module, after bond wire lift-off, will result in open circuit. While the failure of press-pack is mostly manifested as a short circuit[15]. Short-circuit failure has great advantages when devices are connected in series in high-voltage equipment. A limited number of device failures will not affect the normal operation of series-connected components. With the redundant design, the overall reliability is high, but the cost and power consumption will also increase.

The press-pack device realises the interconnection of the packaging material by applying mechanical pressure, generally 10-20 N/mm<sup>2</sup>. The electrical layout and heatsink are arranged at both ends of the device, which easily achieves the series connection of multiple devices. The structure of the press-pack device consists of two types: full press-pack and disc-spring press-pack. The full press-pack package is evolved from high-power diodes and thyristors. It uses ceramic packaging technology and has good sealing. The disc-spring press-pack is ABB's patented packaging technology (ABB Stakpak): the built-in paralleled disc-spring realises the decoupling of the pressure among paralleled chips leading to even pressure distribution. With regards to press-pack IGBT installation, a layer of TIM is also coated between the device and the heatsink to reduce thermal resistance [16]. Since there is no electrical isolation between the press-pack devices and the heatsinks, deionized water or insulating oil is generally required as a coolant to avoid being conductive. This type of packaging is typically utilised in HVDC power transmission and high-power traction drives.

The packaging materials of each layer of the solder-bonding module are interconnected by reflow soldering and wire bonding. The electrical connection is concentrated on the upper part of the module, and the heatsink is located at the bottom. Both are electrically insulated by direct bonded copper (DBC). The module is not completely sealed: silicone gel is encapsulated into the module to isolate the external environment such as moisture, acid, and alkali, and to improve the insulation capacity. In the application field assembly, the module is fixed on the heatsink surface by screws. In order to reduce the contact thermal resistance between the module baseplate and heatsink surface, a layer of thermal interface material (TIM) must be coated between such two surfaces during installation. This type of packaging is used in most power conversion applications such as power supply units, electric vehicles, wind turbine drivetrain converter, grid-tied inverters and etc. Thus, this thesis will focus on the investigation of reliability and condition monitoring of the solder-bonding module.

#### **1.3 AGEING MECHANISMS AND FAILURE MODES**

The ageing failure of power devices is a combined result of the accumulation of internal fatigue damage under stress and the effect of the external environment. The complicated multi-physics coupling will produce various failure modes. According to the types of stresses

the device suffered, the failure mechanism can be divided into two types: thermomechanical stress and electrical stress.

#### 1.3.1 Thermomechanical stress

The packaging materials of power semiconductor devices have differences in CTEs. When operating conditions changing, the material interconnection interface will be subjected to strong alternating thermomechanical stress. Under such long-term effect, creep, fatigue, and wear-out will cause interconnection degradation and device failure. The ageing failure modes and failure mechanisms are summarised in Table 1.1. The thermal interface material between the power semiconductor device and the heat sink will also gradually degrade due to thermal cycling, which will appear in both packaging types.

| Device         | Failure modes                    | Ageing mechanisms            |

|----------------|----------------------------------|------------------------------|

|                | Bond wire lift-off               | Fatigue                      |

| Solder-        | Solder degradation (void, crack) | Creep, fatigue               |

| bonding        | Metal reconstruction             | Plastic strain               |

|                | TIM degradation                  | Volatilization, displacement |

|                | Contact surface damage           | Fretting wear                |

| Press-<br>pack | Spring failure                   | Fatigue, stress relaxation   |

|                | TIM degradation                  | Volatilization, displacement |

Table 1.1: Failure mechanisms caused by thermomechanical stress

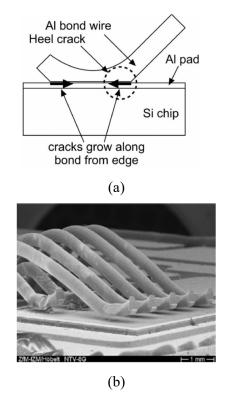

Under the effect of thermomechanical stress, the solder-bonding device suffers internal ageing, which mainly occurs at the interconnection interfaces such as bond wires and solder layers. The bond wire failure is mainly manifested as the bond wire lift-off, as shown in Figure 1.3 [2, 6]. There is a large difference between the CTEs of aluminium bond wires (23 ppm/K) and silicon chips (3 ppm/K). The bond wire heel on the chip surface will be subjected to high reciprocating shear stress under large junction temperature fluctuations. The shear stress is likely to cause fatigue resulting in a crack initiation, and the further development of the crack will eventually lead to bond wire lift-off [2, 6]. After a single wire

falls off, the falling process of remaining bond wires will be accelerated due to current overloaded, which may also cause the top of the lead to fuse [5]. A high-power device is mostly packaged with multi-chip in parallel, in which dozens of bond wires are shunted at the same time. This requires extremely high sensitivity of condition monitoring, necessitating to comprehensively consider measurement signals, monitoring objects and diagnosis solutions.

Figure 1.3: Bond wire lift-off, (a) diagram [2] and (b) scanning electron microscope (SEM) photo [6]

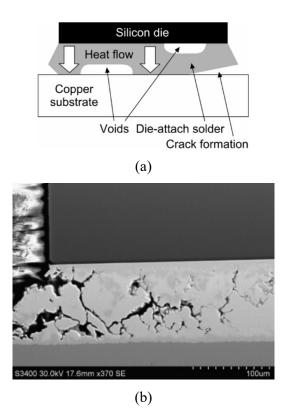

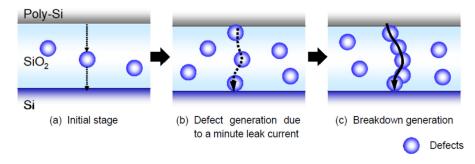

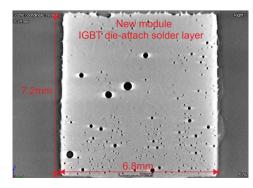

The ageing of the solder layer is manifested as the increase of voids and cracks, as shown in Figure 1.4 [2, 17]. Although the vacuum reflow process is widely used, air bubbles remain in the solder layer during the soldering process, forming initial voids. The initial void will cause stress concentration on the surrounding solder area, lead to void growth and crack initiation, and accelerate device ageing process [2, 5, 17]. In order to improve the current capability, the chip solder area and the baseplate of the high-power device are relatively large. Although the void rate of commercial product can generally be controlled below 5%, some studies have shown that the voids distributed on the boundary between the solder layer

and the chip will cause the cracks to develop faster [18]. In addition, there is also stress concentration at the corners of the solder layer, which is easy to creep and cause initial cracks under the alternating thermal stress [19]. A large amount of stress concentrates on the crack tip and accelerates its expansion and development, decreasing the effective contact area of the solder layer and increasing the thermal resistance of the device. It can be seen that a single failure of the solder layer is a very complicated process, so a more convenient and effective advanced modelling method is needed to evaluate this. At the same time, based on its most important feature, the increase of thermal resistance, the condition monitoring strategy should be studied correspondingly.

Figure 1.4: Solder degradation, (a) diagram [2] and (b) SEM photo [17]

Bond wire lift-off and solder layer degradation are the two most common ageing mechanisms for solder-bonding devices. The occurrence of the two mechanisms is closely related to the changing rate and amplitude of the chip junction temperature  $(T_j)$  during device operation. The power cycling test results show that under a small amplitude temperature cycling  $(\Delta T_j)$  the device is mainly damaged by the solder layer fatigue. As the junction-to-case thermal resistance  $(R_{th,j-c})$  of the device increases,  $\Delta T_j$  increases accordingly, leading to

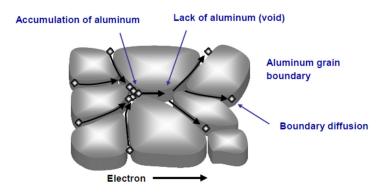

the bond wire fall off in a short time [3, 20]. In addition, the metallization layer on the surface of the chip is a granular structure formed under vacuum conditions. Under the effect of thermal stress, metallization reconstruction results in plastic deformation of the material, surface particles bulging, and increased electrical resistance and surface roughness [21]. Reconstruction of the chip surface metallization and the bond wire shedding will cause changes in the current distribution on the chip's surface and interior and increase the risk of local over-electric stress failure of the chip [22]. In practices, these two failure mechanisms are interacted, which increases the difficulty of accurately identifying the health state of the device.

The thermal interface material attached to the power semiconductor device will also be degraded under thermal cycling. Thermal interface materials mostly use silicone grease. It is a mixture of silicone oil and thermally conductive fine particles and has low thermal conductivity. Although the thickness of thermal interface materials is generally only 10-100µm, its thermal resistance can account for above 50% of the total thermal resistance of the system [11]. Warping and deformation of the device baseplate during thermal cycling will cause pumping and squeezing of the TIM; high temperature and thermal cycling will separate the silicone oil and the filler particles, volatilise the silicone oil, and dry up the silicone grease. Such effects can decrease the thermal conductivity of the silicone grease. The thermal interface material degradation does not directly affect the electrical characteristics of the device, but similar to the ageing of the solder layer it causes an increase in thermal resistance [23, 24]. Therefore, it is necessary to study the corresponding monitoring methods to distinguish it from the solder layer ageing.

The press-pack packaging system eliminates the bond wire and solder layer in the solderbonding devices. Compared with the solder-bonding devices, the operating life of press-pack can be increased by at least an order of magnitude [25]. However, the effect of thermomechanical stress will cause the internal ageing of the press-pack devices, resulting in the contact degradation of packaging interconnection interface material. The thermal mismatch of press-pack packaging materials will cause relatively little sliding between contact materials, e.g. the sliding distance between the IGBT chip (Si, CTE= 3 ppm/K) and the upper metal sheet (Ag/Al, 19/23 ppm/K) in the disc-spring press-pack is about 10 $\mu$ m [15]. Periodic fretting will cause wear and local fatigue on the contact surface, resulting in fretting damage [26].

It is worth noting that the press-pack usually packages multiple chips parallelly into a single device. This is prone to the problem of uneven pressure distribution and will accelerate the degradation of the device. In a press-pack IGBT, improper pressuring or a  $1\sim3\mu$ m height difference between parallel chips can cause 90% pressure difference among chips [10, 27]. Uneven pressure distribution will cause excessive mechanical stress and poor contact on the local area leading to mechanical damage [8]. It will also change the current distribution among paralleled chips and increase the risk of local over-electrical stress failure. In practices, the degradation failure process is often related to uneven stress distribution [28]. Therefore, attention should be paid to such uniformity problem when studying the ageing failure mechanism.

#### 1.3.2 Electrical stress

In addition to packaging ageing, the high voltage device will also suffer considerable electrical stress under long-term operation. The failures caused by electrical stress are summarised in Table 1.2 [29].

| Location                      | Failure modes                                                   | Ageing mechanisms                                           |

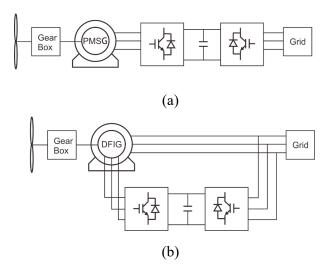

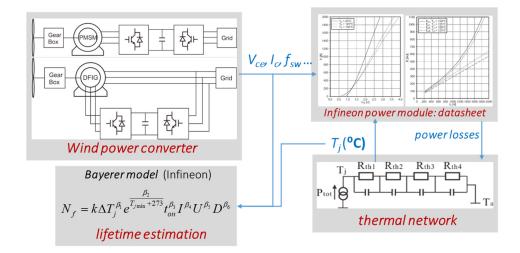

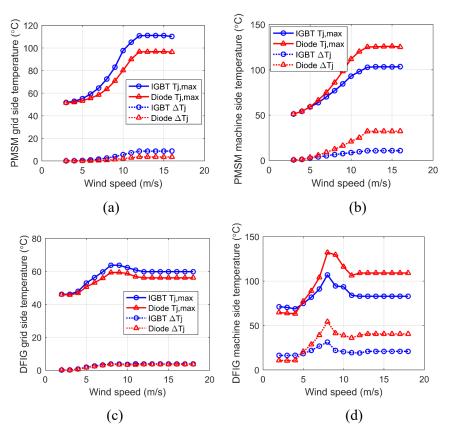

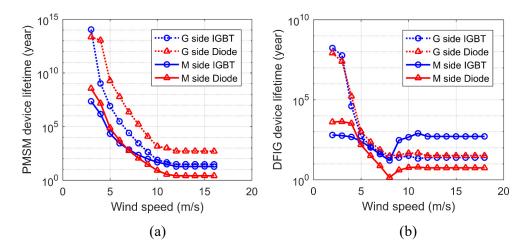

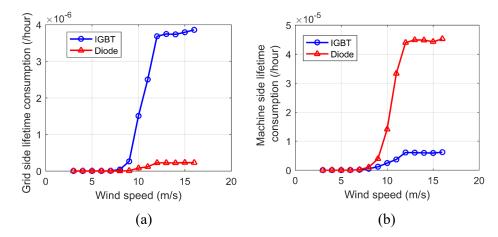

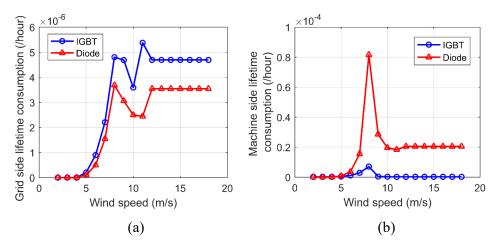

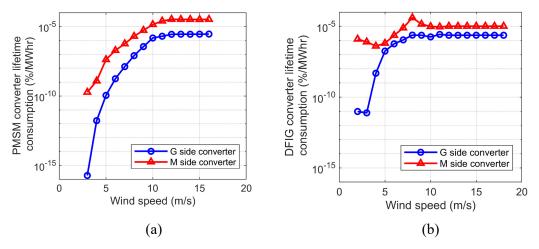

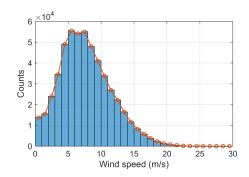

|-------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------|