#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### Permanent WRAP URL:

http://wrap.warwick.ac.uk/165223

#### Copyright and reuse:

This thesis is made available online and is protected by original copyright. Please scroll down to view the document itself. Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Development of Schottky and MOS interfaces for SiC power devices

Arne Benjamin Renz School of Engineering University of Warwick

Dissertation submitted for the degree of Doctor of Philosophy October 2021

### Contents

| Acknowledgements                                          | V      |

|-----------------------------------------------------------|--------|

| Declaration                                               | vi     |

| Publications                                              | vii    |

| Abstract                                                  | xi     |

| List of Abbreviations and Symbols                         | xii    |

| List of Figures                                           | xviii  |

| List of Tables                                            | xxiii  |

| Chapter 1: Introduction                                   |        |

| 1.1 SEMICONDUCTOR APPLICATIONS OVERVIEW                   | 1      |

| 1.1.1 Application space for other semiconductor materials | 2      |

| 1.1.2 The use of wide bandgap semiconductor devices       | 3      |

| <b>1.2</b> SEMICONDUCTOR ALLOYS AND COMPOUND SEMICONDUC   | TORS 5 |

| 1.3 REVIEW OF WIDE BANDGAP MATERIAL DEVICES               | 7      |

| 1.4 THESIS OUTLINE                                        | 10     |

| 1.5 REFERENCES                                            | 12     |

####

| 2.2 ELECTRICAL PROPERTIES                | 18 |

|------------------------------------------|----|

| 2.3 EPITAXIAL GROWTH OF 4H-SIC USING CVD | 21 |

| 2.4 MATERIAL CHALLENGES IN SIC           | 24 |

| 2.5 SIC DEVICES                                                |

|----------------------------------------------------------------|

| 2.5.1 Schottky Barrier Diodr                                   |

| 2.5.2 Merged PiN Schottky and Junction barrier Schottky diodes |

| 2.5.3 Metal-oxide semiconductor capacitors                     |

| 2.6 SCHOTTKY INTERFACE THEORY                                  |

| 2.6.1 Current transport across the Schottky barrier            |

| 2.6.2 Ideality factor                                          |

| 2.7 METAL-OXIDE-SEMICONDUCTOR (MOS) INTERFACE THEORY           |

| 2.7.1 Ideal C-V MOSCAP response in 4H-SiC                      |

| 2.7.2 Accumulation regime                                      |

| 2.7.3 Depletion regime                                         |

| 2.7.3 Flatband regime                                          |

| 2.7.3 Trapped charge and its impact on C-V responses           |

| 2.8 ELECTRICAL CHARACTERISATION TECHNIQUES                     |

| 2.8.1 I-V analysis                                             |

| 2.8.2 C-V analysis                                             |

| 2.9 PHYSICAL CHARACTERISATION TECHNIQUES                       |

| 2.9.1 Secondary Ion Mass Spectrometry49                        |

| 2.9.2 Atomic Force Microscopy                                  |

| 2.9.3 Scanning Electron Microscopy51                           |

| 2.9.4 Transmission electron microscopy52                       |

| 2.9.5 X-ray photoelectron spectroscopy                         |

| 2.9.6 Physical characterisation methodology overview           |

| 2.10 REFERENCES                                                |

| Chapter 3: The improvement of Mo/4H-SiC Schottky diodes via a P2O5 |    |

|--------------------------------------------------------------------|----|

| surface treatment                                                  |    |

| 3.1 INTRODUCTION                                                   | 59 |

| 3.2 DEVICE FABRICATION AND EXPERIMENTAL PROCEDURE                  | 61 |

| 3.3 CURRENT-VOLTAGE (I-V)                                          | 64 |

| 3.4 XPS AND SIMS STUDY                                             | 69 |

| 3.5 SURFACE MORPHOLOGY STUDY USING AFM AND SEM                     | 74 |

| 3.6 CROSS-SECTIONAL ANALYSIS USING TEM                             | 77 |

| 3.7 DEFECT CHARACTERISATION USING SYNCHROTRON XRT                  | 78 |

| 3.8 DISCUSSION                                                     | 80 |

| 3.9 CONCLUSION                                                     | 84 |

| 3.10 REFERENCES                                                    | 85 |

## Chapter 4: 3.3 kV SiC JBS diodes employing a P<sub>2</sub>O<sub>5</sub> surface passivation treatment to improve electrical characteristics

| 4.1 INTRODUCTION                                  |     |

|---------------------------------------------------|-----|

| 4.2 DEVICE FABRICATION AND EXPERIMENTAL PROCEDURE |     |

| 4.3 SCHOTTKY DIODE ELECTRICAL RESULTS             |     |

| 4.4 SCHOTTKY DIODE XPS INVESTIGATION              |     |

| 4.5 3.3 KV JBS DIODES – ELECTRICAL RESULTS        |     |

| 4.6 DOUBLE PULSE SWITCHING TEST                   | 100 |

| 4.7 CONCLUSION                                    | 103 |

| 4.8 REFERENCES                                    | 105 |

| Chapter 5: Development of High-Quality Gate Oxide on 4H-SiC Using         |     |

|---------------------------------------------------------------------------|-----|

| Atomic Layer Deposition                                                   |     |

| 5.1 INTRODUCTION                                                          | 107 |

| 5.2 DEVICE FABRICATION AND EXPERIMENTAL PROCEDURE                         | 111 |

| 5.3 INITIAL C-V AND TDDB MEASUREMENTS                                     | 115 |

| 5.4 IN-DEPTH C-V INVESTIGATION OF THE SIO <sub>2</sub> /4H-SIC INTERFACES | 121 |

| 5.5 SURFACE CHEMISTRY STUDY USING XPS AND SIMS                            | 126 |

| 5.6 CONCLUSION                                                            | 132 |

| 5.7 REFERENCES                                                            | 133 |

## **Chapter 6: Initial investigations into the MOS interface of**

## freestanding 3C-SiC layers for device applications

| 6.1 INTRODUCTION                                  | . 136 |

|---------------------------------------------------|-------|

| 6.2 DEVICE FABRICATION AND EXPERIMENTAL PROCEDURE | . 139 |

| 6.3 SURFACE ROUGHNESS INVESTIGATION USING AFM     | . 141 |

| 6.4 CRYSTAL QUALITY INVESTIGATION USING XRD       | . 143 |

| 6.5 ELECTRICAL RESULTS                            | . 145 |

| 6.6 CONCLUSION                                    | . 150 |

| 6.7 REFERENCES                                    | . 152 |

## **Chapter 7: Conclusion**

| 7.1 INTRODUCTION                 |  |

|----------------------------------|--|

| 7.2 SCHOTTKY DIODE CONCLUSIONS   |  |

| 7.2.1 Schottky diode future work |  |

| 7.3 MOS INTERFACE CONCLUSIONS    |  |

| 7.3.1 MOS Interface future work  |  |

| Appendix A: MATLAB Code for the extraction of ideality factors and |  |

|--------------------------------------------------------------------|--|

| barrier heights                                                    |  |

| A.1 AUTOMATIC DETERMINATION OF BARRIER HEIGHT                      |  |

| A.2 PARAMETER SETUP                                                |  |

#### Acknowledgements

A big thanks goes to Oli Vavasour, who has been an incredibly helpful and supportive colleague and, at most times, teacher throughout the past four years. Your encouragement, knowledge, hands-on experimental and analysis help as well as, at times, annoying pedantry (this is a good thing in the long term) have been a big driving force of my work. Thank you!

To my PhD supervisors Vishal Shah and Peter Gammon, I would like to thank you for your continued support and encouragement, both personal and professional. To this day, I really enjoy working with both of you. You gave me the opportunity to develop my own research ideas, to work independently and to present our work, for which I am extremely grateful. Furthermore, I appreciate the support of many co-workers without whom my research outcomes would have been impossible. Top of the list are the brilliant Fan Li and Tianxiang Dai. Your fabrication and simulation expertise were invaluable throughout the Ph.D. studies. Also in Warwick's Electronic Materials and Interfaces Group, a special thanks goes to John Murphy and Nick Grant for their help. To Jose Gonzalez, Ruizhu Wu, Corinne Maltby, Frank Courtney and Mark Crouch, thank you for your help in my most stressful device fabrication/characterisation moments. To Erfan Bashar, I thank you for our personal and professional relationship. You were always a great friend. The same applies to Guy Baker, who I extremely enjoy working with. You two are absolutely brilliant chaps. Finally, thanks go to my family, especially my mum and dad, brothers, for all your love and support. I would never have made it thus far without you! To my little family including my wife Hendrikje and daughter Josephine, thanks for your love and for simply being wonderful over this time. Words cannot describe how grateful I am to have the two of you in my life. I love you!

#### Declaration

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has been composed by myself and has not been submitted in any previous application for a degree at any other University.

Except where specifically stated, all of the work described in this thesis was carried out by the author or under his direction in the School of Engineering at the University of Warwick. Parts of this thesis have been published by the author during the period of study, from November 2017 to October 2021. They are given in full detail in the Publication List section.

Arne Benjamin Renz October 2021

#### List of journal publications

- A.B. Renz, F.Li, O.J. Vavasour, P.M. Gammon, T. Dai, G.W.C. Baker, F. La Via, M. Zielinski, L. Zhang, N.E. Grant, J.D. Murphy, P.A. Mawby, M. Jennings, and V.A. Shah, "Initial investigations into the MOS interface of freestanding 3C-SiC layers for device applications", *Semiconductor Science and Technology*, vol. 36, no.5, p. 055006, 2021.

- A.B. Renz, O.J. Vavasour, P.M. Gammon, F. Li, T. Dai, M. Antoniou, G.W.C. Baker, E. Bashar, N.E. Grant, J.D. Murphy, P.A. Mawby, and V.A. Shah, "The improvement of atomic layer deposited SiO<sub>2</sub>/4H-SiC interfaces via a high temperature forming gas anneal", *Materials Science in Semiconductor Processing*, vol. 122, p. 105527, 2021.

- A.B. Renz, V.A. Shah, O.J. Vavasour, Y. Bonyadi, F. Li, T. Dai, G.W.C. Baker, S. Hindmarsh, Y. Han, M. Walker, Y. Sharma, Y. Liu, B. Raghothamachar, M. Dudley, P.A. Mawby, and P.M. Gammon, "The improvement of Mo/4H-SiC Schottky diodes via a P2O5 surface passivation treatment", *Journal of Applied Physics*, vol. 127, no.2, p. 025704, 2020.

#### List of co-authored journal publications

- F. Li, A.B. Renz, A. Perez-Tomas, V.A. Shah, P.M. Gammon, F. La Via, M. Jennings, and P.A. Mawby, "A study on freestanding 3C-SiC bipolar power diodes", *Applied Physics Letters*, vol. 118, no. 24, p.242101, 2021.

- 2. G.W.C. Baker, C. Chan, A.B. Renz, Y. Qi, T. Dai, F. Li, V.A. Shah, P.A. Mawby, and P.M. Gammon, "Optimization of

1700 -V 4H-SiC Superjunction Schottky Rectifiers With Implanted P-Pillars for Practical Realization", *IEEE Transactions on Electron Devices*, vol. 68, no. 7, pp. 3497-3504, 2021.

T. Dai, L. Zhang, O.J. Vavasour, A.B. Renz, V.A. Shah, M. Antoniou, P.A. Mawby, and P.M. Gammon, "A Compact Trench-Assisted Space-Modulated JTE Design for High-Voltage 4H-SiC Devices", *IEEE Transactions on Electron Devices*, vol. 68, no. 3, pp. 1162-1167, 2021.

#### List of conference publications

- A.B. Renz, O.J. Vavasour, V.A. Shah, V. Pathirana, T. Trajkovic, Y. Bonyadi, R. Wu, J.A. Ortiz-Gonzalez, X. Rong, G.W.C. Baker, P.A. Mawby, and P.M. Gammon, "3.3 kV SiC JBS diodes employing a P<sub>2</sub>O<sub>5</sub> surface passivation treatment to improve electrical characteristics", *IEEE Energy Conversion Congress & Expo (ECCE)*, accepted for publication, 2021.

- A.B. Renz, O.J. Vavasour, P.M. Gammon, F. Li, T. Dai, S. Esfahani, G.W.C. Baker, N.E. Grant, J.D. Murphy, P.A. Mawby, and V.A. Shah, "Development of high-quality gate oxide on 4H-SiC using atomic layer deposition", *Materials Science Forum*, vol. 1004, pp. 547-553, 2020.

- A.B. Renz, V.A. Shah, O.J. Vavasour, Y. Bonyadi, G.W.C. Baker, F. Li, T. Dai, M. Walker, P.A. Mawby, and P.M. Gammon, "Surface effects of passivation within Mo/4H-SiC Schottky diodes through MOS analysis", Materials Science Forum, vol. 963, pp. 511-515, 2019.

#### List of co-authored conference publications

- T. Dai, L. Zhang, O.J. Vavasour, A.B. Renz, Q. Cao, V.A. Shah, P.A. Mawby, M. Antoniou, P.M. Gammon, "A Compact and Cost-efficient Edge Termination Design for High Voltage 4H-SiC Devices", 33<sup>rd</sup> International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 251-254, 2021.

- T. Dai, A.B. Renz, L. Zhang, O.J. Vavasour, G.W.C. Baker, V.A. Shah, P.A. Mawby, and P.M. Gammon, "Design and Optimisation of Schottky Contact Integration in a 4H-SiC Trench MOSFET", *Materials Science Forum*, vol. 1004, pp. 808-813, 2020.

- G.W.C. Baker, C. Chan, T. Dai, A.B. Renz, F. Li, V.A. Shah, P.A. Mawby, and P.M. Gammon, "Study of 4H-SiC Superjunction Schottky rectifiers with implanted p-pillars", *Materials Science Forum*, vol. 963, pp. 539-543, 2019.

#### List of oral presentations

- A. B. Renz, V.A. Shah, Y. Bonyadi, F. Li, G.W.C. Baker, P.A. Mawby, and P.M. Gammon, "Surface effects of passivation within Mo/4H-SiC Schottky diodes through MOS analysis", oral presentation at *European Materials Research Society Fall Meeting 2018*, Warsaw, Poland.

- A.B. Renz, V.A. Shah, O.J. Vavasour, Y. Bonyadi, G.W.C. Baker, F. Li, T. Dai, M. Walker, P.A. Mawby, and P.M. Gammon, "Development of high-quality gate oxide on 4H-SiC using atomic layer deposition, accepted for oral presentation at

*European Materials Research Society Spring Meeting 2020*, Strasbourg, France, cancelled due to the pandemic.

#### Abstract

The very nature of the wide bandgap semiconductor silicon carbide (SiC), namely its high critical electric field, thermal conductivity and stable native oxide, silicon dioxide (SiO<sub>2</sub>), has enabled the design, fabrication and market penetration of a new generation of power devices, Schottky barrier diodes (SBDs) and metal-oxide-semiconductor field-effect transistors (MOSFETs), with blocking voltages from 600-1700V. Despite the successful commercial realisation of these devices, the surface of SiC and the interfaces it forms with metals (Schottky interface) and insulators (MOS interface), are still the source of reliability problems such as premature breakdown and decreased lifetime of gate oxides on SiC.

The focus of this thesis lies on the exploration of passivation approaches to the Schottky interface as well as the investigation of the quality of deposited gate oxides. Firstly, an electrical and physical analysis of the impact of a proposed phosphorous pentoxide ( $P_2O_5$ ) treatment on planar and optimised 3.3 kV JBS diodes reveals a reduction of Schottky barrier height as well as leakage current, offering a possible path to overcome the basic trade-off between on-state and off-state performance of a diode.

The second part of the thesis focuses on atomic layer deposition (ALD) – deposited SiO<sub>2</sub> layers, where a post-deposition annealing (PDA) study reveals the performance improvement when a PDA in forming gas ambient at 1100°C is carried out. This process was then successfully transferred and validated on freestanding 3C-SiC material, which successfully demonstrated the general suitability of this material for power device applications.

## List of Abbreviations

| AFM                            | Atomic Force Microscopy                  |

|--------------------------------|------------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | Aluminium oxide                          |

| ALD                            | Atomic layer deposition                  |

| BDEAS                          | Bis(diethylamino)silane                  |

| BPD                            | Basal plane dislocation                  |

| C <sub>2</sub> H <sub>4</sub>  | Ethylene                                 |

| C <sub>3</sub> H <sub>8</sub>  | Propane                                  |

| C-V                            | Capacitance-voltage                      |

| CVD                            | Chemical vapour deposition               |

| DLTS                           | Deep-level transient spectroscopy        |

| EDMR                           | Electrically detected magnetic resonance |

| EDX                            | Energy-dispersive x-ray analysis         |

| e-mode                         | Enhancement-mode                         |

| ESR                            | Electron spin resonance                  |

| EV                             | Electric vehicle                         |

| FE                             | Field emission                           |

| FIB                            | Focussed ion beam                        |

| FWHM                           | Full-width-half-maximum                  |

| Ga <sub>2</sub> O <sub>3</sub> | Gallium oxide                            |

| GaAs                           | Gallium arsenide                         |

| GaN                            | Gallium nitride                          |

| GaP                            | Gallium phosphide                        |

| Ge                             | Germanium                                |

| H <sub>2</sub>                 | Hydrogen                                 |

| HCl <sub>3</sub> Si           | Trichlorosilane                                      |

|-------------------------------|------------------------------------------------------|

| HEMT                          | High electron mobility transistor                    |

| HVDC                          | High-voltage direct current                          |

| IGBT                          | Insulated-gate bipolar transistor                    |

| InAs                          | Indium arsenide                                      |

| InP                           | Indium phosphide                                     |

| InSb                          | Indium antimonide                                    |

| JBS                           | Junction barrier Schottky                            |

| LED                           | Light emitting diode                                 |

| LPCVD                         | Low pressure chemical vapour deposition              |

| MOS                           | Metal-oxide-semiconductor                            |

| MOSCAP                        | Metal-oxide-semiconductor capacitor                  |

| MOSFET                        | Metal-oxide-semiconductor field-effect<br>transistor |

| MPS                           | Merged PiN Schottky                                  |

| Ν                             | Nitrogen                                             |

| OBC                           | On-board charger                                     |

| P <sub>2</sub> O <sub>5</sub> | Phosphorous pentoxide                                |

| Pb                            | Si dangling bond                                     |

| P <sub>bC</sub>               | Carbon dangling bond                                 |

| PDA                           | Post-deposition anneal                               |

| РОА                           | Post-oxidation anneal                                |

| RMS                           | Root-mean square value                               |

| SBD                           | Schottky barrier diode                               |

| SBH                           | Schottky barrier height                              |

| SEM                           | Scanning electron microscopy                         |

| Si                              | Silicon                             |

|---------------------------------|-------------------------------------|

| SiC                             | Silicon carbide                     |

| SiGe                            | Silicon germanium                   |

| SiH4                            | Silane                              |

| SIMS                            | Secondary ion mass spectrometry     |

| SiO <sub>2</sub>                | Silicon dioxide                     |

| SiP <sub>2</sub> O <sub>7</sub> | Silicon diphosphate                 |

| TDDB                            | Time-dependent dielectric breakdown |

| TE                              | Thermionic emission                 |

| TED                             | Threading edge dislocation          |

| TEM                             | Transmission electron microscopy    |

| TEOS                            | Tetraethyl orthosilicate            |

| TFE                             | Thermionic field emission           |

| ТМА                             | Trimethylaluminium                  |

| ТоА                             | Take-off angle                      |

| TSD                             | Threading screw dislocation         |

| UPS                             | Uninterruptable power supply        |

| XPS                             | X-ray photoelectron spectroscopy    |

| XRD                             | X-ray diffraction                   |

## List of Variables and Symbols

| А               | Device area                     |

|-----------------|---------------------------------|

| A               | Effective Richardson's constant |

| BE              | Binding energy                  |

| C <sub>FB</sub> | Flatband capacitance            |

| C <sub>IT</sub>    | Capacitance of interface traps          |

|--------------------|-----------------------------------------|

| CIT                | Capacitance of interface traps          |

| C <sub>OX</sub>    | Oxide capacitance                       |

| Cs                 | Semiconductor capacitance               |

| dI/dt              | Current fall/rise rate                  |

| D <sub>IT</sub>    | Density of interface trapped charge     |

| D <sub>MC</sub>    | Mobile charge areal density             |

| E <sub>00</sub>    | Tunneling energy of the semiconductor   |

| E <sub>C</sub>     | Conduction band                         |

| Ecrit              | Critical electric field                 |

| Espectr.           | Measured energy of the detected/ejected |

|                    | electrons.                              |

| ET                 | Trap level energy position              |

| Ev                 | Valence band                            |

| E <sub>X-ray</sub> | X-ray energy (h*v)                      |

| G <sub>M</sub>     | Measured conductance                    |

| Gp                 | Parallel conductance                    |

| ħ                  | Reduced Planck's constant               |

| I <sub>RR</sub>    | Reverse recovery current                |

| J                  | Current density                         |

| J <sub>R</sub>     | Leakage current density                 |

| J <sub>S</sub>     | Saturation current                      |

| k                  | Boltzmann's constant                    |

| m*                 | Tunnelling effective mass               |

| m <sub>0</sub>     | Effective electron rest mass            |

|                    |                                         |

| N <sub>D</sub>      | Drift-region dopant concentration  |  |  |  |

|---------------------|------------------------------------|--|--|--|

| N <sub>F</sub>      | Quantity of fixed charge           |  |  |  |

| n <sub>i</sub>      | Intrinsic carrier concentration    |  |  |  |

| N <sub>IT</sub>     | Number of interface trapped charge |  |  |  |

| N <sub>M</sub>      | Quantity of mobile oxide charge    |  |  |  |

| N <sub>OT</sub>     | Number of oxide trapped charge     |  |  |  |

| Q                   | Electron charge                    |  |  |  |

| Q <sub>F</sub>      | Fixed oxide charge                 |  |  |  |

| QIT                 | Interface trapped charge           |  |  |  |

| Q <sub>M</sub>      | Mobile oxide charge                |  |  |  |

| Qот                 | Oxide trapped charge               |  |  |  |

| QR                  | Extracted charge                   |  |  |  |

| R <sub>ON</sub>     | On-resistance                      |  |  |  |

| R <sub>ON</sub> ,sp | Specific on-resistance             |  |  |  |

| Т                   | Absolute temperature               |  |  |  |

| toff                | Off-time                           |  |  |  |

| t <sub>ON</sub>     | On-time                            |  |  |  |

| V                   | Applied bias, Voltage              |  |  |  |

| V <sub>B</sub>      | Breakdown voltage                  |  |  |  |

| V <sub>BI</sub>     | Built-in potential                 |  |  |  |

| V <sub>F</sub>      | Forward voltage drop               |  |  |  |

| V <sub>FB</sub>     | Flatband voltage                   |  |  |  |

| V <sub>R</sub>      | Reverse bias                       |  |  |  |

| Wg                  | Bandgap                            |  |  |  |

| $\Delta V_{FB}$    | Hysteresis voltage                       |

|--------------------|------------------------------------------|

| η                  | Ideality factor                          |

| λ                  | Thermal conductivity                     |

| μn                 | Electron mobility                        |

| σ                  | Surface potential fluctuation            |

| τ <sub>IT</sub>    | Time constant of the interface trap      |

| $\phi^{0}{}_{B,n}$ | Theoretical maximum metal-               |

|                    | semiconductor barrier height without     |

|                    | consideration of effects such as barrier |

|                    | height lowering                          |

| Фвл                | Barrier height                           |

| φ <sub>M</sub>     | Difference between vacuum level and      |

|                    | Fermi level in the metal                 |

| фм                 | Potential difference between the         |

|                    | conduction band level and Fermi level    |

|                    | in the n-type doped semiconductor        |

| φs                 | Difference between vacuum level and      |

|                    | Fermi level in the semiconductor         |

| Xs                 | Semiconductor electron affinity          |

| ω                  | AC measurement frequency                 |

## List of Figures

| Figure 1.1: A schematic of a typical drivetrain in an electric vehicle with multiple           |

|------------------------------------------------------------------------------------------------|

| inverter and converter stages                                                                  |

| Figure 2.1 : Hexagonal (a) and cubic (b) SiC lattice, dark atoms represent Si and              |

| light atoms represent C atoms [7]15                                                            |

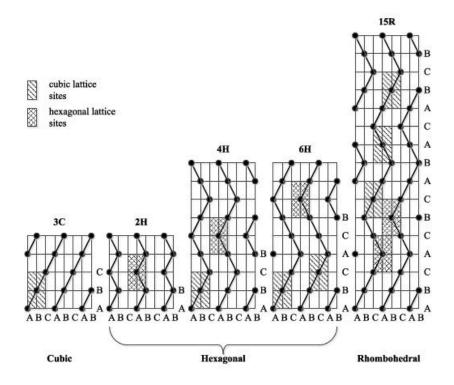

| Figure 2.2: Stacking structure of selected SiC polytypes [9]16                                 |

| Figure 2.3: The stacking layer sequence in SiC depicting the three different                   |

| occupation sites [8]16                                                                         |

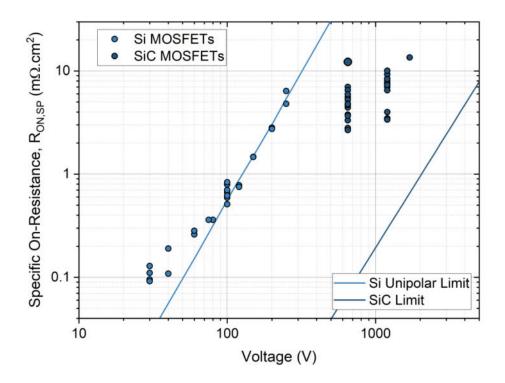

| Figure 2.4: Unipolar limit comparison of devices which were fabricated on Silicon              |

| or Silicon carbide                                                                             |

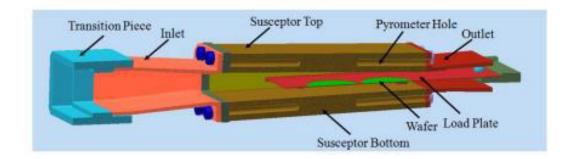

| Figure 2.5: Schematic of a typical hot-wall vertical CVD reactor, where the                    |

| substrate is located on the load plate at the centre of the reactor [13]22                     |

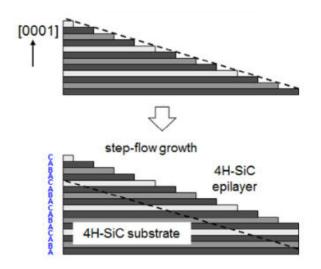

| Figure 2.6: Schematic of the step flow growth on layers grown on a 4H-SiC                      |

| substrate, from [22]                                                                           |

| Figure 2.7: Schematic of the propagation of TEDs, TSDs and BPDs and conversion                 |

| rate of these at the interface between substrate and epitaxial layer, from [22]25              |

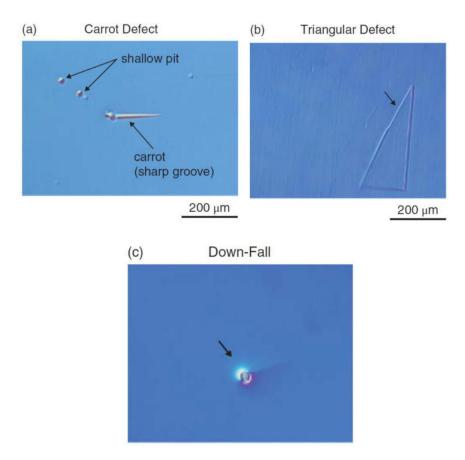

| Figure 2.8: Microscopic images of the carrot defect, triangular defect and downfall            |

| defect in the epitaxial layers, from [22]                                                      |

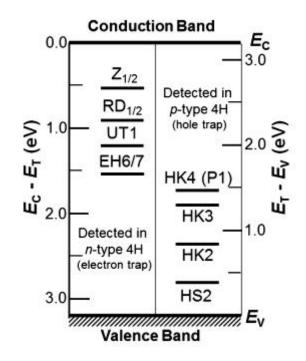

| Figure 2.9: Major deep levels in 4H-SiC epitaxial layers, when they are grown 4°               |

| off-axis, from [22]                                                                            |

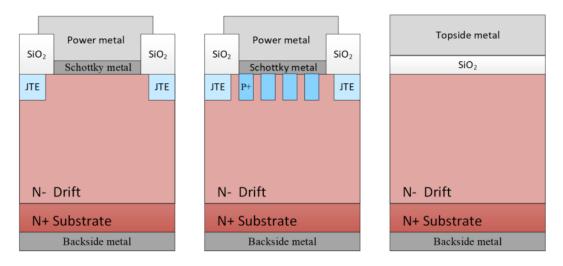

| Figure 2.10: Cross-sectional view of the described device structures Schottky barrier          |

| diode (left), merged pin Schottky or junction barrier Schottky (middle) and metal-             |

| oxide-semiconductor capacitor (right)                                                          |

| Figure 2.11: The Schottky metal-semiconductor interface involving a moderately                 |

| lowly n-doped semiconductor. (Top) The interface instantly after connection at t=0,            |

| prior to a steady-state, and (bottom) after the formation of a depletion region, with $\chi$ s |

| – the semiconductor electron affinity, $\phi_S$ – Difference between vacuum level and          |

| Fermi level in the semiconductor, $\phi_M$ – Difference between vacuum level and Fermi         |

| level in the metal, $\phi^0_{B,n}$ – theoretical maximum metal-semiconductor barrier height    |

| without consideration of effects such as barrier height lowering, $E_C$ and $E_V$ -            |

| conduction band and valence band, respectively, and $\phi_N$ – the potential difference        |

| between the conduction band level and Fermi level in the n-type doped                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| semiconductor                                                                                                                               |

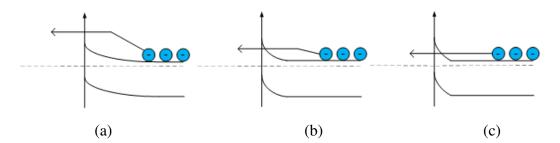

| Figure 2.12: Band diagram schematic of the three dominant current transport                                                                 |

| mechanisms (a) thermionic emission, (b) thermionic field emission and (c) field                                                             |

| emission                                                                                                                                    |

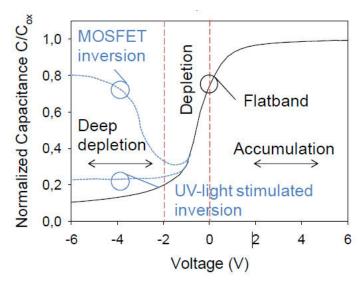

| Figure 2.13: Schematic representation of an ideal C-V response of an n-type SiC                                                             |

| MOSCAP (black), showing the accumulation, flatband and deep depletion section,                                                              |

| from [33]                                                                                                                                   |

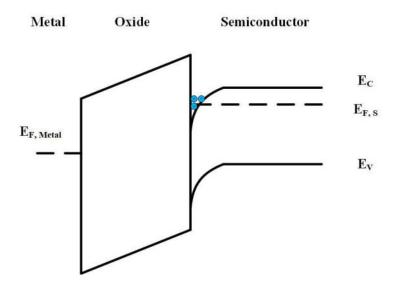

| Figure 2.14: Band diagram of an n-type 4H-SiC MOSCAP in accumulation38                                                                      |

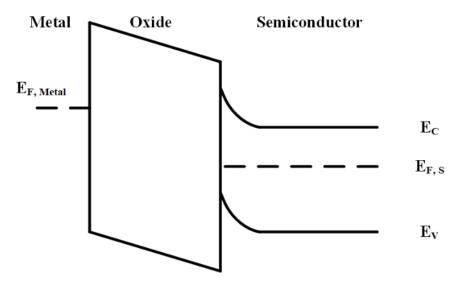

| Figure 2.15: Band diagram of an n-type 4H-SiC MOSCAP in depletion                                                                           |

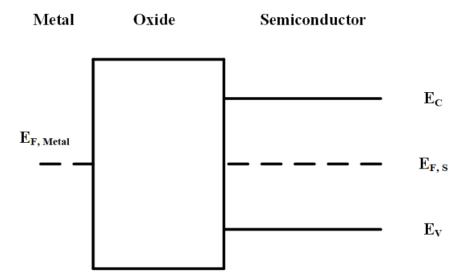

| Figure 2.16: Band diagram of an n-type 4H-SiC MOSCAP in flatband mode40                                                                     |

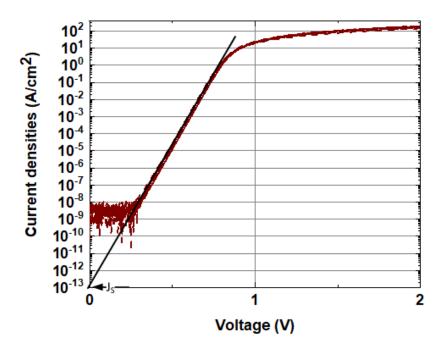

| Figure 2.17: Logarithmic current trace of a typical n-type 4H-SiC SBDs in the on-                                                           |

| state with $J_S$ – Saturation current density and the ideality factor and SBH extraction                                                    |

| method indicated                                                                                                                            |

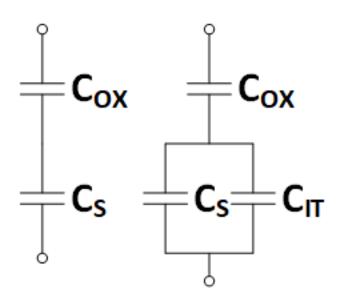

| Figure 2.18: Equivalent circuit of the ideal MOSCAP (left) and the circuit used for                                                         |

| the high-low technique                                                                                                                      |

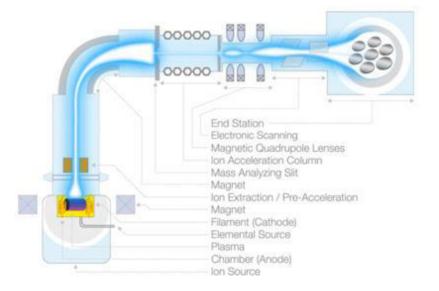

| Figure 2.19: Simplified schematic of a SIMS rig [37]49                                                                                      |

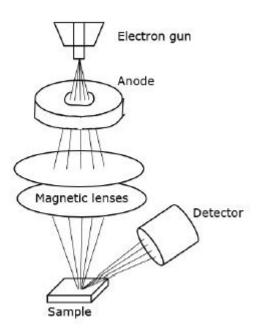

| Figure 2.20: Simplified schematic of a scanning electron microscope, from rig [38].                                                         |

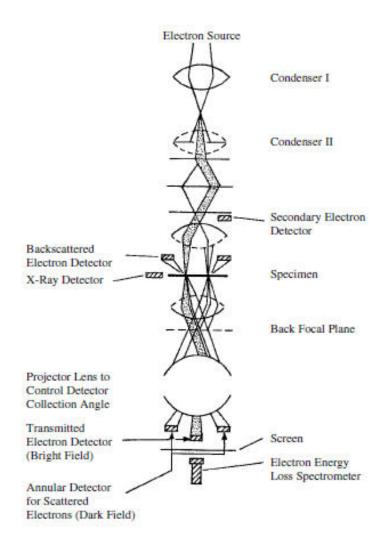

| Figure 2.21: Simplified schematic of a transmission electron microscope, from [30].                                                         |

|                                                                                                                                             |

| as the Schottky contact metal. The Schottky contact area is $4.39 \times 10^{-4}$ cm <sup>2</sup> 63                                        |

| <b>Figure 3.2:</b> Typical on-state I-V characteristics (a) of the Schottky diodes, measured                                                |

| at 22 °C. SBH and ideality factors (b) for these diodes at room temperature as well.                                                        |

|                                                                                                                                             |

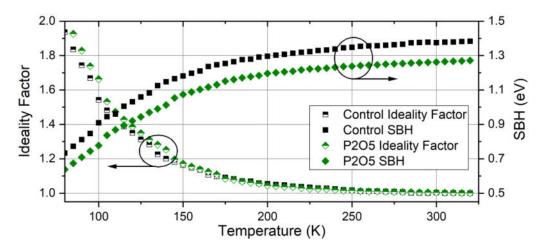

| Figure 3.3: SBH and ideality factors for a typical control and P2O5-treated diode                                                           |

| from 80 to 320 K                                                                                                                            |

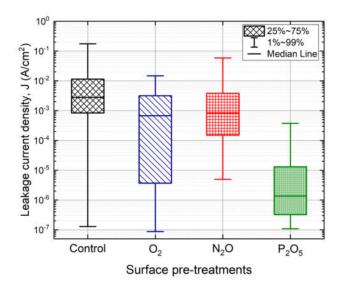

| <b>Figure 3.4:</b> Diode leakage current characteristics at $VR = 500 V$ , measured at $22^{\circ}C$ .                                      |

| Median values are represented due to the logarithmic scale                                                                                  |

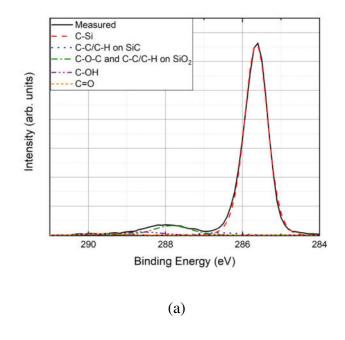

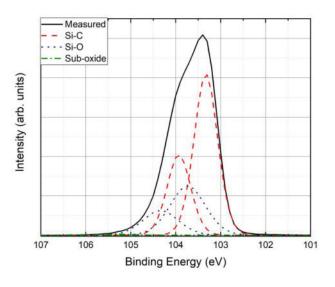

| Figure 3.5: XPS data and fits for the (a) C 1s region, (b) Si 2p region without                                                             |

| surface treatment                                                                                                                           |

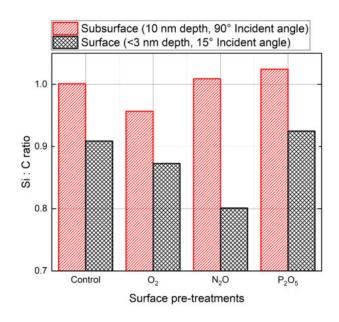

| Figure 3.6: Si:C ratio of the investigated samples at different surface depth71                                                             |

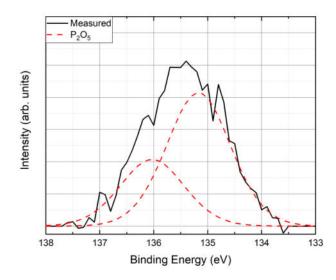

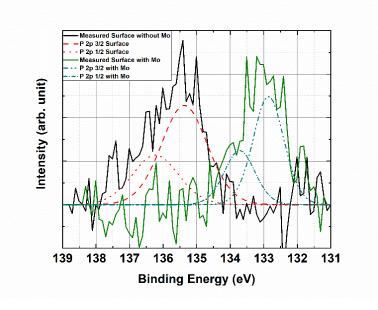

| <b>Figure 3.7:</b> P 2p region showing a P <sub>2</sub> O <sub>5</sub> peak for the P <sub>2</sub> O <sub>5</sub> -treated sample <b>72</b> |

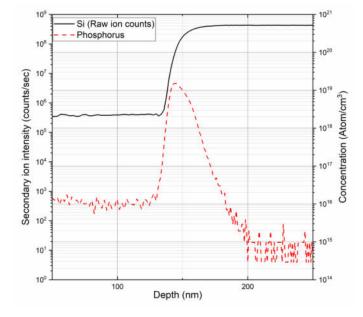

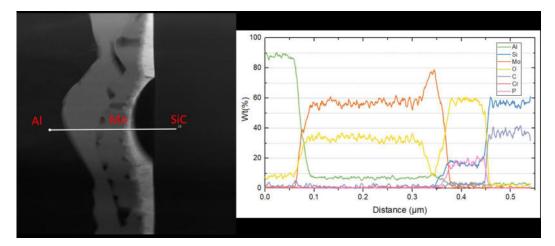

| Figure 3.8: SIMS results for the P2O5-treated sample.    73                                                 |

|-------------------------------------------------------------------------------------------------------------|

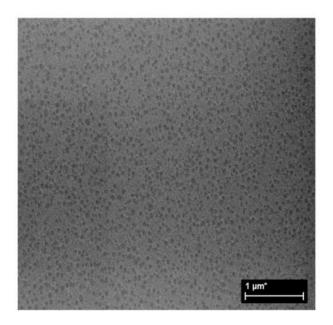

| Figure 3.9: SEM images of (a) a P <sub>2</sub> O <sub>5</sub> -treated sample and (b) an untreated control  |

| sample with a 1 µm and 200 nm scan size, respectively75                                                     |

| Figure 3.10: AFM images of (a) a P <sub>2</sub> O <sub>5</sub> -treated sample and (b) an untreated control |

| surface with a $5 \times 5 \mu m^2$ scan size                                                               |

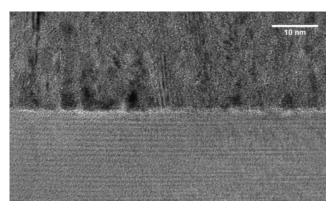

| Figure 3.11: HRTEM images of the Mo/SiC interface of (a) the P <sub>2</sub> O <sub>5</sub> -treated and (b) |

| the untreated control SBD and (c) EDX linescan through a Schottky diode sample                              |

| that had undergone a more dilute HF dip (1ml HF:100ml H2O) to further investigate                           |

| the observed decorations78                                                                                  |

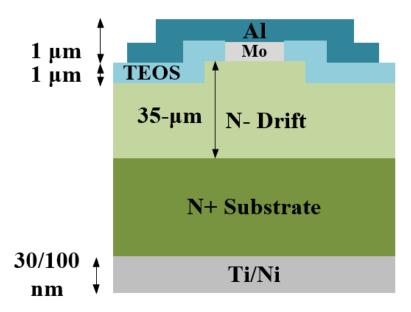

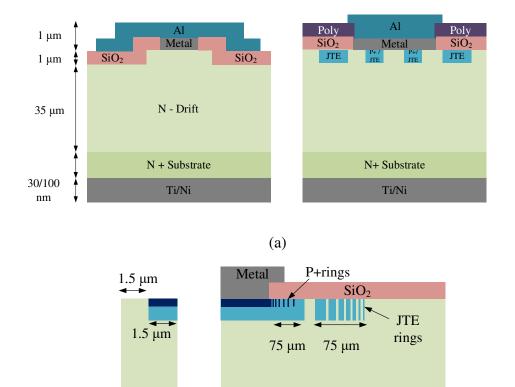

| Figure 4.1: (a) left: Cross-section of the fabricated unterminated Schottky diodes and                      |

| right: Cross-section of the fabricated 3.3 kV JBS diodes. 89                                                |

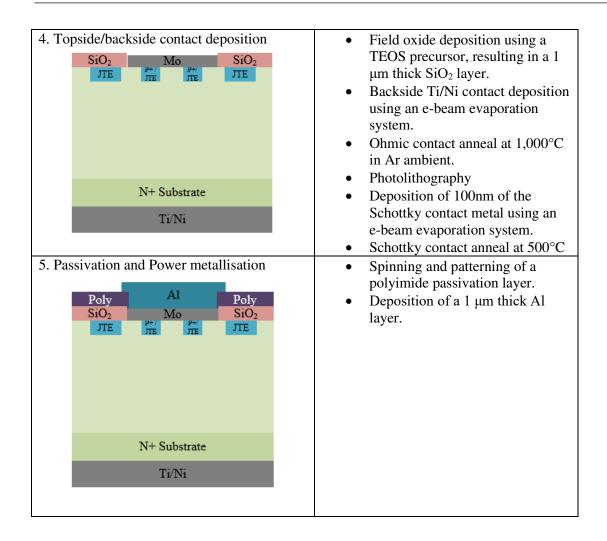

**Figure 4.2:** (a) Ideality factors and work functions (b) over SBHs for the Schottky diodes, measured between  $1 \times 10^{-7}$  and 10 A cm<sup>-2</sup>. (b) Leakage current densities of more than 100 devices each, measured at -200 V, for a device area of  $4.39 \times 10^{-4}$  cm<sup>2</sup>.

#### 92

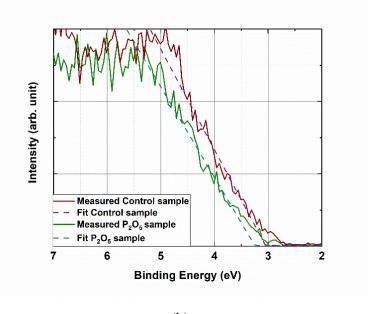

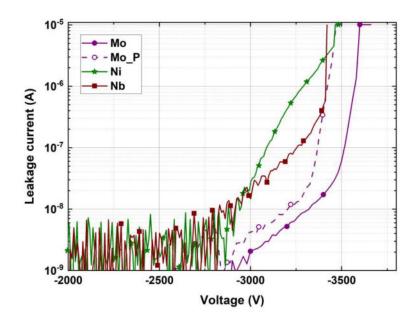

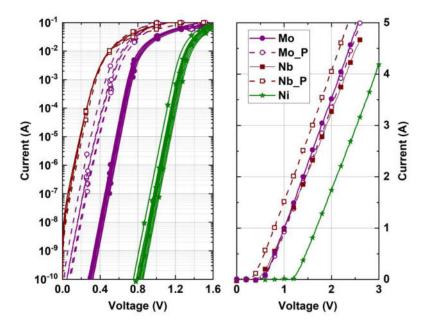

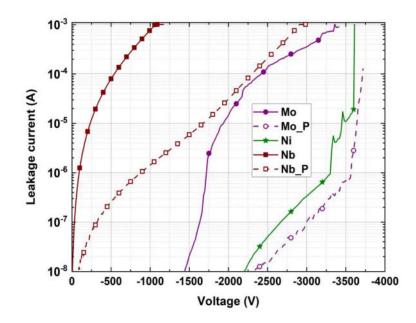

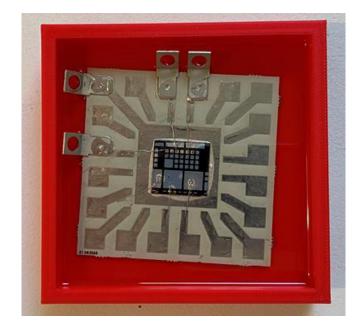

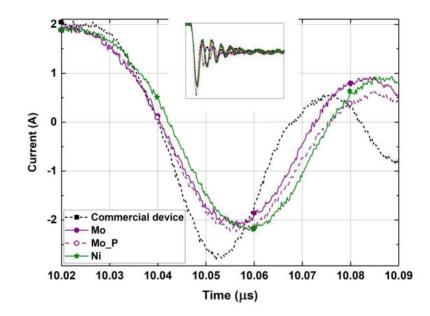

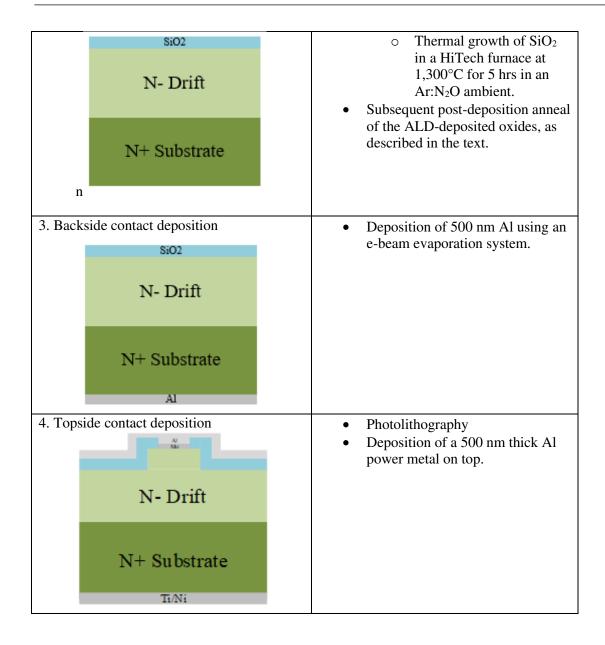

Figure 4.3:(a) P2p region showing a P2O5 peak for the P2O5-treated bare surface and for a Schottky sample with a 3-4nm Mo layer. (b) Valence band extraction for a **Figure 4.4:** Leakage current measurement on PiN diodes (are is 1.56 mm<sup>2</sup>) at room Figure 4.5: left, the exponential turn-on characteristics of the small JBS diodes (active area of  $1.56 \text{ mm}^2$ ). These results were used for the extraction of barrier heights and ideality factors (extracted for current values between  $1 \times 10^{-7}$  and 10 A.cm<sup>-2</sup>) at room temperature. Right, static on-state characteristics of the large JBS Figure 4.6: Leakage current measurements, up to 3800V. Measurements were Figure 4.7: Circuit diagram of the clamped inductive switching rig with  $V_{DC} - DC$ power supply,  $R_G$  – gate resistor,  $I_G$  – gate current,  $L_C$  – Inductor......100 Figure 4.8: Chip prototype package for the double-pulse switching test. The substrate of the bare die was connected to the IMS board using conductive silver paste. The terminals were soldered onto the board after wire bonding. Then, the

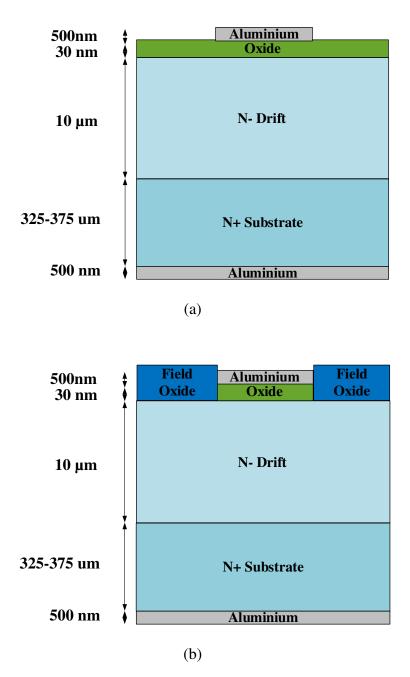

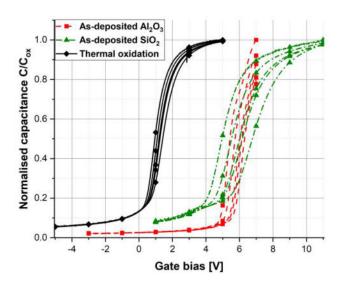

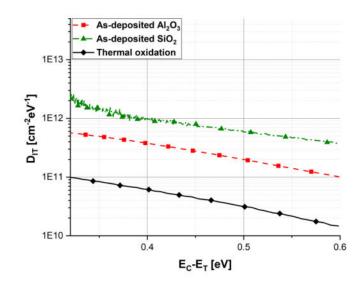

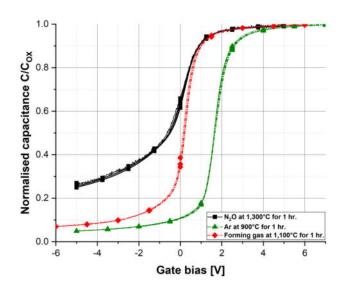

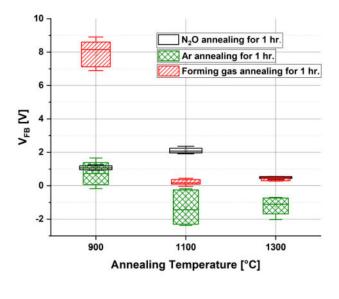

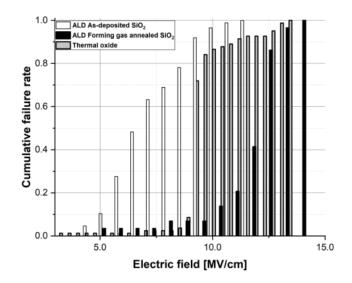

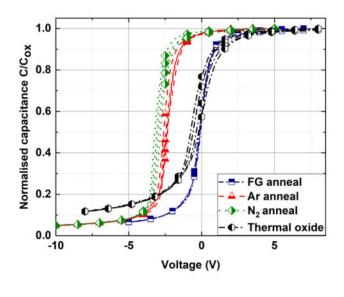

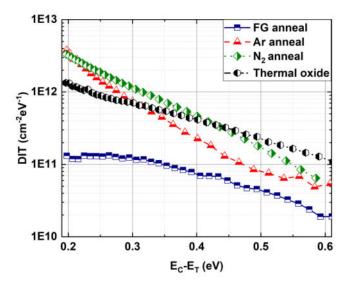

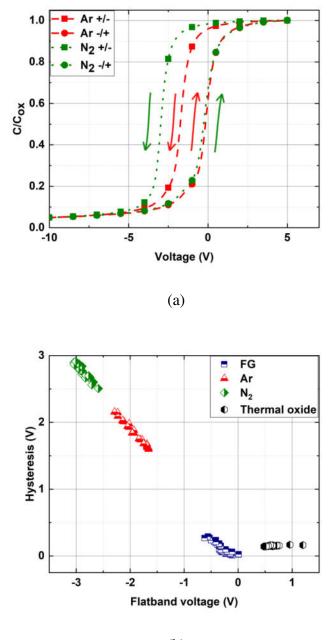

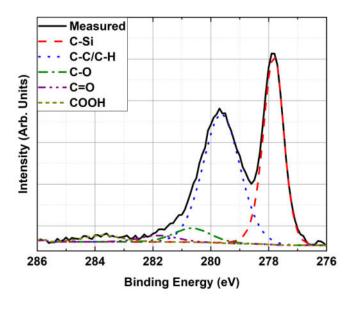

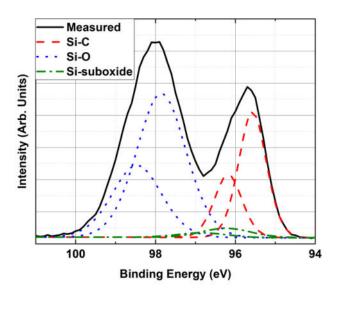

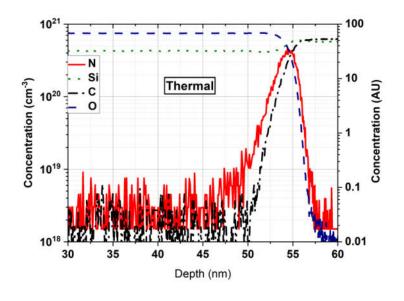

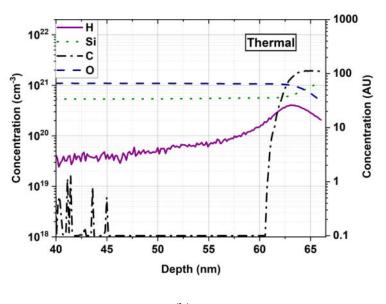

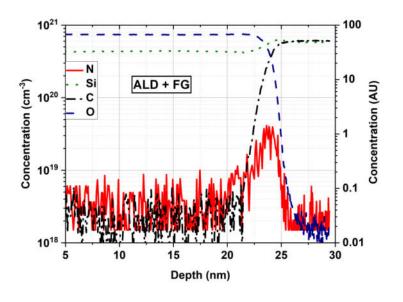

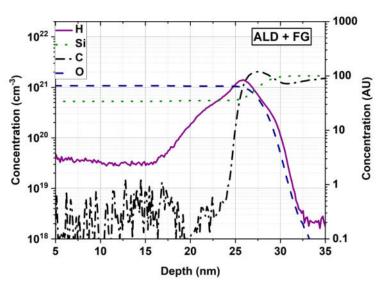

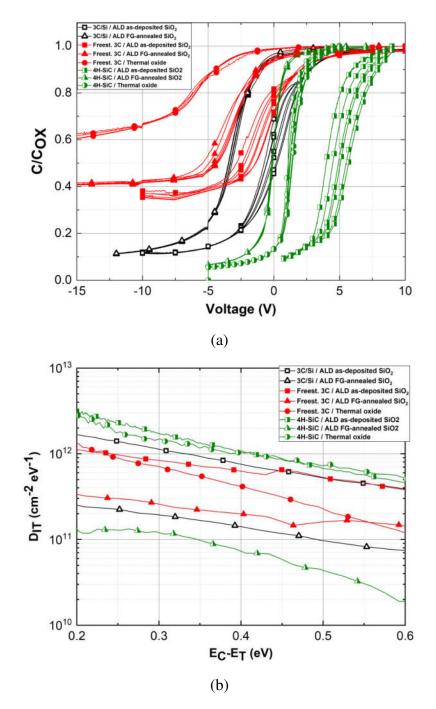

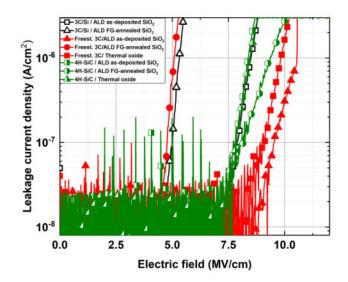

Figure 5.1: Cross section schematic diagram of (a) fabricated MOSCAPs used for Figure 5.2: (a) Representative C-V response of as-deposited layers and (b) their density of interface traps......116 Figure 5.3: (a) Typical C-V response of best annealed samples for each ambient and (b) the distribution of flatband voltages after PDAs at different temperatures and Figure 5.4: The breakdown distribution of MOSCAPs, measured at room Figure 5.5: (a) Capacitance-voltage (1 kHz, 10 kHz, 100 kHz, 1 MHz), normalised to the oxide capacitance, of annealed ALD-deposited and thermally oxidised samples and (b) D<sub>IT</sub> with respect to the energy trap level E<sub>T</sub> below the conduction band level Figure 5.6: (a) Hysteresis C-V response of Ar and N2 annealed samples at 1 MHz. Samples were swept from accumulation to deep depletion and backwards. (b) Hysteresis voltage plotted over flatband voltage for 50 MOSCAPs per different Figure 5.7: XPS data and fits for the (a) C 1s region and (b) Si 2p region of the ALD Figure 5.8: SIMS profiles of nitrogen (a) and hydrogen (b) in the thermally oxidised sample. The sample had a grown SiO<sub>2</sub> layer on top of the semiconductor, profiles are shown for the whole of the oxide and the first 5-10nm of the semiconductor. H and N are quantified with absolute values, Si, C and O with arbitrary units......130 Figure 5.9: SIMS profiles of nitrogen (a) and hydrogen (b) in the FG-annealed ALD-deposited sample. The sample had a deposited SiO<sub>2</sub> layer on top of the semiconductor, profiles are shown for the whole of the oxide and the first 5-10nm of the semiconductor. H and N are quantified with absolute values, Si, C and O with

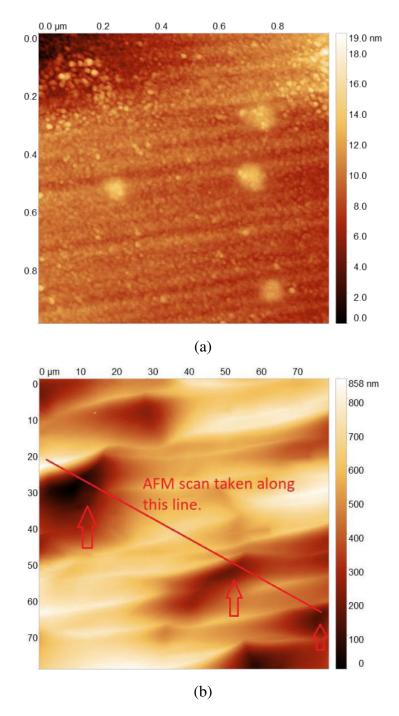

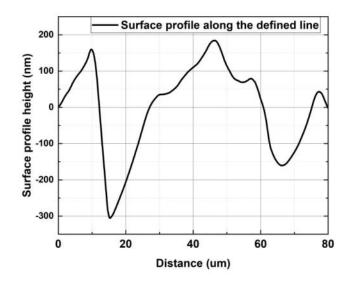

| Figure 6.1: (a) Atomic force microscopy images of freestanding 3C-SiC samples                                    |

|------------------------------------------------------------------------------------------------------------------|

| with with 1 $\mu$ m x 1 $\mu$ m (a) and 80 $\mu$ m x 80 $\mu$ m (b) scan sizes141                                |

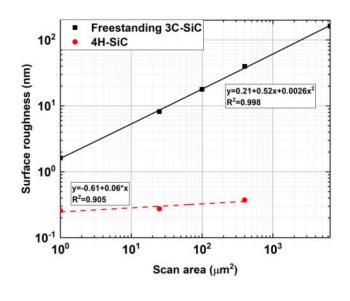

| Figure 6.2: (a) Plot of surface roughness over scan area (c) with includes a 4H-SiC                              |

| sample as well. The surface profile in image (b) was extracted the line in figure 6.1                            |

| (b), starting from the top left corner down to the bottom right corner142                                        |

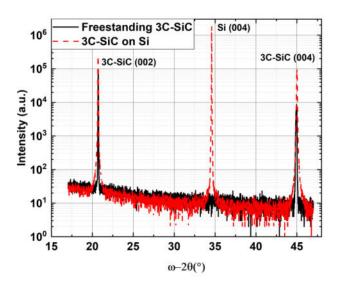

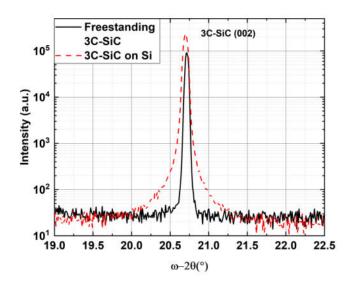

| <b>Figure 6.3:</b> $\omega$ -2 $\theta$ XRD scans (rocking curves) depicting (a) the full XRD spectrum           |

| and the (b) 3C-SiC (002) region for a freestanding 3C-SiC and a 3C-SiC on Si                                     |

| samples144                                                                                                       |

| Figure 6.4: Normalised capacitance-voltage curves for each dataset (a) and the                                   |

| respective $D_{TT}$ curves (b). The device area is 8.04 x 10 <sup>-4</sup> cm <sup>2</sup> . For thermal and 4H- |

| SiC oxides, the device area is $3.14 \times 10^{-4} \text{ cm}^2$ 147                                            |

| <b>Figure 6.5:</b> Leakage current measurements. The device area is $8.04 \times 10^{-4} \text{ cm}^2$ . For     |

| thermal and 4H-SiC oxides, the device area is $3.14 \times 10^{-4} \text{ cm}^2$ <b>148</b>                      |

#### **List of Tables**

**Table 1.1**: The material properties of Si and selected wide bandgap semiconductors at 300 K [12, 14-16], where  $W_g$  – bandgap (eV),  $E_{crit}$ , critical electric field (MV/cm),  $n_i$  – intrinsic carrier concentration (cm<sup>-3</sup>),  $\lambda$  – thermal conductivity (W/cm.K), elec. sat. velocity–electron saturation velocity (cm.s<sup>-1</sup>), $\mu_n$  – electron mobility (cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup>). **Table 2.1:** A summary of the main electrical properties of Si, the most important polytypes of SiC and wurtzite GaN at 300 K [1]. Given the rarity of c-GaN and ubiquity of w-GaN, the wurtzite polytype is commonly referred to simply as 'GaN', and it can be assumed that the wurtzite polytype is being considered unless stated

otherwise. 17

**Table 2.2:** Overview of used characterisation techniques in the course of this thesis.

55

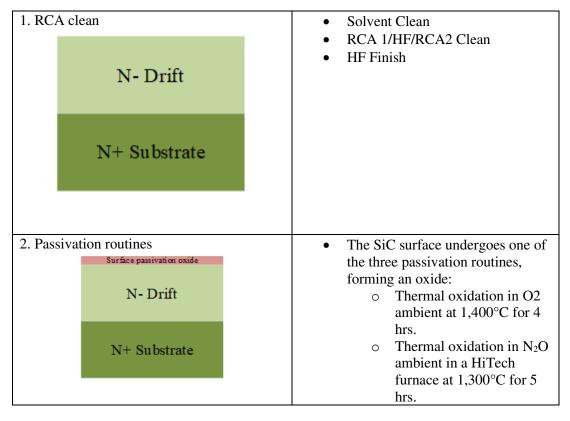

| <b>Table 3.1:</b> Process flow for the fabrication of the Schottky barrier diodes                |

|--------------------------------------------------------------------------------------------------|

| Table 3.2: Summary of measured ideality factors, barrier heights, and reverse                    |

| leakage currents of the as-grown and treated samples. All measurements were carried              |

| out at room temperature. Mean values are provided with standard deviations67                     |

| Table 3.3: Summary of measured defect densities of the as-grown and treated                      |

| samples. 80                                                                                      |

| <b>Table 4.1:</b> Process flow for the fabrication of 3.3 kV 4H-SiC JBS devices. <b>90</b>       |

| Table 4.2: Summary of measured barrier heights (average), ideality factors (average)             |

| and leakage current (median) measured at -200 V. Device area for leakage current                 |

| measurements is $4.38 \times 10^{-4} \text{ cm}^2$                                               |

| Table 4.3: Summary of measured barrier heights (average), ideality factors (average)             |

| and leakage current (typical)) measured at 1 $\mu A$ for 1.56 $mm^2$ JBS diodes. $R_{ON,SP}$ for |

| 42.25 mm <sup>2</sup> JBS diodes                                                                 |

| Table 5.1: Process flow for the MOSCAP fabrication                                               |

| <b>Table 5.2:</b> Flatband voltage, hysteresis and frequency dispersion of the ALD SiO2          |

| MOSCAPs, after PDA. All values are given with standard deviations. 16 devices                    |

| were measured for each annealing condition117                                                    |

| <b>Table 5.3:</b> Flatband voltage, hysteresis and frequency dispersion of the ALD SiO2                  |

|----------------------------------------------------------------------------------------------------------|

| MOSCAPs, after PDA. All values are given with standard deviations. 16 devices                            |

| were measured for each annealing condition122                                                            |

| <b>Table 5.4:</b> Density of mobile charge states from 25 samples each with a device area                |

| of $1.257 \times 10^{-3}$ cm <sup>2</sup> . Values are average values provided with standard deviations. |

|                                                                                                          |

| Table 5.5: SIMS results: peak interfacial concentration of H and N.       129                            |

| Table 6.1: Summary of measured flatband voltage, hysteresis and frequency                                |

| dispersion of 16 samples per category, with a device area of 8.04 x $10^{-4}$ cm <sup>2</sup> . For      |

| thermal and 4H-SiC oxides, the device area was $3.14 \times 10^{-4} \text{ cm}^2$ . <b>149</b>           |

#### **Chapter 1: 1 Introduction**

This thesis is focused on the surface of the wide bandgap semiconductor material silicon carbide (SiC) and the interfaces it forms with metals (Schottky interface) and insulators (MOS interface). In particular, it aims to provide insights into surface conditioning procedures and their impact on the quality of Schottky interfaces. Secondly, it aims to create a robust understanding on how to form good quality insulator/SiC interfaces by means of insulator deposition techniques. Post-deposition treatments of the deposited insulator, which have shown to produce high-quality interfaces on other materials such as silicon (Si), have been tailored to the SiC material. The most promising treatments were then further investigated to highlight one possible path to high quality interfaces on SiC. The progress made on these insulated layers will make possible transistors, metal-oxide-semiconductor field-effecttransistor (MOSFETs), that are more reliable and have fewer losses when they are switched. In combination with the improved Schottky diodes, this would lead to power electronic converter solutions with reduced losses and hence increased efficiency.

#### **1.1 SEMICONDUCTOR APPLICATIONS OVERVIEW**

Despite significant setbacks due to the two World Wars, the electronics technology has changed people's lives across the globe during the twentieth century at an unprecedented extent and speed, with this trend continuing since the turn of the millennium. Today's electronics applications cover a wide range, from low-power consumer electronics such as smart phones, up to high-voltage direct current (HVDC) grid level converters. Since all of these applications require different operating

conditions, the electronic device engineering has always played a critical role in the electronics hierarchy, covering device structure design, fabrication and choice of semiconductor materials. These semiconductor materials and their key parameters - bandgap energy, charge carrier mobility, saturation velocity, critical electric field and thermal conductivity - determine the device's performance in the applications.

For the past decades, Si has been the dominant semiconductor device shaping the semiconductor market through its availability on large wafer diameters with extremely low material defects and its reliable oxide, silicon dioxide (SiO<sub>2</sub>), leaving only marginal market niches for other semiconductor materials such as germanium (Ge), gallium arsenide (GaAs), gallium nitride (GaN), and silicon carbide (SiC). As of 2018, 87 % of the devices within the power semiconductor market were still based on Si [1].

#### 1.1.1 APPLICATION SPACE FOR OTHER SEMICONDUCTOR MATERIALS

The most influential semiconductor material parameter is the bandgap energy, since this correlates with most other parameters such as critical electric field, intrinsic carrier concentration, which directly dictate the suitability of a material for a defined application. Germanium, indium arsenide (InAs) and indium antimonide (InSb), all being narrow bandgap semiconductors, can mostly be found in low-power applications such as photodetectors in the infrared radiation detection, due to their ability to detect and emit photons in this spectrum. Opposite to this, wide band gap semiconductors such as SiC and GaN are suitable for high power applications, such as power converters for automotive applications and, in the case of silicon carbide, even for ultrahigh voltage applications (> 5 kV) such as traction, static var compensation and high-voltage direct current (HVDC) [2-4]. The wide bandgap semiconductor material SiC will be the focus of this thesis.

#### 1.1.2 THE USE OF WIDE BANDGAP SEMICONDUCTOR DEVICES

The very nature of the wide bandgap enables devices fabricated on wide bandgap semiconductor materials such as SiC and GaN to withstand much higher electric fields, on the order of ten times higher, than Si [5]. Their good thermal conductivity also allows the use of devices at higher temperature, such as at 100°C in the car engine bay. Given that wide bandgap semiconductor devices have a much higher critical electric field than conventional devices, electronic device designers have the chance to either block a significantly higher voltage for the same device dimensions or reducing the thickness of the device by the same ratio, allowing for the resistance to be scaled down. The combination of the advantages allows for the use in power conversion [4, 6], automotive converters [5, 7], ultra-high frequency and space applications [8-10].

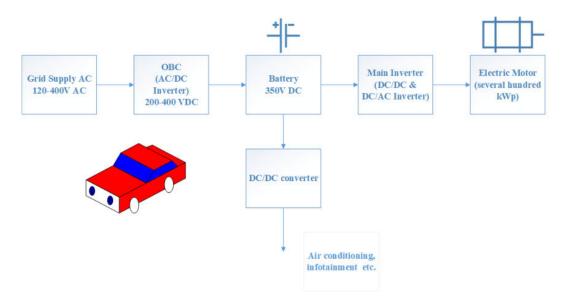

The potential benefits of using power semiconductor devices in applications become obvious when the powertrain in electric vehicles (EVs) is regarded. A typical schematic of this can be seen in Fig. 1.1. It depicts the importance of power electronics devices, since there are multiple stages which need the conversion of electrical power, both in the form of DC/DC converters as well as DC/AC inverters. The most relevant of these conversion stages is, however, the main inverter stage, which converts DC currents and voltages from the battery-side side into AC power which is needed for the operation of the electrical machine, which in most cases is either an induction machine or a permanent magnet synchronous machine.

The converter or inverter topologies are based on the operation of power semiconductor devices, in particular three-terminal devices, transistors, which have been developed on very mature silicon wafers over the past five decades. To this day, the vast majority of converters/inverts use silicon-based insulated-gate bipolar transistors (IGBTs) due to its excellent reliability and low price.

In recent years, a few manufacturers of EVs have switched from using Si IGBTs to using new silicon carbide-based MOSFETs in their main inverter, starting a possible transition away from Si-based transistors to SiC-based topologies for high power applications. This trend is accompanied by the uptake of GaN transistors in low voltage/power applications, such as on-board chargers (OBCs).

Due to the material properties of SiC, which will be explained in more detail later in this chapter, manufacturers were able to scale down the size and weight of the main inverter, e.g. the main inverter stage of a Tesla Model 3 2018 weighs about 4.8 kg, compared to 11 kg in a 2019 Nissan Leaf and 8.2 kg in a 2019 Jaguar I-Pace, both of which are using Si-IGBT-based inverters[11]. In addition to this, the Tesla has a power density which is 4.4 x higher than the Nissan Leaf. The efficiency was increased

Figure 1.1 A schematic of a typical drivetrain in an electric vehicle with multiple inverter and converter stages.

up to 97% [11] using the SiC-based technology, too. Although this came at the expense of higher costs, it allowed for the manufacturing of an electrical vehicle with an extended range due to the use of wide bandgap semiconductor devices, e.g. a more efficient inverter stage and lower overall weight of the powertrain. Also, more typically, this allows for a reduction in the number of expensive and heavy batteries the car must carry for the same range. The lighter inverter and battery pack in turn make the car more efficient.

## 1.2 SEMICONDUCTOR ALLOYS AND COMPOUND SEMICONDUCTORS

The chemical composition of semiconductors is the most commonly used property to distinguish them. The vast majority of semiconductors comprise of a single chemical element, in most cases either silicon or germanium, located in group 14 of the periodic table. With Si representing the benchmark material in terms of its reliability and application relevance, Ge is a narrow bandgap material, especially used in infrared sensor applications.

The combination of two or more semiconductor elements in a solution or a compound is called an alloy[12].

Both silicon and germanium can form an alloy with each other, silicon germanium (SiGe), on which commercial products such as SiGe diodes are commercially available. Alloys can also be made with the two remaining group 14, or group IV, materials carbon and tin, to form IV-IV alloys, though most of these are unstable and near-impossible to prepare.

Often, compound semiconductors are formed when materials of different groups are used. III-V semiconductors, using elements from group 13 (e.g., Al, Ga, In) and 15 (e.g., N, P, As, Sb), include GaAs, indium phosphide (InP), gallium phosphide (GaP), and GaN, allowing bandgap engineering. From a foundational material (typically GaAs or InP), one can engineer an alloy with the desired bandgap and lattice constant (e.g., In<sub>0.53</sub>Ga<sub>0.47</sub>As, which lattice matches to InP but has a narrower bandgap). This flexibility in material properties and combinations, combined with a direct bandgap for most III-V materials, has led them to dominate in light emitting diode (LED) and photodiode applications. As a rule of thumb, the selection of materials from a lower position in the periodic table will result in a narrower bandgap and vice versa. II-VI semiconductors also exist but they occupy an even smaller niche than III-V materials and their properties will not be further discussed in this thesis.

Beyond group IV and analogous III-V and II-VI semiconductors, many other crystalline compound can be semiconducting and suitable for device fabrication. An example is gallium oxide  $(Ga_2O_3)$  – while conventionally considered an insulator, its bandgap of 4.8 eV still allows it to be used as a wide bandgap semiconductor when suitably doped.

Silicon carbide is a binary IV-IV compound semiconductor, similar to III-V semiconductors, and has a wide bandgap of 3.21 eV [13]. With its wide bandgap and related electrical parameters, such as a high critical electric field of 2-3 MV/cm, SiC is already responsible for significant improvements in the power electronics field from voltage ratings of 600 V and up.

#### **1.3 REVIEW OF WIDE BANDGAP MATERIAL DEVICES**

This brief overview of the current application space of wide bandgap devices will focus on the most industrially relevant materials: SiC, GaN and, to a lesser extent, diamond and  $Ga_2O_3$ . An overview of important material properties can be found in TABLE 1.1.

Table 1.1: The material properties of Si and selected wide bandgap semiconductors at 300 K [12, 14-16], where  $W_g$  – bandgap (eV),  $E_{crit}$ , critical electric field (MV/cm),  $n_i$  – intrinsic carrier concentration (cm<sup>-3</sup>),  $\lambda$  – thermal conductivity (W/cm.K), elec. sat. velocity–electron saturation velocity (cm.s<sup>-1</sup>), $\mu_n$  – electron mobility (cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup>)

| Semiconductor<br>Material      | Wg<br>(eV) | E <sub>crit</sub><br>(MV/cm) | n <sub>i</sub><br>(cm <sup>-3</sup> )           | λ<br>(W/cm.K) | Elec.<br>Sat.<br>Velocity<br>$(10^7.cm.$<br>$s^{-1})$ | μn<br>(cm <sup>2</sup> .V <sup>-</sup><br><sup>1</sup> .s <sup>-1</sup> ) |

|--------------------------------|------------|------------------------------|-------------------------------------------------|---------------|-------------------------------------------------------|---------------------------------------------------------------------------|

| Si                             | 1.12       | 0.2                          | 1.5 x10 <sup>10</sup>                           | 1.5           | 1                                                     | 1350                                                                      |

| 4H-SiC                         | 3.26       | 2.8                          | 8 x10 <sup>-9</sup>                             | 4.5           | 2                                                     | 720-<br>650                                                               |

| GaN                            | 3.39       | 3.75-3.3                     | 1.9 x10 <sup>-10</sup>                          | 1.3           | 2.5                                                   | 2000-<br>1000                                                             |

| Diamond                        | 5.45       | 10                           | 1.6 x10 <sup>-27</sup>                          | 20            | 2.7                                                   | 3800                                                                      |

| 3C-SiC                         | 2.36       | 1.4                          | 1.5 x 10 <sup>-1</sup>                          | 3.2           | 2                                                     | 800                                                                       |

| Ga <sub>2</sub> O <sub>3</sub> | 4.85       | 8                            | 2.6 x10 <sup>-9</sup><br>- 1 x10 <sup>-22</sup> | 0.1-0.3       | 1.8-2.0                                               | 300                                                                       |

The material properties of silicon carbide, mean that devices such as Schottky barrier diodes (SBDs) and MOSFETs can be used at a much higher voltage level. Whereas commercial Si SBDs and MOSFETs are being employed at lower voltages, their SiC counterparts have penetrated the power device market at blocking voltages from 600 V to 1700 V over the past two decades [3], possibly extending this further up to 3300 V within the next five years. SBDs and MOSFETs rely on only a single charge carrier type for operation (typically electrons). This allows them to switch quickly and efficiently, unconstrained by minority carrier generation and recombination effects, which dominate in bipolar devices. Although this comes at the expense of higher conduction losses, this does not restrict their uptake in the market for automotive power devices, with blocking voltages at around 650°V.

Furthermore, SiC devices have been used in traction applications in the railway sector, uninterruptable power supplies (UPS) [2-4] and EV applications such as inverters, on-board chargers, DC-DC converters and DC rapid chargers, and they are also are at the brink of entering into AC drives and wind applications [7], where improvements in efficiency are needed. An example of this was shown in section 1.1.2. On a non-commercial level, ultra-high voltage (>10 kV) devices have been successfully demonstrated [17-19].

Factors which limit the further uptake of SiC devices are its higher cost per wafer compared to Si, its higher density of performance deteriorating material defects such as basal plane dislocations (BPDs), threading edge dislocations (TEDs), threading screw dislocations (TSDs) [13, 20], and issues with the reliability of the insulator/SiC interface, which lower the lifetime of MOS-based devices and reduce channel mobilities [21], hence increasing the specific on-resistance  $R_{SP,ON}$  of the devices.

GaN power devices are currently utilising mainly lateral device architectures, offering good performance in high-frequency [22], gas sensors [23] motor drives [24] and rail traction drives [25], although always at considerably lower voltage (maximum 650-900 V) and power ratings than SiC. Lateral power GaN devices such as enhancement-mode (e-mode) high electron mobility transistors (HEMTs) and diodes are already commercially available up to 900 V[5], competing with Si IGBTs and SiC MOSFETs in automotive applications in this voltage range. The previously mentioned lower power ratings compared to SiC are due to the lateral device geometry: in a lateral device, the current flows through a smaller cross-sectional area, compared to large vertical devices, increasing on-state resistance and limiting the current carrying capability of these devices, so they are limited to applications up to a few kW [26]. GaN research has been ongoing into vertical GaN devices, using either freestanding GaN or GaN bulk substrates and, most importantly, using lower-cost GaN-on-Si substrates, which could successfully block voltages up to 1.2 kV [26]. For high-cost premium devices, GaN-on-SiC substrates are available in research areas and could potentially capitalise on the lower lattice mismatch between GaN and SiC and the higher thermal conductivity of SiC substrates [27]. Generally however, the limitations in material- layer structures unsuitable for vertical devices, high defect density from growth on mismatched substrates and limited wafer diameters - are still hampering the further development of GaN devices, since this is still significantly restricting their current, voltage and power ratings[26].

Amongst the mentioned wide bandgap semiconductors, 3C-SiC, further explained in chapter 2, diamond and  $Ga_2O_3$  devices do mainly exist in niche research applications, where successful 3C-MOSFETs [28]

and diodes[29], quasi-vertical diamond SBDs [30, 31] and research-grade  $Ga_2O_3$  diodes [15] have been shown.  $Ga_2O_3$  devices suffer from the material's extremely low thermal conductivity and the challenges arising when trying to p-type dope material [32], whereas diamond devices suffer from the absence of a reliable doping process. Hence, although these materials all offer potential power electronics advantages over Si, their poor material quality, high material cost or other engineering challenges hamper further development.

The results reported in this thesis aimed to develop a surface conditioning process of 4H-SiC Schottky diodes and a dielectric deposition process on SiC materials (3C and 4H) suitable for MOS devices.

# **1.4 THESIS OUTLINE**

In the following chapter, the material properties and growth methods of SiC are introduced. Afterwards, it introduces the power device structures that are analysed in the thesis with a focus on their interfaces. It then ends with the electrical and physical characterisation methods.

Chapter 3 then delivers an investigation into the impact of a phosphorous pentoxide surface passivation treatment on the performance of planar SiC SBDs. After showing the static electrical results, a surface study employing AFM/SEM, TEM, XPS is carried out to investigate impacts on the device brought about by this treatment. The transfer of this process into 3.3 kV power structures will be presented in chapter 4, where the development of the cross-sectional structures, the electrical performance as well as an XPS investigation are shown. A double pulse switching test is carried out on the fabricated device structures, too.

Chapter 5 then delivers a post-deposition annealing study on ALDdeposited silicon dioxide layers, in which the impact of different temperatures, ambients and post-deposition anneals on electrical characteristics of MOSCAP structures is shown. Key electrical parameters of interest that are investigated are flatband voltage, hysteresis voltage and frequency dispersion. The surface bonding chemistry is again investigated by means of XPS. In the final results chapter, the aforementioned ALD deposition process is done on freestanding 3C-SiC material, where an investigation focuses on material properties first. An AFM and XRD study is followed by electrical characterisation of MOSCAPs using thermal oxides, LPCVD-deposited and ALD-deposited oxides.

# **1.5 REFERENCES**

- [1] F. Roccaforte *et al.*, "Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices," vol. 187, pp. 66-77, 2018.

- [2] L. F. Alves *et al.*, "SIC power devices in power electronics: An overview," in 2017 Brazilian Power Electronics Conference (COBEP), 2017: IEEE, pp. 1-8.

- [3] X. She, A. Q. Huang, Ó. Lucía, and B. J. I. T. o. I. E. Ozpineci, "Review of silicon carbide power devices and their applications," vol. 64, no. 10, pp. 8193-8205, 2017.

- [4] S. Ji, Z. Zhang, F. J. C. T. o. E. M. Wang, and Systems, "Overview of high voltage SiC power semiconductor devices: Development and application," vol. 1, no. 3, pp. 254-264, 2017.

- [5] J. O. Gonzalez, R. Wu, S. Jahdi, and O. Alatise, "Performance and reliability review of 650 V and 900 V silicon and SiC devices: MOSFETs, cascode JFETs and IGBTs," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 9, pp. 7375-7385, 2019.

- [6] J. Wang, V. Veliadis, J. Zhang, Y. Alsmadi, P. R. Wilson, and M. J. J. I. P. E. M. Scott, "IEEE ITRW working group position paper-system integration and application: Silicon carbide: A roadmap for silicon carbide adoption in power conversion applications," vol. 5, no. 2, pp. 40-44, 2018.

- [7] A. Morya, M. Moosavi, M. C. Gardner, and H. A. Toliyat, "Applications of Wide Bandgap (WBG) devices in AC electric drives: A technology status review," in 2017 IEEE International Electric Machines and Drives Conference (IEMDC), 2017: IEEE, pp. 1-8.

- [8] D. J. Spry *et al.*, "Prolonged 500° C operation of 100+ transistor silicon carbide integrated circuits," in *Materials Science Forum*, 2018, vol. 924: Trans Tech Publ, pp. 949-952.

- [9] J.-M. Lauenstein *et al.*, "Room Temperature Radiation Testing of a 500° C Durable 4H-SiC JFET Integrated Circuit Technology," in 2019 IEEE Radiation Effects Data Workshop, 2019: IEEE, pp. 1-7.

- [10] S. Perez, A. Francis, J. Holmes, T. J. A. P. Vrotsos, and Presentations, "Silicon Carbide Junction Field Effect Transistor Compact Model for Extreme Environment Integrated Circuit Design," vol. 2021, no. HiTEC, pp. 000118-000122, 2021.

- [11] L. I. Gear, "Tesla's Innovative Power Electronics: The Silicon Carbide Inverter," 18/09/2021 2021. [Online]. Available: <u>https://www.idtechex.com/en/research-article/teslas-innovative-power-</u> electronics-the-silicon-carbide-inverter/23080.

- [12] S. Adachi, *Properties of semiconductor alloys: group-IV*, *III-V and II-VI semiconductors*. John Wiley & Sons, 2009.

- [13] T. Kimoto and J. A. Cooper, *Fundamentals of silicon carbide technology:* growth, characterization, devices and applications. John Wiley & Sons, 2014.

- [14] R. Hull, *Properties of crystalline silicon* (no. 20). IET, 1999.

- [15] H. Xue, Q. He, G. Jian, S. Long, T. Pang, and M. J. N. r. l. Liu, "An overview of the ultrawide bandgap Ga 2 O 3 semiconductor-based Schottky barrier diode for power electronics application," vol. 13, no. 1, pp. 1-13, 2018.

- [16] F. Li *et al.*, "Status and Prospects of Cubic Silicon Carbide Power Electronics Device Technology," *Materials*, vol. 14, no. 19, p. 5831, 2021.

- [17] E. Van Brunt *et al.*, "27 kV, 20 A 4H-SiC n-IGBTs," in *Materials Science Forum*, 2015, vol. 821: Trans Tech Publ, pp. 847-850.

- [18] J. W. Palmour *et al.*, "Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV," in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2014: IEEE, pp. 79-82.

- [19] E. Brunt et al., "22 kV, 1 cm 2, 4H-SiC n-IGBTs with improved conductivity modulation," in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2014: IEEE, pp. 358-361.

- [20] F. J. R. S. La Via, "Silicon carbide epitaxy," 2012.

- [21] P. Fiorenza, F. Giannazzo, and F. Roccaforte, "Characterization of SiO2/4H-SiC interfaces in 4H-SiC MOSFETs: a review," *Energies*, vol. 12, no. 12, p. 2310, 2019.

- [22] G. Longobardi, "GaN for power devices: Benefits, applications, and normallyoff technologies," in 2017 International Semiconductor Conference (CAS), 2017: IEEE, pp. 11-18.

- [23] M. A. H. Khan and M. V. J. S. Rao, "Gallium nitride (GaN) nanostructures and their gas sensing properties: a review," vol. 20, no. 14, p. 3889, 2020.

- [24] X. Ding, Y. Zhou, J. J. C. T. o. E. M. Cheng, and Systems, "A review of gallium nitride power device and its applications in motor drive," vol. 3, no. 1, pp. 54-64, 2019.

- [25] E. A. Jones, F. F. Wang, D. J. I. J. o. E. Costinett, and S. T. i. P. Electronics, "Review of commercial GaN power devices and GaN-based converter design challenges," vol. 4, no. 3, pp. 707-719, 2016.

- [26] Y. Zhang, A. Dadgar, and T. J. J. O. P. D. A. P. Palacios, "Gallium nitride vertical power devices on foreign substrates: a review and outlook," vol. 51, no. 27, p. 273001, 2018.

- [27] R. S. Pengelly, S. M. Wood, J. W. Milligan, S. T. Sheppard, W. L. J. I. T. o. M. T. Pribble, and Techniques, "A review of GaN on SiC high electronmobility power transistors and MMICs," vol. 60, no. 6, pp. 1764-1783, 2012.

- [28] H. Nagasawa, M. Abe, K. Yagi, T. Kawahara, and N. J. p. s. s. Hatta, "Fabrication of high performance 3C-SiC vertical MOSFETs by reducing planar defects," vol. 245, no. 7, pp. 1272-1280, 2008.

- [29] F. Li *et al.*, "A study on free-standing 3C-SiC bipolar power diodes," vol. 118, no. 24, p. 242101, 2021.

- [30] N. Donato, N. Rouger, J. Pernot, G. Longobardi, and F. J. J. o. P. D. A. P. Udrea, "Diamond power devices: state of the art, modelling, figures of merit and future perspective," vol. 53, no. 9, p. 093001, 2019.

- [31] H. J. M. S. i. S. P. Umezawa, "Recent advances in diamond power semiconductor devices," vol. 78, pp. 147-156, 2018.

- [32] A. Kyrtsos, M. Matsubara, and E. Bellotti, "On the feasibility of p-type Ga2O3," *Applied Physics Letters*, vol. 112, no. 3, p. 032108, 2018.

# 2 Silicon Carbide Properties, Growth, Characterisation and Devices

Throughout this thesis, the crystal structure, physical and electrical properties of silicon carbide will be frequently referred to. This chapter will deliver descriptions of the crystal structure of SiC, SiC epitaxial growth, epitaxial layer defects and the most widely used growth technique, chemical vapour deposition (CVD). The chapter will then introduce the power devices that are analysed in this thesis, the theory of their interfaces and the electrical and physical techniques used to characterise them.

# 2.1 SEMICONDUCTOR CRYSTAL STRUCTURES, SIC POLYTYPES

When crystals are formed between solid elements or compounds, they create regular lattice patterns. Single element semiconductors, such as Si, Ge, and diamond, mostly form diamond crystal structures. Compound semiconductors most frequently form diamond-like zincblende structures (e.g. GaAs, InGaAs, GaP), though wurtzite structures that resemble hexagonal close-packed crystal structures can also be found. The most relevant compound semiconductors, GaN and SiC, are predominantly a hexoganl crystal lattice, called wurtzite.

Although their chemical composition is identical, most semiconductor materials can exhibit different crystal structures, a phenomenon that is called polymorphism [2]. For a subgroup of polymorph crystals, the stacking sequence of the smallest repetitive cell, a unit cell, differs in one axis. This structural effect is called polytypism [3]. Silicon carbide's crystalline structure is unique in that, to this day, more than 200 polytypes

have been found [4-7], although only a few of these have been shown to be stable.

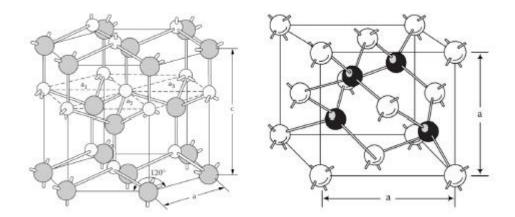

SiC only allows for a rigid 50:50 stoichiometry of silicon and carbon atoms. Each carbon atom bonds to four silicon atoms, and vice versa, forming two fundamental structural patterns that can be seen in Fig.2.1, from [8]. Si and C atoms are linked via covalent bonds and form a tetrahedron. The hexagonal structure, Fig. 2.1(a), can be found in most SiC polytypes. All hexagonal polytypes of SiC are called  $\alpha$ -SiC.

Cubic SiC, or  $\beta$ -SiC, as depicted in Fig.2.1 (b), is referred to as zincblende pattern, which has the same diamond structure as Si and Ge.

Figure 2.1 : Hexagonal (a) and cubic (b) SiC lattice, dark atoms represent Si and light atoms represent C atoms [7].

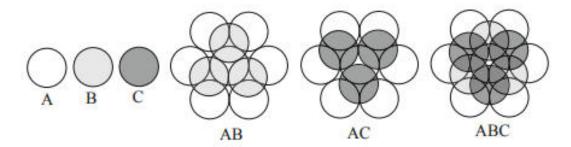

To differentiate between the different polytypes, their stacking sequence needs to be analysed. For simplification in this section, only the position of the Si atoms will be assessed, as the carbon atom aligns with it vertically in the c-plane, as seen in Figure 2.1a. For simplification, Fig. 2.2 can be observed [9]. Only three double-atomic layers denoted A, B and C exist in SiC and all polytypes can be formed when changing the stacking sequence of these. The order in which the occupational sites repeat determines each polytype.

Figure 2.2: The stacking layer sequence in SiC depicting the three different occupation sites [8].

The stacking sequence of relevant polytypes of SiC is shown in Fig. 2.3, reproduced from [10]. Their labelling follows rules which are outlined in [11], where the first number refers to the number of layers needed to form a complete unit cell, H, C and R refer to hexagonal, cubic and rhombohedral lattice structures, respectively. The fundamental electrical properties of the introduced polytypes will be outlined in the next section.

Figure 2.3: Stacking structure of selected SiC polytypes [9].

Table 2.1: A summary of the main electrical properties of Si, the most important polytypes of SiC and wurtzite GaN at 300 K [1]. Given the rarity of c-GaN and ubiquity of w-GaN, the wurtzite polytype is commonly referred to simply as 'GaN', and it can be assumed that the wurtzite polytype is being considered unless stated otherwise.

| Properties                         | Units                 | Si                     | 4H-SiC               | 6H-SiC            | 3C-SiC                 | w-GaN                   |

|------------------------------------|-----------------------|------------------------|----------------------|-------------------|------------------------|-------------------------|

| Bandgap                            | (eV)                  | 1.12                   | 3.26                 | 3.0               | 2.36                   | 3.39                    |

| Critical Electric<br>field         | (MV/cm)               | 0.2                    | 2.8                  | 2.5               | 1.4                    | 3.75-3.3                |

| Electron Saturation<br>Velocity    | (cm/s)                | $1 \times 10^{7}$      | $2 \times 10^{7}$    | $2 \times 10^{7}$ | $2 \times 10^{7}$      | $2.5 \times 10^{7}$     |

| Electron mobility                  | (cm <sup>2</sup> /Vs) | 1350                   | 720-650              | 500               | 800                    | 2000-1000               |

| Hole mobility                      | (cm <sup>2</sup> /Vs) | 480                    | 120                  | 80                | 40                     | 30                      |

| Intrinsic Carrier<br>Concentration | (cm <sup>-3</sup> )   | 1.5 x 10 <sup>10</sup> | 8 x 10 <sup>-9</sup> | 10 <sup>-5</sup>  | 1.5 x 10 <sup>-1</sup> | 1.9 x 10 <sup>-10</sup> |

| Thermal<br>Conductivity.           | (W/cm.K)              | 1.5                    | 4.5                  | 3-4               | 3.2                    | 1.3                     |

# **2.2 ELECTRICAL PROPERTIES**

For the successful performance of power electronics devices, it is of paramount importance to consider the electrical properties of the material these devices are fabricated with. Key electrical parameters at 300 K can be found in Table 2.1. Their impact on device performance will be briefly described now. The bandgap of a material will determine how many carriers, at any given temperature, can cross from the valence band to the conduction band, impacting the intrinsic carrier concentration  $(n_i)$ , which correlates with leakage current levels. The thermal conductivity governs maximum current rating via the thermal resistance between junction and die attach. On a circuit level, the device performance will be governed by the bulk mobility parameters (device resistance) and electron saturation velocity (switching).

For 4H-SiC, the extremely low intrinsic carrier concentration of approximately 8 x 10<sup>-9</sup> cm<sup>-3</sup> at 300 K (Table 2.1) make devices suitable to operate at much higher temperatures than Si. Since this parameter is 13 orders of magnitude higher for Si, a Si device compared to an identical SiC device will have higher leakage currents at a given operating temperature, resulting in higher losses and earlier device breakdown. This high temperature performance is also improved by 4H-SiC's thermal conductivity of 4.5 W/cm.K, approx. 3 times higher than for GaN and Si, which aids removal of heat generated by on-state and switching losses.