A Thesis Submitted for the Degree of PhD at the University of Warwick

**Permanent WRAP URL:**

http://wrap.warwick.ac.uk/169206

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Build Framework and Runtime Abstraction for Partial Reconfiguration on FPGA SoCs

by

### Alex R. Bucknall

#### Thesis

Submitted to the University of Warwick in fulfilment of the requirements for admission to the degree of

**Doctor of Philosophy**

School of Engineering

January 2022

# Contents

| List of      | Tables                                   | vi  |

|--------------|------------------------------------------|-----|

| List of      | Figures                                  | vii |

| Ackno        | wledgments                               | x   |

| Declar       | ations                                   | xi  |

| ${f Abstra}$ | act                                      | xii |

| Acron        | yms                                      | xiv |

| Chapt        | er 1 Introduction                        | 1   |

| 1.1          | Motivations                              | 2   |

| 1.2          | Objectives                               | 3   |

| 1.3          | Contributions                            | 4   |

| 1.4          | Thesis Roadmap                           | 6   |

| 1.5          | Publications                             | 6   |

| 1.6          | Open Source                              | 7   |

| Chapt        | er 2 Background                          | 8   |

| 2.1          | Computing Platforms                      | 9   |

| 2.2          | General Purpose Processors               | 9   |

|              | 2.2.1 x86                                | 9   |

|              | 2.2.2 ARM                                | 9   |

| 2.3          | Graphical Processing Units               | 10  |

| 2.4          | Application Specific Integrated Circuits | 11  |

| 2.5          | Field Programmable Gate Arrays           | 12  |

|              | 2.5.1 Architecture                       | 13  |

|              | 2.5.2 Reconfiguration                    | 16  |

|              | 2.5.3 Development Process                | 21  |

|              | 2.5.4 PR Design Challenges               | 22  |

| 2.6          | FPGAs compared to GPPs, GPUs & ASICs     | 25  |

| 2.7          | Heterogeneous SoCs                       | 27  |

|       | 2.7.1  | Intel                                                | 27           |  |  |  |  |

|-------|--------|------------------------------------------------------|--------------|--|--|--|--|

|       | 2.7.2  | Xilinx                                               | 28           |  |  |  |  |

| 2.8   | Opera  | ating Systems (Linux)                                | 30           |  |  |  |  |

| 2.9   | Summ   | nary                                                 | 32           |  |  |  |  |

| Chapt | er 3 I | Literature Review                                    | 33           |  |  |  |  |

| 3.1   | Design | n Methodologies                                      | 33           |  |  |  |  |

|       | 3.1.1  | Vendor PR Tools                                      | 33           |  |  |  |  |

| 3.2   | Acade  | emic PR Tools                                        | 38           |  |  |  |  |

|       | 3.2.1  | Build Workflows & Floorplanning                      | 38           |  |  |  |  |

|       | 3.2.2  | PR Runtime Management                                | 43           |  |  |  |  |

| 3.3   | Applio | cations of Partial Reconfiguration                   | 47           |  |  |  |  |

|       | 3.3.1  | Communications Systems                               | 48           |  |  |  |  |

|       | 3.3.2  | Networking                                           | 48           |  |  |  |  |

|       | 3.3.3  | Image Processing                                     | 49           |  |  |  |  |

|       | 3.3.4  | Machine Learning                                     | 49           |  |  |  |  |

|       | 3.3.5  | Automotive                                           | 50           |  |  |  |  |

|       | 3.3.6  | Space                                                | 51           |  |  |  |  |

|       | 3.3.7  | Autonomous Adaptive Systems                          | 52           |  |  |  |  |

| 3.4   | Summ   | nary                                                 | 53           |  |  |  |  |

| Chapt | er 4 ( | Over the Network FPGA Reconfiguration                | 55           |  |  |  |  |

| 4.1   |        | luction                                              | 55           |  |  |  |  |

| 4.2   |        | ibutions                                             | 56           |  |  |  |  |

| 4.3   | Relate | Related Work                                         |              |  |  |  |  |

| 4.4   |        | m Architecture                                       | 59           |  |  |  |  |

|       | 4.4.1  | Traditional Approach                                 | 59           |  |  |  |  |

|       | 4.4.2  | DMA Proxying                                         | 60           |  |  |  |  |

|       | 4.4.3  | Network Partial Reconfiguration                      | 61           |  |  |  |  |

| 4.5   | Case S | Study                                                | 63           |  |  |  |  |

|       | 4.5.1  | Advanced Encryption Standard                         | 65           |  |  |  |  |

|       | 4.5.2  | PRESENT                                              | 65           |  |  |  |  |

| 4.6   | Exper  | iments                                               | 66           |  |  |  |  |

|       | 4.6.1  | Frame Decoding in PS (PCAP)                          | 66           |  |  |  |  |

|       | 4.6.2  | Frame Decoding in PS (Integrated Controller in PL)   | 67           |  |  |  |  |

|       | 4.6.3  | Frame Decoding in PL (Custom PR Controller)          | 69           |  |  |  |  |

|       | 4.6.4  | Bitstream Over Network                               | 70           |  |  |  |  |

| 4.7   |        | nary                                                 | 71           |  |  |  |  |

|       |        |                                                      |              |  |  |  |  |

| Chapt |        | Design and Build Framework for Partial Reconfigurers |              |  |  |  |  |

|       |        |                                                      | <b>73</b> 73 |  |  |  |  |

| 5.1   | THEFOC | luction                                              | 19           |  |  |  |  |

| 5.2    | Contri  | butions                                         |

|--------|---------|-------------------------------------------------|

| 5.3    | Relate  | ed Work                                         |

|        | 5.3.1   | Vendor Tools                                    |

|        | 5.3.2   | Current Research                                |

| 5.4    | Conce   | pts                                             |

|        | 5.4.1   | Heterogeneous Systems on Chip 82                |

|        | 5.4.2   | Operating Systems                               |

|        | 5.4.3   | Partial Reconfiguration                         |

|        | 5.4.4   | PR Design Workflow                              |

| 5.5    | Build   | Toolflow                                        |

| 5.6    | Edaliz  | e & FuseSoC                                     |

| 5.7    | Hardw   | vare Abstraction                                |

| 5.8    | Infrast | tructure Generation                             |

|        | 5.8.1   | Compile-time Generated Interfacing 90           |

|        | 5.8.2   | Automatic PR Region Generation 91               |

|        | 5.8.3   | PR Module Chaining                              |

|        | 5.8.4   | Customised Base Design                          |

|        | 5.8.5   | Internal Configuration Access Port              |

| 5.9    | Linux   |                                                 |

|        | 5.9.1   | PMU Firmware                                    |

|        | 5.9.2   | Device Tree                                     |

|        | 5.9.3   | Device Tree Overlay                             |

|        | 5.9.4   | Kernel Drivers                                  |

| 5.10   | Evalua  | ation                                           |

|        | 5.10.1  | FPGA Resource Consumption                       |

|        | 5.10.2  | Build Time Complexity                           |

| 5.11   | Summ    | ary                                             |

| Chapte | er 6 I  | Partial Reconfiguration Runtime & Configuration |

| Maı    | nagem   | ent 102                                         |

| 6.1    | Introd  | uction                                          |

| 6.2    | Contri  | butions                                         |

| 6.3    | Relate  | ed Work                                         |

|        | 6.3.1   | FPGA Manager                                    |

| 6.4    | Runtin  | me Abstraction                                  |

|        | 6.4.1   | Hardware Resources                              |

|        | 6.4.2   | Device Tree Overlay                             |

|        | 6.4.3   | Linux Userspace Drivers                         |

|        | 6.4.4   | Xilinx AXI DMA                                  |

| 6.5    | ICAP    | DMA Provisioning                                |

| 6.6    | Config  | guration Manager                                |

|       | 6.6.1  | Runtime API                                           | 09        |

|-------|--------|-------------------------------------------------------|-----------|

| 6.7   | Evalu  | ation                                                 | 11        |

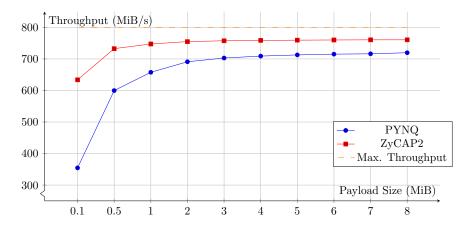

|       | 6.7.1  | Accelerator Performance                               | 12        |

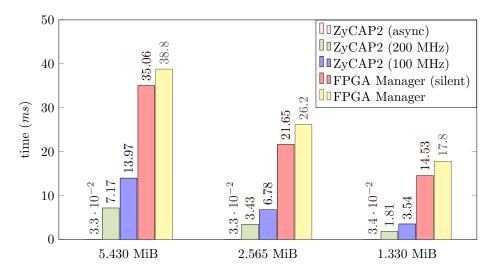

|       | 6.7.2  | Partial Reconfiguration Performance                   | 13        |

| 6.8   | Case   | Study $\dots$ 1                                       | 15        |

|       | 6.8.1  | PR Region Data Chaining                               | 16        |

|       | 6.8.2  | Design Process                                        | 17        |

|       | 6.8.3  | Comparison to Existing Tools                          | 18        |

|       | 6.8.4  | Runtime Application                                   | 18        |

| 6.9   | Summ   | nary                                                  | 20        |

| Chapt | er 7   | Autonomous Adaptive Systems Framework using           |           |

| Par   | tial R | econfiguration 1                                      | <b>21</b> |

| 7.1   | Introd | luction                                               | 21        |

| 7.2   | Contr  | ibutions                                              | 22        |

| 7.3   | Relate | ed Work                                               | 23        |

|       | 7.3.1  | Adaptive System Concepts                              | 23        |

|       | 7.3.2  | Robot Operating System                                | 24        |

|       | 7.3.3  | Configuration Terminology                             | 25        |

|       | 7.3.4  | FPGA Acceleration of Adaptive Systems                 | 25        |

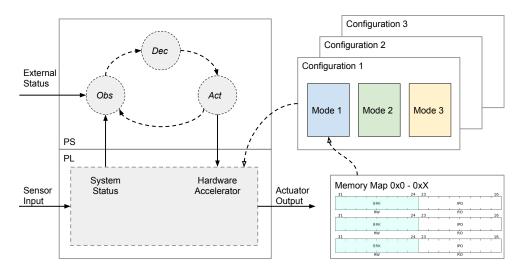

| 7.4   | Archi  | tecture                                               | 28        |

|       | 7.4.1  | Adaptive Hardware Design Tooling                      | 28        |

|       | 7.4.2  | Runtime Configuration Schemas                         | 29        |

|       | 7.4.3  | Configuration Manager                                 | 30        |

|       | 7.4.4  | Configuration API                                     | 31        |

| 7.5   | Demo   | nstration                                             | 32        |

|       | 7.5.1  | ROS2 Architecture                                     | 33        |

|       | 7.5.2  | Experiment                                            | 34        |

| Chapt | er 8 ( | Conclusion and Future Work 1                          | 37        |

| 8.1   | Sumn   | nary of Contributions                                 | 37        |

|       | 8.1.1  | Network-Enabled FPGA Reconfiguration 1                | .38       |

|       | 8.1.2  | Python Library for SoC Interfaces Extraction and Gen- |           |

|       |        | eration                                               | 38        |

|       | 8.1.3  | Automated End-to-End PR Development Flow 1            | 39        |

|       | 8.1.4  | High Performance Runtime PR Manager                   | 39        |

|       | 8.1.5  | Abstracted Configuration Manager for CPSs 1           | 40        |

| 8.2   | Futur  | e Work                                                | 40        |

|       | 8.2.1  | Containerization of vendor tooling within $ZyCAP2$ 1  | 40        |

|       | 8.2.2  | Integration of FuseSoC into ZyCAP2 tools 1            | 41        |

|       | 8 2 3  | FuseSoC Vitis HLS Support 1                           | 41        |

|       | 8.2.4 | Xilinx DFX | Abstrac | t Shel | l Wo | rkflo | w. |  |   |  | <br> | 141 |

|-------|-------|------------|---------|--------|------|-------|----|--|---|--|------|-----|

| 8.3   | Summ  | ary        |         |        |      |       |    |  | • |  |      | 142 |

| Appen | dix A | Code Snip  | pets    |        |      |       |    |  |   |  |      | 143 |

# List of Tables

| 2.1 | Comparison of FPGA Hard & Soft Processors            |

|-----|------------------------------------------------------|

| 2.2 | Intel FPGA SoC Families                              |

| 2.3 | Xilinx FPGA SoC Families                             |

|     |                                                      |

| 4.1 | Resource Utilization on Zynq-7020                    |

| 4.2 | Network PR Experiment Results 67                     |

| 5.1 | Build Tool Comparison                                |

|     | PR Manager static PL resources                       |

|     |                                                      |

| 6.1 | Runtime Comparison                                   |

| 6.2 | Runtime Latency Breakdown Average Across 25 Runs 113 |

# List of Figures

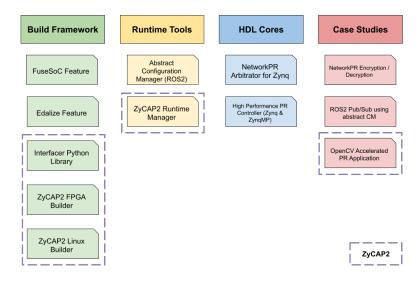

| 1.1  | Thesis Contributions                                                                                                    | 5  |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

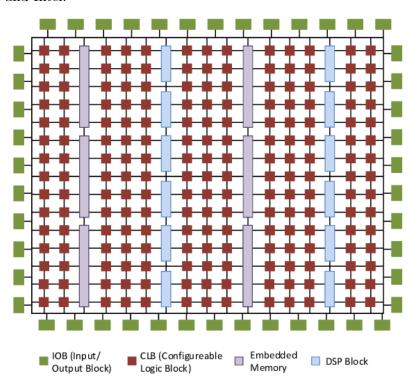

| 2.1  | Generic Xilinx FPGA Architecture [1]                                                                                    | 12 |

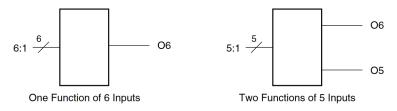

| 2.2  | Ultrascale CLB LUT6 and dual LUT5 blocks [2]                                                                            | 14 |

| 2.3  | Ultrascale CLB LUT and storage elements (1 of 6 in a Slice) [2]                                                         | 14 |

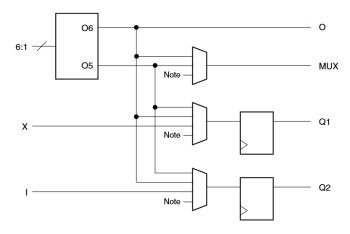

| 2.4  | Ultrascale CLB Shift Register Logic [2]                                                                                 | 14 |

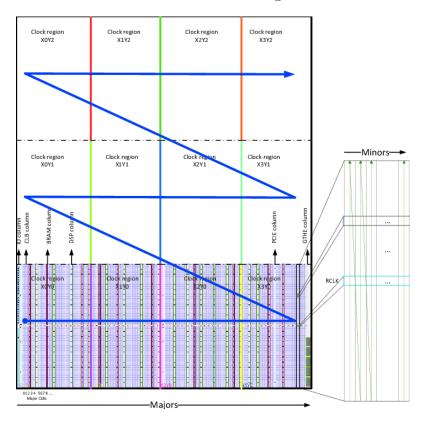

| 2.5  | Ultrascale Kintex Floor plan [3]                                                                                        | 15 |

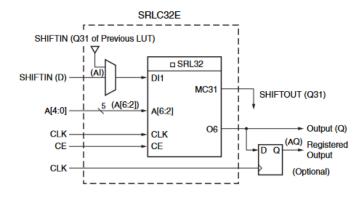

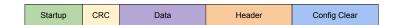

| 2.6  | Xilinx Static Bitstream Layout (7 Series FPGAs) [4]                                                                     | 16 |

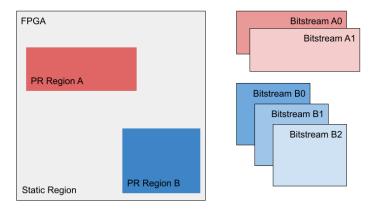

| 2.7  | Example of partially reconfigurable regions and PR bitstreams                                                           | 18 |

| 2.8  | Xilinx Partial Bitstream Layout (7 Series FPGAs) [4]                                                                    | 18 |

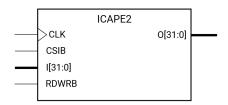

| 2.9  | Xilinx ICAPE2 Primitive (7 Series FPGAs) [5]                                                                            | 20 |

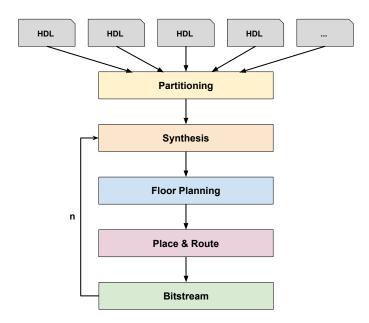

| 2.10 | PR Build Process where $n$ is the number of configurations                                                              |    |

|      | required to be generated                                                                                                | 23 |

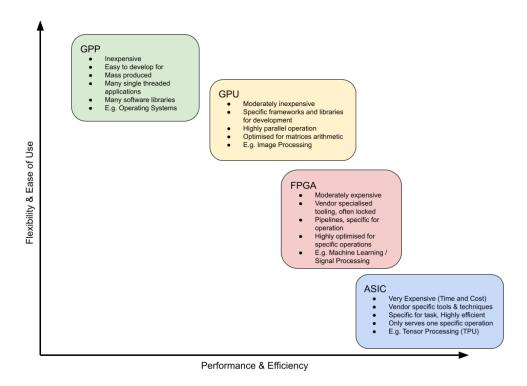

| 2.11 | General comparison of GPP, GPU, FPGA and ASIC                                                                           | 26 |

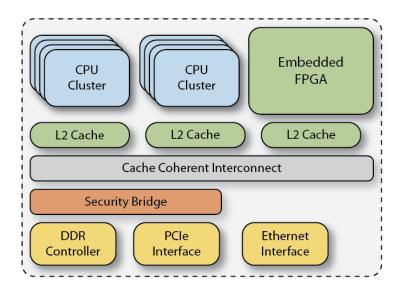

| 2.12 | Generic FPGA SoC Architecture [6]                                                                                       | 28 |

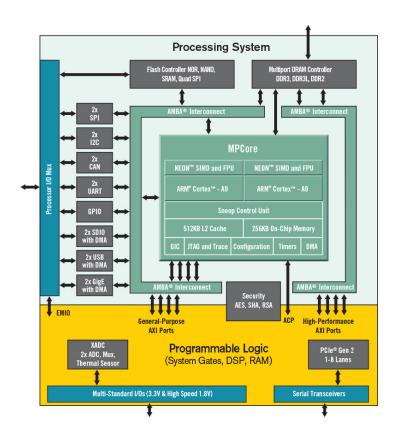

| 2.13 | Zynq-7000 Architecture [7]                                                                                              | 29 |

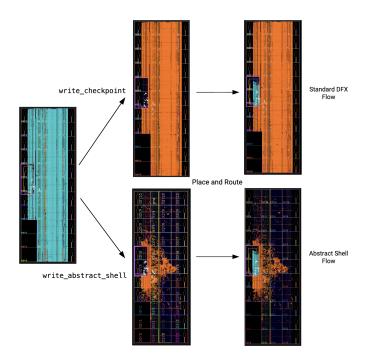

| 3.1  | Standard DFX vs Abstract Shell implementation logic [8]                                                                 | 35 |

| 3.2  | Example of Vitis HLS Pragma for AXI Stream Slave/Masters.                                                               | 36 |

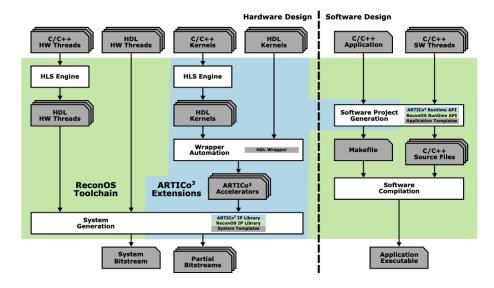

| 3.3  | ReConOS toolchain with ARTICO3 extensions [9]                                                                           | 41 |

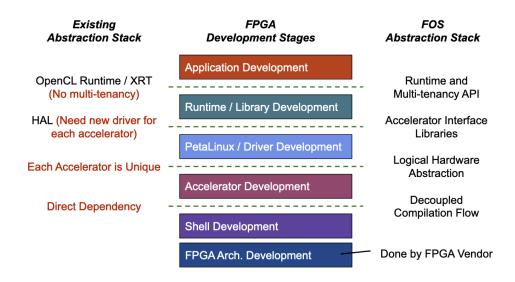

| 3.4  | FOS compared to traditional development abstraction $[10]$                                                              | 42 |

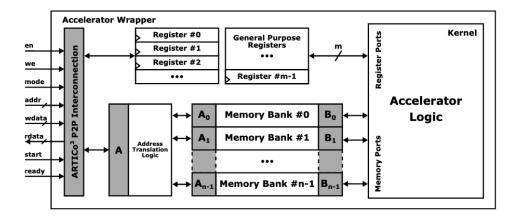

| 3.5  | ARTICO3 kernel wrapper [9]                                                                                              | 43 |

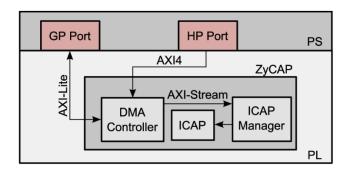

| 3.6  | ZyCAP highlighting interfaces between PS and PL [11]                                                                    | 47 |

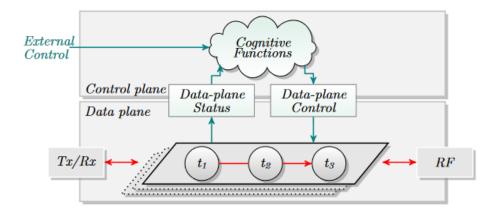

| 3.7  | Concept of a cognitive radio with control and data planes split                                                         |    |

|      | across a CPU and FPGA [12] $\hdots$                                                                                     | 48 |

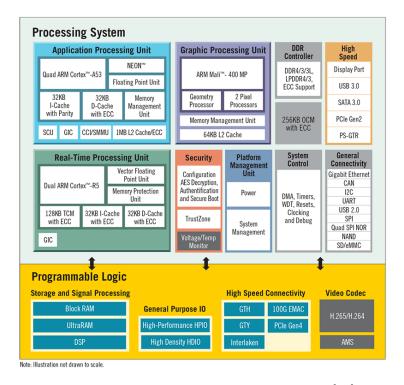

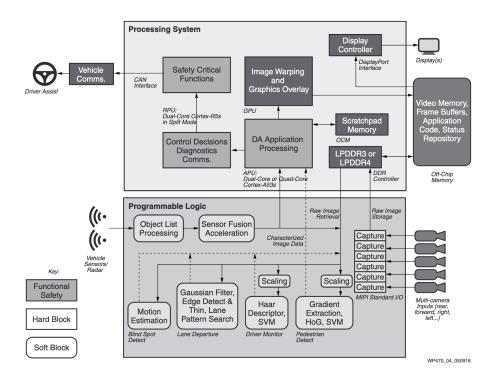

| 3.8  | Xilinx ZynqMP Example ADAS Application [13]                                                                             | 51 |

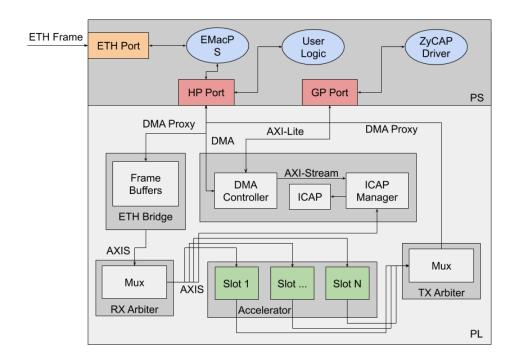

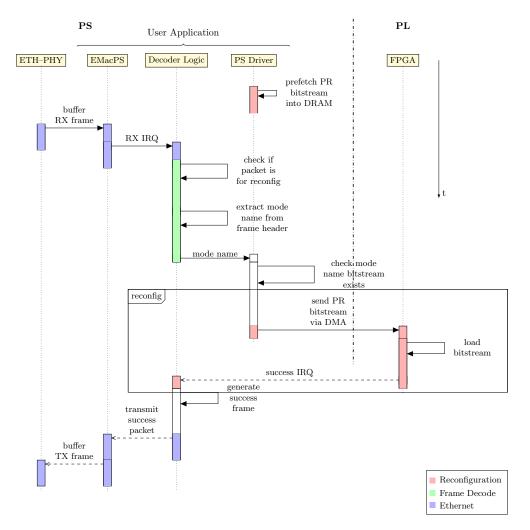

| 4.1  | Network Enabled PR Architecture                                                                                         | 64 |

| 4.2  | Zynq Processing Ethernet Packets in PL                                                                                  | 67 |

| 4.3  | Sequence of events when Ethernet frames are handled by PS and reconfiguration is managed by an integrated PR controller |    |

|      | in PL                                                                                                                   | 68 |

|      |                                                                                                                         | -  |

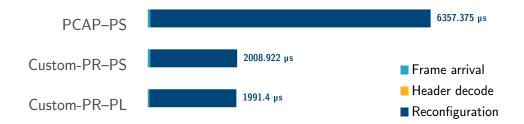

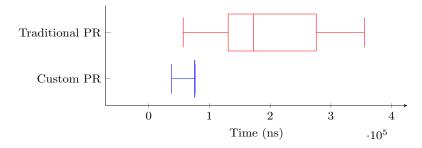

| 4.4  | Variation in partial reconfiguration triggered over the network interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

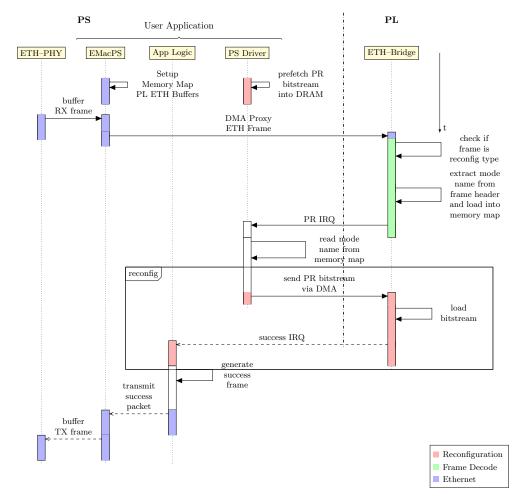

| 4.5  | Sequence of events when the packet decoding is handled within                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | the network interface in PL, while the reconfiguration is initiated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | from the PS using a custom reconfiguration manager 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

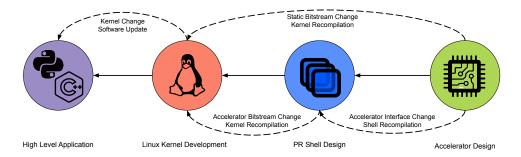

| 5.1  | Example Linux PR workflow. Designers are required to propag-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | ate their changes up from the accelerator, through to the shell,<br>the Linux kernel, as well as track PL changes from their high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | level applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

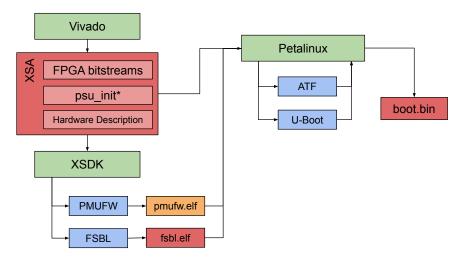

| 5.2  | The Xilinx Linux build flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

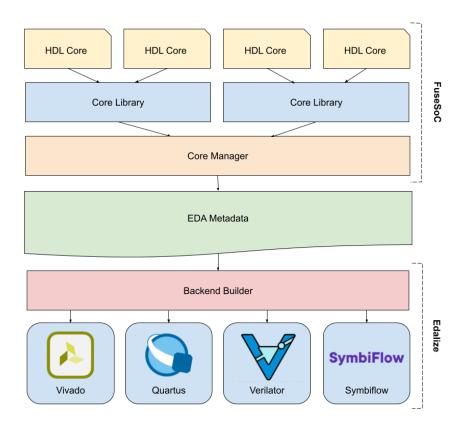

| 5.3  | FuseSoC to Edalize workflow with example EDA tooling 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

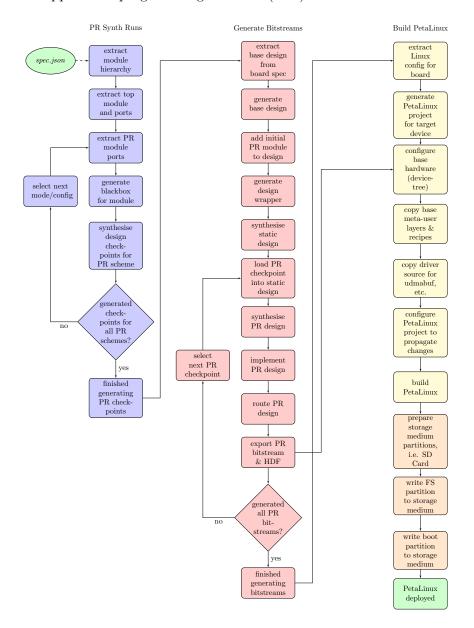

| 5.4  | Stages of the PR build flow [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

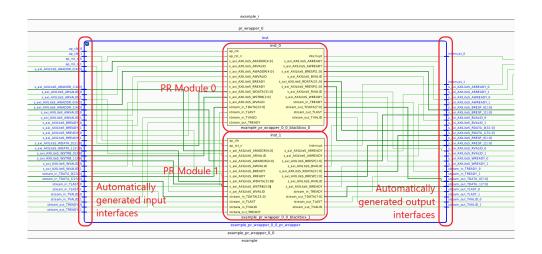

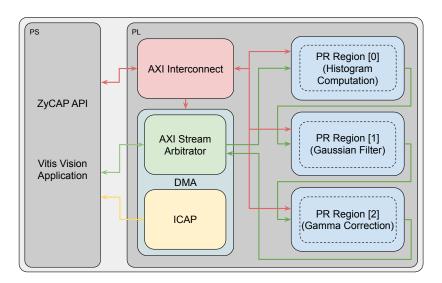

| 5.5  | PL architecture generated using the ZyCAP2 build tooling 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.6  | Synthesis schematic after build tool generates wrappers for each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | PRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

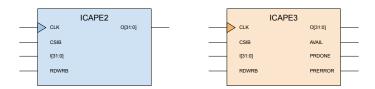

| 5.7  | ICAPE2 and ICAPE3 macros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

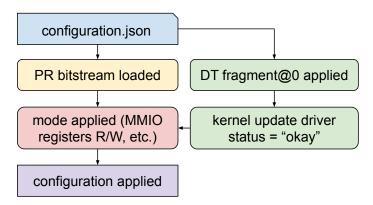

| 5.8  | Applying DT fragment via configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.9  | Example of Vitis HLS Pragma for AXI Stream Slave/Masters. 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.10 | Avnet Ultra96v2 Development Kit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

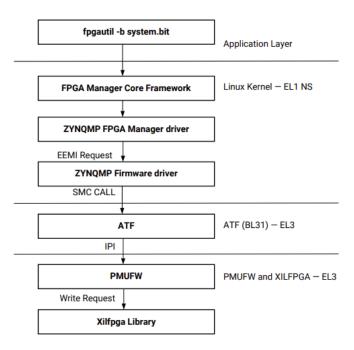

| 6.1  | Loading of the PCAP from FPGA Manager (ZynqMP)[15] $109$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

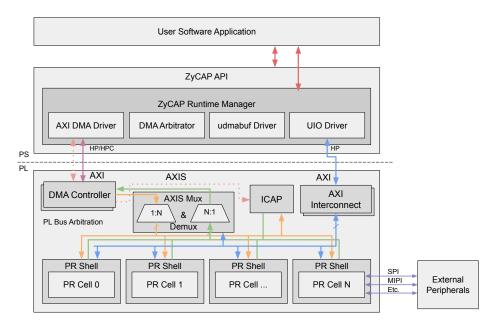

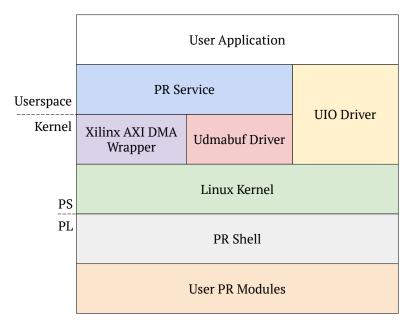

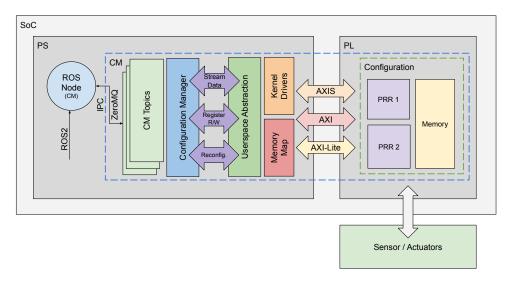

| 6.2  | ZyCAP Linux Stack [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

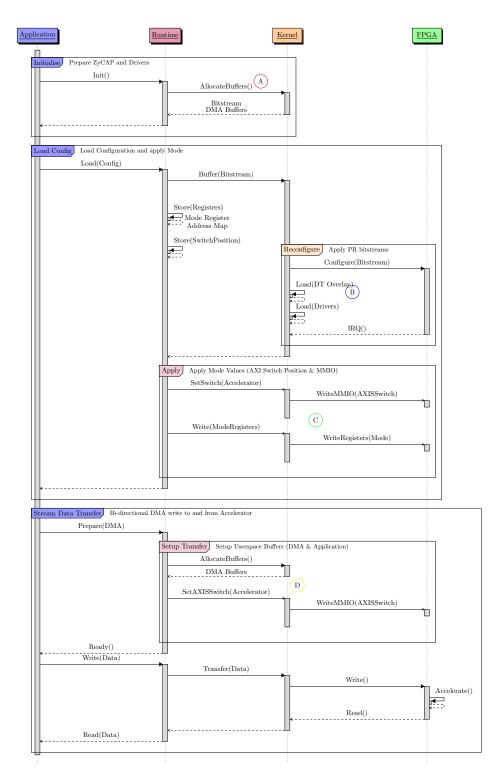

| 6.3  | Sequence diagram for the ZyCAP Runtime (Loading and Data transfer). (A) Setup of the ZyCAP and driver. (B) Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | of PR bitstream. (C) Application of PR modes. (D) Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | transfer between accelerator and software application 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

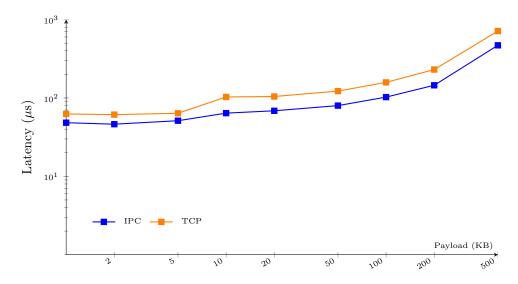

| 6.4  | DMA Driver Benchmark across 1000 transfers (PL clocked at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 200 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

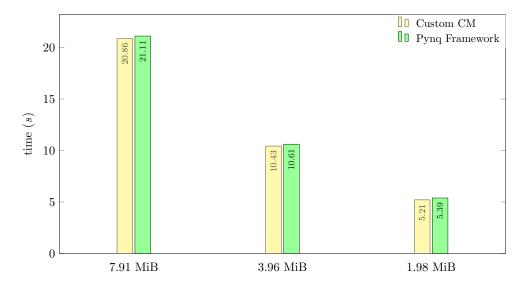

| 6.5  | PR Runtime Performance (time to load bitstream) 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.6  | Overview of HLS Vitis Vision chained accelerator demo 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

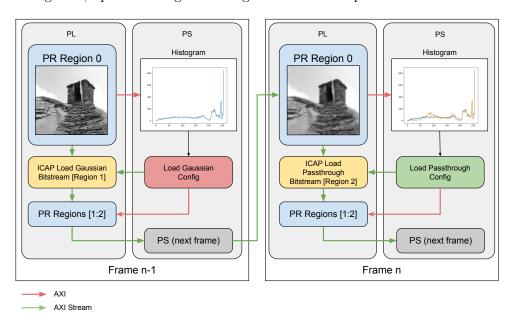

| 6.7  | PS uses histogram to determine accelerators to apply. Blue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | graph indicates original histogram, Orange indicates the new                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | histogram after configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.1  | Visualisation of hardware abstraction and definition 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

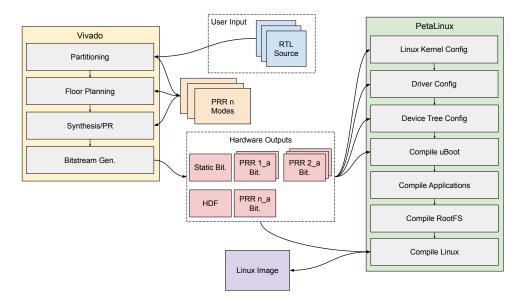

| 7.2  | An outline of the Xilinx PR build flow, from generating hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | within Vivado, to exporting hardware data into PetaLinux. $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ . $$ |

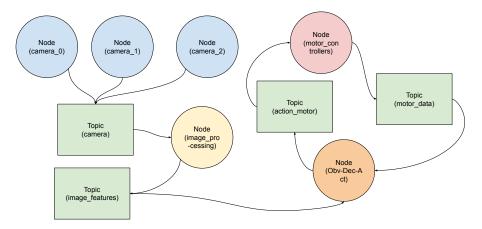

| 7.3  | Simplified example of a potential unmanned aerial vehicle ROS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | application, where camera data could be used for object avoidance $133$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |