ELSEVIER

Contents lists available at ScienceDirect

# Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# Electron beam lithography and dimensional metrology for fin and nanowire devices on Ge, SiGe and GeOI substrates

Nikolay Petkov<sup>a,c,\*</sup>, Margarita Georgieva<sup>a,c</sup>, Sinan Bugu<sup>c</sup>, Ray Duffy<sup>c</sup>, Brendan McCarthy<sup>c</sup>, Maksym Myronov<sup>b</sup>, Ann-Marie Kelleher<sup>c</sup>, Graeme Maxwell<sup>c</sup>, Giorgos Fagas<sup>c</sup>

- a Physical Sciences Department, Munster Technological University (MTU), Rosa Avenue, Bishopstown, Cork T12 P928, Ireland

- <sup>b</sup> Department of Physics, University of Warwick, Gibbet Hill Road, Coventry CV4 7AL, UK

- <sup>c</sup> Tyndall National Institute, Lee Maltings, Cork T12 R5CP, Ireland

#### ARTICLE INFO

Keywords: electron beam lithography HSQ Ge High density lines

#### ABSTRACT

Until now there is no systematic study on the effect of the substrate type on the hydrogen silsesquioxane (HSQ) electron beam lithography (EBL) patterning process. We investigate arrays of line structures with varying width and spacing, starting at 10 nm, exposed at varying dose, and developed by salty NaOH and TMAH developers on group IV semiconductor substrates. We demonstrate that the HSQ EBL process on Ge is much more limited in achieving the smallest obtainable features, having optimal uniformity and fidelity, in comparison to Si. Monte-Carlo simulations of the e-beam/substrate interactions for "pure" Si and Ge substrates, and varying content Ge/Si epitaxial layers on Si, suggest that the limitations seen are directly linked to back-scattered electron (BSE) generation. As predicted by the simulations and shown experimentally, improved fidelity and resolution of the features can be achieved by minimizing the (BSE) generation coming from the Ge contribution in the substartes. Finally, from a metrology perspective, it is demonstrated that although line patterns may appear resolved in SEM images, the variation in the brightness across neighbouring lines is a key parameter in understanding the resist clearance between lines, that will affect the next etching step for pattern transfer onto the underlying substrate. These results are important for patterning high-density line structures and nano-device engineering as required for realising state-of-the art laterally stacked group IV multi-channel field effect transistors (FETs).

### 1. Introduction

Fin and nanowire semiconductor nanostructures defined by lithography are the central structural units of top-down fabricated multi-gated field effect transistor (FET) devices. As outlined by IRDS, the FinFET is the key device architecture that could enable logic device scaling until 2025 [1], to be followed by a transition to gate-all-around (GAA) structures such as lateral nanowires or nanosheet FETs with improved electrostatics [2]. The lateral GAA design would eventually evolve into vertically stacked GAAs to gain back the performance loss due to increasing parasitics at tighter pitches [3]. While device architectures are subject to changes, alternatives to Si as the channel material are being explored for increased performance. Such GAA mluti-channel devices include SiGe [4] and Ge [5] are defined normally on strained Ge-containing *epi* layers. Similarly, Ge-based epi layers grown as quantum wells can be used to realise quantum dots by nanoscale gates, and demonstrate spin-based qubits [6,7]. Both, types of devices can benefit

by detailed investigation of the EBL HSQ patterning process on Gecontaining substrates, which is the main topic of this study.

The realisation of prototype FET devices with ultimately small dimensions (width and spacing between the channels) starts routinely with lithography definition followed by reactive-ion etching. Photolithography has been the only method that meets large-scale patterning throughput for the semiconductor industry but comes with its intrinsic limitations in the achievable feature size. While the projections that extreme ultraviolet lithography (EUV) will offer necessary resolution, extending the application of the photon-based lithography in the next decades, alternative methods for ultimately small structures exist [8]. One such method is electron beam lithography (EBL) that finds wide applications for device prototyping in research-based labs, due to the controllable use of tightly focused electron beams (e-beams) with a cross-section down to a nm, at a set but tuneable incident energy (up to 100 kV). EBL patterning can provide access to easily varied (by the design) device architectures for revealing new physical phenomena,

<sup>\*</sup> Corresponding author at: Physical Sciences Department, Munster Technological University (MTU), Rosa Avenue, Bishopstown, Cork T12 P928, Ireland. E-mail address: Nikolay.Petkov@mtu.ie (N. Petkov).

provided that there is a well understood e-beam/substrate interaction and resist processing conditions such as controllable resist thickness, pre-exposure treatments, resist development, etc.

Hydrogen silsesquioxane (HSQ), an inorganic resist, is the resist of choice for a negative EBL patterning process, where the exposed area remains after development, due to its high etch resistance to Cl-based reactive ion etching (RIE) [9,10]. We and others have demonstrated that single and arrays of Si and Ge structures can be readily developed by a combination of HSQ EBL patterning and RIE etching processes [11–13]. The nanofabricated structures can be used as test vehicles for optimising semiconductor manufacturing steps such as dopant technology [14], or as structure-directing patterns for directed self-assembly [15], or as channel material for high performance devices such as nanowire FETs or sensors [11,16].

Generally, the EBL patterning resolution can be improved by reducing the width of the e-beam exposure point-spread function and/or by increasing the resist contrast. The resolution limit for isolated HSQ structures has been reached by reducing the e-beam-substrate interactions on a thin SiN membrane substrate, resulting in structures down to a few nm in diameter [17]. Similarly, introducing a salty NaOH developer (the conventional CMOS-compatible developer is tetramethylammonium hydroxide, TMAH) increases the development rate, respectively improving the HSQ contrast, and results in reduced bridging or footing between closely spaced structures [18]. Focused Heion beam lithography has also shown some advancement in achieving densely packed HSQ structures [19].

Although the salty NaOH developer shows a clear advantage for high resolution/fidelity nanostructures, it is well-known that the Na-ions are highly mobile on silicon oxide surfaces posing ion contamination and device integrity problems. Addressing this issue, it has been demonstrated that the Na-ion contamination can be removed through a rigorous rinsing protocol resulting in capacitor device characteristics with no indication of ionic or metal contamination [20].

Herein we start with comparing the simulated e-beam/substrate interactions for substrates, from Si and Ge, through SiGe with varying Ge content, to GeOI, and relate those to SEM imaging data of line-structures developed in HSQ. We investigate structures with varying width/spacing (starting at 10 nm) of the lines exposed at varying dose and developed by salty NaOH and TMAH developers. We compare the images of the structures, correlating dimensional effects (width and spacing) onto the uniformity, fidelity and pattern resolution at the optimal dose condition, and additionally examine the exposure dose window for well-resolved structures. We further make conclusions based on dimensional metrology applied to the defined structures to establish pattern transfer onto the Ge-containing substrates of the developed HSQ patterns. This will enable the development of high-density structures for the realisation of ultimately small but with increased complexity device architectures.

#### 2. Materials and methods

In order to examine the patterning process of high-density line structures used as fin/nanowire multi-channels in FET devices a test pattern was designed; it is composed of 5 parallel lines with 250 nm length, linked to larger 500 nm wide pads. This test pattern is prototypic for realisation of multiple channels or gates of FET devices, and potentially gated quantum dots and multi-qubit devices. The line width (W) and spacing (S) were varied starting at W = 10 nm and S = 2  $\times$  W and were increased by 5 nm up to W = 50 nm. The test pattern was then exposed by using Elionix 100 kV EBL system on separate pieces coated with 3 w/w % HSQ at 2000 rpm for 30 s and baked at 120 °C for 3 min to give HSQ resist layer with about 40 nm thickness. The HSQ resist solution was freshly prepared using HSQ powder dissolved in dry methyl isobutyl ketone (MIBK) solvent, stored at 5 °C and used within a week from its preparation for exposures. The exposures were done as dose tests starting at the minimal dose possible (determined by the resolution

of the pattern generator and a beam step size of 0.5 nm) at a set current, i.e., when a 1 nA e-beam current was used, the minimal dose calculated was 4000 μC/cm<sup>2</sup>. The dose tests were set as an incremental increase in the dose for the same test pattern by one quarter of the minimal dose until a maximum dose of three times the minimal dose is reached. Such tests were done with Si, Ge, SiGe and GeOI substrates. Note that for the Ge-containing substrates the surface was treated with 20% HCL before spinning the resist. This is an important step related to the adhesion of the HSQ structures to the Ge substrates after devolvement as demonstrated previously by us [12]. We note that after the exposure all substrates were developed using two different strategies at room temperature: i) salty development using a mixture of 1% NaOH and 4%NaCl for 30 s, and ii) TMAH development using commercial developer for 2 min. The pattern transfer was done by reactive ion-etching (RIE) using Cl<sub>2</sub>/N<sub>2</sub> gas mixture in an Oxford Instruments Cobra etcher. The same RIE process was used for the Si, SiGe, Ge and GeOI substrates with etch selectivity close to 3 (substrate to resist etch rate ratio) for the Si and about 2 for the Ge-containing substrates.

After development, the substrates were imaged on a Helios Nanolab dual beam SEM/FIB instrument using 5 kV acceleration voltage and through-lens detector. The instrument was also used to obtain cross-sectional SEM images of the patterned structures. The images were used to determine the optimal dose for high fidelity patterns and the acceptable exposure dose range. The optimal dose in  $\mu\text{C/cm}$  for each substrate was chosen as the one that yields patterns with: i) largest number of well-formed structures from the whole design and ii) best fidelity structures at high density (S = 2  $\times$  W). The acceptable exposure dose range is the dose range from the whole dose test where all structures appear but are under- or over-exposed when compared to the structures obtained under optimal dose conditions.

#### 3. Results and discussion

# 3.1. Si and Ge high-fidelity patterning with HSQ EBL

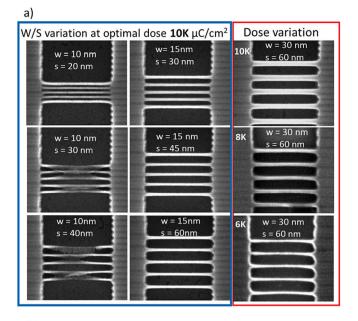

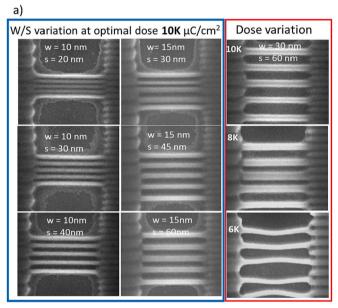

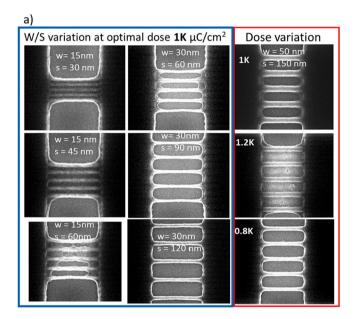

Fig. 1a and b show images of the HSQ patterns on Si and Ge, developed by using salty development. As seen and supported by our Monte-Carlo simulations (see below for further explanation), the optimal dose for high fidelity features on Si is much higher than the one for Ge, 10,000 vs 6000  $\mu\text{C/cm}^2,$  respectively. For both substrates, there is also a variation in the fidelity of the structures as a function of the spacing between neighbouring lines (see images under W/S variation). For example, the lines with W = 10 nm developed on Si (first column in Fig. 1a) showed falling-over structures as spacing increases. This effect is attributed to under-exposure, and is further supported by the observation that the falling-over parts of the lines are seen towards the middle, where normally the effective dose increase due to connecting pads is lower. For a small nominal increase in the width of the line, W = 15 nm, uniformly formed lines were seen for all different variations in the spacing. In comparison, the overall fidelity of the lines developed on Ge is far inferior. The dose of 6 K  $\mu$ C/cm<sup>2</sup> was determined as optimal, yet falling-over or bridging are seen for many of the structures. From the images in the dose variation column (3rd column in Fig. 1a and b), where a "relaxed" (W = 30 nm) design of the lines is compared, it is clear that the dose range for acceptable, good uniformity structures on Si is covering a wider processing window (6–10,000 μC/cm<sup>2</sup>). In contrast, the dose range on Ge is centred around the optimal dose of 6000, with largely over-or under-exposed patterns outside  $\pm 1000 \ \mu\text{C/cm}^2$  of the optimal dose.

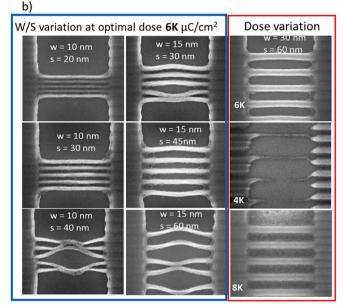

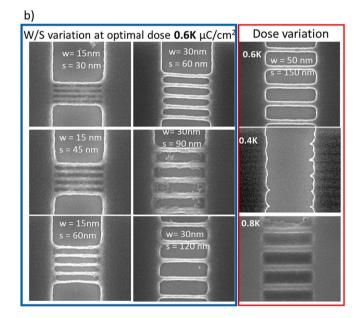

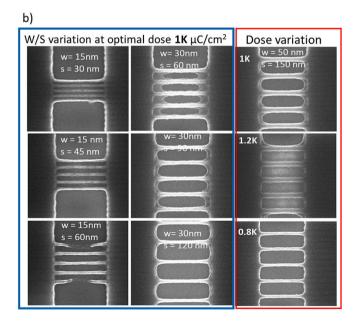

We further examined the optimal dose and the acceptable exposure dose range for structures patterned on Si and Ge but developed using the TMAH developer (Fig. 2). It is well documented that the TMAH development results in reduced fidelity of structures, and poor uniformity due to a lower HSQ development rate in comparison to the salty developer [18]. As a result, there is increased bridging or footing between closely spaced structures for all dimensions but most prominently for the

**Fig. 1.** Selected SEM images from the whole dose test exposures obtained by using salty developer for a) Si and b) Ge. The images are grouped as i) W/S variation at optimal dose of 10,000 and 6000  $\mu$ C/cm² for Si and Ge, respectively (enclosed in blue) and ii) dose variation at a set "relaxed" (large-width) design of the lines, W = 30 nm and S = 60 nm (enclosed in red). (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

dimensions lower than 30 nm (1st column in Fig. 2a and b), with largely unresolved features at small widths, W = 10 nm (see SI, Fig. S1). For both the Si and Ge substrates, the structures that showed reasonably good fidelity are with lower density,  $S=3\times W$  and larger W ( $\geq \! 30$  nm). Generally, the fidelity of the line structures at varying W and S are inferior for the Ge substrate but the differences between the features on Si and Ge are not as large as the ones seen when the salty developer was used. However, similarly to the salty development, the acceptable dose window on Ge is very limited, as seen on the dose variation column, 3rd column in Fig. 2b.

Figs. 1 and 2 clearly demonstrate that the HSQ EBL process, using both salty and TMAH developers on Ge is much more limited with respect to obtainable smallest dimensions (W and S), their uniformity

**Fig. 2.** Selected SEM images from the whole dose test exposures obtained using TMAH developer for a) Si and b) Ge. The images are grouped as i) W/S variation at optimal dose of 1000 and  $600~\mu\text{C/cm}^2$  for Si and Ge, respectively (enclosed in blue) and ii) dose variation at set "relaxed" (large-width) design of the lines, W = 50 nm and S = 150 nm (enclosed in red). (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

and fidelity in comparison to Si. The main reasons for these differences, and specifically the influence of the Ge substrate over the exposures have not been investigated in detail yet and deserve special attention.

The type of substrate and the incident acceleration voltage are directly linked to the exposure point-spread function and associated proximity effect. This add-on dose during the exposure of each structure by its neighbours is critical for achieving high-density features. While the secondary-electron (SE) emission contributes to resist exposure close to the incident e-beam, due to the small electron free path of the low energy SEs, the range and intensity of the back scattered electron (BSE) is detrimental for controlling the add-on dose and possible overexposure effect, respectively loss of well-defined line patterns [17]. Briefly, the dependence of the SEs emission yield to the type of substrate can be

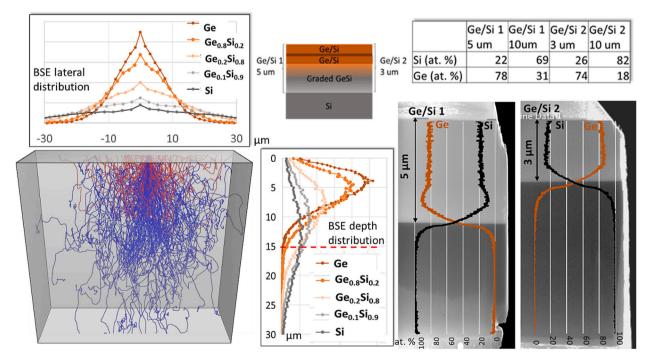

calculated, and shows a small increase within the atomic number for Z = 10 to 30 but it is insignificantly low for high (100 kV) incident electrons (see SI, Fig. S2) [21]. Similarly, the spread of the incident electron beams due to forward scattering in thin resists (such as HSQ resist used here, 35-40 nm) and under highly accelerated incident beams is negligible. However, the contribution of the BSEs produced in the substrate to the exposure point-spread function is significant and increases with the atomic number (see SI, Fig. S2). The BSE distribution and yield, in depth and laterally, can be simulated for different substrates by using Monte-Carlo simulation codes such as CASINO [22]. Recently, a method for the experimental determination of these parameters has been developed and showed excellent comparison with the Monte-Carlo predictions [23]. Fig. 3 shows the Monte-Carlo simulated electron trajectories (in blue) and formed BSE trajectories (in red) after the interaction of the focused 100 kV incident electron beam with the Ge<sub>0.8</sub>Si<sub>0.2</sub> substrate. The lateral and depth distribution plots of the BSEs for Ge, Si and various Ge/Si alloy concentrations at 100 kV are compared in Fig. 3. It can be seen that the Ge substrate results in a much higher (about 5 times higher than Si) number of BSE produced laterally and in the depth of the substrate. In parallel, the Ge/Si alloys showed a gradual decrease in the number of BSEs formed (lateral and in depth) with the increase of the Si content, while the BSEs depth range increases with the Si content; the smallest BSE range is at about 10  $\mu m$  for pure Ge and high Ge content substrates. The Monte-Carlo calculations suggest that the limitations seen for Ge HSQ EBL process are directly linked to the BSEs generation and that those can be minimized by reducing the Ge content in the substrates

The BSEs formation is also directly linked to the incident acceleration voltage (see SI, Fig. S3), i.e. going from 100 to 30 kV, there is about tenfold increase in the number of the BSEs (in both lateral and depth directions), while the BSEs range for Ge is reduced from 10 to 3  $\mu m$ . This demonstrates the clear advantage of using high (100 kV) systems for patterning Ge substrates. The higher range of the BSEs seen for high-kV incident beams has a specific advantage for Ge-containing substrates in the form of epitaxially grown layers on Si. If the grown layers are

relatively thin (1–3  $\mu m$ ), the high acceleration "pushes" down the BSEs depth maxima below the thickness of Ge-epi layers, and into the Si support wafer. This results in a reduced amount of the BSEs formed in comparison to "pure" Ge substrates, consquently favourable exposure conditions, e.g. reduced proximity effect and better fidelity for highly dense structures. To demonstrate this and to support the argument that reduced Ge content in the substrate is advantageous for the HSQ patterning, we performed HSQ exposure tests with two substrates having different Ge/Si epi layer thicknesses on Si, schematically shown in Fig. 3.

#### 3.2. Controlling EBL patterning on Ge-based substrates

Two Ge/Si substrates on Si(001) were grown by reduced pressure chemical vapor deposition [24,25]. While the Ge/Si\_1 substrate has epilayers total thickness of 5  $\mu m$ , for the Ge/Si\_2 substrate the thickness was reduced to 3  $\mu m$ . Notably, at the top there are two cladding layers, each 100 nm with  $Ge_{0.8}Si_{0.2}$  composition, that are used to confine a 20 nm lightly strained Ge quantum well (dark brown on the schematics). The rest of the Ge/Si epi stack contains micron-sized graded Ge/Si buffer layers on top of the Si carrier wafer. The averaged Ge at. % content in the epi-grown layers for the two substrates studied was determined by EDS line scans on cross-sectioned samples. The scans were done for 5 and 3 μm lengths, and showed values of about 78 and 74 at. % Ge for the Ge/ Si 1 and the Ge/Si 2, respectively (see Table in Fig. 3). These values are lower than the nominal 80 at. % Ge in the Ge/Si cladding layers and reflect the presence of graded Ge/Si layers close to the Si carrier substrate (see EDS profiles in Fig. 3). On the other hand, when the EDS line scans were done for a total of 15 µm, the averaged Ge content observed was 31 and 18 at. % for the Ge/Si 1 and Ge/Si 2 substrates, respectively. Clearly, the observed reduction of the Ge content is due to the higher contribution from the Si carrier wafer along the 15 µm scans; considerably higher in the Ge/Si\_2 substrate. The longer (15  $\mu m$ ) total length of the line scans was chosen to reflect the depth range of BSEs formed in Ge<sub>0.8</sub>Si<sub>0.2</sub> for 100 kV incident beams, as depicted in the BSEs depth

Fig. 3. *E*-beam deceleration trajectories (in blue) and trajectories generating BSEs (in red) calculated using CASINO software for  $Ge_{0.8}Si_{0.2}$  substrate, and the BSEs lateral and depth distribution plots for various Ge/Si substrates. Schematics of the  $Ge/Si_1$  and  $Ge/Si_2$  supports used in the study with the corresponding cross-sectional EDS line profiles. Table summarizing the averaged Si and Ge at. % for  $Ge/Si_1$  and  $Ge/Si_2$  supports measured across the Ge/Si layers (5 and 3  $\mu$ m) and across total of 10  $\mu$ m for both substrates. The length of 15  $\mu$ m for the total EDS line scan was chosen because that is the range of BSEs formed in Ge, seen in the BSE depth distribution plot. (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

profile simulations in Fig. 3.

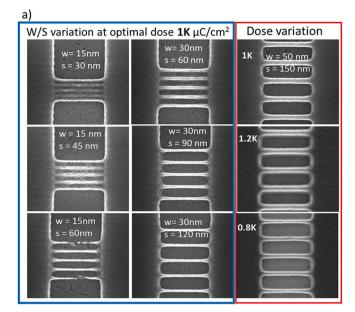

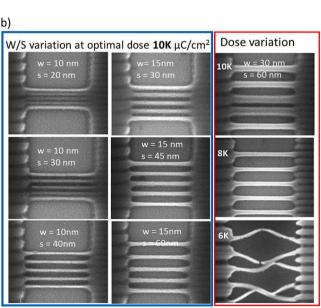

This "dilution" of the Ge content along the 15  $\mu m$  depth, and consequently the lower number of BSEs formed is responsible for the differences in dose tests seen for the Ge/Si substrates and the "pure" Ge substrate. The BSEs lateral distribution plots in Fig. 3 show a gradual decrease in the number of BSEs formed as the Ge content in the substrates is decreased. Within the 15  $\mu m$  depth, sample Ge/Si\_2 is with a composition close to Ge0.2Si0.8, as determined by the EDX measurements, and the simulations show considerably lower number BSEs for this composition than for the Ge0.8Si0.2 (note that nominally the top layers have Ge0.8Si0.2/Ge/ Ge0.8Si0.2 composition). Sample Ge/Si\_1 has higher Ge content within the 15  $\mu m$  depth than the Ge/Si\_2 sample, but still much lower than the nominal Ge0.8Si0.2 composition. Fig. 4 shows the comparison of the HSQ dose tests obtained at 10000  $\mu$ C/cm² dose

and after salty development for the two Ge/Si substrates used. These results can be directly compared to the images in Fig. 1a and b, showing the dose tests for Si and Ge, respectively. Clearly, the optimal dose for both Ge/Si substrates is closer to that for the Si substrate, and the Ge/Si\_1 sample shows consistently over-exposed structures at that dose for than the Ge/Si\_2 sample. Moreover, the Ge/Si\_2 exposures are with better fidelity, and uniformity almost as good as the "pure" Si substrate. The accessible dose window, seen in the dose variation column for both substrates, however is still not as good as for the Si exposures, but much better than for Ge. Similarly, Fig. 5 compares the dose test exposures at  $1000~\mu\text{C/cm}^2$  for both Ge/Si substrates, processed by using the TMAH developer. As expected the smallest width, W = 10 nm, structures were not resolved and for all structures, the uniformity and the fidelity were worse than when using the salty development. While the TMAH

Fig. 4. Selected SEM images from the whole dose test exposures obtained by using salty developer for a) Ge/Si\_1 and b) Ge/Si\_2. For both substrates the images are grouped as i) W/S variation at dose of 10,000 (enclosed in blue) and ii) dose variation at a set "relaxed" (large-width) design of the lines,  $W=30\,$  nm and  $S=60\,$  nm (enclosed in red). (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

**Fig. 5.** Selected SEM images from the whole dose test exposures obtained by using TMAH developer for a) Ge/Si\_1 and b) Ge/Si\_2. For both substrates the images are grouped as i) W/S variation at dose of 1000 (enclosed in blue) and ii) dose variation at a set "relaxed" (large-width) design of the lines, W=50~nm and S=150~nm (enclosed in red). (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

developed patterns show smaller differences between both Ge/Si samples, generally the patterns on the Ge/Si\_2 substrate are with higher fidelity and their nominal dimensions and overall appearance are closer to the "pure" Si TMAH developed sample. In short, the dose test patterns on both Ge/Si substrates, but most evidently on the Ge/Si\_2 substrate, were closer to the "pure" Si and substantially different than the "pure" Ge substrate. We attribute these observations to the Ge "dilution", down to <20 at. % Ge, in the first 15  $\mu m$  from the substrate surface where the majority of BSEs are formed as supported by the Monte-Carlo simulations.

We further demonstrate HSQ test exposures on GeOI (see SI, Fig. S4) where the thin Ge device layer contributes to <1 at. %, based on EDS line scans, in the first 15  $\mu m$  from the substrate. The obtained SEM images show features that are very close to the dimensions, uniformity and fidelity seen for the "pure" Si (Fig. 1a), which once more reveals the importance of minimizing the Ge contribution/thickness in the top surface of the substrate. Both the Ge quantum well structures (Ge/Si 1 and Ge/Si 2 substrates) as well as the GeOI substrates are viable substrates for the realisation of multi-GAA FET devices and potentially gated quantum dots devices for quantum computing. Such future device architectures can make use of the high density/fidelity patterning process developed in this study. Herein we only show examples of undercut, multi-wire Ge structures formed by using the developed salty HSQ EBL process, followed by selective Cl2 reactive ion etching (RIE) into GeOI and vapor-HF undercut (SI, Fig. S5) as the first steps in realising such devices. In the next section we illustrate the importance of the dimensional metrology data for obtaining comprehensive information about the fidelity of the patterning process.

#### 3.3. Dimensional metrology

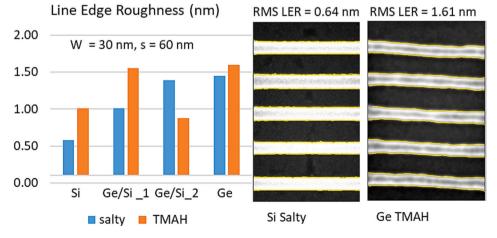

One of the first dimensional metrology parameters to consider when evaluating a resist pattering process is the line edge roughness (LER). We note that the HSQ resist has superior LER properties when compared to other resists for the EUV technology [8]. Fig. 6 summarises the LER data from the dose test exposures for structures with "relaxed" (W = 30 nm and S = 60 nm) dimensions obtained by using salty and TMAH development on the various substrates studied. We used Analyse stripes plugin for ImageJ [26] to post-process the SEM images and extract root mean square (RMS) estimates of the LER for all images obtained. The actual image acquisition was done by auto brightness/contrast adjustment before each image is taken. Part of the procedure is image pixel grey value equilibration and binarization. Examples of the region of interest, the thresholding levels, and the line edge profiles, used to calculate the LER values for two distinct cases are also shown in Fig. 6.

We note that the LERs values calculated are around 1 nm and compare well with the values published by N. Mojarad, et al. [8]. The lowest LER values are for the Si substrate and largest are for the Ge, again reflecting the negative effects of the Ge during the exposure. From the LER analysis of all images obtained we can conclude that, the salty development produces structures with consistently lower LER values across all different substrates. The LERs values presented are averaged values for 3 separate repetitions of the same dose test pattern on different substrates. Plots like the one presented in Fig. 6a were calculated for structures with other widths showing similar trend, i.e., higher LER values were observed for TMAH developer and for Ge substrates. We also note that the observed grooved side walls of the large pads linked to the multiple lines in the SEM images seen in Figs. 1 and 4 are result of the pattern generation scan process, as well as the patterning step size (which was 0.5 nm). We are confident that the observed side wall roughness which is related to the step size and the resolution of the pattern generator are only seen on the large pads. This is explained by the observation of the same periodicity of the grooves formed on the top surface of the large pads as the grooves on the side wall. It is interesting that this effect is much more pronounced for the salty NaOH developer than for the TMAH, which deserves a separate investigation, but can be linked to faster and more aggressive developer process when using salty NaOH.

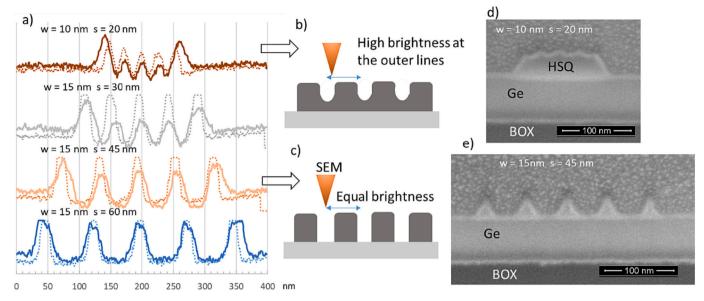

The dimensional metrology performed by SEM and AFM provides the most commonly used data sets for the evaluation of the lithography figures-of-merit [27]. However, a correlative analysis data set, i.e., imaging the same area of interest by different measurement modality, can provide additional critical information for the pattering process. For example, structures similar to the SEM images shown in Fig. 1a and b for the smallest widths, W = 10 nm and spacing,  $S = 2 \times W$ , are generally described in several published results as well-resolved structures with high fidelity [18,19]. However, upon closer inspection, the SEM images show varying brightness of the lines, with the highest brightness for the two outer lines. The SEM brightness profiles across the patterned lines for structures developed on GeOI using salty (dotted lines) and TMAH (continuous lines) developers are summarised in Fig. 7a. While for most of the structures obtained by salty development, the brightness levels are even across all four lines, (excluding the W = 10 nm; S = 20 nm pattern), for the TMAH developed structures several of the profiles have outer lines showing higher brightness. Moreover, by correlating the SEM brightness profiles shown in Fig. 7a to cross-sectional images (Fig. 7d and e) we establish that patterns having high brightness of the outer lines, are far from expected (Fig. 7d), and lack resist clearance between neighbouring lines. This generally affects the subsequent etching step for forming well-defined fin or nanowire structures. An example of a well-defined Ge nanowire array using GeOI substrate and following the

Fig. 6. Line edge roughness data for nominal W = 30 nm structures obtained by using salty and TMAH developers on the various substrates studied, and examples of ImageJ processed SEM images for outlining the line edge profile in yellow that is used to calculate RMS line edge roughness values. (For interpretation of the references to colour in this figure legend, the reader is referred to the web version of this article.)

Fig. 7. a) Brightness intensity profiles extracted from a set of SEM images taken across line structures developed on Si with nominal dimensions shown in the insets. Continuous and dotted profiles denote TMAH and salty development, respectively. b) and c) schematics of two borderline cases depicting idealised cross-sectional representations corresponding to SEM profiles mentioned in the insets. d) and e) cross-sectional SEM images of HSQ patterns with nominal dimensions shown in the insets, both structures were obtained by salty development and correspond to dotted profiles in a).

process sequence of i) HSQ patterning using salty developer, ii) highly selective Cl<sub>2</sub>-based RIE and iii) buried oxide undercut, is shown on SI, Fig. 5. This pattern transfer process will only be possible if the HSQ resist clearance is full, as seen on the cross-sectional image in Fig. 7e and the corresponding SEM brightness profile in Fig. 7a.

Based on the plan-view SEM brightness profiles shown in Fig. 7a, we postulate that there is a general dependence in the brightness variation that can be used as a key metrology parameter for understanding the resist clearance and the success and fidelity of the etched structures. High fidelity patterns are only obtained if the extracted SEM brightness values for all lines from the profile are very close, while the higher the difference in brightness between the outer lines and the inner neighbouring lines in the pattern, the poorer the resist clearance will be. These two borderline cases are schematically depicted in Fig. 7b and c. We note that the quantification of the thickness values in nm of isolated structures has been modelled and linked to SEM brightness variations at the edges of the structures [28]. The data suggested that for lower voltages (< 5 kV) of the incident e-beams, there is direct relationship between the emission of the SEs at the edges and the absolute value of the layer thickness, making top-down SEM a suitable metrology tool for thickness determination. Herein, we complement these studies by providing a qualitative method for determining if there is acceptable resist clearance between neighbouring lines in the patter that allows for successful pattern transfer in the underlaying substrate. This is important as using AFM to determine the resist thickness between neighbouring lines in an array is limited for high density and small width structures due to the complex tip/surface interactions.

# 4. Conclusions

We present a systematic study of the HSQ EBL process for Gecontaining substrates revealing the limitations in achieving the smallest obtainable features, their uniformity, and fidelity, in comparison to Si. The effect of diminishing the Ge-content in the top surface where the incident e-beam/substrate interactions are, was identified as key parameter for achieving improved fidelity and resolution of the features. This was established by using a combination of Monte-Carlo simulations of the e-beam/substrate interactions and dose test exposures on a variety of substrates with varying Ge-content in the top surface such as Ge/Si

heterostructure *epi*-layers and GeOI. We showed through extensive SEM imaging for a variety of dose patterns that reduced Ge content is advantageous for minimizing the BSEs formation, that is detrimental for the fidelity of the structures. In parallel, a 100 kV e-beam further "pushes" the BSEs deeper in the carrier Si substrate, which is an advantage compared to 50 or 30 kV e-beam. All these factors should be considered when designing the overall EBL patterning process for the Ge-containing substrates by proper design of the thickness of the Ge epigrowth so that reduced BSE formation is met, but still having epi layers with acceptable crystal quality.

We further link our EBL studies to dimensional metrology parameters such as LER and resist clearance between lines to establish the applicability of the HSQ process for device manufacturing. In this respect the variation in the SEM brightness levels across neighbouring lines was identified as key parameter showing that although line patterns may appear resolved in the SEM images the resist clearance between lines might not be complete. Finally, obtained results were used to make conclusions on the applicability of the HSQ EBL patterning process, and how it affects the development of an actual fabrication sequence for engineering devices with relevance to quantum information.

## **Declaration of Competing Interest**

The authors declare the following financial interests/personal relationships which may be considered as potential competing interests.

Nikolay Petkov reports financial support was provided by Science Foundation Ireland. Giorgos Fagas reports financial support was provided by European Commission.

# Data availability

Data will be made available on request.

# Acknowledgements

This work was supported by the European Union's Horizon 2020 project ASCENT+ (GA No 871130) and by the Frontiers for Partnership programme of the Science Ireland Foundation (Project ID: 21/FFP-A/

9257).

#### Appendix A. Supplementary data

Supplementary data to this article can be found online at https://doi.org/10.1016/j.mee.2023.112071.

#### References

- [1] https://irds.ieee.org/editions/2022/more-moore, 2023.

- [2] S. Mukesh, J. Zhang, A Review of the Gate-All-around Nanosheet FET Process Opportunities, Electronics 11 (2022) 3589, https://doi.org/10.3390/ electronics11213589.

- [3] C.-E. Tsai, et al., 6 Stacked Ge0.95Si0.05 nGAAFETs without parasitic channels by wet etching, in: 2022 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), 978–1–6654-0923-0, 2022, https://doi.org/10.1109/ VLSI-TSA54299 2022 9770969

- [4] C.-L. Chu, et al., Stacked SiGe nanosheets p-FET for Sub-3 nm logic applications, Sci. Rep. 13 (2023) 9433, https://doi.org/10.1038/s41598-023-36614-2.

- [5] B. Duriez, et al., Scaled p-Channel Ge FinFET with Optimized Gate Stack and Record Performance Integrated on 300mm Si Wafers, Technical Digest -International Electron Devices Meeting, IEDM, 6724666, 20.1.1-20.1.4, 2013, https://doi.org/10.1109/IEDM.2013.6724666.

- [6] L.C. Camenzind, et al., A hole spin qubit in a fin field-effect transistor above 4 kelvin, Nat. Electron 5 (2022) 178–183, https://doi.org/10.1038/s41928-022-00722

- [7] N.W. Hendrickx, et al., A four-qubit germanium quantum processor, Nature 580 (2021), https://doi.org/10.1038/s41586-021-03332-6.

- [8] N. Mojarad, et al., Beyond EUV lithography: a comparative study of efficient photoresists' performance, Sci. Rep. 5 (2015) 9235, https://doi.org/10.1038/ srep09235

- [9] K. Yamazaki, H. Namatsu, 5-nm-order Electron-beam lithography for Nanodevice fabrication, Jpn. J. Appl. Phys. (2004), https://doi.org/10.1143/jjap.43.3767, 1

- [10] J.K.W. Yang, et al., Sub-15nm nanoimprint molds and pattern transfer, J. Vac. Sci. Technol. B 24 (2006) 3157, https://doi.org/10.1116/1.3264670.

- [11] Y.M. Georgiev, et al., Detection of ultra-low protein concentrations with the simplest possible field effect transistor, Nanotechnology 30 (2019), 324001, https://doi.org/10.1088/1361-6528/ab192c.

- [12] R.G. Hobbs, et al., Resist-substrate interface tailoring for generating high-density arrays of Ge and Bi2Se3 nanowires by electron beam lithography, J. Vac. Sci. Technol. B 30 (2012), 041602, https://doi.org/10.1116/1.4724302.

- [13] Ahmad Echresh, et al., Electrical characterization of germanium nanowires using a symmetric hall Bar configuration: size and shape dependence, Nanomaterials 2021 (2017) 11, https://doi.org/10.3390/nano11112917.

- [14] Ray Duffy, et al., Access resistance reduction in Ge nanowires and substrates based on non-destructive gas-source dopant in-diffusion, J. Mater. Chem. C 43 (2014) 9248–9257, https://doi.org/10.1039/C4TC02018A.

- [15] R.G. Hobbs, et al., Selective sidewall wetting of polymer blocks in hydrogen silesquioxane directed self-assembly of PS-b-PDMS, J. D. ACS Appl. Mater. Inter. 4 (2012) 4637–4642, https://doi.org/10.1021/am301012p.

- [16] L. Gaben, et al., HSQ lithography for nanowire first integration: an interesting alternative for gate last fabrication of Sub-7nm Stacked Nanowire FETs, in: Extended Abstracts of the 2016 International Conference on Solid State Devices and Materials, Tsukuba, 2016, pp. 619–620.

- [17] V.R. Manfrinato, et al., Resolution limits of electron-beam lithography towards the atomic scale, Nano Lett. 13 (4) (2014) 1555–1558, https://doi.org/10.1021/ pl304715p

- [18] J.K.W. Yanga, K.K. Berggren, Using high-contrast salty development of hydrogen silsesquioxane for sub-10-nm half-pitch lithography, J. Vac. Sci. Technol. B 25 (2007) 6, https://doi.org/10.1116/1.2801881.

- [19] D. Winston, et al., Scanning-helium-ion-beam lithography with hydrogen silsesquioxane resist, J. Vac. Sci. Technol. B 27 (2009) 6, https://doi.org/10.1116/ 1.3250204.

- [20] M. Brink, et al., Contamination mitigation of hydrogen silsesquioxane resist processed with Na<sup>-</sup> - containing developer for nanoscale CMOS device patterning, J. Vac. Sci. Technol. B 32 (2014), 022204, https://doi.org/10.1116/1.4867653.

- [21] https://www.globalsino.com/EM/page4803.html, 2023.

- [22] https://www.gegi.usherbrooke.ca/casino/, 2023.

- [23] D.A. Czaplewski, The range and intensity of backscattered electrons for use in the creation of high fidelity electron beam lithography patterns, Nanotechnology 24 (2013) 305302, https://doi.org/10.1088/0957-4484/24/30/305302.

- [24] C. Morrison, M. Myronov, Electronic transport anisotropy of 2D carriers in biaxial compressive strained germanium, Appl. Phys. Lett. 111, 19 (2017), 192103, https://doi.org/10.1063/1.5010933.

- [25] M. Myronov, et al., High quality strained Ge Epilayers on a Si0.2Ge0.8/Ge/Si(100) global strain-tuning platform, Electrochem. Solid-State Lett. 13 (11) (2010) H388–H390, https://doi.org/10.1149/1.3482159.

- [26] https://imagejdocu.list.lu/doku.php?id=macro:analyze\_stripes#installation,

- [27] T.-F. Yao, et al., In-line metrology of nanoscale features in semiconductor manufacturing systems. Precis. Eng. 47 (2016).

- [28] K. Tugrul, et al., Estimating step heights from top-down SEM images, Microsc. Microanal. 25 (2019) 903–911, https://doi.org/10.1017/s143192761900062x.