#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### Permanent WRAP URL:

http://wrap.warwick.ac.uk/182629

#### Copyright and reuse:

This thesis is made available online and is protected by original copyright. Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

### Benchmarking the Robustness performance of SiC cascode JFETS against contemporary devices using simulations and experimental measurements

by

### Sunday Nereus Akor Agbo

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in Engineering

University of Warwick, School of Engineering January 2023

## Table of Contents

| Acknowl     | edgements                                                     | iv   |

|-------------|---------------------------------------------------------------|------|

| Declarat    | ion                                                           | V    |

| List of Pu  | ublished Work                                                 | vi   |

| Abstract    |                                                               | vii  |

| Abbrevia    | itions                                                        | viii |

| List of Fig | gures                                                         | x    |

| List of Ta  | ibles                                                         | xvi  |

| Chapter     | 1. Introduction                                               | 1    |

| 1.1.        | Background                                                    | 1    |

| 1.2.        | Aims and Objectives                                           | 3    |

| 1.3.        | Key Contributions                                             | 4    |

| 1.4.        | Thesis Outline                                                | 5    |

| Refere      | ences                                                         | 6    |

| Chapter     | 2. SiC Cascode JFET Modelling                                 | 7    |

| 2.1.        | Introduction to Cascode                                       | 7    |

| 2.2.        | Performance and advantages of SiC Cascode JFETs               | 11   |

| 2.3.        | Applications of Cascode JFET                                  | 14   |

| 2.4.        | Challenges of SiC Cascode JFET                                | 16   |

| 2.5.        | Fundamentals of Finite element modelling (FEM)                | 16   |

| •           | Energy Band Gap                                               | 17   |

| •           | Fermi Statistics                                              | 17   |

| •           | Intrinsic Carrier Concentration (n <sub>i</sub> )             | 17   |

| •           | Carrier mobility ( $\mu_n$ and $\mu_p$ )                      | 18   |

| •           | Poisson's Equation                                            | 19   |

| •           | Carrier continuity equations                                  | 20   |

| •           | Thermal Model                                                 | 23   |

| 2.6.        | Finite Element Modelling (FEM) of SiC Cascode JFETs           | 25   |

| •           | Structure Geometry and Mesh                                   | 25   |

| •           | Static characteristics                                        | 27   |

| •           | Mixed mode simulation (Double pulse test)                     | 29   |

| Refere      | ence                                                          |      |

| Chapter     | 3. AVALANCHE IN CASCODE JFET                                  |      |

| 3.1.        | Introduction to Unclamped Inductive Switching (UIS)           | 46   |

| 3.2.        | UIS theory                                                    | 49   |

| 3.3.        | Experimental Measurements of Single Shot UIS in Cascode JFETs | 50   |

| 3.4.         | Bench Marking the SiC Cascode JFET UIS Performance                                        | 54  |

|--------------|-------------------------------------------------------------------------------------------|-----|

| 3.5.         | UIS in Stand-alone SiC JFETs                                                              | 56  |

| •            | Impact of JFET gate resistance on the UIS performance                                     | 57  |

| •            | Impact of avalanche current on the UIS performance                                        | 59  |

| 3.6.         | Failure Analysis of SiC Cascode JEFT Under UIS                                            | 61  |

| 3.7.<br>simu | Finite Element Analysis (FEA) simulations of failure during unclamped i<br>Ilations (UIS) |     |

| •            | SiC trench MOSFET UIS simulation                                                          | 66  |

| •            | SiC cascode JFET UIS simulation                                                           | 68  |

| 3.8.         | Experimental Measurement of Repetitive UIS                                                | 73  |

| 3.9.         | Conclusion                                                                                | 77  |

| Refe         | rences                                                                                    | 78  |

| Chapte       | r 4. Short Circuit Performance of SiC Cascode JFETs                                       | 80  |

| 4.1.         | Introduction                                                                              | 80  |

| 4.2.         | Theory of Short Circuit Current Flow                                                      | 82  |

| •            | SPICE Simulations of Short Circuits                                                       | 84  |

| 4.3.         | Short Circuit Benchmarking for 650 V Power Devices                                        | 86  |

| 4.4.         | Simulations of short circuit in SiC MOSFETs                                               | 93  |

| •            | Impact of circuit parameters on SiC MOSFET short circuit current                          | 93  |

| Im           | npact of VGS on short circuit transient                                                   | 93  |

| Im           | npact of external gate resistance ( <i>R<sub>G</sub></i> ) on short circuit transient:    |     |

| •            | Impact of Fabrication Parameters on Short circuit                                         | 99  |

| 4.5.         | Simulations of Short Circuit in SiC Cascode JFETs                                         | 106 |

| •            | Impact of Parameters on SiC Cascode JFETs Short Circuit Currents                          | 106 |

| •            | Cascode JFET failure during short circuit operation                                       | 118 |

| 4.6.         | Conclusion                                                                                | 127 |

| Refe         | rences                                                                                    | 129 |

| Chapte       | r 5. Short Circuit performance of SiC CASCODE JFETs in Parallel                           | 132 |

| 5.1.         | Introduction                                                                              | 132 |

| 5.2.         | Experimental setup and measurements                                                       | 135 |

| 5.3.         | Simulation of short circuit in parallel SiC planar MOSFET                                 |     |

| •            | Varying $V_{TH}$                                                                          | 141 |

| •            | Varying R <sub>G</sub>                                                                    | 145 |

| •            | Varying Temperatures                                                                      | 148 |

| •            | Varying parasitic inductance                                                              | 150 |

| 5.4.         | Simulation of short circuit in parallel SiC trench MOSFET.                                | 153 |

| •            | Varying V <sub>TH</sub>                                                                   | 154 |

| •            | Varying R <sub>G</sub>                                                                    | 157 |

| ٠         | Varying Temperatures                                     |     |

|-----------|----------------------------------------------------------|-----|

| •         | Varying parasitic inductance                             |     |

| 5.5.      | Simulation of short circuit in parallel SiC Cascode JFET |     |

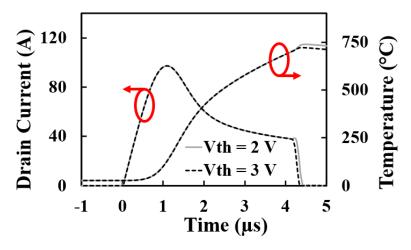

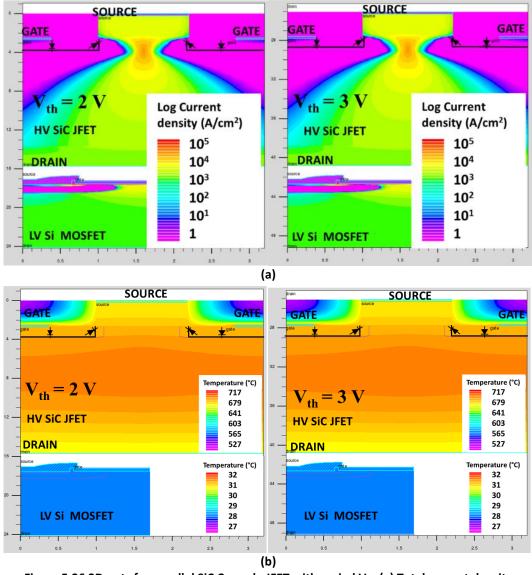

| •         | Varying $V_{TH}$                                         |     |

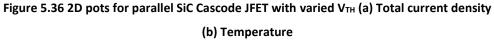

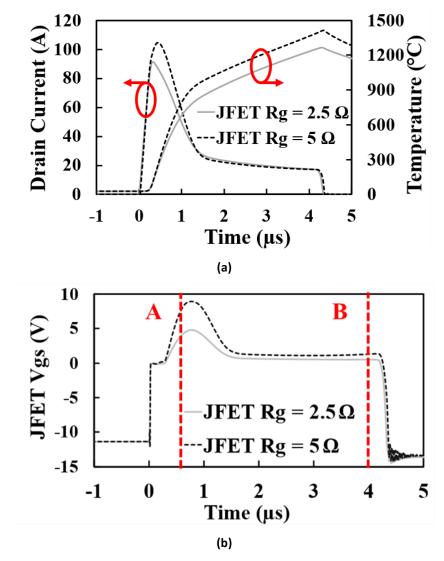

| •         | Varying JFET Gate Resistance (JFET-R <sub>G</sub> )      |     |

| •         | Varying JFET Temperature (T <sub>CASE</sub> )            |     |

| 5.6.      | Conclusion                                               |     |

| Refere    | nces                                                     |     |

| Chapter ( | 6. CONCLUSION AND FUTURE WORK                            |     |

| 6.1.      | Conclusions                                              |     |

| 6.2.      | Future work                                              |     |

| •         | Structures                                               |     |

| •         | Multi-device packages                                    | 176 |

| •         | Harsh environments                                       |     |

| APPENDI   | X A TCAD script                                          |     |

| APPEN     | IDIX A1. High Voltage JFET structure                     |     |

| APPEN     | IDIX A2. Low Voltage MOSFET structure                    |     |

| APPEN     | IDIX A3. Cascode JFET Double Pulse test                  |     |

| APPEN     | IDIX A4. Cascode JFET UIS                                |     |

| APPEN     | IDIX A5. Cascode JFET Short circuit                      |     |

| APPENDI   | X B JFET Cell Structure                                  |     |

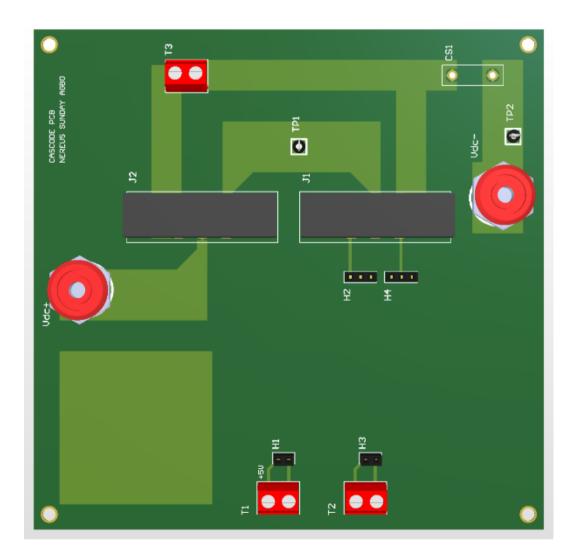

| APPENDI   | X C PCB Design drawings                                  |     |

| APPEN     | IDIX C1. Schematic drawings                              |     |

| APPEN     | IDIX C2. Layout drawings                                 |     |

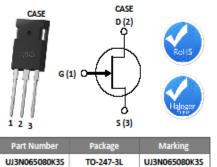

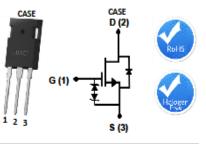

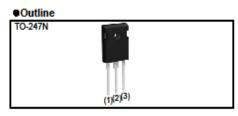

| APPENDI   | X D Reference Datasheets                                 | 193 |

| APPEN     | IDIX D1. SiC Standalone JFET datasheet                   |     |

| APPEN     | IDIX D2. SiC Cascode JFET datasheet.                     |     |

| APPEN     | IDIX D3. SiC Trench MOSFET datasheet.                    | 195 |

| APPEN     | IDIX D4. SiC Planar MOSFET datasheet                     | 196 |

| APPEN     | IDIX D5. Si Superjuction MOSFET datasheet                |     |

### Acknowledgements

First, I would like to thank my supervisor Olayiwola Alatise for his immense patience and support throughout my thesis. Also, many thanks to my second supervisor Jose Ortiz-Gonzalez for helping me with a fresh perspective in times of doubt. You both believed in me and provided invaluable guidance over the course of my research. Thanks for believing in me. I would also like to acknowledge the support from everybody in the Power Electronics Applications and Technology in Energy Research (PEATER) group. Everyone was always approachable, and ready to help and collaborate which made my research a lot easier. To Simon Mendy, Robert Wu, Erfan Bashar, Guy Baker, Benjamin Renz, Kyrylo Melnyk, and Nikolaos losifidis, I am very appreciative of your expertise, input, and friendship as well.

I am immensely thankful to my parents and siblings for their support, love, and understanding through the whole process. Finally, I would like to thank Jenifer, Douglas, Henry, Sylvia, Will, Linda, and Nazia, you all always made it a priority to check on me throughout the stressful period of my research.

### Declaration

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has not been submitted for a degree at any other University. All the work described in this thesis was carried out by the author or under his direction except where specifically stated.

Parts of this thesis have been published by the author during the period of study in the school of Engineering at the University of Warwick from February 2019 until December 2022. They are given in full detail in the Publication List section.

> Sunday N. A. Agbo January 2023

### List of Published Work

- S. N. Agbo, J. Ortiz-Gonzalez, R. Wu, and O. Alatise, "Characterisation of Unclamped Inductive Switching in SiC Cascode JFETs," in The 10th International Conference on Power Electronics, Machines and Drives (PEMD 2020), 2021-01-01 2021: Institution of Engineering and Technology, doi: 10.1049/icp.2021.1114.

- II. S. N. Agbo, J. Ortiz-Gonzalez, and O. Alatise, "Performance of SiC cascode JFETs under single and repetitive avalanche pulses," Microelectronics Reliability, vol. 110, p. 113644, 2020, doi: 10.1016/j.microrel.2020.113644.

- III. S. N. Agbo, J. Ortiz Gonzalez, R. Wu, S. Jahdi, and O. Alatise, "UIS performance and ruggedness of stand-alone and cascode SiC JFETs," Microelectronics Reliability, vol. 114, p. 113803, 2020/11/01/ 2020, doi: https://doi.org/10.1016/j.microrel.2020.113803.

- IV. S. N. Agbo, E. Bashar, R. Wu, S. Mendy, J. O. Gonzalez, and O. Alatise, "Simulations and Measurements of Failure Modes in SiC Cascode JFETs under Short Circuit Conditions," in 2021 IEEE 22nd Workshop on Control and Modelling of Power Electronics (COMPEL), 2021-11-02 2021: IEEE, doi: 10.1109/compel52922.2021.9646031.

- V. J. Ortiz Gonzalez, R. Wu, S. N. Agbo, and O. Alatise, "Robustness and reliability review of Si and SiC FET devices for more-electric-aircraft applications," Microelectronics Reliability, vol. 100-101, p. 113324, 2019/09/01/ 2019, doi: https://doi.org/10.1016/j.microrel.2019.06.016.

- VI. E. Bashar et al., "Comparison of Short Circuit Failure Modes in SiC Planar MOSFETs, SiC Trench MOSFETs and SiC Cascode JFETs," in 2021 IEEE 8th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2021-11-07 2021: IEEE, doi: 10.1109/wipda49284.2021.9645092.

- VII. R. Wu et al., "Measurement and simulation of short circuit current sharing under parallel connection: SiC MOSFETs and SiC Cascode JFETs," Microelectronics Reliability, p. 114271, 2021-10-01 2021, doi: 10.1016/j.microrel.2021.114271.

- VIII. R. Wu, S. Mendy, N. Agbo, J. O. Gonzalez, S. Jahdi, and O. Alatise, "Performance of Parallel Connected SiC MOSFETs under Short Circuits Conditions," Energies, vol. 14, no. 20, p. 6834, 2021-10-19 2021, doi: 10.3390/en14206834.

- IX. E. Bashar et al., "A Review of Short Circuit Performance in 650 V Power Devices: SiC MOSFETs, Silicon Super-junction MOSFETs, SiC Cascode JFETs, Silicon MOSFETs and Silicon IGBTs," in PCIM Europe 2022; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 10-12 May 2022 2022, pp. 1-8, doi: 10.30420/565822162.

- X. O. Alatise et al., "A Comparison of the Short Circuit Performance of 650 V SiC Planar MOSFETs, Trench MOSFETs and Cascode JFETs," IET Conference Proceedings, pp. 335-339

- XI. J. Ortiz Gonzalez, A. Deb, E. Bashar, S. N. Agbo, S. Jahdi, and O. Alatise, "Benchmarking the robustness of Si and SiC MOSFETs: Unclamped inductive switching and short-circuit performance," Microelectronics Reliability, vol. 138, p. 114719, 2022/11/01/ 2022, doi: https://doi.org/10.1016/j.microrel.2022.114719.

- XII. S. Mendy, N. S. Agbo, J. O. Gonzalez, and O. Alatise, "Influence of the SiC JFET Gate Impedance on the Off-State Voltage Balance in Cascode Configuration," in 2022 IEEE Workshop on Wide Bandgap Power Devices and Applications in Europe (WiPDA Europe), 18-20 Sept. 2022 2022, pp. 1-6, doi: 10.1109/WiPDAEurope55971.2022.9936268.

### Abstract

This thesis provides the first comprehensive benchmarking exercise of SiC Cascode JFETs against similarly rated SiC Planar MOSFETs, Trench MOSFETs and other devices. Experimental measurements of short circuits in single and parallel devices, single and repetitive unclamped inductive switching as well as double pulse tests are used together with finite element simulations throughout the thesis. Power device robustness measures how well a device can sustain shocks during anomalous operation. These operating conditions are high voltages that exceed the device breakdown (avalanche conduction), or simultaneous high current and voltage through the device (Short circuit conduction). The silicon Carbide (SiC) cascode JFET is an electronic switch that combines two power devices, a low voltage silicon (Si) MOSFET and a high voltage SiC JFET operating as a single switch. This configuration avoids the challenges of reduced gate oxide reliability in SiC MOSFETs, and negative turn-on Voltage for JFETs. However, the robustness of SiC cascode JFETs have not been examined as extensively as conventional devices. Hence, this thesis investigates the robustness of SiC cascode JFETs as well as the failure modes during such operation and benchmarks the performance against conventional devices.

Analysis of avalanche robustness in SiC Cascode JFETs indicated a peculiar style of failure at high temperatures characterised by a soft failure (delayed turn-off, change of current slope, and dip in voltage), and an eventual catastrophic failure. This failure is different from other devices analysed which demonstrated a single catastrophic failure. The results show that the gate resistance of the SiC JFET plays a crucial role during avalanche mode conduction. Finite element simulations confirm this observation.

The Short circuit (SC) robustness analysis of the SiC Cascode JFET demonstrated invariability with temperature. In contrast, benchmarked devices show a SC correlation with temperature. The short circuit operation also revealed the Cascode JFET fails with a drain-source short while the gate-source junction is still functional. Also revealed is the crucial role of increasing JFET gate resistance in reducing short circuit robustness. The SC robustness is also analysed for parallel connected devices. The analysis demonstrates the parameters with the largest impact on SC current shared between paralleled devices. Variation in the embedded JFET gate resistance within the cascode JFET presents with the highest impact as confirmed by finite element simulation, while interface charges and the doping of the CSL region present with the largest impact in SiC MOSFETs.

vii

### Abbreviations

- C<sub>GS</sub> Gate-drain capacitance

- C<sub>DS</sub> Drain-source capacitance

- $C_{GS}$  Gate-source capacitance

- DC Direct current

- D<sub>it</sub> Density of interface states

- D<sub>n</sub>, D<sub>p</sub> Diffusion coefficients

- DUT Device under test

- E Electric Field

- $E_{\text{max}}-Maximum \ electric \ field$

- $E_C$ ,  $E_V$  Conduction, Valence band energy

- $E_{AV}$  Avalanche energy

- Esc Short circuit energy

- E<sub>G</sub> Energy bandgap

- $\epsilon_s \text{Dielectric constant}$

- GaN Gallium Nitride

- $I_{AV}$  Avalanche current

- I<sub>D</sub> Drain current

- I<sub>GS</sub> Gate source current

- $I_L$  Load current

- Isc Short circuit current

- J Total current density

- $J_n$ ,  $J_p$  Electron, Hole current density

- k Boltzmann's constant

- $L_{DC}$  DC source parasitic inductance

- L<sub>D</sub> Drain parasitic Inductance

- L<sub>s</sub> Source parasitic inductance

- $\kappa$  Thermal Conductivity

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- n, p Electron, Hole density

- n<sub>i</sub> Intrinsic carrier concentration

- $N_C$ ,  $N_V$  Conduction, Valence density of states

- q Electronic charge

R<sub>Drift</sub> – Drift Resistance

R<sub>DS(ON)</sub> – Drain to source on-state resistance

R<sub>G</sub> – Gate resistance

R<sub>GS</sub> – Gate-source resistance

R<sub>G,JFET</sub> – JFET gate resistance(Cascode structure)

R<sub>ON</sub> – On-state resistance

R<sub>ON,sp</sub> – Specific on-state resistance

R<sub>th</sub> – Thermal Resistance

Si – Silicon

SiC – Silicon Carbide

SCSOA – Short circuit safe operating area

SCWT - Short circuit withstand time

SOA – Safe operating area

$t_{\text{AV}}$  – Time in avalanche

T<sub>CASE</sub> – Case temperature

T<sub>J</sub> – Junction temperature

T<sub>J(max)</sub> – Maximum junction temperature

$t_{\text{ON}} - \text{ON} \text{ time}$

t<sub>PULSE</sub> – Pulse width time

$t_{sc}$  – Short circuit withstand time

TCAD – Technology computer-aided design

μ - Carrier mobility

$\mu_n$  – Electron mobility

$\mu_p$  – Hole mobility

UIS – Unclamped Inductive Switching

V – Electrostatic potential

V<sub>BR(DSS)</sub> – Manufacturer's rated breakdown voltage

v<sub>sat</sub> – Saturation drift velocity

V<sub>DD</sub> – Input voltage

V<sub>DS</sub> – Drain-source voltage

$V_{GS(th)}$ ,  $V_{th}$  – Threshold voltage

V<sub>GS</sub> – Gate-source voltage

WBG – Wide bandgap

ZTC – Zero temperature coefficient

## List of Figures

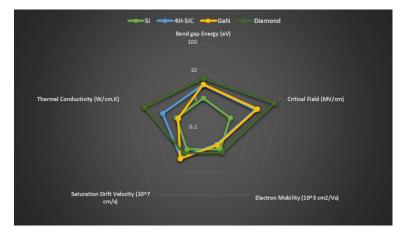

| Figure 1.1 Semiconductor material properties                                                       | 2    |

|----------------------------------------------------------------------------------------------------|------|

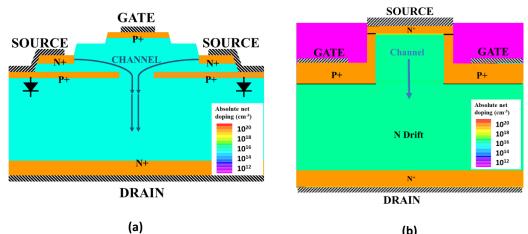

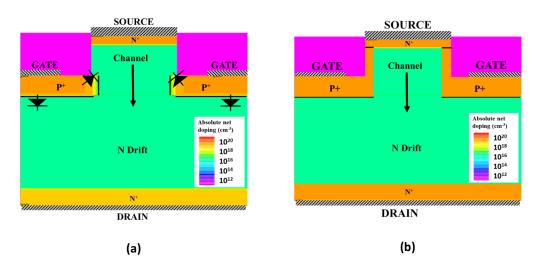

| Figure 2.1 Cell structure of (a) 2-channel JFET (b) Vertical channel JFET                          |      |

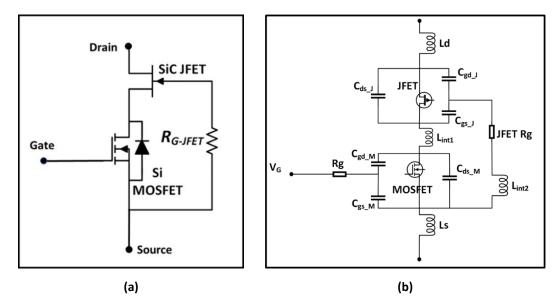

| Figure 2.2 (a) Simple Internal structure of the SiC Cascode JFET (b) Internal structure with       |      |

| the various parasitic                                                                              |      |

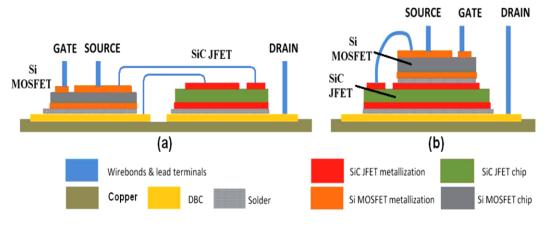

| Figure 2.3 (a) Side-by-side co-package configuration, and (b) stack                                |      |

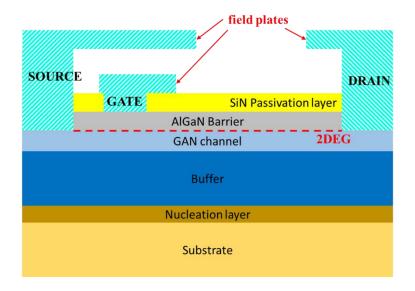

| Figure 2.4 Cell structure of a GaN HEMT (Not drawn to scale)                                       |      |

| Figure 2.5 3 <sup>rd</sup> quadrant performance of the Cascode reproduced from literature [39] (a) |      |

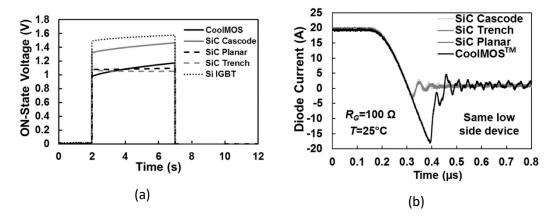

| Forward voltage of body diodes (b) reverse recovery current in the body diodes                     | 12   |

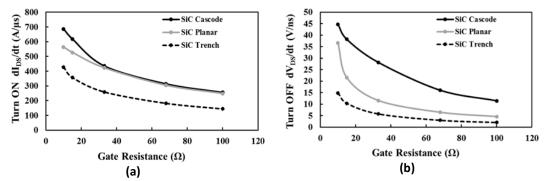

| Figure 2.6(a) Measured turn-on dI/dt vs Gate resistance for different SiC technologies (b)         |      |

| Measured turn-off dV/dt vs gate resistance for different SiC technologies                          |      |

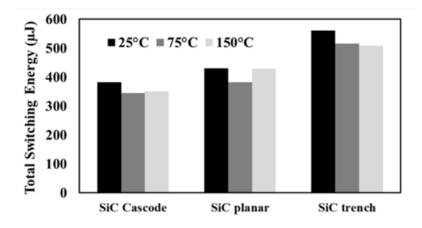

| Figure 2.7 Total Switching Energy of the SiC devices at different temperatures.                    |      |

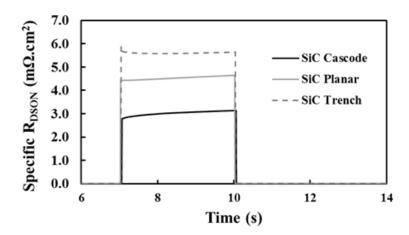

| Figure 2.8 Specific ON-state resistance of the different SiC device technologies                   |      |

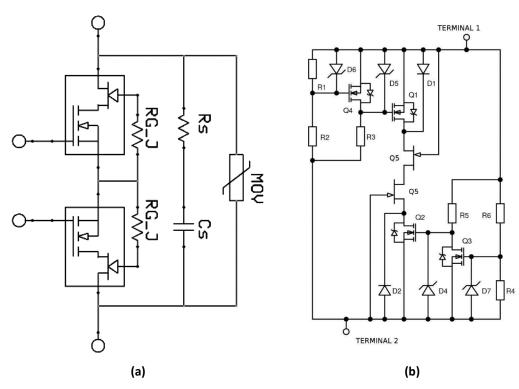

| Figure 2.9 (a) Circuit architecture of a solid-state circuit breaker (b) Two-terminal self-        | . 14 |

|                                                                                                    | 11   |

| biasing circuit breaker concept[65]                                                                |      |

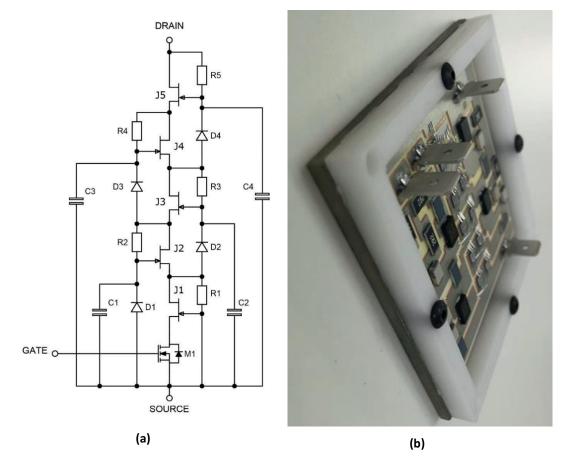

| Figure 2.10 (a) super cascode circuit (b) super cascode module prototype[1]                        | . 15 |

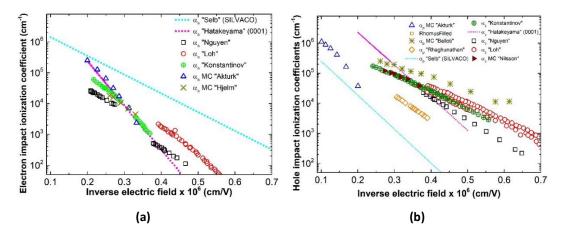

| Figure 2.11 Relationship of impact ionisation coefficient with electric field for SiC              |      |

| reproduced from literature [89-99]                                                                 |      |

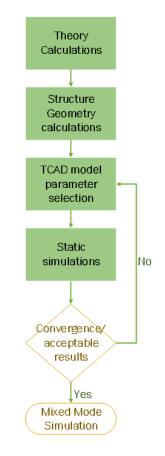

| Figure 2.12 Flow chart of FEA modelling strategy                                                   |      |

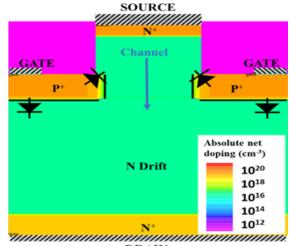

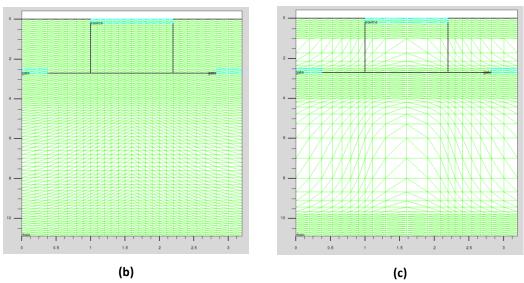

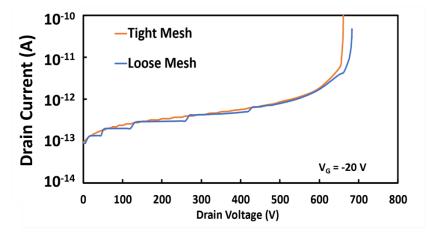

| Figure 2.13 SiC JFET structure with different mesh strategies (b) Tight Mesh (C) Loose Me          |      |

|                                                                                                    |      |

| Figure 2.14 SiC JFET static breakdown Simulation                                                   |      |

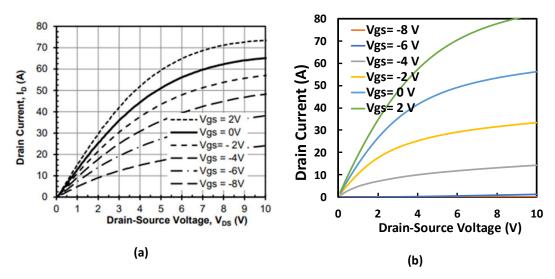

| Figure 2.15 Output characteristics of SiC stand-alone JFET (a) Datasheet (b) Simulated             |      |

| Figure 2.16 Transfer characteristics of SiC stand-alone JFET (a) Datasheet (b) Simulated           |      |

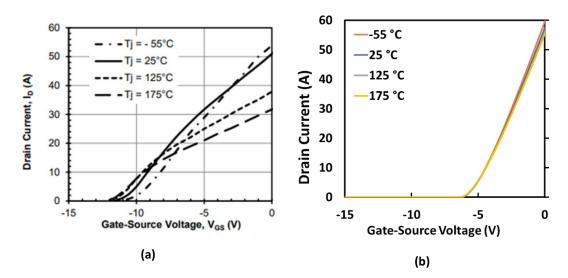

| Figure 2.17 SiC stand-alone JFET capacitances (a) Datasheet (b) Simulated                          |      |

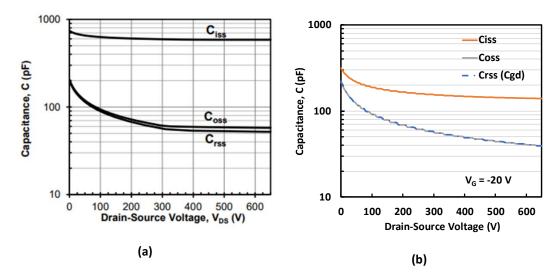

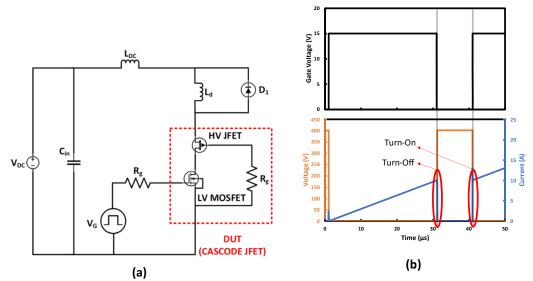

| Figure 2.18 (a) Double pulse test circuit (b) Typical characteristics of a double pulse test .     |      |

| Figure 2.19 Double pulse test experimental setup                                                   | . 29 |

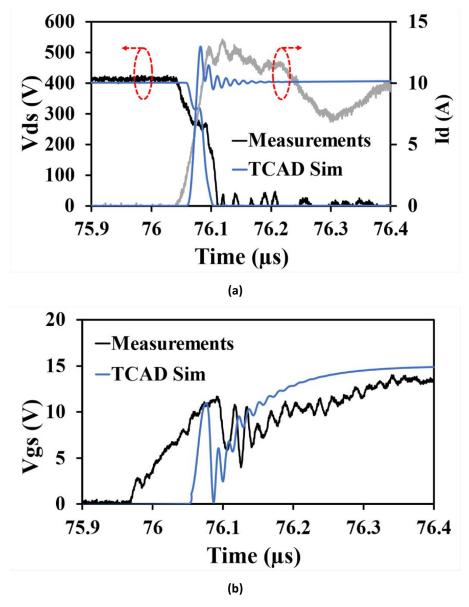

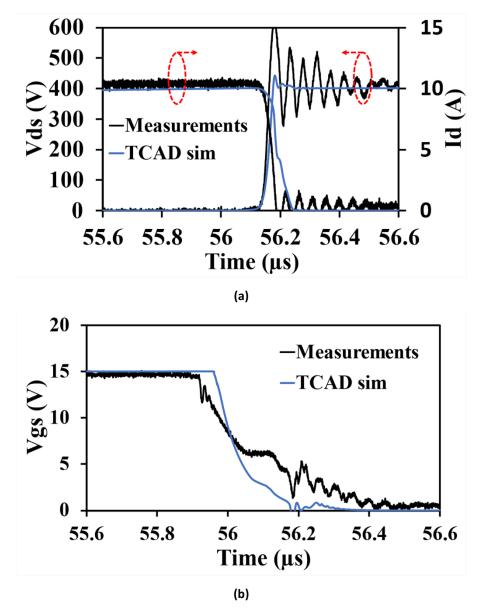

| Figure 2.20 Experimental measurement and simulated turn-on transient in SiC cascode                |      |

| JFETs (a) Cascode drain-source voltage and drain current (b) Gate-source Voltage                   |      |

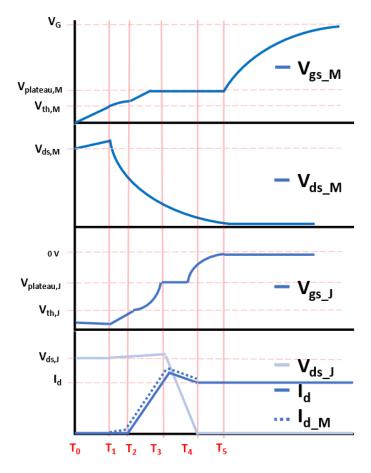

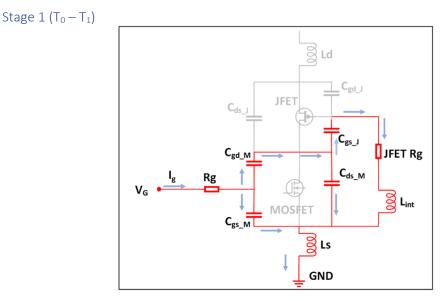

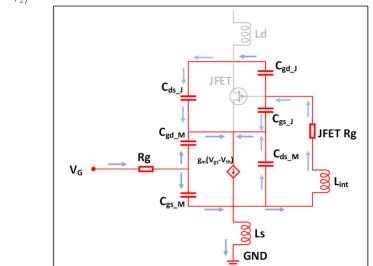

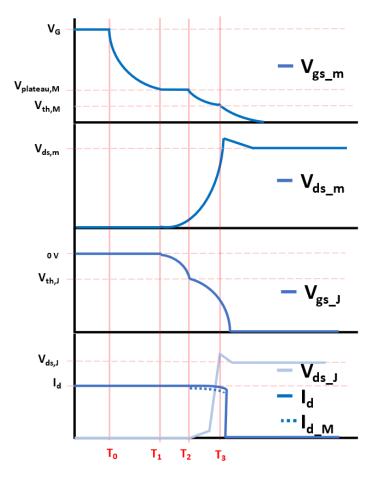

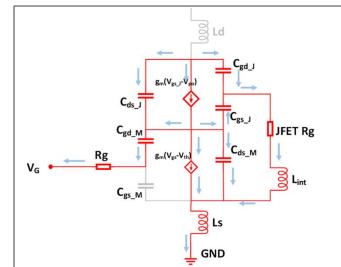

| Figure 2.21 Turn-on transitions in a SiC Cascode JFET                                              | . 31 |

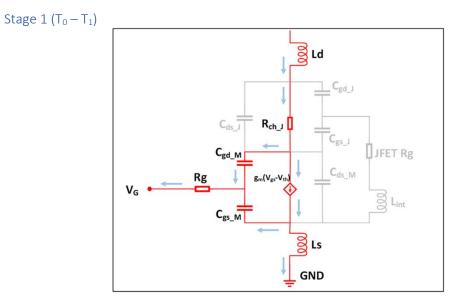

| Figure 2.22 Equivalent circuit of SiC Cascode JFET during Stage 1 of turn-on                       | . 31 |

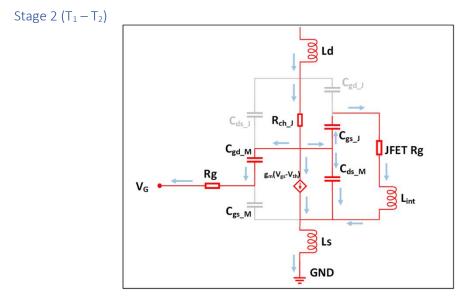

| Figure 2.23 Equivalent circuit of SiC Cascode JFET during Stage 2 of turn-on                       | . 32 |

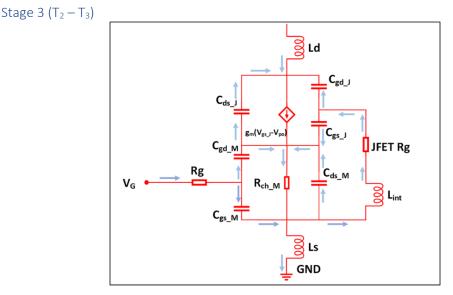

| Figure 2.24 Equivalent circuit of SiC Cascode JFET during Stage 3 of turn-on                       | . 32 |

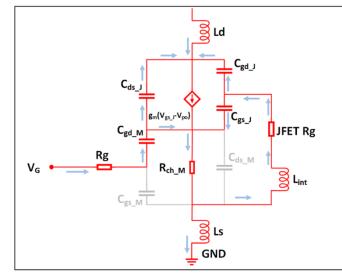

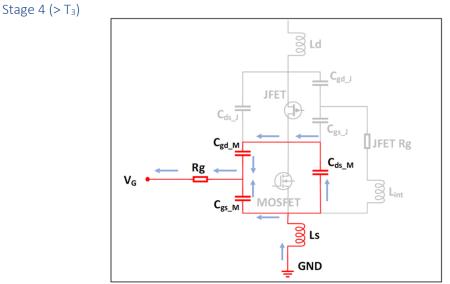

| Figure 2.25 Equivalent circuit of SiC Cascode JFET during Stage 4 of turn-on                       | . 33 |

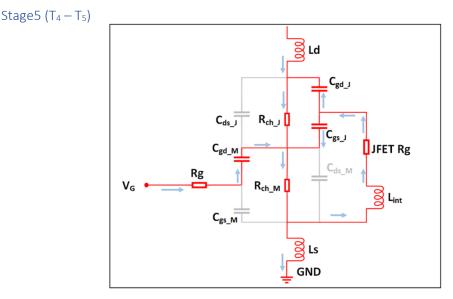

| Figure 2.26 Equivalent circuit of SiC Cascode JFET during Stage 5 of turn-on                       | . 33 |

| Figure 2.27 Equivalent circuit of SiC Cascode JFET during Stage 6 of turn-on                       | . 34 |

| Figure 2.28 Experimental measurement and simulated turn-off transient in SiC cascode J             | FET  |

| (a) Cascode drain-source voltage and drain current (b) Gate-source Voltage                         |      |

| Figure 2.29 Turn-off transitions in a SiC Cascode JFET                                             |      |

| Figure 2.30 Equivalent circuit of SiC Cascode JFET during Stage 1 of turn-off                      |      |

| Figure 2.31 Equivalent circuit of SiC Cascode JFET during Stage 2 of turn-off                      |      |

| Figure 2.32 Equivalent circuit of SiC Cascode JFET during Stage 3 of turn-off                      |      |

| Figure 2.33 Equivalent circuit of SiC Cascode JFET during Stage 4 of turn-off                      |      |

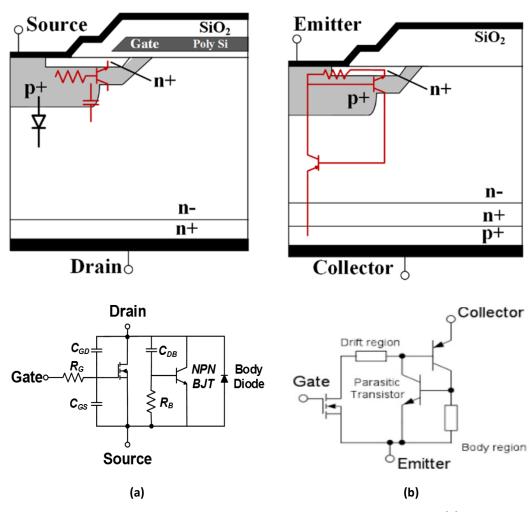

| Figure 3.1 Conventional planar power device structures showing their parasitics (a) Plana          |      |

| MOSFET structure with parasitic BJT(top), MOSFET equivalent circuit with parasitics                |      |

| (bottom) (b) Planar IGBT structure with parasitic thyristor(top) IGBT equivalent circuit wi        | th   |

| parasitics (bottom)                                                                                |      |

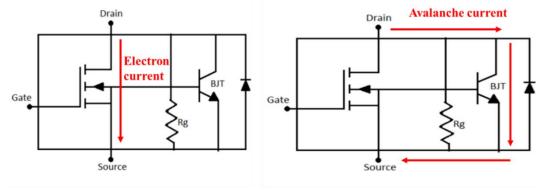

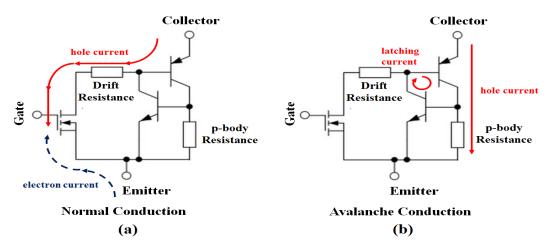

| Figure 3.2 Current path in conventional MOSFETs during (a) Normal conduction (b)                   |      |

| Avalanche conduction                                                                               | ۸۵   |

|                                                                                                    | . 40 |

| Figure 3.3 Current path in conventional IGBTs during (a) Normal conduction (b) Avalanche                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| conduction                                                                                                                              |

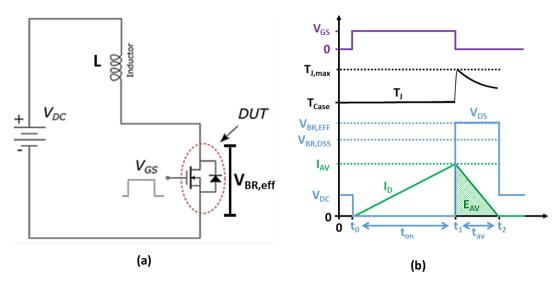

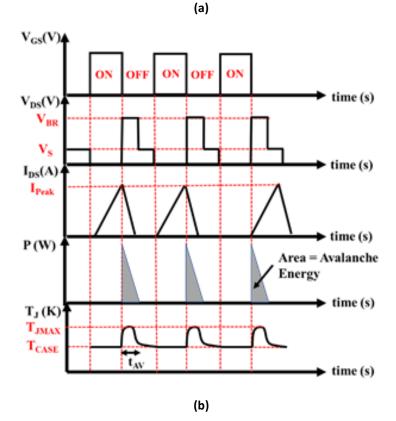

| Figure 3.4(a) Conventional UIS circuit (b) Typical avalanche characteristics, top-V <sub>GS</sub> ; middle-                             |

| Junction Temperature; bottom-I <sub>D</sub> ,V <sub>DS</sub>                                                                            |

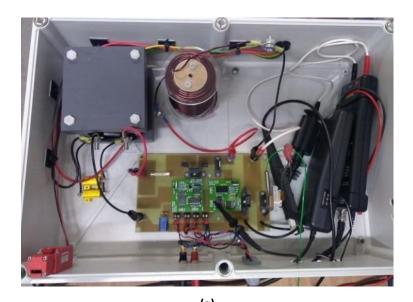

| Figure 3.5 (a) Experimental test rig for UIS measurements (b) PCB Board for UIS testing 51                                              |

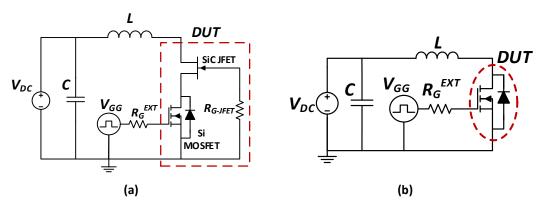

| Figure 3.6 (a) Circuit diagram for single shot avalanche test on SiC Cascode JFETs (b) Circuit                                          |

| diagram for single shot avalanche test on SiC MOSFET                                                                                    |

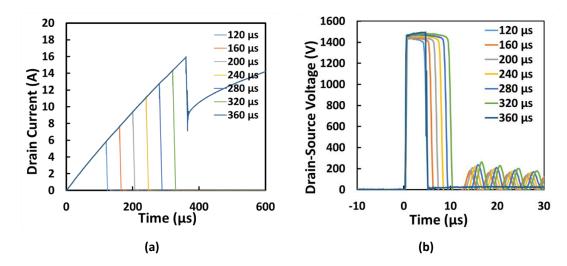

| Figure 3.7 (a) Avalanche current waveforms for SiC Trench MOSFET at 25 °C (b) Avalanche                                                 |

| voltage waveforms for SiC Trench MOSFET at 25 °C.                                                                                       |

| Figure 3.8 (a) Avalanche current waveforms for SiC Trench MOSFET at 105 °C (b) Avalanche                                                |

| voltage waveforms for SiC Trench MOSFET at 105 °C                                                                                       |

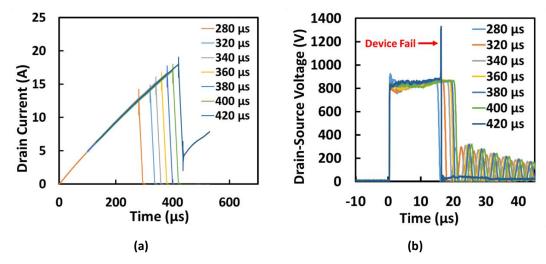

| Figure 3.9 (a) Avalanche current waveforms for SiC Cascode JFET at 25 °C (b) Avalanche                                                  |

| voltage waveforms for the SiC Cascode JFET at 25 °C                                                                                     |

| Figure 3.10 (a) Avalanche current waveforms for SiC Cascode JFET at 105 °C (b) Avalanche                                                |

| voltage waveforms for the SiC Cascode JFET at 105 °C                                                                                    |

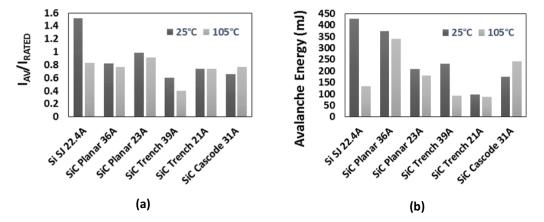

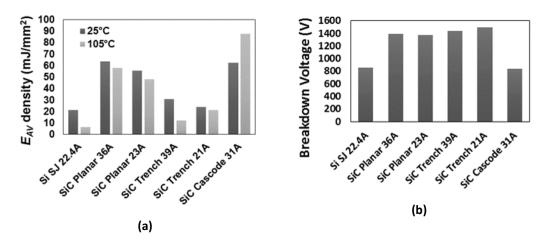

| Figure 3.11 Avalanche performance comparison with L = 1 mH (a) Avalanche current to                                                     |

| rated current ratio (b) Maximum avalanche energy                                                                                        |

| Figure 3.12 Avalanche performance comparison with L = 1 mH (a) Maximum avalanche                                                        |

| energy density (b) UIS Avalanche Voltage                                                                                                |

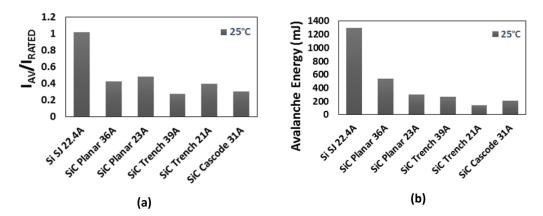

| Figure 3.13 Avalanche performance comparison with $L = 6 \text{ mH}$ (a) Avalanche current to                                           |

| rated current ratio (b) maximum avalanche energy                                                                                        |

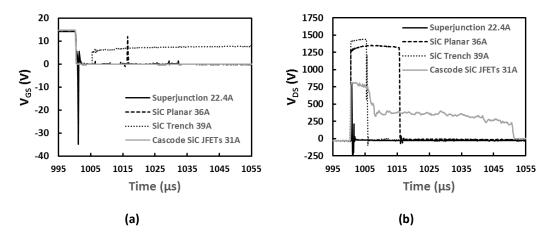

| Figure 3.14 Avalanche performance comparison (a) Gate-Source voltage at failure (b) Drain-<br>Source Voltage characteristics at failure |

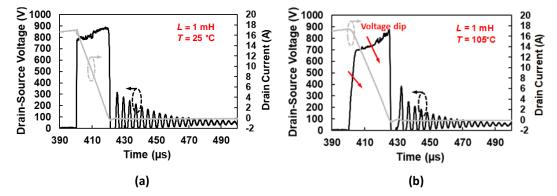

| Figure 3.15 UIS test SiC Cascode, (a) Ambient temperature (b) Temperature 105°C                                                         |

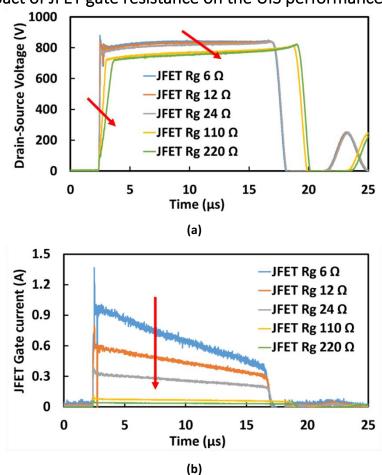

| Figure 3.16 (a) Impact of RG-JFET on standalone SiC JFET drain-source voltage during UIS                                                |

| [ID=12.3 A, T=25 °C] (b) Impact of RG-JFET on JFET gate current during UIS [ID=12.3 A, T=25                                             |

| °C]                                                                                                                                     |

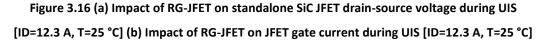

| Figure 3.17 (a) Impact of RG-JFET on standalone SiC JFET drain-source voltage during UIS                                                |

| [ID=12.3 A, T=150 °C] (b) Impact of RG-JFET on JFET gate current during UIS (ID=12.3 A,                                                 |

| T=150 °C)                                                                                                                               |

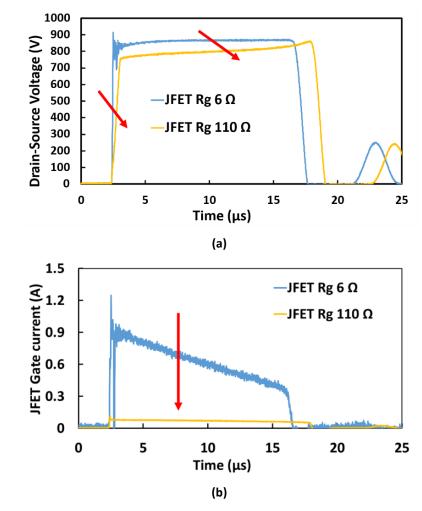

| Figure 3.18 JFET gate current for different RG-JFET values at 25 °C, 75 °C, 125 °C, and 150                                             |

| °C                                                                                                                                      |

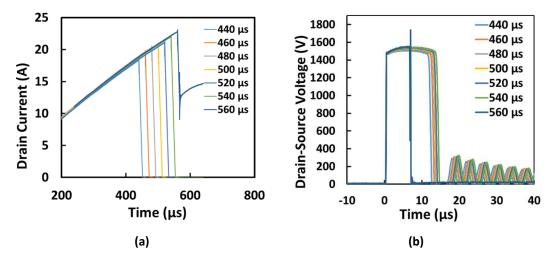

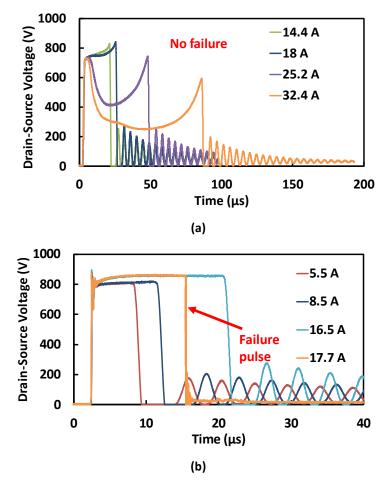

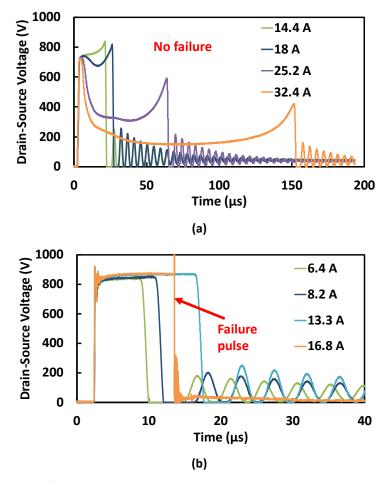

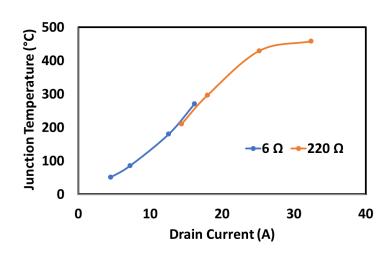

| Figure 3.19 Impact of avalanche current on the stand alone SiC JFET drain-source voltage                                                |

| during UIS at 25 °C (a) $R_{G-JFET}$ =220 $\Omega$ (b) $R_{G-JFET}$ =6 $\Omega$                                                         |

| Figure 3.20 Impact of avalanche current on the stand alone SiC JFET drain-source voltage                                                |

| during UIS at 150 °C (a) $R_{G-JFET}$ =220 $\Omega$ (b) $R_{G-JFET}$ =6 $\Omega$                                                        |

| test (T=25 C)                                                                                                                           |

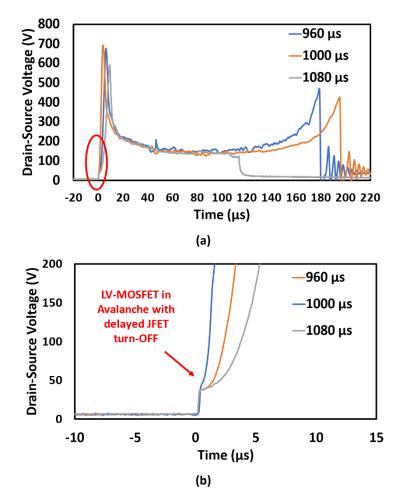

| Figure 3.22 (a) Avalanche voltage transient showing delayed turn-off of the SiC JFET while                                              |

| the LV Si MOSFET is in avalanche. (b). Zoomed in version of 'a'                                                                         |

| Figure 3.23 Gate voltage charging measurements with 220 $\Omega$ gate resistance                                                        |

| Figure 3.24 Equivalent circuits for the failed SiC Cascode JFET                                                                         |

| Figure 3.25 3rd quadrant characteristics of (a) unstressed SiC Cascode JFET and (b)                                                     |

| damaged SiC Cascode JFET63                                                                                                              |

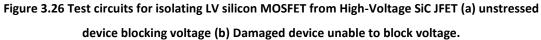

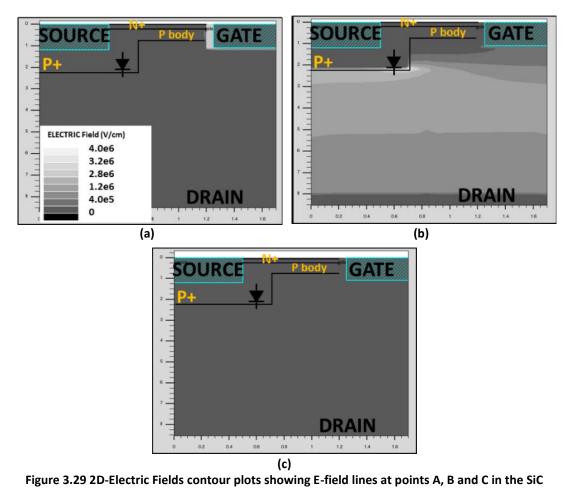

| Figure 3.26 Test circuits for isolating LV silicon MOSFET from High-Voltage SiC JFET (a)                                                |

| unstressed device blocking voltage (b) Damaged device unable to block voltage                                                           |

| Figure 3.27 VGS, VDS and IS for (a) unstressed and (b) damaged SiC Cascode JFET                                                         |

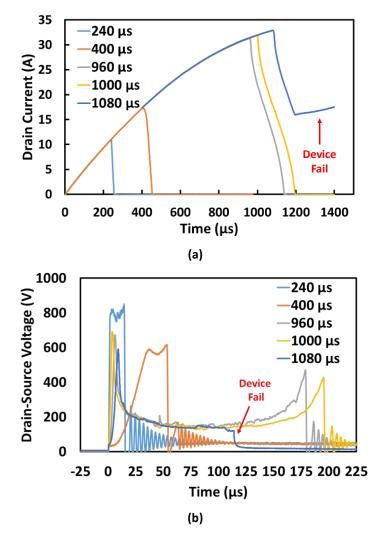

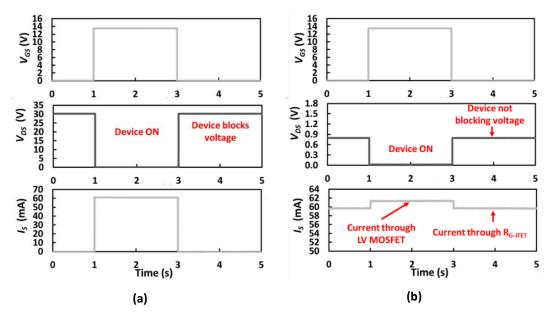

| Figure 3.28 Simulated avalanche (a) Current and (b) Drain-source voltage of SiC Trench                                                  |

| MOSFETs undergoing failure under UIS                                                                                                    |

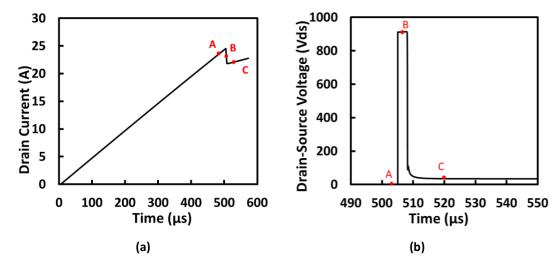

| Figure 3.29 2D-Electric Fields contour plots showing E-field lines at points A, B and C in the                                          |

| SiC Trench MOSFET                                                                                                                       |

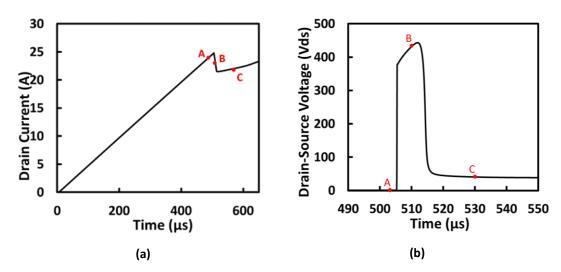

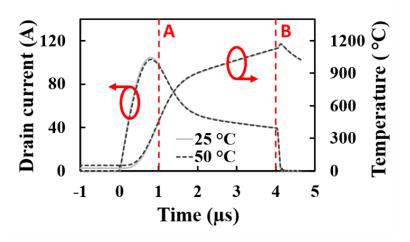

| C in the SiC Trench MOSFET — (68<br>Figure 3.31 Simulated Avalanche (a) current and (b) Voltage for the SiC Cascode JFET during<br>UIS showing conduction: A, avalanche: B, and electrothermal failure: C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 3.30 2D-Current density contour plots showing current flow path at points A, B and |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

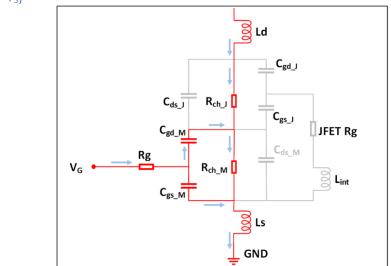

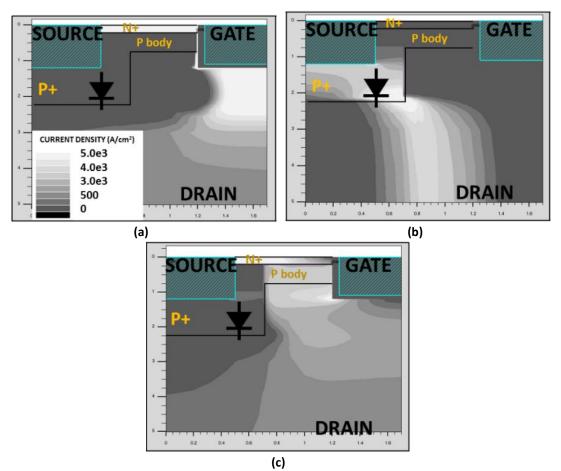

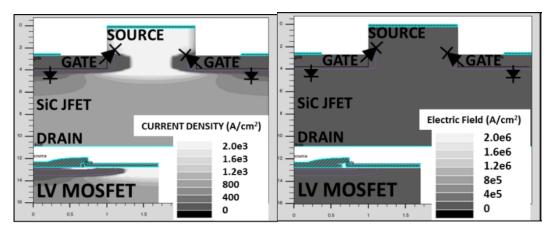

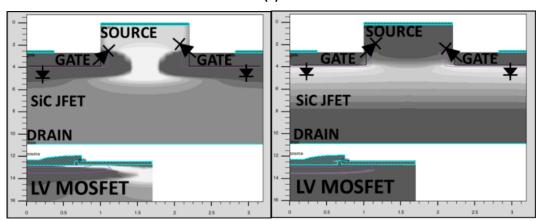

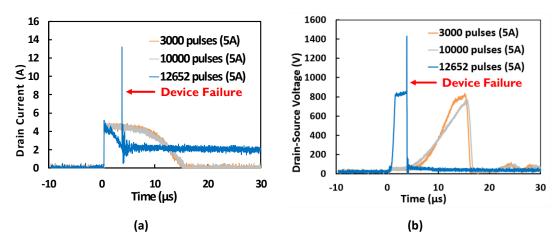

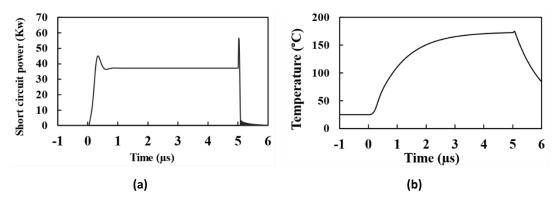

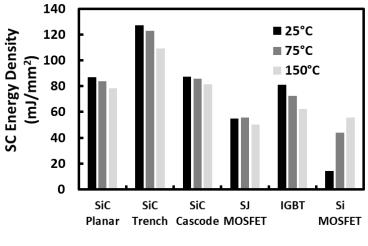

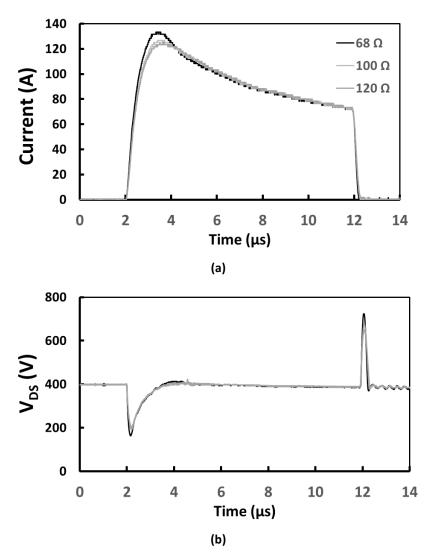

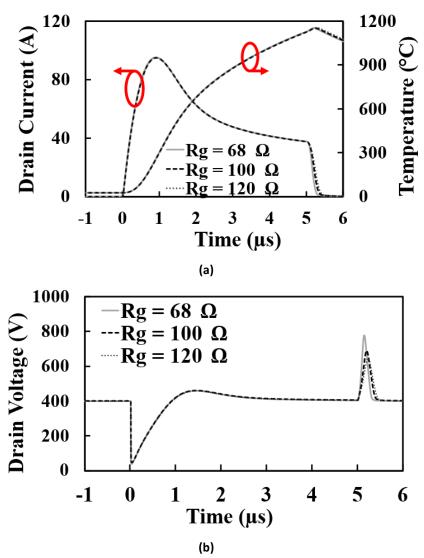

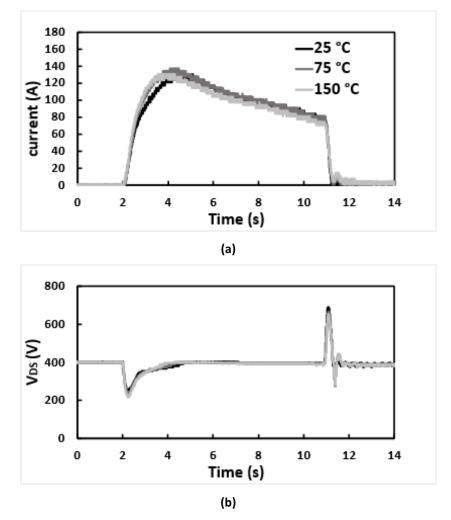

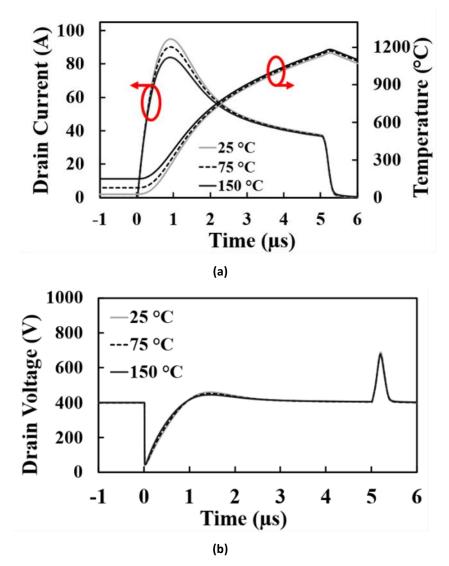

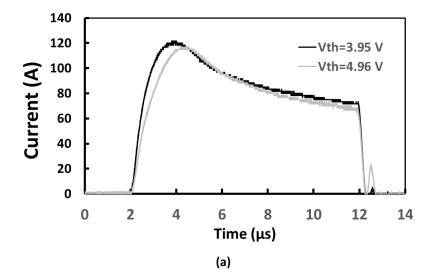

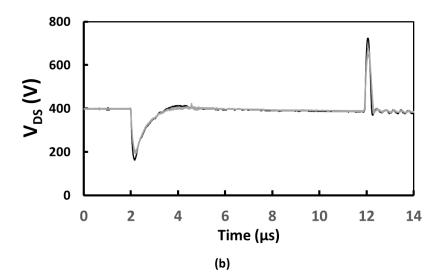

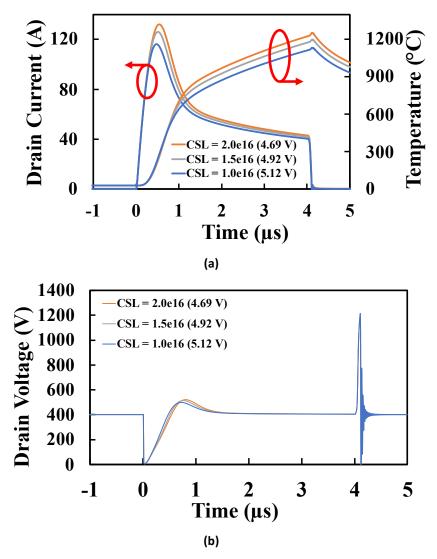

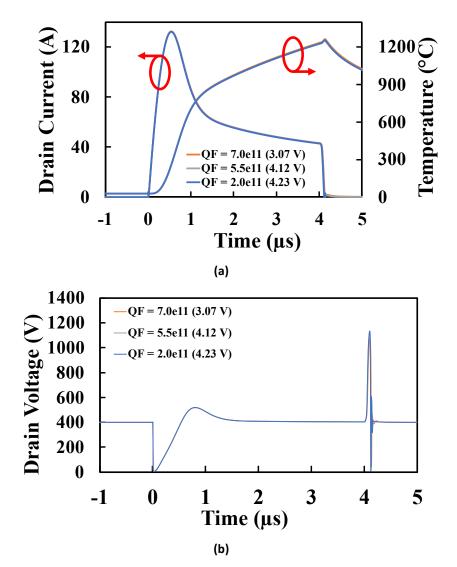

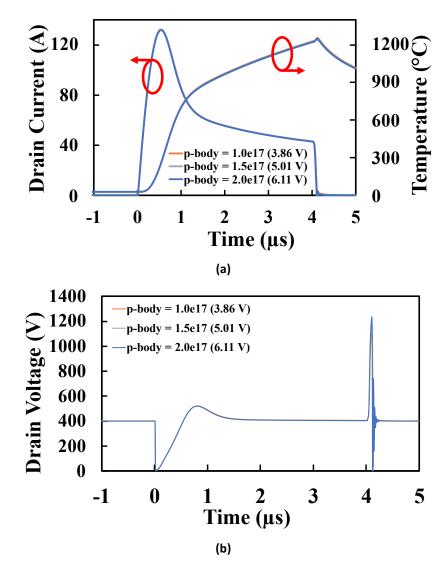

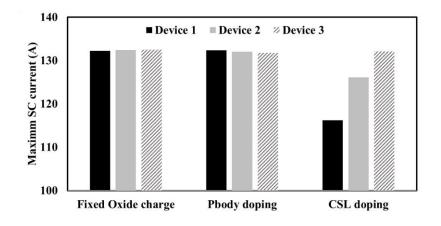

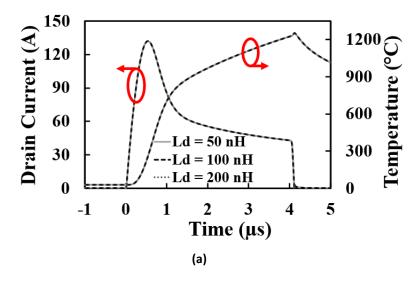

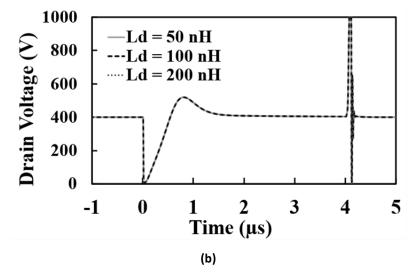

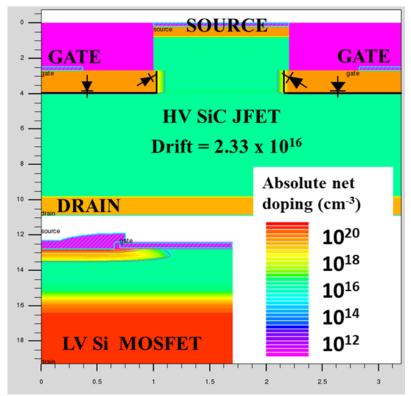

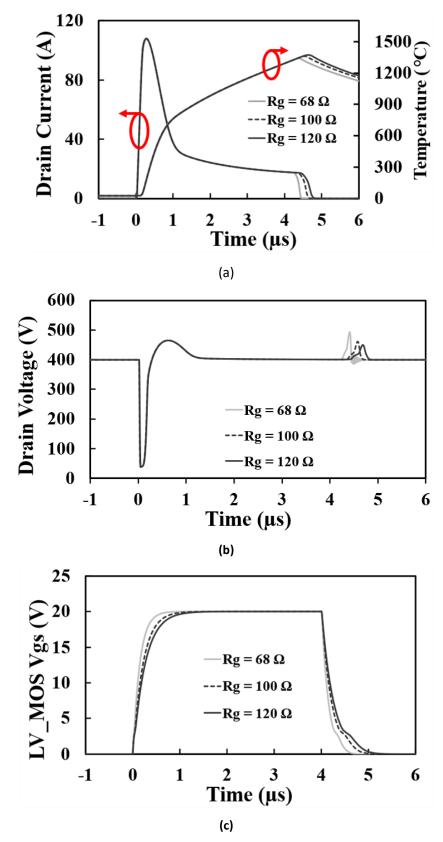

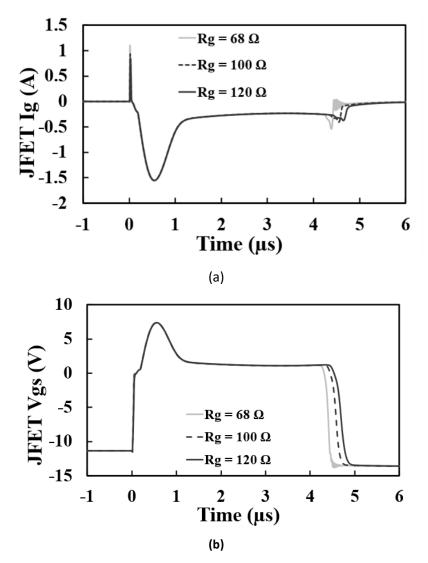

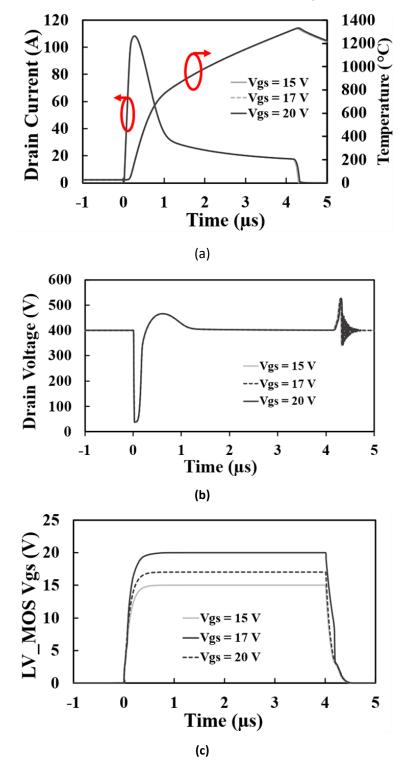

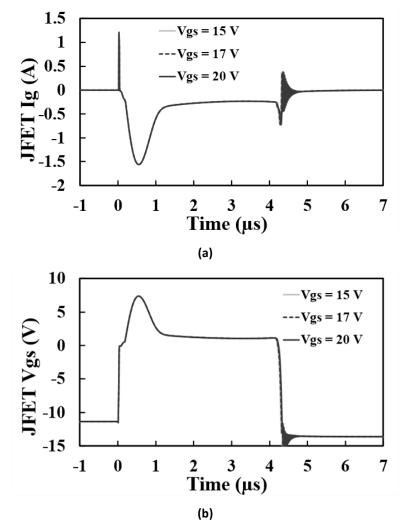

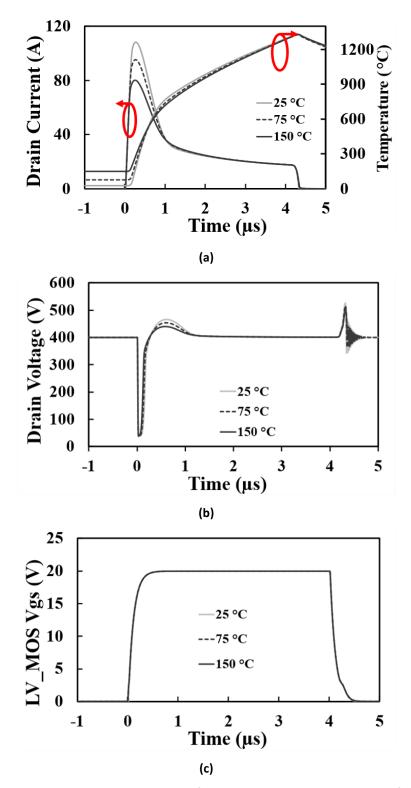

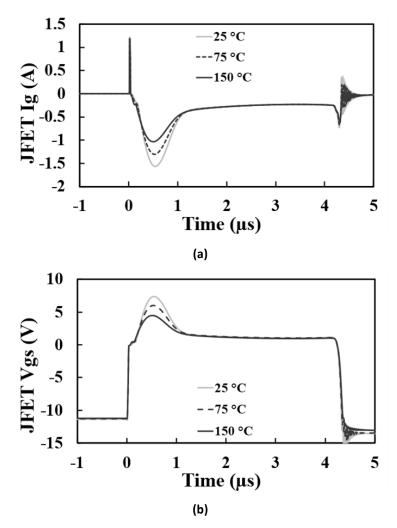

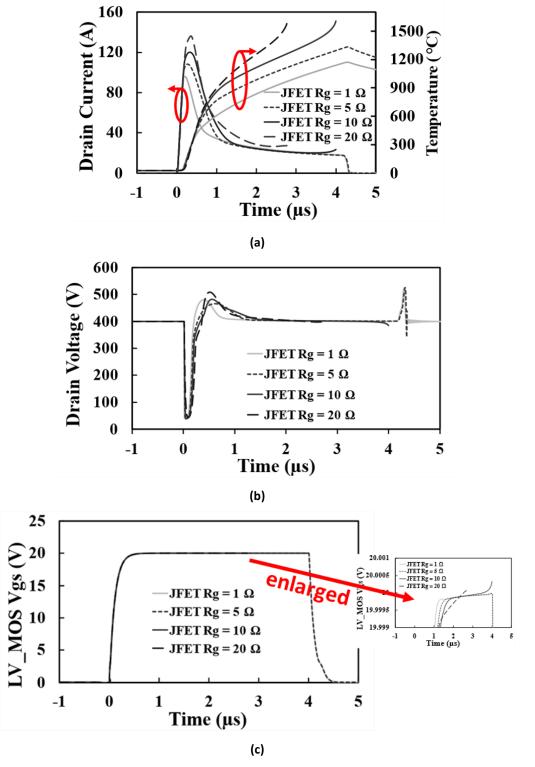

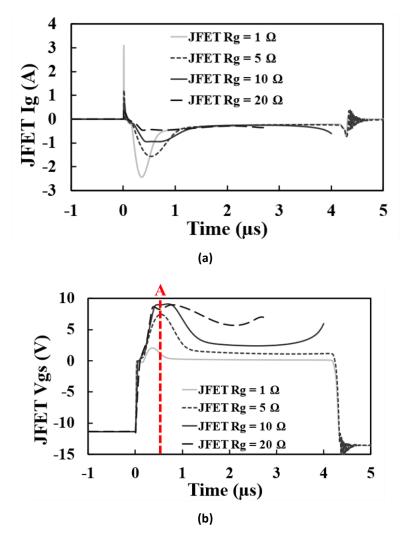

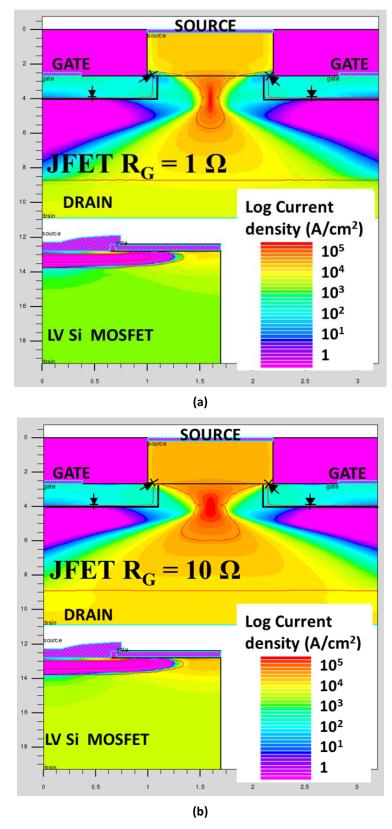

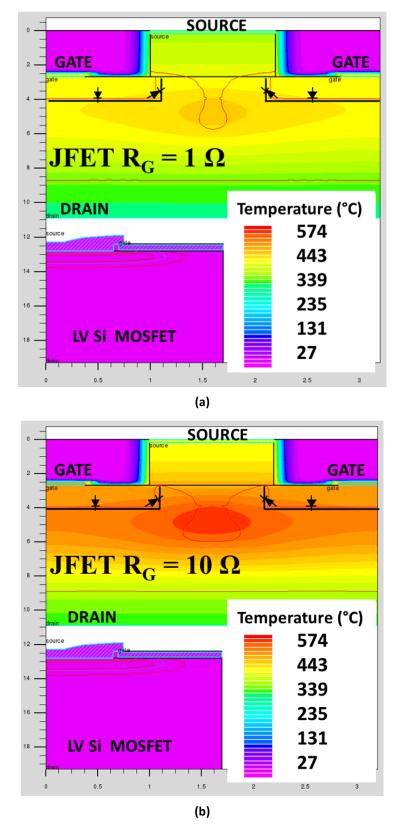

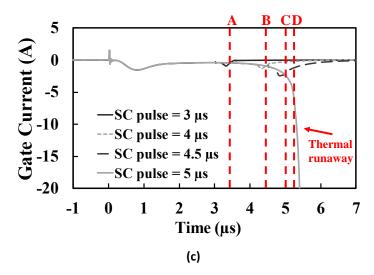

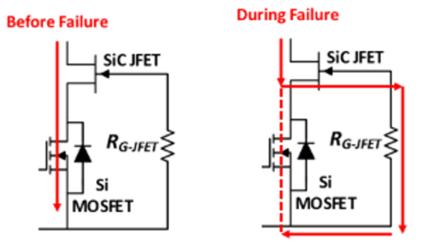

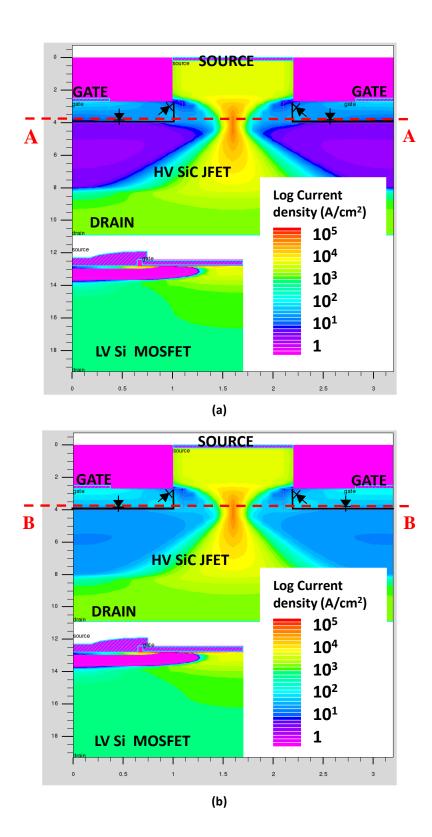

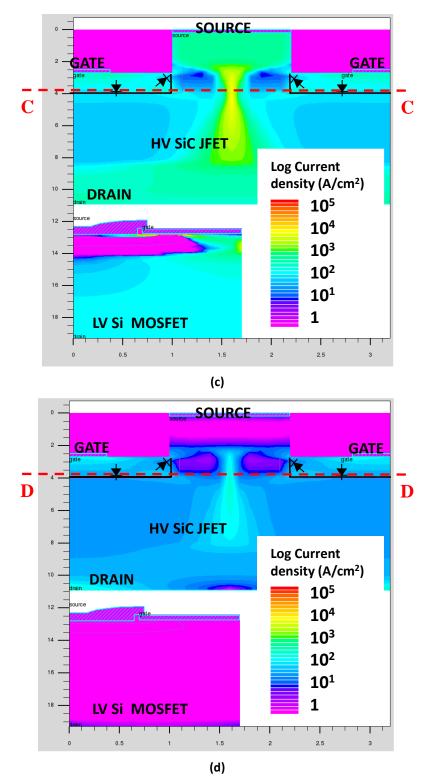

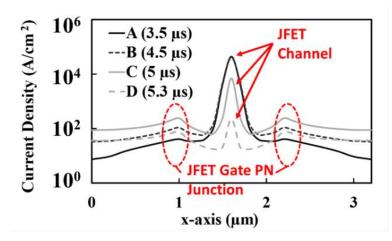

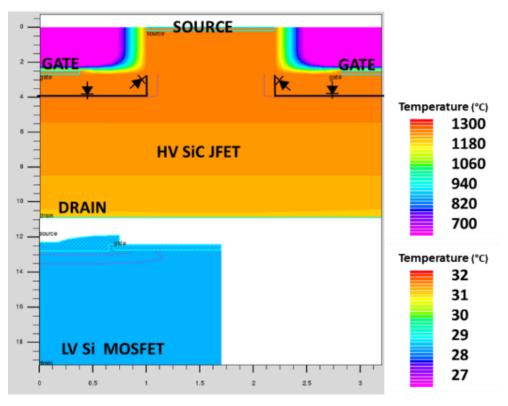

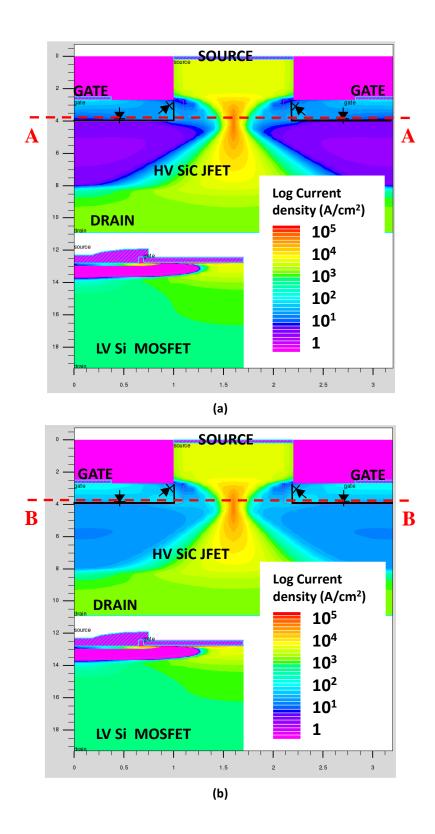

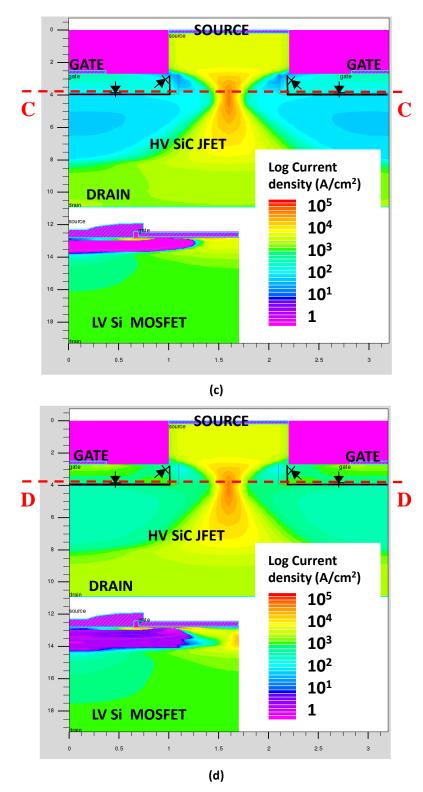

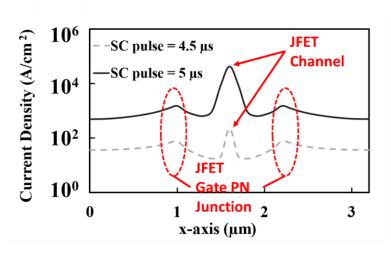

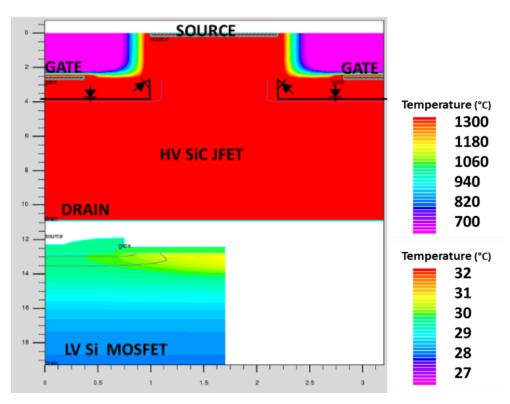

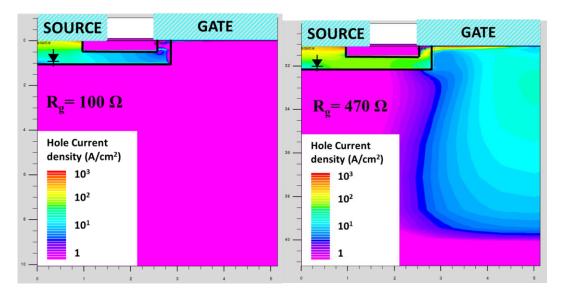

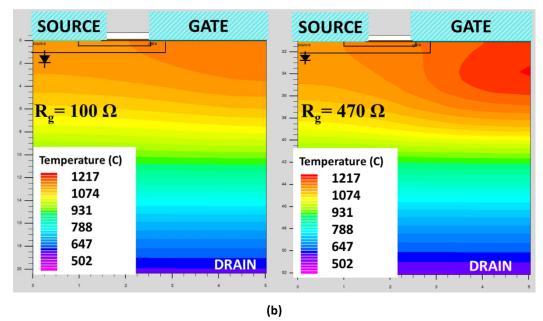

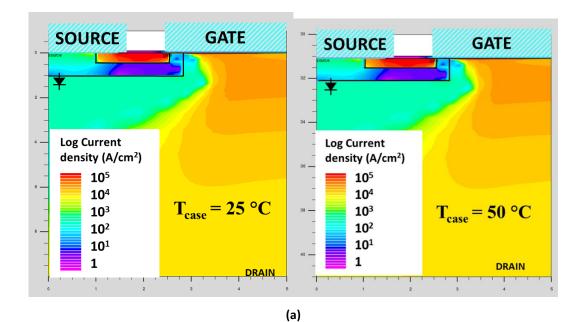

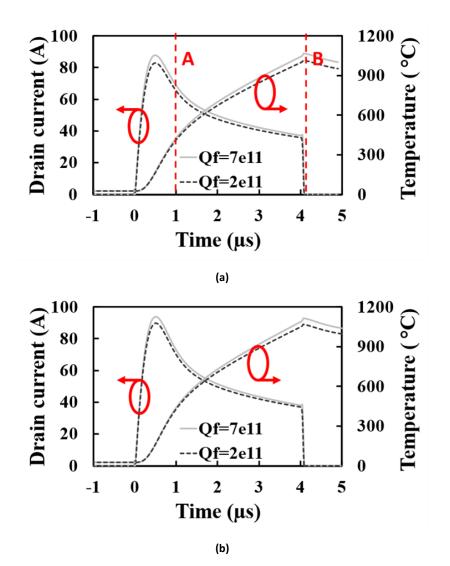

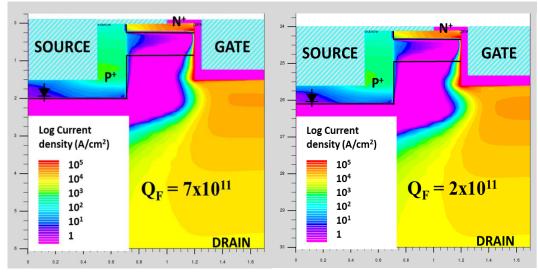

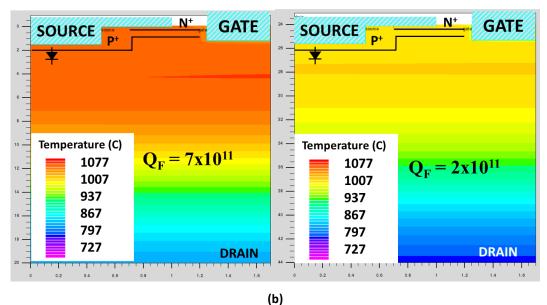

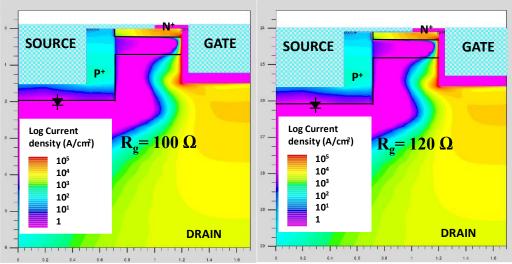

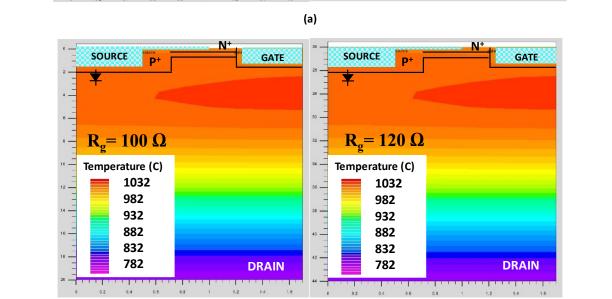

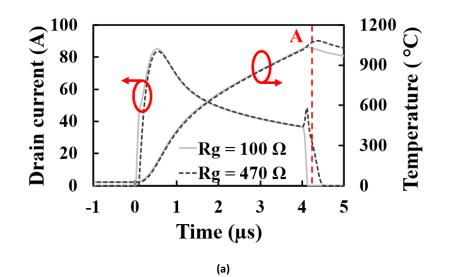

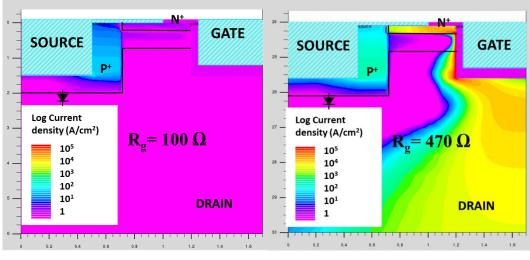

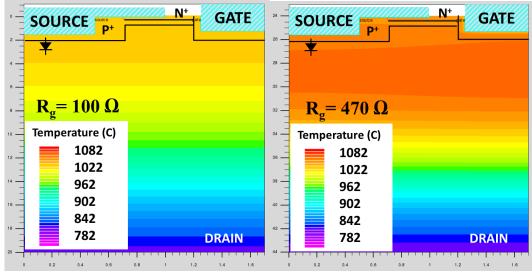

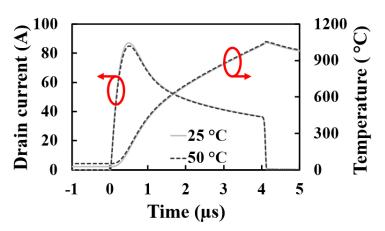

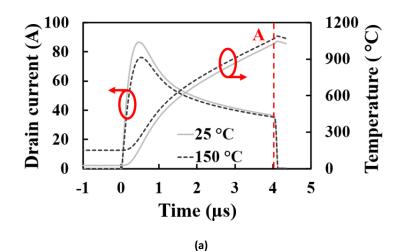

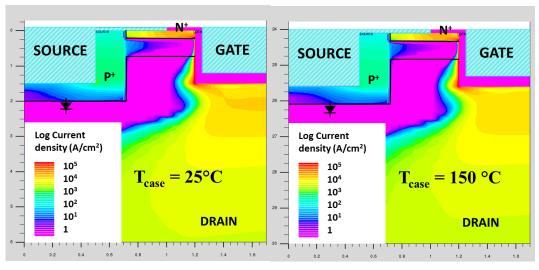

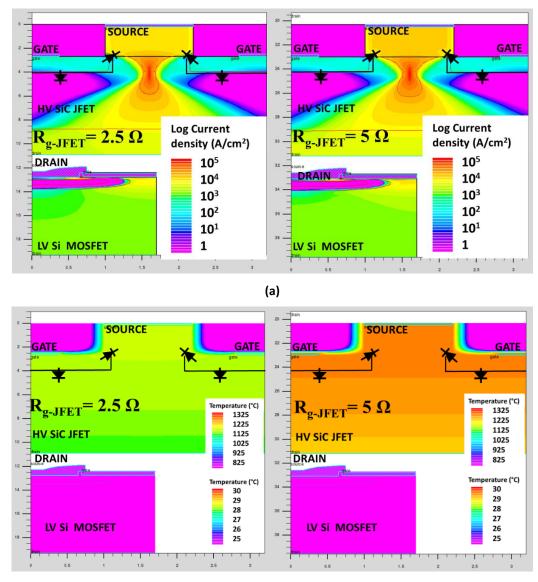

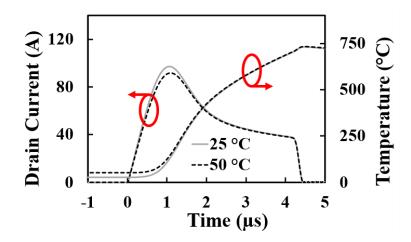

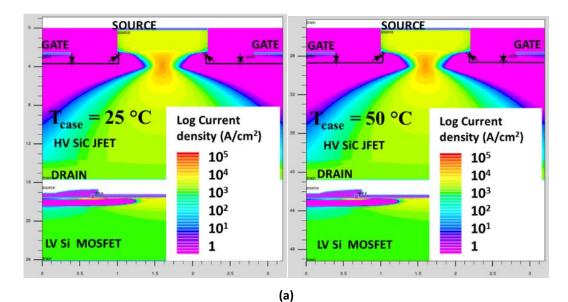

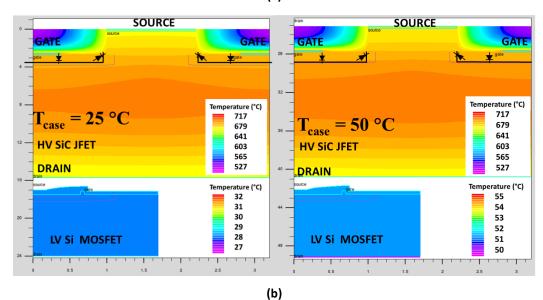

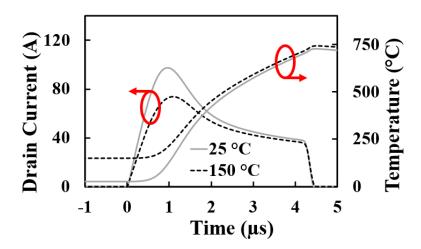

| UIS showing conduction: A, avalanche: B, and electrothermal failure: C.       69         Figure 3.32 2D contour plots of Current density[left] and Electric Fields (right) showing       avalanche characteristics at points A, B and C in the SIC Cascode JFET       70         Figure 3.33 Simulated (a) V <sub>DS</sub> and (b) I <sub>D</sub> (c) I <sub>GJ</sub> for SIC Cascode JFET with R <sub>G-HET</sub> = 5Ω and (c)       71         Figure 3.34 Simulated (a) V <sub>DS</sub> and (b) I <sub>D</sub> (c) I <sub>GJ</sub> for SIC Cascode JFET with increasing R <sub>G-HET</sub> 72         Figure 3.35 (a) Repetitive avalanche test setup (b) Repetitive avalanche waveforms       73         Figure 3.37 Test sequence pulses for the auxiliary devices       74         Figure 3.37 Test sequence pulses for the auxiliary devices       74         Figure 3.37 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b)       voltage         voltage       76         Figure 3.30 Repetitive Avalanche current characteristics for SiC Trench MOSFET (b)       Repetitive avalanche voltage characteristics for SiC Trench MOSFET       76         Figure 4.1 MOSFET equivalent circuit simulation of SIC Cascode JFET (a) Short circuit power (b) Simulated Junction Temperature rise.       83       83         Figure 4.2 Spice short circuit simulation of SIC Cascode JFET (a) Short circuit measurements. 87       77       Figure 4.3 Short circuit test schematic (b) Gate pulses for short circuit measurements. 87       78         Figure 4.3 Short circuit test schematic of Sicacacode JFET under different pulse durations until fail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C in the SiC Trench MOSFET                                                                |

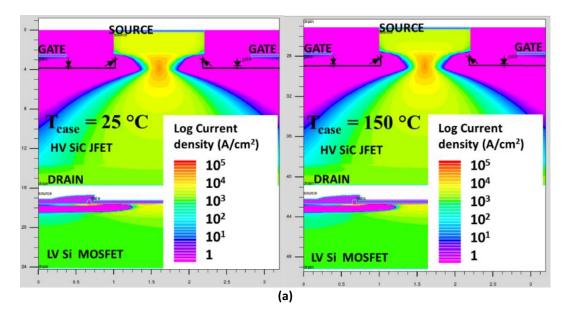

| Figure 3.32 2D contour plots of Current density(left) and Electric Fields (right) showing       70         Figure 3.33 Simulated (a) Vos and (b) Io (c) Io, I for SIC Cascode JFET with Rc./JET = 5Ω and (c)       71         Figure 3.33 Simulated (a) Vos and (b) Io (c) Io, I for SIC Cascode JFET with Increasing Ro./JET       71         Figure 3.33 Simulated (a) Vos and (b) Io (c) Io, I for SIC Cascode JFET with Increasing Ro./JET       72         Figure 3.36 Repetitive avalanche test setup (b) Repetitive avalanche waveforms       73         Figure 3.37 Eat sequence pulses for the auxiliary devices.       74         Figure 3.38 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b)       76         Voltage       76         Figure 3.39 Repetitive Avalanche current characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SIC Cascode JFET (a) Short circuit power (b)       Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit test system.       87       77         Figure 4.4 Short circuit transients for the SiC Cascode JFET at (a) different VDS       80         Simulated Junction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                                                                         |

| avalanche characteristics at points A, B and C in the SiC Cascode JFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |

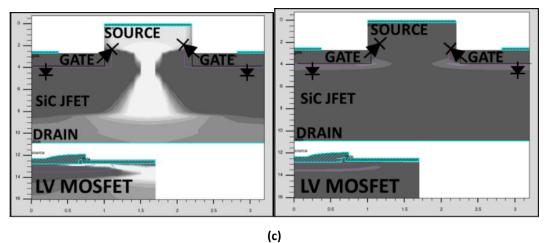

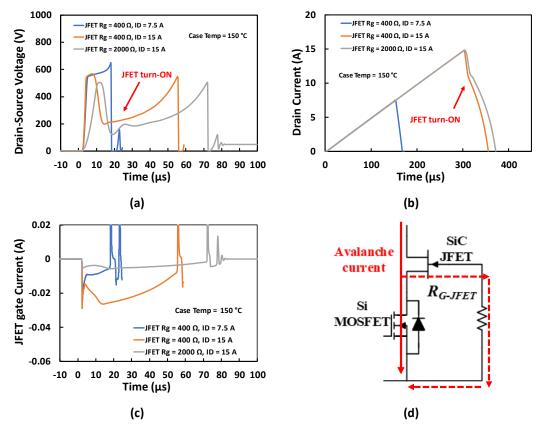

| Figure 3.33 Simulated (a) Vos and (b) Io (c) IoJ for SiC Cascode JFET with RGJFET = 5Ω and (c)Current path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

| Current path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                                                         |

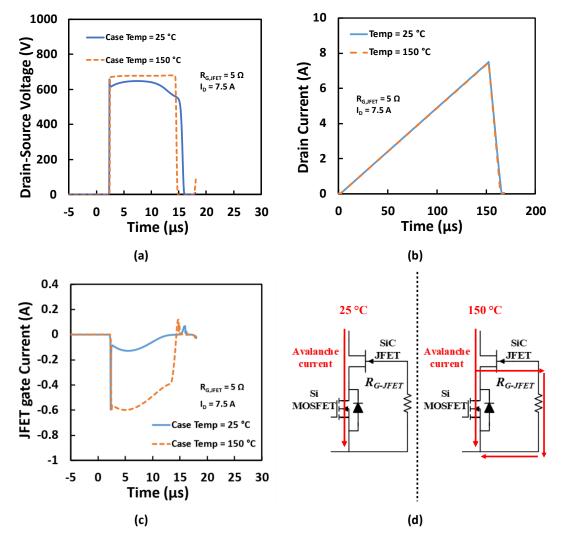

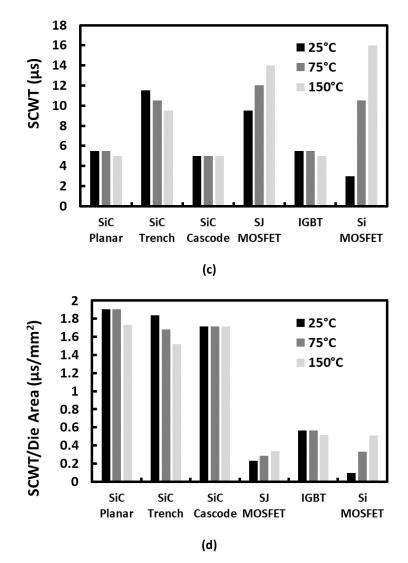

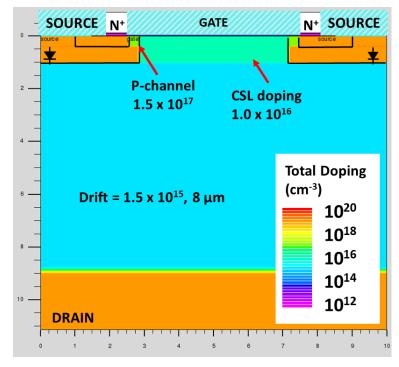

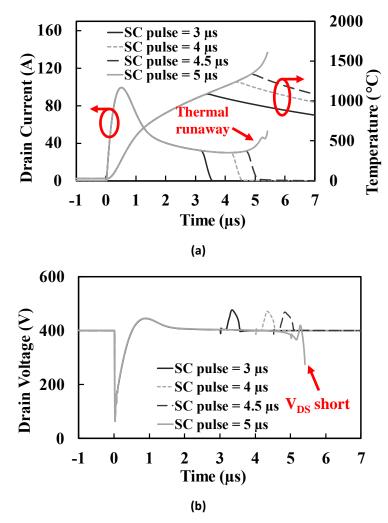

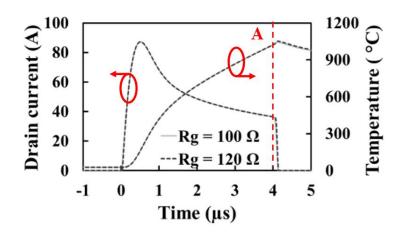

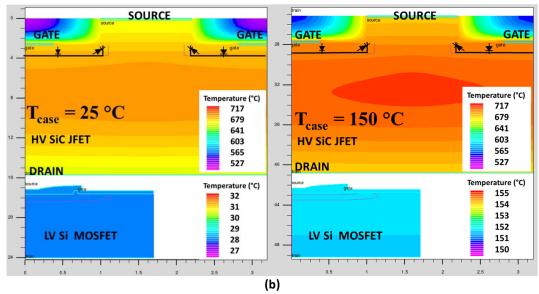

| Figure 3.34 Simulated (a) Vos and (b) Io (c) IoJ for SiC Cascode JFET with increasing ReJFET<br>and Jay and (d) Current path. 72<br>Figure 3.35 (a) Repetitive avalanche test setup (b) Repetitive avalanche waveforms 73<br>Figure 3.36 Repetitive avalanche circuit showing auxiliary devices 74<br>Figure 3.37 Test sequence pulses for the auxiliary devices 74<br>Figure 3.38 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b)<br>voltage 76<br>Figure 3.39 Repetitive avalanche current characteristics for SiC Trench MOSFET (b)<br>Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)<br>Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)<br>Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)<br>Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated<br>Junction Temperature rise. 85<br>Figure 4.2 Spice short circuit simulation of SiC Cascode JFET a(a) Short circuit power (b)<br>Simulated Junction Temperature rise. 85<br>Figure 4.3 Spice short circuit simulation of SiC Cascode JFET (a) Short circuit power (b)<br>Simulated Junction Temperature rise. 85<br>Figure 4.4 Short Circuit Measurement Test system 87<br>Figure 4.5 (a). Short circuit tarsisents for the SiC Cascode JFET a(a) different VDS<br>voltage (b) different initial Junction Temperatures 88<br>Figure 4.4 Short circuit transients for the SiC Cascode JFET under different pulse durations<br>until failure (a) Short circuit current to b) Short circuit VDS 89<br>Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy<br>density for all technologies (c) SCWT for each technology (d) SCWT normalized by chi size<br>92<br>Figure 4.11 SiC MOSFET simulated in SILVACO TCAD 93<br>Figure 4.12 Experimental measurement of short circuit Vos<br>93<br>Figure 4.13 Short circuit Current for all technologies (b) SHORT CIRCUIT Energy<br>density for all technologies (c) SCWT for each technology (d) SCWT normalized by chi size<br>92<br>Figure 4.13 Short circuit TCAD Simulation of SiC MOSFET showing the Impact of <i>gate</i><br>voltage (a) Short circu |                                                                                           |

| and I <sub>AV</sub> and (d) Current path.       72         Figure 3.35 (a) Repetitive avalanche test setup (b) Repetitive avalanche waveforms       73         Figure 3.36 Repetitive avalanche circuit showing auxiliary devices.       74         Figure 3.37 Test sequence pulses for the auxiliary devices.       74         Figure 3.38 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b)       76         Voltage       76         Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SiC Cascode JFET (a) Short circuit power (b) Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit test system.       87         Figure 4.4 Short Circuit Measurement Test system.       87         Figure 4.5 (a). Short circuit transients for the SiC Cascode JFET at (a) different VDS       voltages (b) different initial Junction Temperatures.         Figure 4.7 Short circuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit transients for the SiC Cascode JFET at (a) different VDS         voltages (b) different initial Junction Temperatures.       88         Figure 4.5 Short circuit transients for the SiC Cascode JFET under diff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

| Figure 3.36 Repetitive avalanche circuit showing auxiliary devices.       74         Figure 3.37 Test sequence pulses for the auxiliary devices.       74         Figure 3.38 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b)       76         Figure 3.39 Repetitive Avalanche measurements from Cascode JFET B (a) current and (b)       76         Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche voltage characteristics for SiC Trench MOSFET (c)       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SiC Cascode JFET (a) Short circuit power (b) Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit test schematic (b) Gate pulses for short circuit measurements. 87       71         Figure 4.5 (a). Short circuit transients for the SiC Cascode JFET at (a) different VDS       89         Figure 4.5 (a). Short circuit transients for the SiC Cascode JFET at (a) different VDS       89         Figure 4.5 (b) different initial Junction Temperatures       89         Figure 4.10 Peak SHORT CIRCUIT Current (b) Short circuit VDS       89         Figure 4.10 Short circuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit current for all technologies (b) SHORT CIRCUIT En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |

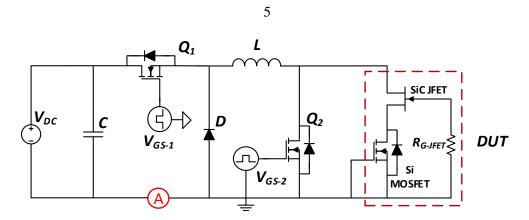

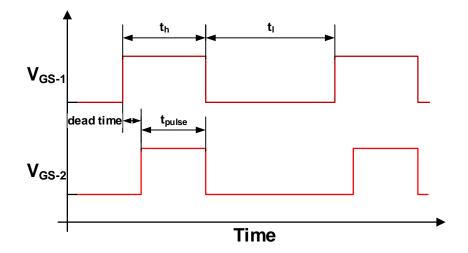

| Figure 3.37 Test sequence pulses for the auxiliary devices       74         Figure 3.38 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b)       76         Figure 3.39 Repetitive Avalanche measurements from Cascode JFET B (a) current and (b)       76         Voltage       76         Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances       83         Figure 4.2 Spice short circuit simulation of SiC Cascode JFET (a) Short circuit power (b) Simulated Junction Temperature rise       85         Figure 4.4 Short Circuit Measurement Test system       87         Figure 4.5(a). Short circuit transients for the SiC Cascode JFET at (a) different VDS       88         Figure 4.7 Short circuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit torest tore for all technologies (b) SHORT CIRCUIT Energy       90         Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy       91         Figure 4.11 Sic MOSFET simulated in SILVACO TCAD       92         Figure 4.12 Sperimental measurement of short circuit Vos       94         Figure 4.13 Short circuit turent for all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 3.35 (a) Repetitive avalanche test setup (b) Repetitive avalanche waveforms 73     |

| Figure 3.38 Repetitive Avalanche measurements from Cascode JFET A (a) current and (b) voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 3.36 Repetitive avalanche circuit showing auxiliary devices                        |

| voltage       76         Figure 3.39 Repetitive Avalanche measurements from Cascode JFET B (a) current and (b)       76         Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche voltage characteristics for SiC Trench MOSFET (b)       76         Repetitive avalanche voltage characteristics for SiC Trench MOSFET (a)       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit simulation of SiC Cascode JFET (a) Short circuit measurements.       87         Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements.       87         Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements.       87         Figure 4.5 (b) of tircuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit transients for the SiC Cascode JFET under different pulse durations until failure.       90         Figure 4.4 Short circuit Current for all DUTs in Table 4-2.       91         Figure 4.1 SiC MOSFET simulated in SILVACO TCAD.       93         Figure 4.11. SiC MOSFET simulated in SILVACO TCAD.       93         Figure 4.12 Experimental measurement of sict Circuit in SiC MOSFET showing the Impact of gate voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 3.37 Test sequence pulses for the auxiliary devices                                |

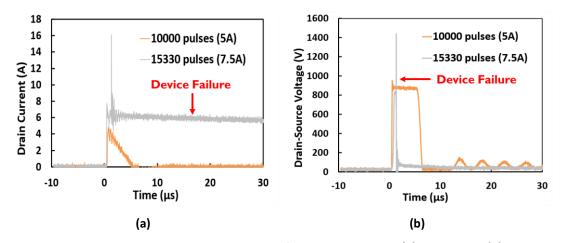

| Figure 3.39 Repetitive Avalanche measurements from Cascode JFET B (a) current and (b)         voltage       76         Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)       Repetitive avalanche voltage characteristics for SiC Trench MOSFET         Repetitive avalanche voltage characteristics for SiC Trench MOSFET       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit test submatic (b) Gate pulses for short circuit measurements. 87       87         Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements. 87       88         Figure 4.5 Short circuit transients for the SiC Cascode JFET at (a) different VDS       80         voltages (b) different initial Junction Temperatures       88         Figure 4.3 Short circuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit vorrent (b) Short circuit VDS       89         Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy       91         Figure 4.11. SiC MOSFET simulated in SILVACO TCAD       93         Figure 4.12 Short circuit TCAD Simulation of SiC MOSFET showing the Impact of gate voltage (a) Short circuit Current for short circuit in SiC MOSFET showing the Impact of different gate voltages (a) short circuit te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                           |

| voltage       76         Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)         Repetitive avalanche voltage characteristics for SiC Trench MOSFET       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit simulation of SIC Cascode JFET (a) Short circuit power (b)       Simulated Junction Temperature rise.         Sigure 4.4 Short Circuit Measurement Test system       87         Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements.       87         Figure 4.6 Short circuit current transients for the SiC Cascode JFET at (a) different VDS       voltages (b) different initial Junction Temperatures       88         Figure 4.7 Short circuit transients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit current (b) Short circuit VDS       89         Figure 4.9 Short circuit current for all DUTs in Table 4-2       90         Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy density for all technologies (c) SCWT for each technology (d) SCWT normalized by chip size       92         Figure 4.11. SiC MOSFET simulated in SILVACO TCAD       93         Figure 4.13 Short circuit TCAD Simulation of SiC MOSFET showing the Impact of different gate voltages (a) short circui                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |

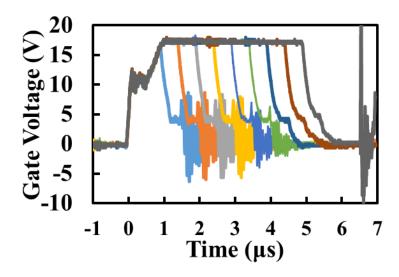

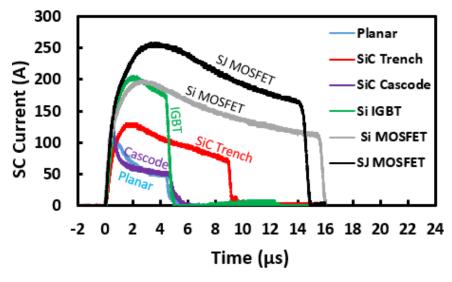

| Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)         Repetitive avalanche voltage characteristics for SiC Trench MOSFET       76         Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and inductances.       83         Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated Junction Temperature rise.       85         Figure 4.3 Spice short circuit simulation of SIC Cascode JFET (a) Short circuit power (b)       Simulated Junction Temperature rise.         Sigure 4.4 Short Circuit Measurement Test system       87         Figure 4.5 (a). Short circuit terms thrasients for the SiC Cascode JFET at (a) different VDS       voltages (b) different initial Junction Temperatures         Sigure 4.7 Short circuit current thrasients for the SiC Cascode JFET under different pulse durations until failure (a) Short circuit current (b) Short circuit VDS       89         Figure 4.8 Short circuit currents for all DUTs in Table 4-2       91         Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy density for all technologies (c) SCWT for each technology (d) SCWT normalized by chip size       92         Figure 4.12 Experimental measurement of short circuit tin SiC MOSFET showing the impact of gate resistance (a) short circuit current (b) short circuit VDS       94         Figure 4.13 Short circuit TCAD Simulated in SILVACO TCAD       93         Figure 4.14 Experimental measurement of short circuit In SiC MOSFET showing the impact of gate resistance (a) short                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • • • • • • • • • • • • • • • • • • • •                                                   |

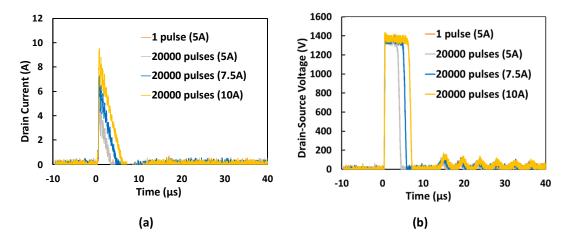

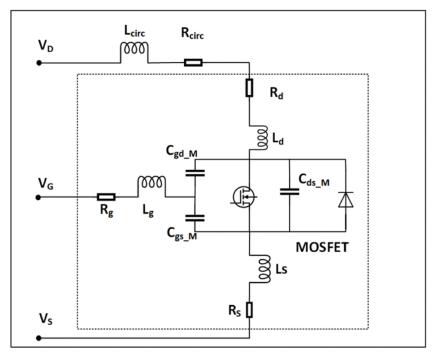

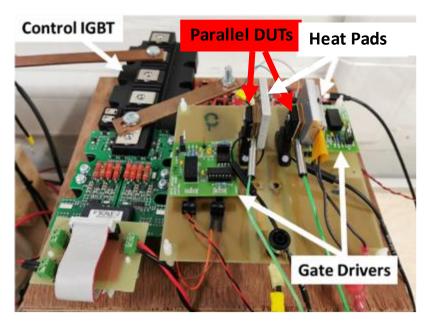

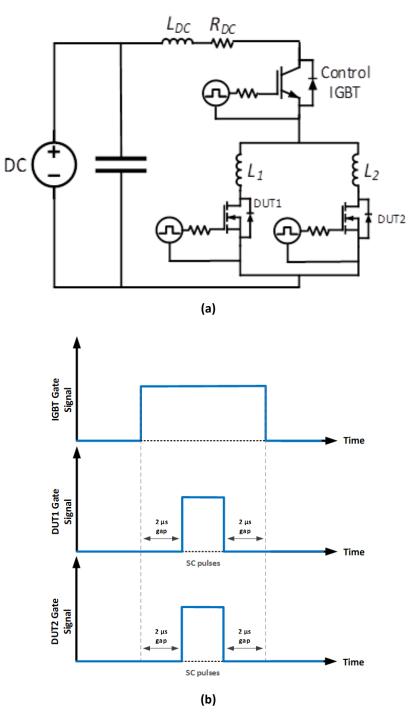

| Figure 4.1 MOSFET equivalent circuit showing device parasitic capacitances and<br>inductances.83Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated<br>Junction Temperature rise.85Figure 4.3 Spice short circuit simulation of SiC Cascode JFET (a) Short circuit power (b)85Simulated Junction Temperature rise.85Figure 4.4 Short Circuit Measurement Test system.87Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements. 87Figure 4.6 Short circuit current transients for the SiC Cascode JFET at (a) different VDSvoltages (b) different initial Junction Temperatures88Figure 4.7 Short circuit transients for the SiC Cascode JFET under different pulse durationsuntil failure (a) Short circuit current (b) Short circuit VDS.89Figure 4.9 Short circuit Currents for all DUTs in Table 4-2.91Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy92Figure 4.11. SiC MOSFET simulated in SILVACO TCAD.93Figure 4.12 Experimental measurement of short circuit in SiC MOSFET showing the impact94Figure 4.13 Short circuit current and hot-spot temperature (b) Drain-source voltage (c) V <sub>GS</sub> 95Figure 4.14 Experimental measurement of short circuit V <sub>DS</sub> 96Figure 4.15 Short circuit TCAD Simulation of SiC MOSFET showing the Impact of <i>R<sub>G</sub></i> (a). Short circuit TCAD Simulation of SiC MOSFET showing the Impact of gate resistance (a) short circuit current (b) short circuit V <sub>DS</sub> 96Figure 4.15 Short circuit TCAD Simulation of SiC MOSFET showing the Impact of <i>R<sub>G</sub></i> (a). Short circuit TCAD Simulation of SiC MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 3.40 (a) Repetitive avalanche current characteristics for SiC Trench MOSFET (b)    |

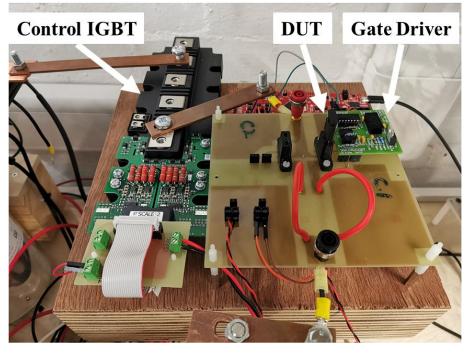

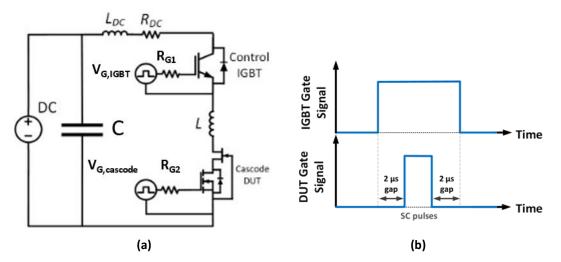

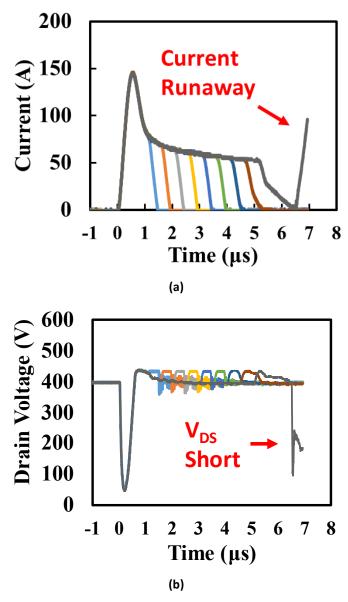

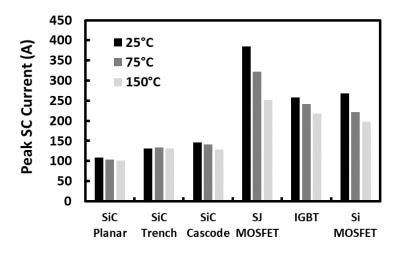

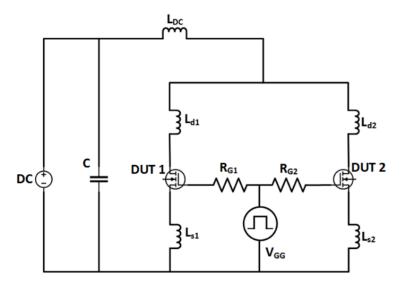

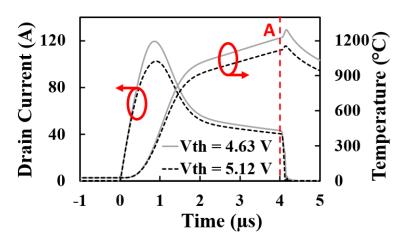

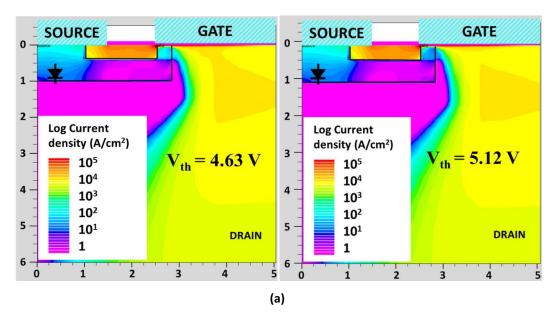

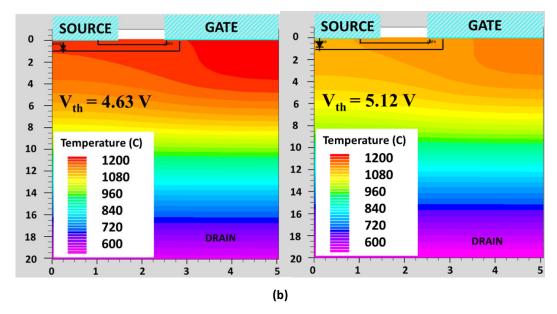

| inductances83Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) SimulatedJunction Temperature riseFigure 4.3 Spice short circuit simulation of SIC Cascode JFET (a) Short circuit power (b)Simulated Junction Temperature rise85Figure 4.4 Short Circuit Measurement Test system87Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements. 87Figure 4.6 Short circuit current transients for the SiC Cascode JFET at (a) different VDSvoltages (b) different initial Junction Temperatures88Figure 4.7 Short circuit transients for the SiC Cascode JFET under different pulse durationsuntil failure (a) Short circuit current (b) Short circuit VDS89Figure 4.8 Short circuit VGS transients for the SiC Cascode JFET under different pulsedurations until failure.90Figure 4.9 Short circuit CURCUIT Current for all DUTs in Table 4-2.91Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energydensity for all technologies (c) SCWT for each technology (d) SCWT normalized by chip size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |

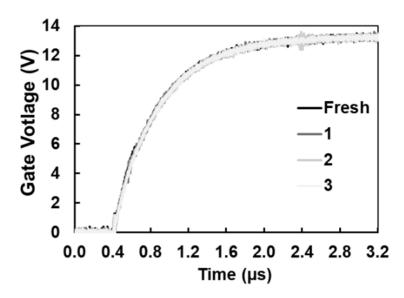

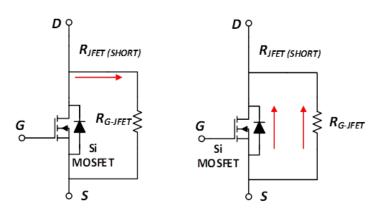

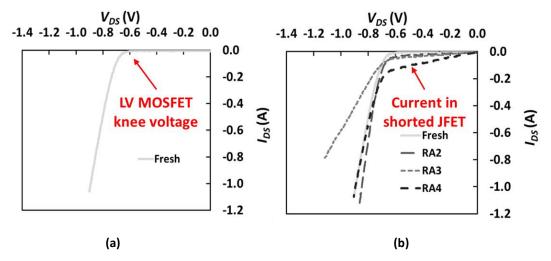

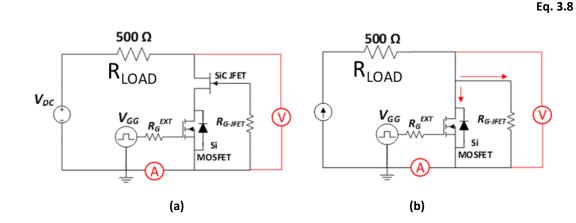

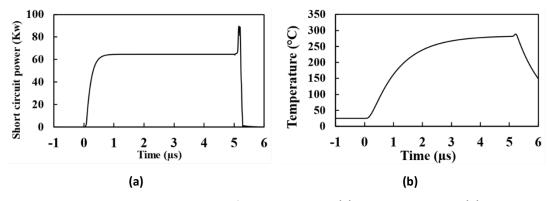

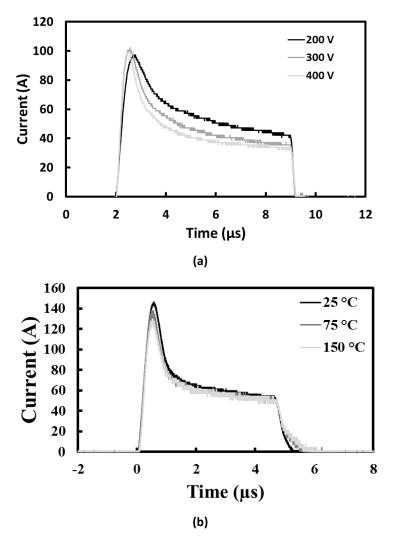

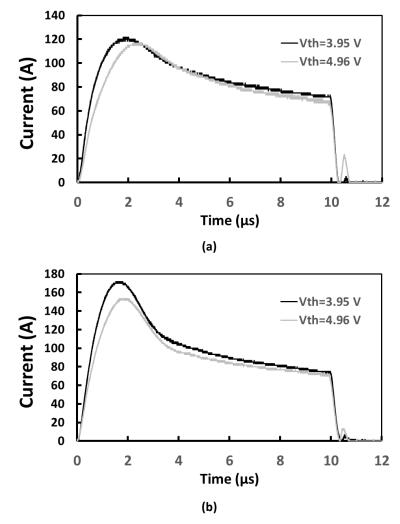

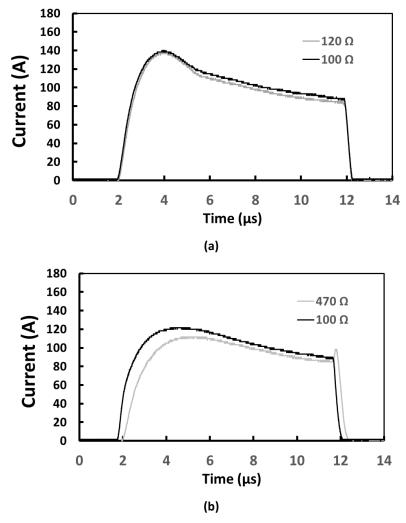

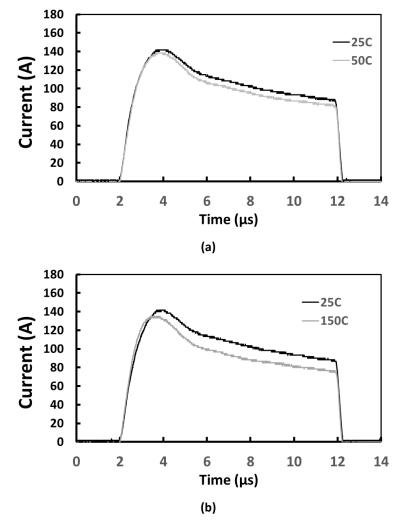

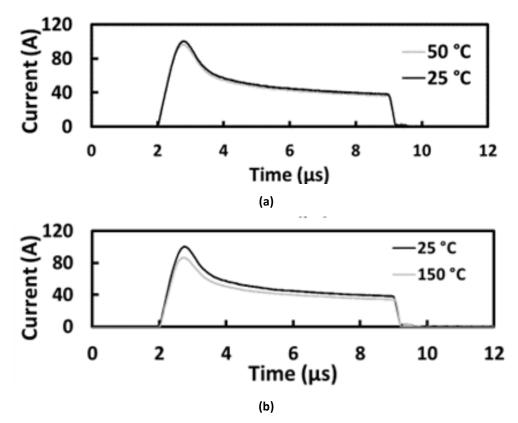

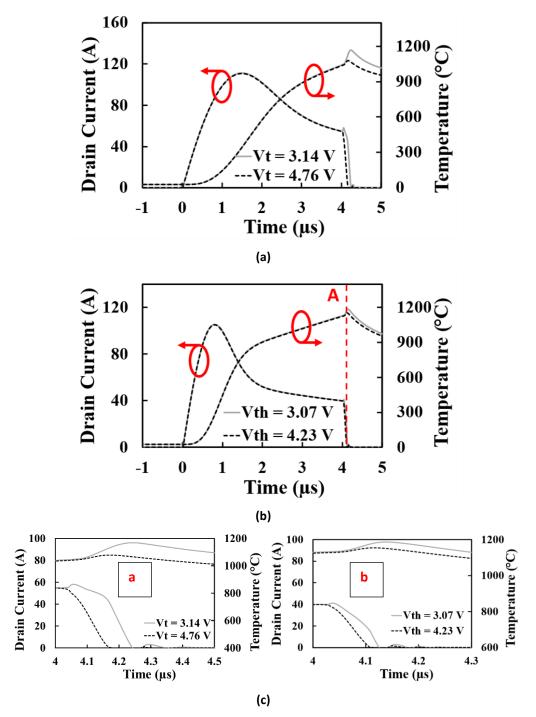

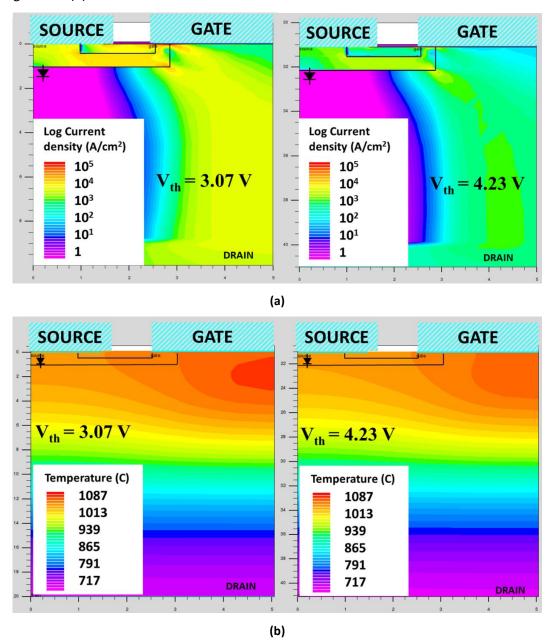

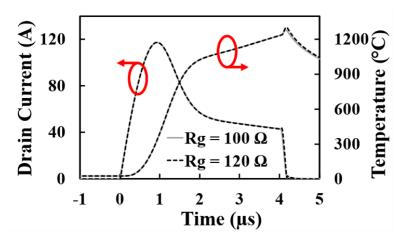

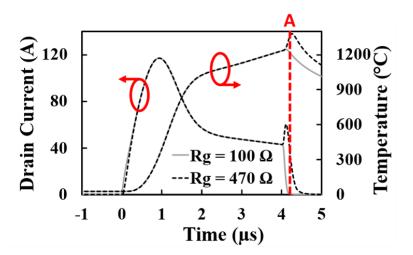

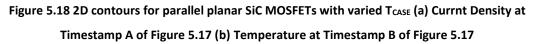

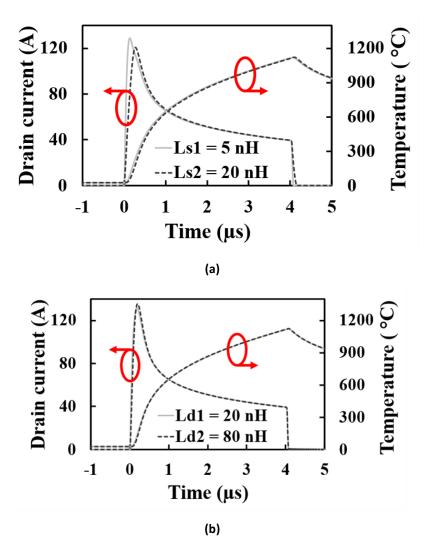

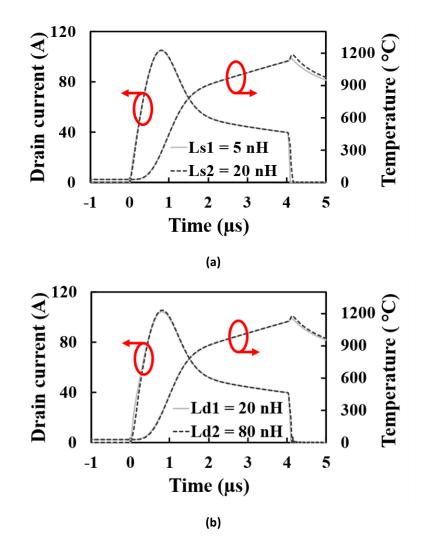

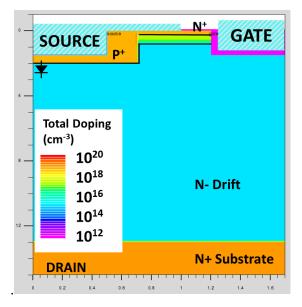

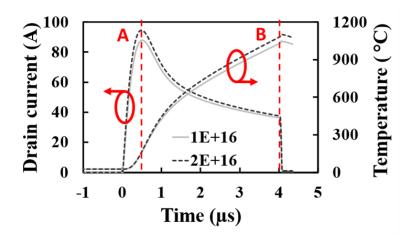

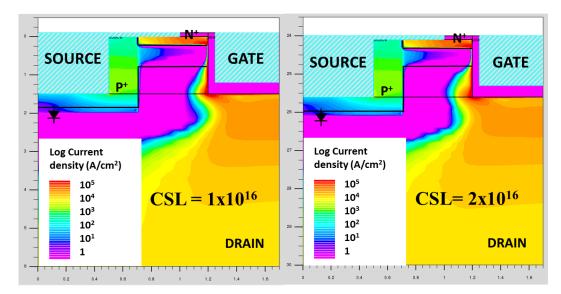

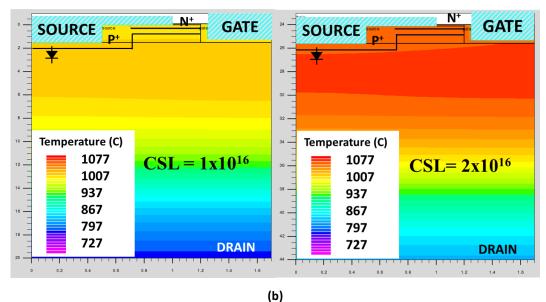

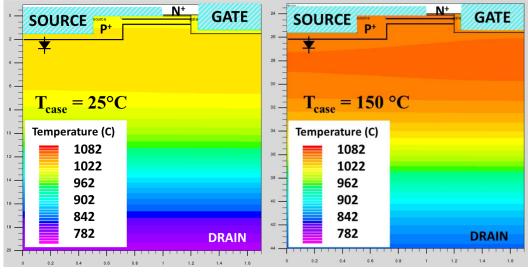

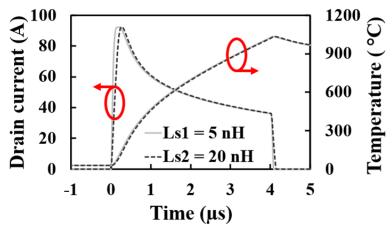

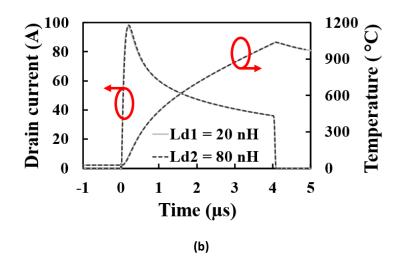

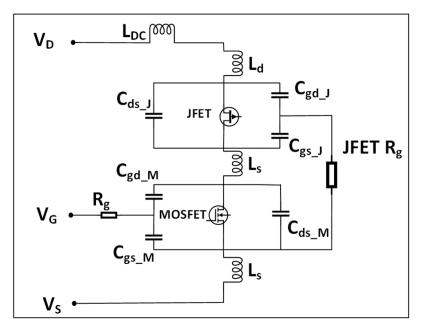

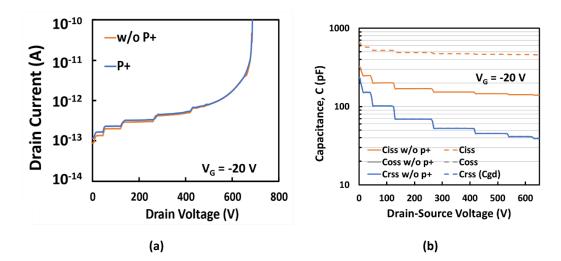

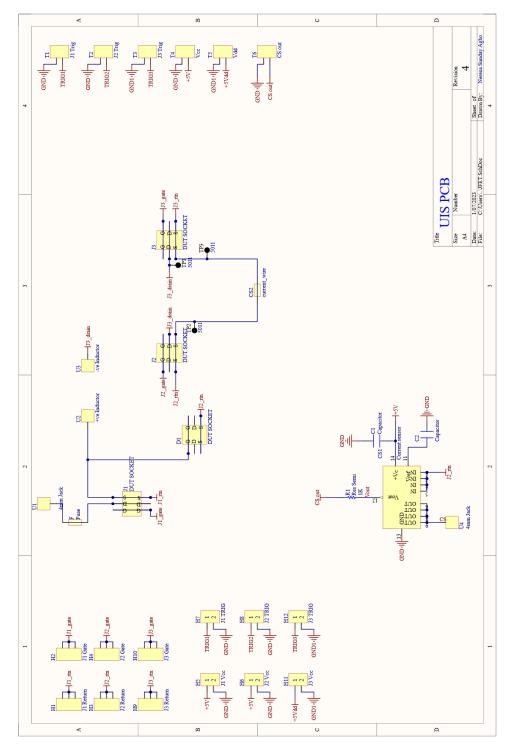

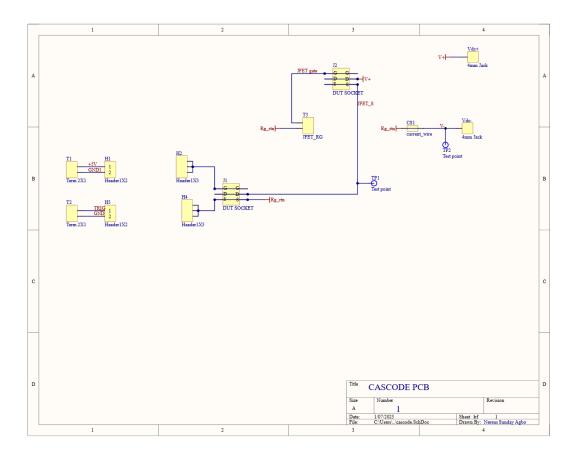

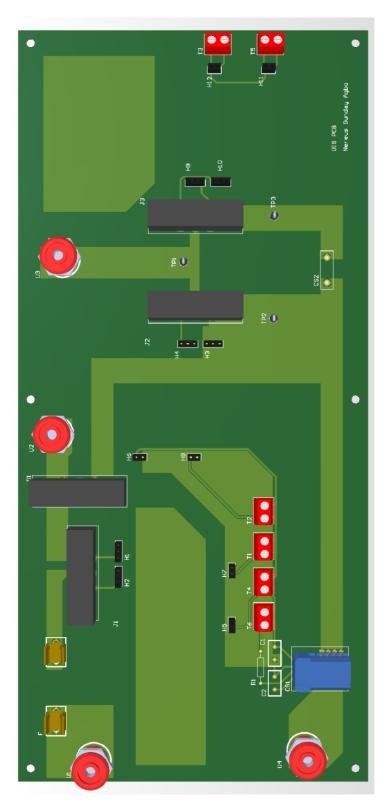

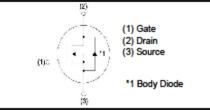

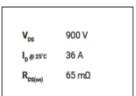

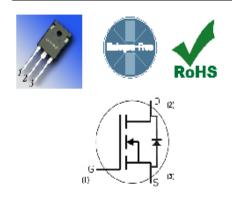

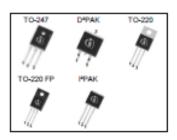

| Figure 4.2 Spice short circuit simulation of SiC MOSFET (a) Short circuit power (b) Simulated<br>Junction Temperature rise.85Figure 4.3 Spice short circuit simulation of SIC Cascode JFET (a) Short circuit power (b)Simulated<br>Junction Temperature rise.85Figure 4.4 Short Circuit Measurement Test system87Figure 4.5 (a). Short circuit test schematic (b) Gate pulses for short circuit measurements. 8787Figure 4.6 Short circuit current transients for the SiC Cascode JFET at (a) different VDS88voltages (b) different initial Junction Temperatures88Figure 4.7 Short circuit transients for the SiC Cascode JFET under different pulse durations89Figure 4.8 Short circuit VOS transients for the SiC Cascode JFET under different pulse<br>durations until failure (a) Short circuit VOS transients for the SiC Cascode JFET under different pulse<br>durations until failure.90Figure 4.10 Peak SHORT CIRCUIT Current for all DUTs in Table 4-2.91Figure 4.10 Peak SHORT CIRCUIT Current for all technologies (b) SHORT CIRCUIT Energy<br>density for all technologies (c) SCWT for each technology (d) SCWT normalized by chip size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |