University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

### A Thesis Submitted for the Degree of PhD at the University of Warwick

http://go.warwick.ac.uk/wrap/60452

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

### APPLICATIONS OF FORMAL METHODS IN ENGINEERING

Volume 1 of 2

Sang Cong Tran B.Eng (Hons.), M.Phil (Eng.)

A thesis submitted for the degree of Doctor of Philosophy in the Engineering Department University of Warwick December 1991

### Abstract

The main idea presented in this thesis is to propose and justify a general framework for the development of safety-related systems based on a selection of criticality and the required level of integrity. We show that formal methods can be practically and consistently introduced into the system design lifecycle without incurring excessive development cost.

An insight into the process of generating and validating a formal specification from an engineering point of view is illustrated, in conjunction with formal definitions of specification models, safety criteria and risk assessments. Engineering specifications are classified into two main classes of systems, memoryless and memory bearing systems. Heuristic approaches for specification generation and validation of these systems are presented and discussed with a brief summary of currently available formal systems and their supporting tools.

It is further shown that to efficiently address different aspects of real-world problems, the concept of embedding one logic within another mechanised logic, in order to provide mechanical support for proofs and reasoning, is practical. A temporal logic framework, which is embedded in Higher Order Logic, is used to verify and validate the design of a real-time system. Formal definitions and properties of temporal operators are defined in HOL and real-time concepts such as timing marker, interrupt and timeout are presented. A second major case study is presented on the specification a solid model for mechanical parts. This work discusses the modelling theory with set theoretic topology and Boolean operations. The theory is used to specify the mechanical properties of large distribution transformers. Associated mechanical properties such as volumetric operations are also discussed.

### Declaration

,

This dissertation is the result of my own work and, unless otherwise stated in the text, includes nothing which is the outcome of work done in collaboration. No part of this dissertation has already been, or is currently being, submitted for any degree, diploma or other qualification at any other university.

### Acknowledgement

During the time of this project, it is pleasing to note the number of people who have given their help and support. Thanks are due to my supervisor Dr. Evor Hines. He diligently read through the various drafts of this thesis and made valuable written comments. His insistence on clear writing has set a standard which I will always try to aim for.

In addition, I would like to express my sincerest thanks to Professor John Cullyer. This work could never have taken shape without his continued guidance and support. His patience during my earlier days and his ever optimistic manner has brought me through some of the most difficult times. He made valuable suggestions on earlier drafts of this thesis, and was the source of many excellent discussions.

This work could not have started without the financial support of T&N Technology Limited, Goodyear Transformers Limited and the Science and Engineering Research Council. The technical advice and individual guidance received while working there greatly help in this project. Of the innumerable people who helped, I must explicitly acknowledge Kevin Marks at T&N Technology Ltd. and Ken Frewin at Goodyear Transformers Ltd., who were the source of many stimulating discussions.

Thanks are also due to colleagues who have been around at various times to ask questions or answer mine. I would particularly like to thank Wai Wong for help at various times with HOL theorems and tactics and in response to my persistent questions about  $I_{\rm ATFX}$  typesetting.

This work would not have been completed without the HOL system. Thanks are due to the hardware verification group at Cambridge University. I am especially grateful to Dr. Mike Gordon for leading the way in hardware verification and giving advice when it was most needed. To my parents

,

# Contents

|   | Abs  | tract  |                                             | ii |

|---|------|--------|---------------------------------------------|----|

|   | Ack  | nowled | dgement                                     | iv |

|   | VO   | LUME   | 1                                           |    |

| 1 | Intr | oducti | on                                          | 1  |

|   | 1.1  | Backg  | round and Related Work                      | 3  |

|   |      | 1.1.1  | Design methodologies                        | 3  |

|   |      | 1.1.2  | Specification and verification for software | 4  |

|   |      | 1.1.3  | Specification and verification for hardware | 4  |

|   | 1.2  | Overv  | riew of Thesis                              | 7  |

| 2 | For  | mal M  | ethods in Safety-Related Systems            | 10 |

|   | 2.1  | The C  | oncept of Safety                            | 11 |

|   |      | 2.1.1  | Safety in computer-based systems            | 11 |

|   |      | 2.1.2  | Applying formal methods                     | 12 |

|   | 2.2  | Design | n Methodology                               | 13 |

|   |      | 2.2.1  | Development lifecycle                       | 14 |

|   | 2.3  | Safety | Criteria Selection                          | 16 |

|   |      | 2.3.1  | Measures of risk                            | 18 |

|   |      | 2.3.2  | Safety integrity levels                     | 19 |

|   | 2.4  | Deter  | mination of Assessment Levels               | 20 |

|   |      | 2.4.1  | Level selection                             | 22 |

|   | 2.5  | Select | ion of Development Techniques               | 22 |

,

,

|   | 2.6 | Validation and Verification         | 23         |

|---|-----|-------------------------------------|------------|

|   |     | 2.6.1 Informal techniques           | 24         |

|   |     | 2.6.2 Semi-formal techniques        | 25         |

|   |     | 2.6.3 Formal techniques             | 25         |

|   | 2.7 | Discussion                          | 26         |

| 3 | For | mal Specifications in Engineering   | 28         |

|   | 3.1 | Introduction                        | 28         |

|   |     | 3.1.1 System Classification         | 29         |

|   | 3.2 | Formal Model of Safety              | 31         |

|   |     | 3.2.1 Risk assessment               | 32         |

|   | 3.3 | A Specification Model               | 34         |

|   |     | 3.3.1 Model representation          | 35         |

|   |     | 3.3.2 Formula of correctness        | 36         |

|   |     | 3.3.3 Total and partial correctness | 38         |

|   | 3.4 | Specification Generation            | 40         |

|   |     | 3.4.1 Memoryless systems            | 40         |

|   |     | 3.4.2 Memory bearing systems        | 43         |

|   | 3.5 | Specification Validation            | 43         |

|   |     | 3.5.1 Memoryless systems            | 44         |

|   |     | 3.5.2 Memory bearing systems        | 45         |

|   | 3.6 | Description of Formal Methods       | 47         |

|   |     | 3.6.1 First order logic             | 48         |

|   |     |                                     | 49         |

|   |     | 3.6.3 Temporal logic                | 50         |

|   | 3.7 | Discussion                          | 51         |

| 4 | HO  | L Theorem Prover                    | 53         |

|   | 4.1 | Introduction                        | 5 <b>3</b> |

|   | 4.2 |                                     | 53         |

|   | 4.3 | The HOL logic                       | 54         |

.

|   |     | 4.3.1    | Terms                                      | 55         |

|---|-----|----------|--------------------------------------------|------------|

|   |     | 4.3.2    | Types                                      | 56         |

|   |     | 4.3.3    | Hilbert's ε-operator                       | 58         |

|   | 4.4 | The M    | leta-Language                              | 5 <b>9</b> |

|   | 4.5 | The H    | OL System                                  | 62         |

|   |     | 4.5.1    | Theories: definitions, axioms and theorems | 6 <b>3</b> |

|   |     | 4.5.2    | Primitive inference rules                  | 64         |

|   |     | 4.5.3    | Tactics and tacticals                      | 6 <b>6</b> |

|   | 4.6 | Summ     | nary                                       | 67         |

| 5 | Em  | bedded   | d Temporal Logic                           | 69         |

|   | 5.1 | Timing   | g Verification                             | <b>69</b>  |

|   |     | 5.1.1    | First order logic                          | 6 <b>9</b> |

|   |     | 5.1.2    | Temporal logic                             | 70         |

|   |     | 5.1.3    | Interval temporal logic                    | 70         |

|   |     | 5.1.4    | Other techniques                           | 71         |

|   |     | 5.1.5    | Higher order logic                         | 71         |

|   | 5.2 | Tempo    | oral Operators                             | 71         |

|   |     | 5.2.1    | Basic operations                           | 72         |

|   |     | 5.2.2    | Timing conditions                          | 73         |

|   |     | 5.2.3    | Defining time markers                      | 74         |

|   | 5.3 | Tempo    | oral Projection                            | 77         |

|   |     | 5.3.1    | Mapping function                           | 78         |

|   |     | 5.3.2    | Interrupts                                 | 81         |

|   |     | 5.3.3    | Time limits                                | 82         |

|   | 5.4 | Formu    | lation of Temporal Correctness             | 84         |

|   | 5.5 | Discus   | ssion                                      | 84         |

| 6 | АТ  | 'hrottle | e Control System                           | 8 <b>6</b> |

|   | 6.1 | Introd   | uction                                     | 8 <b>6</b> |

|   |     | 6.1.1    | System description                         | 87         |

|   |     | 6.1.2   | System requirements                                 | 88  |

|---|-----|---------|-----------------------------------------------------|-----|

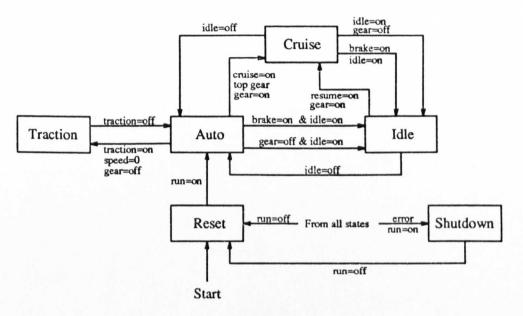

|   |     | 6.1.3   | Design methodology                                  | 90  |

|   | 6.2 | Backg   | round Behaviour                                     | 94  |

|   |     | 6.2.1   | Manual control                                      | 95  |

|   |     | 6.2.2   | Cruise/Resume control                               | 96  |

|   |     | 6.2.3   | Traction control                                    | 97  |

|   |     | 6.2.4   | Idle control                                        | 98  |

|   |     | 6.2.5   | Shutdown/Reset mode                                 | 98  |

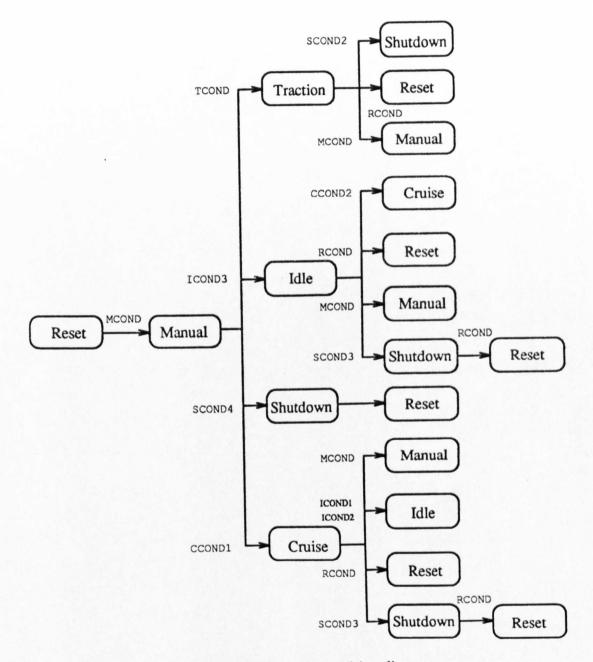

|   |     | 6.2.6   | Function NextState                                  | 98  |

|   | 6.3 | Foreg   | round Behaviour                                     | 101 |

|   |     | 6.3.1   | Motion                                              | 103 |

|   |     | 6.3.2   | Real-time characteristics                           | 104 |

|   |     | 6.3.3   | Maximum response time                               | 105 |

|   |     | 6.3.4   | Maximum registered time                             | 106 |

|   |     | 6.3.5   | Maximum transit time                                | 106 |

|   |     | 6.3.6   | Position and direction                              | 107 |

|   | 6.4 | Impro   | bying the Performance                               | 108 |

|   | 6.5 | The C   | omplete Specification                               | 111 |

|   | 6.6 | Verific | cation Plan and Methodology                         | 111 |

|   |     | 6.6.1   | Proof plan                                          | 112 |

|   |     | 6.6.2   | Safety properties                                   | 112 |

|   |     | 6.6.3   | State transitions                                   | 114 |

|   |     | 6.6.4   | Deterministic state-machine                         | 116 |

|   | 6.7 | Discu   | ssion                                               | 117 |

|   |     |         |                                                     |     |

| 7 | Mee |         |                                                     | 120 |

|   | 7.1 |         | luction                                             | 120 |

|   | 7.2 | Desig   | ning Mechanical Parts                               | 121 |

|   |     | 7.2.1   | Communication between the designer and the modeller | 122 |

|   |     | 7.2.2   | Time taken and costs incurred in the design process | 122 |

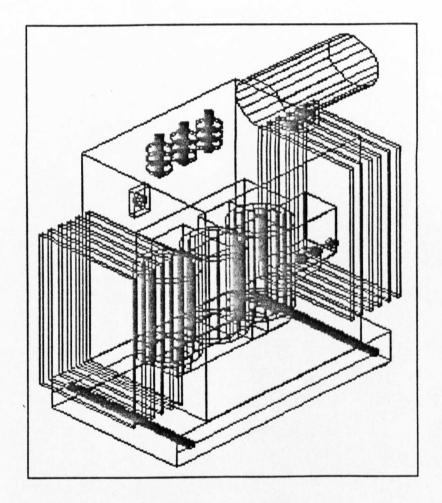

|   | 7.3 | Geom    | netric Modelling in Transformer Design              | 123 |

|   |            | 7.3.1   | Spatial arrangement                  | 123         |

|---|------------|---------|--------------------------------------|-------------|

|   |            | 7.3.2   | Volumetric verification              | 124         |

|   | 7.4        | Mathe   | matical Foundations                  | 124         |

|   | 7.5        | Point-S | Set Algebra                          | 127         |

|   |            | 7.5.1   | Metric space                         | 1 <b>29</b> |

|   |            | 7.5.2   | Open sets and neighbourhood          | 130         |

|   |            | 7.5.3   | Closed sets                          | 1 <b>32</b> |

|   |            | 7.5.4   | Closure                              | 133         |

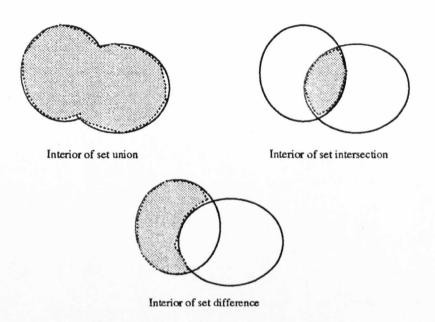

|   |            | 7.5.5   | Interior                             | 135         |

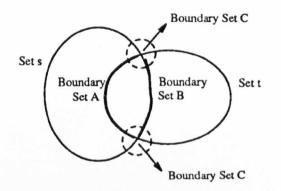

|   |            | 7.5.6   | Boundary                             | 136         |

|   |            | 7.5.7   | Dimensional property of boundary     | 140         |

|   | 7.6        | Closed  | i Point-Set Topology                 | 142         |

|   |            | 7.6.1   | Defining OBJECT                      | 144         |

|   |            | 7.6.2   | Solid primitives                     | 146         |

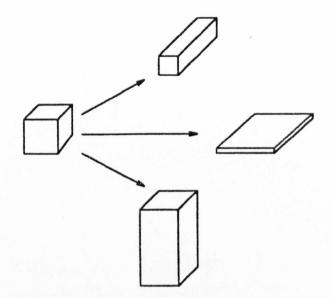

|   |            | 7.6.3   | Generic and parameterised primitives | 149         |

|   | 7.7        | Comb    | inations of Solid Primitives         | 151         |

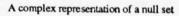

|   |            | 7.7.1   | Modified boolean operations          | 152         |

|   |            | 7.7.2   | Boolean model                        | 156         |

|   | 7.8        | Solid I | Modelling in Transformer Designs     | 157         |

|   |            | 7.8.1   | Null-object detection                | 161         |

|   |            | 7.8.2   | Specifying the manufacturing process | 164         |

|   |            | 7.8.3   | Computation of overall volume        | 166         |

|   | <b>7.9</b> | Discu   | ssion                                | 168         |

| 8 | Cor        | cludin  | ig Remarks                           | 171         |

| Ŭ | 8.1        |         | nary of Thesis                       | 171         |

|   | 0.1        | 8.1.1   | Methodology                          | 171         |

|   |            | 8.1.2   | Specification techniques             | 173         |

|   |            | 8.1.2   | Timing analysis                      | 174         |

|   |            | 8.1.4   | Specifying behaviour                 | 175         |

|   | 8.2        |         | ssion                                | 176         |

|   | 0.4        |         | JJIVI                                | 110         |

|      |                                                             | ·       |                                                   |     |  |  |

|------|-------------------------------------------------------------|---------|---------------------------------------------------|-----|--|--|

|      |                                                             | 8.2.1   | Correctness of a real design                      | 176 |  |  |

|      |                                                             | 8.2.2   | Relating different levels of abstraction          | 177 |  |  |

|      |                                                             | 8.2.3   | Verification process                              | 177 |  |  |

| 8.   | 3                                                           | Future  | Work                                              | 178 |  |  |

|      |                                                             | 8.3.1   | Executable specifications                         | 178 |  |  |

|      |                                                             | 8.3.2   | Computer aided design with formal methods         | 178 |  |  |

| 8.   | 4                                                           | Final T | Thoughts                                          | 179 |  |  |

| R    | efe                                                         | erences | 3                                                 | 181 |  |  |

| v    | 01                                                          | LUME    | 2                                                 |     |  |  |

| А    | A                                                           | Form    | nal Solid Modelling System                        |     |  |  |

| В    | B. Temporal Definitions and Theorems                        |         |                                                   |     |  |  |

| С    | C. HOL Specification of DBW Controller                      |         |                                                   |     |  |  |

| D    | ). I                                                        | formal  | Specification of Solid Modelling                  |     |  |  |

| E    | . F                                                         | aper -  | The Development of a High Quality Software Design | 1   |  |  |

| Met  | ho                                                          | lology  | for Automotive Applications                       |     |  |  |

| F    | F. Paper - Formal Methods in Automotive Applications        |         |                                                   |     |  |  |

| G    | G. Paper - On the Development of Formal Methods Based Soft- |         |                                                   |     |  |  |

| ware | e D                                                         | esign ] | Methodology for Automotive Applications           |     |  |  |

| Н    | [. H                                                        | Paper - | Formal Solid Modelling Using Higher-Order Logic   |     |  |  |

I. Paper - Applications of Formal Methods in the Transformer Industry

.

# List of Figures

,

| 2.1 | Design procedures                                 | 5 |

|-----|---------------------------------------------------|---|

| 2.2 | IEC mapping for software integrity level          | 9 |

| 2.3 | Factors affecting software integrity levels       | 0 |

| 3.1 | Representations of engineering systems            | 0 |

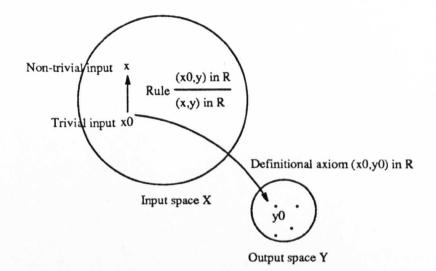

| 3.2 | Specification model                               | 6 |

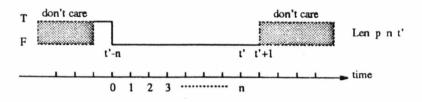

| 5.1 | Representation of Len                             | 4 |

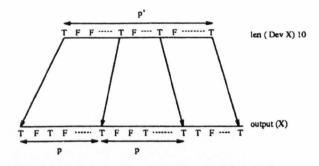

| 5.2 | The projection $p$ When $p'$                      | 7 |

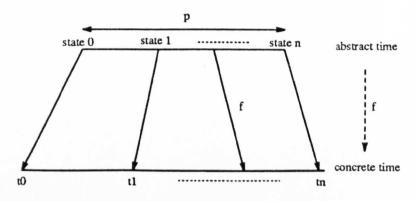

| 5.3 | Mapping from abstract states to time              | 9 |

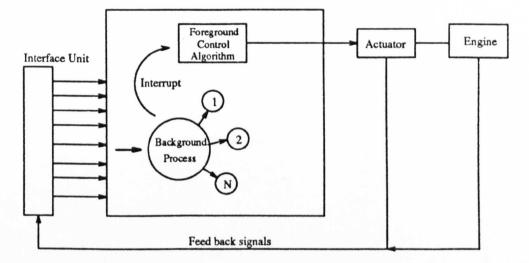

| 6.1 | DBW system overview                               | 8 |

| 6.2 | DBW State diagram                                 | 5 |

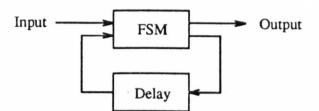

| 6.3 | A Mealy machine                                   | 1 |

| 6.4 | DBW state transition diagram                      | 2 |

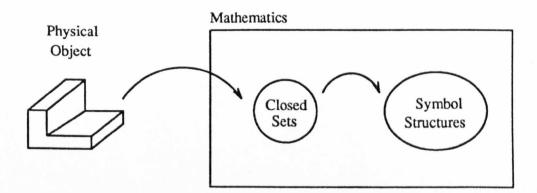

| 7.1 | The use of formal geometrical model               | 3 |

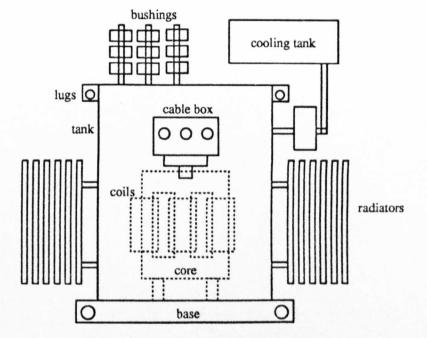

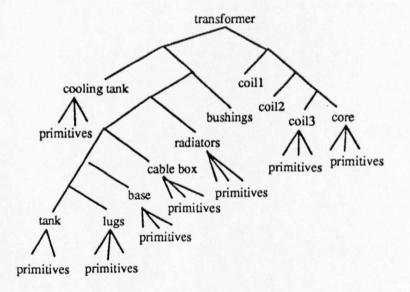

| 7.2 | The schematic diagram of a simplified transformer | 5 |

| 7.3 | Representation scheme                             | 7 |

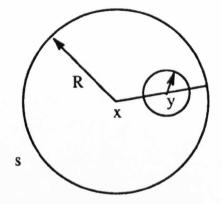

| 7.4 | Neighbourhood in an open ball                     | 2 |

| 7.5 | Defining the interior of set operations           | 6 |

| 7.6 | Set compositions of the boundary of s INTER $t$   | 9 |

| 7.7 | Scaling transformation                            | 9 |

| 7.8 | Dangling faces                                    | 2 |

| 7.9 | Geometric components of A REG_INTER B             | 4 |

-

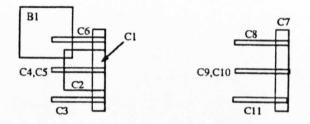

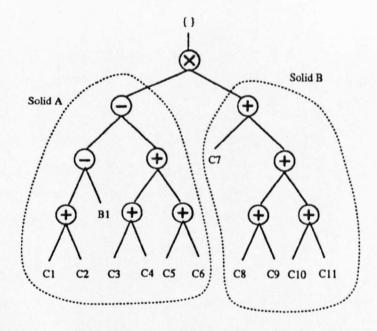

| 7.10 | A geometric model of a power transformer | 158 |

|------|------------------------------------------|-----|

| 7.11 | An example of a null object              | 162 |

| 7.12 | An example of process simplification     | 165 |

| 7.13 | An example of volume verification        | 168 |

# List of Tables

.

| 2.1 | Available standards ( $$ = applicable). | 17  |

|-----|-----------------------------------------|-----|

| 2.2 | Safety integrity levels                 | 21  |

| 2.3 | Assessment levels                       | 21  |

| 2.4 | Assessment techniques                   | 23  |

| 4.1 | Predicate logic notation                | 55  |

| 7.1 | Definitions of geometric objects        | 145 |

ډ

## Chapter 1

# Introduction

As the cost associated with the development of computer-based systems continues to fall, industry worldwide is increasingly coming to depend upon new technology to maintain a competitive edge whilst being able to operate ever more complex control systems that require a high degree of reliability, integrity, dependability and safety. Such systems are generically referred to as being safety-critical.

Engineers and managers have begun to realise that with their new technology comes flexibility and additional safety considerations. These considerations include,

- The knowledge that the correct and safe operation of the business, capital equipment or control system is dependent upon such technology.

- The risk of causing a loss of human life, economic loss or environmental damage is outside their normal engineering judgement.

- That the conventional safety assessment are inefficient and fail to identify weaknesses in the operation of the system.

Till now the only assurance of correct operation of a safety-critical system has been by conventional testing techniques. However, such techniques are not without flaws and cannot locate all faults. Faults often only materialise many months or years after a system has been put into operation, possibly leading to very expensive recall procedure or retro-fits on site, if not dangerous incidents. Manufacturing and nuclear industry, as well as defence contractors, have an urgent requirement to gain confidence in the correct and safe operation of their computer based systems.

With the advent of computers, designers have been able to design more complex systems, since they can be simulated on computers and so debugged to some extent before manufacture. However, for large systems, exhaustive simulation is prohibitively expensive, and requires exponentially large simulation time even with today's fastest computers.

Due to these seemingly unsurmountable problems, designers have been forced to look in other directions to verify designs before building them. Even though the cost of manufacturing is coming down, it is still important to have confidence in the design before it is committed to implementation. This is essential since it is not always possible to test every aspect of the design in the time available. Whilst many applications can tolerate some errors, there are others where minor flaws in the system could mean dangerous or may be too expensive to tolerate. These include,

#### • Safety critical applications :

Increasingly, integrated circuits of enormous complexity are being used in areas where errors in these circuits could lead to loss of life. Examples include flight control systems, railway signalling systems, electronic throttle controller, medical life-support systems such as pacemakers, military applications, nuclear plant controllers, and anti-lock braking systems in cars (see [35]).

• Remotely sited applications :

Applications where access to the systems is difficult would benefit from having the design 100% correct. This is simply because the cost of repairing or replacing faulty components would be too high. Examples include systems installed in arctic regions, satellites, nuclear plants and systems installed on oil or gas pipelines.

• Volume production applications :

2

Many industries manufacture systems for the mass market. If the design of a device in such systems is faulty then the cost of recalling and repairing it would be very high. Examples include circuits in automobiles, in telecommunication systems, and so on.

With important applications such as these, it is necessary to ensure that a design is correct. To achieve this, attention has turned to formal methods for specifying and verifying the correctness of system design.

#### **1.1 Background and Related Work**

Techniques used for the complete specification and verification of systems are briefly summarised in this section. Summaries of only the most relevant work are given, together with pointers to others.

#### 1.1.1 Design methodologies

To-date research reveals an increasing awareness of the process of design but is fundamentally naive in its treatment of methodologies and formal models. It is from work on programming methodology that the basic idea that we have used as the framework of this thesis, have been imported. There are a number of structured design methodologies available [105]. These include MASCOT, SSADM, and JSD. MASCOT is primarily a method for the design and implementation of real time systems. The method is widely used in the UK defence and avionics industries and originated from work done at RSRE. Whilst MASCOT is a development technique, which uses of a graphical data-flow network as the medium for expressing software structure, SSADM in contrast, is a well-defined step-by-step approach. Rather than concentrating on one approach such as functional analysis, SSADM regards functions and data with equal importance. Another important design methodology is the Jackson Development Method (JSD). Within JSD there is a distinction between specification and implementation. JSD approaches the problem via the idea of a model and its relation to function. First an abstract description is written and then one determines how that abstract description is created in an implementation. In JSD the abstract description is created in two steps, and its realisation in a third step which is the development procedure. It is not until the fourth step that system functions are considered.

#### 1.1.2 Specification and verification for software

There are many formalism for the formal specification of software based upon axiomatic definition or model building. For example, the algebraic specification languages OBJ [40], and CLEAR [24] are axiomatic formalisms, and the notation Z [104] is model based. The semi-formal design methodology VDM (Vienna Development Method) is also model-based [67].

Research on specific specification techniques has, more recently, led to research into the general ideas about specifications and operations on specifications. These attempts at general theories aim at more complex notation than those given in Chapter 3 of this thesis, but they are relevant to the further development of the described framework and its application to system design. A particularly useful general study of refinement is described by Back [8].

Much work is concerned with the generation of logical approaches. For example, in Cohen [30], there are simple but general definitions concerning specifications modelled by sets of statements in formal systems. A simple study of operations on specifications is described by Sanella and Wirsing [100]. A substantial theory of such specifications is presented in Goguen and Burstall's theory of institutions [41]. Other approaches work on themes of specifications which are modelled by relations as in, for example [59], to analyse ideas about modularity such as in Back and Mannila [7], or algebraically, as in Bergstra [13].

#### 1.1.3 Specification and verification for hardware

The formal verification of digital hardware is most simply founded upon clearly defined logics such as first order logic, higher order logic, temporal logic, modal logic and so on.

The early work of Milner and others on the LCF project [43] inspired much effort in the area of mechanised theorem proving. A specialised language was developed for specifying and verifying hardware [45] which led to the development of the interim LCF-LSM theorem proving system [46]. Many examples were done using this system including the verification of a simple computer [47]. Many improvements to the LCF system have been made over the years, including an improved rewriting package [91], and a new tactics package [92]. Hanna and Daeche then independently developed the VERITAS theorem prover based on higher order logic [53,54]. With the improved expressive power of higher order logic becoming increasingly attractive, and with the experience gained from the LCF family of theorem provers, Gordon then developed the HOL theorem proving system [49,50], which forms the basis of the work done in this thesis. A number of examples have been successfully completed which demonstrate the use of higher order logic as a vehicle for specification and verification. These include the verification at the detailed timing level of a D-flipflop implemented in logic gates (see [54] and [56] for proofs done in the VERITAS and the HOL systems respectively), the verification of a ring interface chip [48], re-proof of the computer in HOL [68], and the first level proof of correctness of the VIPER microprocessor [31].

The systems mentioned above are all based on general theorem provers, where the proof is done manually and the system merely does the housekeeping. In the direction of automated theorem provers is the work of Boyer and Moore [17]. This has been used by Hunt to verify the correctness of a 16-bit microprocessor [61]. The underlying logic of this theorem prover is first order predicate logic without quantifiers. In principle, proofs are done automatically by this system, but in practice the theorem prover needs to be guided considerably by carefully requesting simpler theorem to be proved first. Barrow's VERIFY system [12] is another example of an automated theorem prover. The underlying model used by this system is that of finite state machines, based on Gordon's LSM language [46]. In both of these systems, logic gates form the set of primitive devices on the basis of which hardware verification is done.

Another general formalism used for verification is temporal logic. An interesting variant is that developed by Moszkowski known as Interval Temporal Logic (ITL) [88]. Proofs using ITL were initially done by hand. Recent work by Hale [52] shows that the HOL system can be used to mechanise proofs in ITL. A subset of ITL has also been developed as an executable language known as Tempura [89]. More recently, Leeser has used a variant of this formalism together with Prolog to reason about circuits down to the detailed transistor level [72].

On the side of more specialised formalism are CIRCAL and  $\mu$ FP. The early work of Milne and Milner on Concurrent Processes [81] inspired a number of calculi. Milne went on to develop CIRCAL [82,83], while Milner went in a slightly different direction and developed the Calculus of Communicating Process (CCS) [85,86]. In the CIRCAL framework, the structure of hardware devices is represented hierarchically, communication between components being effected through commonly named ports. Behaviour in this framework is described as a sequence of events on the external ports of devices. Operators are provided for the composition and the hiding of ports. Several examples have been completed using this framework, including a simple CRT controller by Traub in [113]. Here Traub also presents the various temporal concepts needed to model different granularities of time and the means of moving between them. A Lisp based environment for doing proofs in this formalism has also been developed [112].

Another motivation for using formal methods is the ability to transform designs in a correctness preserving way and hence perform refinements. One common aim is to convert simple but inefficient algorithms into complex but efficient ones. A recent general treatment is presented by Sheeran [101]. Design transformation and derivations are emerging as a practical technique in research on special architectures such as systolic arrays as described in, for example [11].

Sheeran uses  $\mu$ FP [101], which is an extension of the programming language FP developed by Backus. Sheeran introduces the  $\mu$  operator into the basic language FP to model memory in circuit. Both the behaviour (functional part) and the

implementation (geometric part) of a circuit can be presented in this language. With the aid of the  $\mu$  operator, the inputs and outputs are modelled as streams. Behavioural descriptions of circuits can be transformed into their geometric forms thus leading to correctness by construction. Only synchronous system can be modelled by this formalism. Examples done using this framework include the design of a systolic correlator [101].

The above work has concentrated on the gate level and higher. Winskel [116] described a compositional model for the more primitive components of a VLSI technology, namely transistors, capacitors, etc. This work is based on the simulation models developed by Bryant [21]. Though this work is at a more detailed level than what has been described so far, it is not clear how it can be related to the system level.

#### **1.2 Overview of Thesis**

Below is a brief description of the organisation of the material presented in this thesis.

- Chapter 2 provides a general framework for the development of safetyrelated systems based on the selection of criticality and the required level of integrity. Different development and validation techniques are proposed for different levels of integrity required. For very highly safety critical systems, the main emphasis is on the use of formal methods to verify the correctness and ensure that the required level of safety integrity is achieved. This chapter lays down a methodological approach based on which formal methods can be consistently introduced into, and incorporated with, the system design lifecycle.

- Chapter 3 gives an insight into the process of generating and validating a formal specification from an engineering point of view. We give formal definitions of safety and that of a specification. Engineering specifications are classified into two main classes of systems, memoryless and memory

bearing systems. Heuristic approaches for specification generation and validation of these systems are presented and discussed. We also give a brief summary of currently available 'ormal systems and their supporting tools and then the reasons for selecting higher order logic as a specification formalism are discussed.

- Chapter 4 provides a brief description of the HOL system. We describe the species of higher order logic used, the meta-language ML in which the logic is formulated, and the theorem proving strategies used to conduct proofs in HOL. The main emphasis in this chapter is on those features of the HOL system which are used in later chapters of this thesis.

- Chapter 5 illustrates the concept of embedding one logic within another mechanised logic in order to prove soundness and provide mechanical support for proofs and reasoning. This chapter provides a temporal framework based on which the design of a real-time system described in the following chapter can be rigorously specified and validated. Formal definitions and properties of temporal operators are defined in HOL and real-time concepts such as time marker, interrupt and timeout are also discussed.

- Chapter 6 first gives a brief overview of the Drive-by-Wire control system together with its interfaces. Then a novel design is presented which uses the temporal constructs of the previous chapter. A formal specification for this system is presented together with complete proof procedures of safety and correctness. Some of the difficulties involved in arriving at the correctness statement and constructing the proof are discussed.

- Chapter 7 provides a second case study in specifying a solid modelling theory for mechanical parts. The work illustrates one aspect of formal validation techniques, that is correctness by construction. This chapter presents the modelling theory with set theoretic topology and boolean operations. The theory is used in this case to specify the mechanical properties of large

1

distribution transformers. Associated mechanical properties of transformers such as volumetric operations are also discussed.

• Finally, Chapter 8 evaluates the research described in this thesis. Some ideas for further research, possible solutions to problems encountered, and improvements to current strategies are also proposed.

2

## Chapter 2

# Formal Methods in Safety-Related Systems

Despite the ever increasing importance of software systems in UK industry, there is considerable difficulty in providing systems that meet the user requirements, even when safety is not an issue. In response to increasing concern over the use of computer-based systems in safety-related applications, recent government reports and guidelines, such as the ACARD report [1] and the Draft Interim Defence Standard 00-55 [66], call for the use of formal methods, particularly for high integrity applications. Use of the best software development methods available, including formal methods, may also be advisable to prevent legal liability for damage or injury caused by malfunctioning software. However, despite these recommendation there is little evidence of these methods being adopted. Most industries using computer control seem reluctant to invest in staff and computer tools. This chapter explores the reasons for the special concerns for the safety of computer-based systems, the ways in which formal methods can reduce the risk of system failure, and how it can be effectively incorporated into the development cycle.

#### 2.1 The Concept of Safety

It should be emphasised that the present research is concerned with systems which are used in *safety-related* applications. A safety-related system is one via which the safety of human beings and the environment is to be assured. Such safety-related systems can range from quite small items, such as traffic light controllers, to major applications such as nuclear power station and avionics systems. Therefore, safety-related systems should imply those which are critical in one or more of the following areas,

- Safety critical: a system in which failure or design fault could cause risk to human life.

- Security critical: a system in which failure or design fault could cause unauthorised disclosure, alteration, loss or destruction of material.

- Performance critical: a system in which failure or design fault could cause the system not to achieve an important objective.

- Cost critical: a system in which failure or design fault could cause a significant financial loss.

- Environmental critical: a system in which failure or design fault could cause significant damage to the environment or property. This could have associated with it, disruption to normal life and possibly significant political factors.

#### 2.1.1 Safety in computer-based systems

There are many factors contributing to concern over the safety of computer-based systems. Firstly being digital, they are unable to respond in a continuous and interpolative manner that is characteristic of analogue solutions. As a result, computer-based system are unable to average out the effects of inherent design errors, or of erroneous data input. Consequently, digital design principles often

gives way to rule of thumb and engineering judgement to achieve the desired solution.

A second feature of computer-based systems is that where software is used to carry out system functions there is a tendency to build more and more complex systems since constraints such as volume, weight, and hardware rework costs have lesser impact. As systems become more complex the ability to demonstrate adequately the correct performance of the system under all operating conditions is greatly reduced and there is a significant risk that design errors will not be detected. Testing systems and their components does not guarantee that they will operate safely with values between input limits, and furthermore an exhaustive testing of all possible paths through a complex system is practically impossible.

Additionally, concern for the safety of computer-based systems has been compounded by the rapid increase in the demand for computer skills in recent years. As a result many system designers have little training in the pure mathematics disciplines of set theory and logic. These factors have produced a generation of computer professionals who are almost unaware of the relevant mathematics and modelling techniques.

#### 2.1.2 Applying formal methods

The design of a computer-based system, as for all sequential systems is based theoretically on propositional logic and on the assumption that system outputs and internal stages are a function of all previous inputs and the most recent internal state. For relay logic, this type of system has been traditionally represented through the use of state transition tables and diagrams. Unlike relay logic, however, a computer-based system does not behave in a concurrent fashion. For this reason, the order in which the logic is executed is identified as a logical relationship between input condition, system state and output condition for all values of input data. This is achieved through the use of predicate calculus, which allows properties of objects manipulated by the system to be expressed.

Formal methods are mathematical languages which possess rigorously de-

fined syntax and semantics, based on the mathematics of set theory and logic. Using these methods a functional specification of a system can be regarded as a set of mathematical equations and the rules for logical equivalence can be used to prove that two expressions are equivalent. This process has the result that abstract specifications can be defined in the first instance to model the behaviour of the system as required by the user, and can be subsequently refined to more detailed expressions, and eventually into a suitable implementation. At each step logical equivalence can be proven between the expressions, thus proving that the final implementation complies with the abstract specification in every feature. The process offers a potential for eliminating the risk of failing to meet the user requirement, since specification can take place at an abstract level, and could potentially improve design efficiency, as the process is amenable to automation.

However, the use of formal mathematical techniques are not without its drawbacks. Therefore, in order to make an effective approach towards system development for a wide range of safety-related applications, a framework is needed to select and apply appropriate techniques during the development process. The following sections described a methodological approach in the development cycle of safety-related systems.

#### 2.2 Design Methodology

The design approach taken in this thesis consists of a number of consecutive conceptual stages as follows,

- Safety criteria selection: The safety criteria are established in discussion with the user. These are the criteria by which the system is expected to conform for it to be judged operable. The safety criteria differ for each system, industry sector and application because of the way in which the system is to be used, given legal, economic and environmental considerations.

- Determination of assessment levels: For each hazard criteria a specific assessment level is established after discussion with the user. Since there are

no universal techniques for making this type of assessment the criticality of the system with respect to the particular application, is determined and from this the appropriate technique is chosen. By this consultation the user is assured that the correct emphasis is placed on the application.

- Selection of development techniques: Each hazard criteria is evaluated using the selected technique, in terms of the hardware, software and as a complete system.

- Validation and verification: For each hazard criteria, the system will be assessed to conform to some recognisable standard of safe/reliable operation for the agreed assessment level or will be found to be deficient in some way.

#### 2.2.1 Development lifecycle

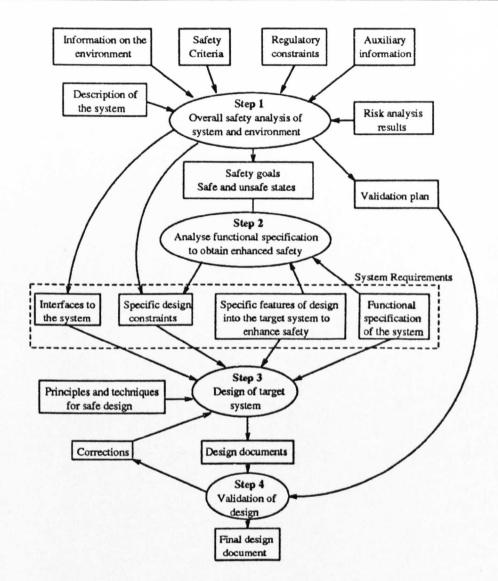

The principles just described can be embodied in four main steps, as shown in Fig.2.1. The first two steps do not deal directly with the design process. Rather they are part of the preparation needed before one can design safety features into the target systems. They usually require a broad range of inputs, including some specialised plant knowledge. It should be noted that the final specification of the target system must itself be safe.

• Step 1: Safety relevant information on the plant and the environment is compiled in this activity. Sources of information can be plant and environment descriptions, risk analyses etc. Auxiliary information such as regulations and general safety criteria should also be gathered in this step. The result of this step is a set of safety goals which should be fulfilled in the design of the target system. These safety goals are often expressed as a set of unsafe states the plant should not be brought into by the target system. A set of specific design constraints is produced during this step, along with a partial validation plan.

Figure 2.1: Design procedures

• Step 2: The initial functional specification should be examined closely with respect to the safety goals established in step 1. The potentially safety critical parts of the target system should be highlighted in order to identify where specific safety measures should be designed into the target system. The result of this step is a specification of the special features which should be designed into the target system in order to enhance safety. These should be added to complete the functional specification.

The third and fourth steps are concerned with the design of the target system and its verification.

- Step 3: The target system is designed on the basis of the functional specifications and the description of the interfaces to the plant, as well as the specification of safety enhancing features made in step 2 and the specific design constraints determined in step 1. During this activity one should also utilise general principles and techniques for safe design, which should have been identified before the design started. The result of this step will be the target system design document.

- Step 4: The design documents are verified with respect to the functional specification, and it is also confirmed that the specific safety relevant requirements and recommendations developed in the first three steps have been followed. Information on any required corrections is returned to step 3. After this step, the final design document is complete.

Needless to say, a high quality of project management and quality control is needed in carrying out these four steps if the potential safety gain is to be realised. The verification procedure in the final step can only proceed properly if full records exists of the progress through the first three steps. The choice of suitable techniques for these steps and the application of the chosen ones are not trivial and the criteria for selecting appropriate techniques are discussed in section 2.5. The following sections discuss the principles and procedures involved in these steps in more details.

#### 2.3 Safety Criteria Selection

The safety criteria for a system must satisfy any relevant legal requirements. Many regulatory authorities have issued guidelines establishing criteria and there are a number of national and international standards. In addition, many companies have developed their own internal standards. Table 2.1 shows some national

|                                  | Defence      | Aerospace    | Nuclear      | Transport    | Medical      | Chemical     | Automation   | 0il/Gas      | Energy       | Finance      |

|----------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| BS5750 <sup>[22]</sup>           |              | $\checkmark$ |

| BS5724                           |              |              |              |              | $\checkmark$ |              |              |              |              |              |

| BS5882 <sup>[23]</sup>           | $\checkmark$ |              | $\checkmark$ |              |              |              |              |              |              |              |

| IEC 880 <sup>[62]</sup>          |              |              | $\checkmark$ |              |              |              |              |              |              |              |

| IEC SC65A WG9/10 <sup>[63]</sup> |              |              |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |

| AQAP 1/13 <sup>[4,5]</sup>       | $\checkmark$ |              | $\checkmark$ |              |              |              |              |              |              |              |

| Def Stan 00-16 <sup>[36]</sup>   | $\checkmark$ |              | $\checkmark$ |              |              |              |              |              |              |              |

| Def Stan 00-55 <sup>[66]</sup>   | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |              |              |              |

| Def Stan 00-31 <sup>[65]</sup>   | $\checkmark$ | $\checkmark$ |              |              |              |              |              |              |              |              |

| CAA 690                          |              | $\checkmark$ |              |              |              |              |              |              |              |              |

| NES 620 <sup>[90]</sup>          | $\checkmark$ |              | $\checkmark$ |              |              |              |              |              |              |              |

| RTCA DO-178A <sup>[98]</sup>     |              | $\checkmark$ |              |              |              |              |              |              |              |              |

| HSE PES1/2 [60]                  |              |              | $\checkmark$ |              |

Table 2.1: Available standards ( $\sqrt{}$  = applicable).

and international standards and their suitable application areas. It should be noted that the table is by no means complete.

From an engineering viewpoint, safety criteria for a system can be either qualitative, for example build to a design standard, or quantitative, such as to build a system so that it does not fail in a dangerous mode more than  $10^{-6}$  times per year. In both cases, it is important to carry out hazard analysis either as part of a process to demonstrate compliance with a numerical target or to alert the designer as to whether or not the applied standard is appropriate.

Quantitative safety criteria are most often used for high risk situations but it should be noted that it is not possible, given the current state of knowledge, to quantify system safety integrity. However, this does not mean that quantified safety criteria for the system as a whole cannot be used. The numerical figure can be used to aid in the decision on the degree of rigour required in the system development process.

#### 2.3.1 Measures of risk

Any approach to safety-related systems has to include a wide range of different types of application presenting a wide variety of different risks. The hazards associated with such diverse applications vary greatly both in character and consequence. Risk is defined by IEC in [63] as follows,

The combination of the frequency, or probability, and the consequence of a specified hazardous event.

However, the means of combination of the frequency, or probability, and the consequence is undefined. The following means of combination could be considered given suitable values for the consequences of hazards,

#### $H_n$ = frequency of occurrence x consequence of hazard

where  $H_n$  represents some subjective assessed measure of risk associated with the hazard. As a result the degree of risk associated with different applications also varies. There is no clear cut point at which we can say this application is safety related and we shall apply full rigour to its development. Safety is essentially a concept which depends on current social values and in fact, it concerns with the level of risk at which the user is prepared to tolerate. Considerations which affect the acceptable level of risk  $H_n$  include

- the number of people affected when a hazard occurs, and

- the degree to which individuals may choose to subject themselves to the risk. For instance, it can be chosen subjectively and quantitatively that the affected radius of a railway accident is 50 metres, whilst it is about 20 metres in a car accident [107,108].

Moreover, since other economic and social factors also play an important part in the consideration, a faithful assessment of the level of risk involved should not only consider the negative hazardous effects but also the positive contributions

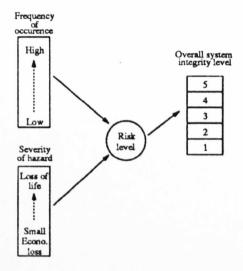

Figure 2.2: IEC mapping for software integrity level

of the system. That is the benefits to be derived from the application should also be taken into account.

The benefits derived from the application and harmful consequences of the hazard may have a direct or indirect effect. For instance, the direct environmental consequences of a population incident may well be associated with indirect effects which relate to the long-term health of the users.

#### 2.3.2 Safety integrity levels

Safety integrity is a continuous quantity which is generally assessed in subjective terms as safe or unsafe, that is either one side or the other of a level which is regarded as acceptable. In practice a discrete measure is used which allows safety integrity to be expressed in quantified terms. The quantification is rather crude, typically the safety integrity of a system is expressed as one of several levels ranging from highly catastrophic hazards to a very low risk level.

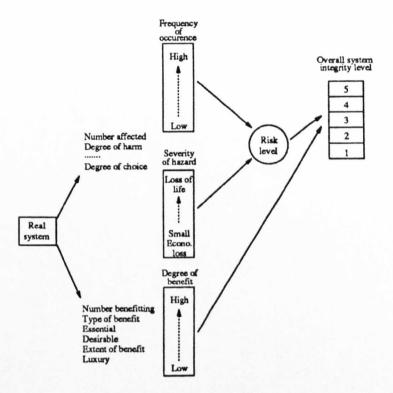

The IEC in [60] postulated a mapping between these safety integrity levels and the consequences associated with the hazard concerned as shown in Fig.2.2. However, this mapping is purely illustrative. As was discussed earlier, safety integrity is affected by a number of factors other than the consequences of the hazard. These factors and their inter-relationships are illustrated in Fig.2.3.

Figure 2.3: Factors affecting software integrity levels

### 2.4 Determination of Assessment Levels

So far, we have identified four major aspects of safety related system involving different levels,

- the severity of hazard,

- the frequency, or probability, of occurrence,

- · the safety integrity required, and

- the degree of assessment required.

The level of required safety integrity relates to the means used to both develop and access the system. The level of assessment relates only to the means used to ensure that an acceptable level of safety is achieved. The severity of hazard and the frequency of occurrence, as discussed in section 2.3.1, are the basis for the selection of safety integrity and assessment levels.

| Integrity level | Associated with            |

|-----------------|----------------------------|

| Low             | local environmental damage |

| Medium          | wide environmental damage  |

| High            | small scale injury         |

| Critical        | small scale loss of life   |

| Catastrophic    | wide scale loss of life    |

Table 2.2: Safety integrity levels

| Level | Assessment                     |

|-------|--------------------------------|

| 0     | System overview                |

| 1     | System structure analysis      |

| 2     | System hazard analysis         |

| 3     | Rigorous analysis              |

| 4     | Formal mathematical techniques |

Table 2.3: Assessment levels

When assessing safety related systems we identify five levels of hazard severity, five levels of safety integrity and five levels of safety integrity assessment, based on the work done by the HSE [60], IEC [63] and other bodies [62,66]. Table 2.2 illustrates the association we make between safety integrity level and hazard severity. Notice that the levels we use do not correspond exactly with those described by the IEC in [63]. We do not explicitly use levels of frequency of occurrence. Rather the frequency of occurrence of a hazard is implicitly incorporated into the scale of hazard severity.

Table 2.3 identifies the levels of assessment. These are associated with the levels of hazard severity and safety integrity identified in Table 2.2. The association of levels of hazard severity, frequency of occurrence, safety integrity and assessment is flexible in the sense that safety is essentially a subjective quality, based on a variety of different factors for which there are few measures and no generally agreed means of combination.

#### 2.4.1 Level selection

One of the most difficult steps is the choice of a level at which to assess the system and its components. This is related to the level of safety integrity which the system should achieve. The required level of safety integrity summarises many interlinked points, all of which are considered,

- Potential for loss of life

- Potential for human injury

- Potential for environmental damage

- Potential for economic damage

- Potential benefit derived from the system

- Expected number of instances of the system

- Expected number of occurrences of the hazard

- Contribution of the system to safety.

The process of determining the assessment level for a particular system is represented by Fig.2.3, which summarises the relationships between the various factors which contribute to safety integrity and the contributions made by different aspects of a system to the overall safety integrity of the system.

Having defined the safety criteria and the safety integrity level which the system should achieve, the next step is to select an appropriate development technique which can ensure that the safety criteria are met.

# 2.5 Selection of Development Techniques

The approach is to associate with each level of assessment a number of techniques which can be used in assessing a system, as shown in Table 2.4 [60]. The most rigorous assessment level, i.e. level 4, is associated with the use of formal mathematical methods. Level 1, however, is associated with the use of a review of the

| Level | Associated techniques                                          |

|-------|----------------------------------------------------------------|

| 0     | Design review                                                  |

| 1     | Checklists, Code walkthrough                                   |

| 2     | Fault tree analysis, Event tree analysis, Cause effect graphs  |

| 3     | State transition diagrams, Petri-Nets, Markov models           |

| 4     | Formal mathematical specification and anal-<br>ysis techniques |

Table 2.4: Assessment techniques

design and design procedures using checklists and a walkthrough and review of the development stages. The assessment of any system typically involves the use of techniques associated with more than one assessment level. For instance, design reviews are performed at all levels and formal hazard analysis is performed at all levels above level 2.

The concept of levels is important to the design and assessment of safetyrelated systems. Safety itself, and the factors which contribute to the level of integrity required and that achieved, are continuous quantities with no established metrics. The concept of levels allows some degree of measurement to be applied to these quantities and hence introduces a more concrete assessment of the system integrity.

Different techniques are associated with the different levels of assessment. These techniques model different aspects of the system. In addition to the independence of the personnel performing the assessment, diversity is therefore provided with respect to the viewpoint from which the system is assessed.

# 2.6 Validation and Verification

Depending on the level of assessment a variety of different verification techniques are applied, ranging from straight forward design review to formalised analyses of all or part of the system. Different levels of safety integrity and different types of application require that differing approaches, with increasing levels of formality, are employed in system development. The validation and verification process takes this into account so that in the process of reviewing a high integrity system more stringent criteria are applied than would be the case for a low integrity system.

However, it is possible to apply a low level of verification to a system which requires a high level of safety integrity. Since the purpose of the assessment is to ensure that the required level of safety integrity has been reached, this may be sufficient. A high level of assessment will, however, provide the necessarily greater degree of assurance that the required integrity level has been achieved.

#### 2.6.1 Informal techniques

Apart from dynamic execution testing, informal or manual methods have been the only methods available for carrying out validation and verification of the system when a fairly low level of safety integrity is required. Such informal methods include,

- walkthrough

- review

- audit/checklists

- code inspection.

As methods, however, they are by no means exhaustive, and although having the advantage of repeatibility they are not particularly effective in detecting errors introduced as a result of minor revisions. Nevertheless, such methods continue to be as cheap and effective as any in finding the majority of errors, especially when performed by experienced designers and therefore, they are most suitable for analysing systems when safety constraints are not critical.

#### 2.6.2 Semi-formal techniques

A number of semi-formal methods are used for those levels which have a high level of associated degree of risk. Typical techniques include fault tree analysis, Markov reliability model, Petri Nets and state transition diagrams.

Just as a rigorous and complete test case analysis is equivalent to formal verification, a rigorous treatment of these analysis is equivalent to formal verification. However, it should be emphasised that a standard analysis using the above techniques applied to system design, like the testing of the system, is informal and incomplete. For instance, fault tree analysis, as it is usually performed, is an effective technique for focusing attention on some significant aspects of the design but, without the rigour of formal verification, it cannot ensure that the required level of safety is achieved.

Therefore, for safety-related systems with a very high level of associated risk, a formal treatment is essential. Although the semi-formal analysis can make significant contributions to achieving safe systems, formal specifications and verification is the only method proposed to date that can achieve in principle, if not in practice, the level of safety required for safety-related applications. Of course, formal verification should be applied in conjunction with, rather than instead of, other techniques.

#### 2.6.3 Formal techniques

Formal verification is used to validate systems against a formal specification that defines what it is required to do. To achieve substantial improvements in system safety, techniques for validating formal specifications are important. The system verification requires that the detailed formal specifications, which is required for system verification, should themselves be verified against a simpler more abstract specification. Of course, the simpler more abstract specification may still be subject to error and must be verified against yet another simpler and still abstract specification, a process that eventually leads to a top-level specification. In the context of safety-related computing, this top-level specification should express the safety requirements of the system.

However, there is no simple systematic method for checking that a top-level specification correctly states the required safety properties of the system, since safety properties, which are included in the specification, are also specified by the user. Therefore, the specification expresses the real safety requirements of the application and must, in the end, be determined by human inspection and his/her understanding. In principle, it is the safety-related properties defined in the top-level specifications that are assured by the verification.

There are a number of tools available to assist with the formal verification of hardware and software systems. Some formal methods have, in fact, evolved from the semantic-analysis tools that were built to manipulate specifications and programs. Tools and their associated specification languages that handle subsets of first-order logic include the Boyer-Moore Theorem Prover (and the Gypsy specification language)[42], LOTOS (and the language CSP) [114], and m-EVES (with language m-Verdi) [34]. Finally, tools that handle subsets of higher order logic include HOL [49], LCF [43], and OBJ [41]. The relative advantages and drawbacks of these formal methods and languages will be discuss further in the following chapter.

# 2.7 Discussion

Designing for safety, particularly for computer-based systems, is an obvious goal, but up to now little guidance existed on how to achieve it. The IEC Working Group 9/10 has recently produced guidelines on design for system safety [63] and the work in this chapter are most closely related to the philosophy on which those guidelines are based and the principles underlying them. In fact, this proposed standard addresses the full lifecycle of the system development. There are two significant points to the standard from IEC WG9/10. Firstly, the standard advances a five-point scale for the levels of safety integrity so as to introduce the concept of degree of risk. Secondly, the standard does not place single emphasis on the use of formal methods for developing and assessing systems unlike the interim Def Stan 00-55 [66]. Rather it proposes the use of a package of techniques chosen from a set of such techniques such that they reflect the system integrity, the application and the industry.

However, the main difference between our approach and that proposed by the IEC standard is that in the Standard the required integrity level is selected on the basis of the level of risk associated with the system, whilst in this approach we also consider the benefits which the system contributes. Furthermore, the level of risk associated in a system as a whole is not directly related to the level of risk associated with software and other components. In fact, the overall level of safety integrity is always higher than its constituent parts.

Finally, the work presented in this chapter outlines a general framework for the development of systems based on the current state of the art. The main emphasis in this thesis as a whole is on the use of formal methods to verify the correctness, and ensure that the required level of safety integrity is indeed achieved. This chapter has laid down a methodological approach based on which formal methods are consistently introduced into, and incorporated with, the system design. The following chapter discusses the concepts of safety and risk from a mathematical point of view and illustrates how such safety objectives can be achieved in a formal development framework.

# Chapter 3

# Formal Specifications in Engineering

# 3.1 Introduction

Formal specification and verification can be used to validate systems against system requirements where the required level of safety integrity is very high, as was discussed in the previous chapter. During the verification of a system, a large number of theorems must be proved. Although these proofs are not mathematically profound, keeping track of the details of the proofs and the interrelationships among the various theorems can be overwhelming. Furthermore, the proofs must be carried out with a very high degree of rigour to ensure the high level of safety required. The generation of a formal specification and its verification is usually carried out in a deductive system, part of which can be automated by employing a mechanical proof checker, also called an automated theorem prover. However, such a proof checker is usually far from automatic. The user must supply many trivial details of the proof, usually in a manner that must accommodate the internal working of the prover. In effect, the user must create the proof, while the verification systems is responsible for the soundness and completeness of the proof. Fortunately, experience has shown that, although mechanical theorem verifiers frequently fail to find proofs that they might be expected to find, they seldom find proofs that are invalid. The construction of

proofs is not inherently difficult, but it is very time consuming.

To satisfy the mechanical theorem prover and to achieve the required level of safety, the specifications must be formal. Informal specifications in plain English may be useful in understanding the system and its documentation, but they cannot serve as a basis for verification. Even carefully written formal specifications are prone to error, and experience has shown that unverified specifications are comparable in reliability to untested programs. Indeed, the process of verification involves, in part, the correction of the formal specification.

In an attempt to obviate the inherent difficulties associated with the development of formal specification, and formal techniques in general, this chapter presents some heuristic approaches to the generation and validation of formal specifications for engineering problems. Our approach is to classify practical systems into categories and then present a formal treatment which is appropriate to each class of system.

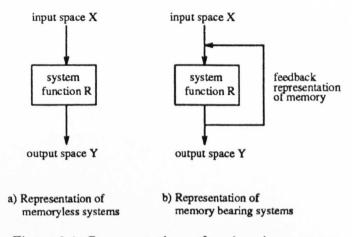

#### 3.1.1 System Classification

From the viewpoint of specifications, practical systems differ not only in terms of their functional properties, but also in terms of the interactions between their inputs and their outputs. We have identified, from an engineering viewpoint, two major classes of systems:

- Memoryless systems: whose every output is a function of the current input alone; such systems have no memory of their past inputs.

- Memory bearing systems: whose current output depends not only on their current input, but also on their past inputs; such systems must constantly memorise, if not an infinite history of their past inputs, at least a summary of it.

Within memory bearing systems, we have identified an important class of systems which has important practical applications,

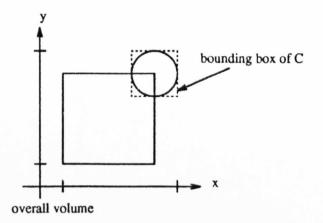

Figure 3.1: Representations of engineering systems

• Continuous processes, whose function is to compute responses to a stream of inputs. In such systems, real-time aspects have to be identified.

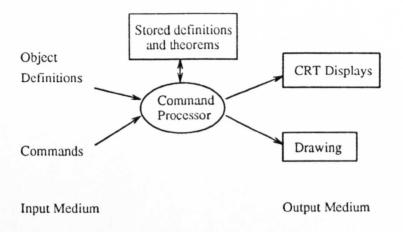

Hence, from the viewpoint of specifications, we distinguished between three classes of systems, memoryless systems, and continuous processes. Typical examples of the first class include a CAD package, or a theorem prover. Examples of the second class include a database management system. Examples of the third class include an operating system, a process control and monitoring system, and a database management system. However, due to the looseness of the classification criteria, a system can be classified into more than one class, as in the case of a database management system. Detailed specification examples of these types of systems are discussed later in Chapter 6 and Chapter 7. In Chapter 6, we will present a case study of a memory bearing device called Drive-by-Wire, and in Chapter 7, a detailed discussion of the specification of a CAD system is presented.

A traditional view of these types of systems is illustrated in Fig.3.1, in which the underlying principle of system modelling is based on a state machine description with or without a feedback loop. With this model in mind, in the following section, we can formally state the safety conditions and the assessment criteria to which the intended systems have to comply.

# 3.2 Formal Model of Safety

In state machine descriptions, a system is modelled as a single, compound function which generates a new state from an input state as shown in Fig.3.1. A formal treatment of safety is only concerned with the current behaviour of the system and therefore, it can be equally applied to machines which may or may not have memory.

Let us suppose now that the operating domain of the system under consideration can be divided into two subsets, S and U which represent the set of safe and unsafe states respectively. Using predicate calculus it is possible to formally state the definition of system safety such that there are three conditions to be satisfied,

When the current state, s<sub>i</sub>, is contained in a set of safe states S, there is a function F that will transform the current state into the next state, s<sub>j</sub>, which is also contained in the set of safe states S.

$$\forall s_i \in S. \ F(s_i) = s_j \supset s_j \in S$$

2. When the current state is contained in a set of unsafe states U, there is a function F that will transform the current state to the next state, which is contained in the set of safe states S.

$$\forall s_i \in U. \ F(s_i) = s_j \supset s_j \in S$$

3. When the current state is contained in a set of unsafe states U, and there does not exist a set of safe states for the current state to be transformed to, then there is a function F that will transform the current state to the next state with the lowest risk.

$$\forall s_i \in U. \ \neg(\exists \ s_j \in S. \ F(s_i) = s_j \ \land \ \mathsf{Risk}_{(s_k)} < \mathsf{Risk}_{(s_j)}) \ \Rightarrow \ F(s_i) = s_k$$

where S is a set of states judged to be safe and, U is a set of states judged to be unsafe, and  $Risk_{s_i}$  is the risk level associated with state  $s_i$ .

In asserting that  $\operatorname{Risk}_{(s_k)} < \operatorname{Risk}_{(s_j)}$  consideration needs to be given to the time taken for the system to achieve state  $s_k$ , and consequently this affects the assessment of the acceptable level of risk in the design. The risk assessment is formally based on a comparison of the cumulative effects of hazards over a finite duration of time. Strategies for defining risk levels are discussed further in the following section.

#### 3.2.1 Risk assessment

There are at least two strategies that can be adopted when considering the consequences of time in assessing a risk level. If  $Risk_{(s_k)}$  is considered to be lower than  $Risk_{(s_l)}$ , however more time is required for the system to achieve state  $s_k$ than state  $s_l$ , a judgement can be made whether safety is best served by achieving state  $s_k$  with a low risk in a longer time than state  $s_l$ . Suppose now that state  $s_l$ has a higher risk than state  $s_k$  but a lower risk than state  $s_j$  and can be achieved in a short time, then the last safety condition, described above, can be qualified as follows,

$$\forall s_i \in U. \ \neg(\exists \ s_j \in \ S. \ F(s_i) = s_j \land$$

$$\operatorname{Risk}_{(s_k)} < \operatorname{Risk}_{(s_i)} < \operatorname{Risk}_{(s_j)} \land \ T_{(s_k)} < T_{(s_i)} ) \Rightarrow \ F(s_i) = s_k$$

where  $T_{s_j}$  is the time required to achieve a particular state  $s_j$  from the current state  $s_i$ . This strategy is appropriate for those instances when it is only possible to predict one state ahead.

However, if it is possible to look ahead more than one state, an alternative strategy might be to achieve a state with a higher risk for a short time in the knowledge that a state with a lower risk will be achieved ultimately. So for this strategy, safety could be expressed as the integral of the level of danger against time,

safety =

$$\int P_{s_i} \cdot \operatorname{Risk}_{s_i} dt$$

where  $P_{s_i}$  is the probability of occurrence and  $\text{Risk}_{s_i}$  represents the level of risk associated with the state  $s_i$ . The value of  $\text{Risk}_{s_i}$  is subjectively judged and could influence the choice of strategy adopted due to the level of confidence in the judgement.