# **Original citation:**

Li, Fan, Sharma, Yogesh K., Walker, David, Hindmarsh, Steven, Jennings, Michael, Martin, David, Fisher, Craig A., Gammon, P. M., Pérez-Tomás, Amador and Mawby, P. A.. (2016) 3C-SiC transistor with Ohmic contacts defined at room temperature. IEEE Electron Device Letters . 10.1109/LED.2016.2593771

## **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/81172

# **Copyright and reuse:**

The Warwick Research Archive Portal (WRAP) makes this work by researchers of the University of Warwick available open access under the following conditions. Copyright © and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners. To the extent reasonable and practicable the material made available in WRAP has been checked for eligibility before being made available.

Copies of full items can be used for personal research or study, educational, or not-for profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

## Publisher's statement:

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting /republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

### A note on versions:

The version presented here may differ from the published version or, version of record, if you wish to cite this item you are advised to consult the publisher's version. Please see the 'permanent WRAP url' above for details on accessing the published version and note that access may require a subscription.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# 3C-SiC Transistor with Ohmic Contacts Defined at Room Temperature

Fan Li, Yogesh Sharma, David Walker, Steven Hindmarsh, Mike Jennings, David Martin, Craig Fisher, Peter Gammon, Amador Pérez-Tomás and Phil Mawby

Abstract— Among all SiC polytypes, only 3C-SiC has a cubic structure and can be hetero-epitaxial grown on large area Si substrate, thus providing an alternative choice for fabricating cheap wide bandgap power devices. Here we present a low resistivity ( $\sim 3 \times 10^{-5}~\Omega.\text{cm}^2$ ) Ohmic contact formed by directly depositing a Ti/Ni metal stack on n-type 3C-SiC without any extra annealing. For the first time, 3C-SiC lateral MOSFETs with as-deposited Ohmic contacts were fabricated, and it turned out not only the Ohmic contact is free from any interface voids, but also a higher field-effect mobility value ( $\sim 80~\text{cm}^2/\text{V.s.}$ ) was achieved compared with the annealed devices.

Index Terms—3C-SiC, channel mobility, MOSFET, Ohmic contact, reliability

#### I. INTRODUCTION

WIDE band gap (WBG) semiconductors are considered as the materials for next generation electronics, particularly in the harsh environment and power electronics area. It is generally known that forming Ohmic contact to WBG semiconductors require not only a highly doped surface region, but also a relative high temperature (around 1000 °C) post-metallisation annealing (PMA) step. The PMA step generates an intermediate semiconductor layer (silicide or carbide) with narrower bandgap to reduce the Schottky barrier height (SBH) as well as creating more free carriers at the contact interface [1]. This additional step increases the fabrication thermal budget and complicates the WBG semiconductor applications in technologies which are sensitive to heat treatments, such as high-k, organic semiconductors, semiconductor heterojunctions etc. In this letter, we demonstrate how 3C-SiC MOSFETs fabrication can benefit from the as-deposited Ohmic contacts, with reliability and electrical performance both improved compared with a conventional PMA process.

The most studied metals for n-type 3C-SiC Ohmic contacts are Al [2-4], Ti [3-5] and Ni [2, 4, 6, 7], and the resultant  $\rho_c$

Manuscript submitted July 20, 2016. This work is supported by Engineering and Physical Sciences Research Council (EPSRC) under Grant EP/I038543/1.

The corresponding author Fan Li and others are with the Faculty of Science, University of Warwick, Coventry, CV4 7AL United Kingdom (e-mail: f.li.1@warwick.ac.uk)

Dr. A. P. Thomas Author is with Catalan Institute of Nanoscience and Nanotechnology (ICN2), CSIC and The Barcelona Institute of Science and Technology, Campus UAB, Bellaterra, 08193 Barcelona, Spain

values covered a huge range from  $10^{-7}$  to  $10^{-1}~\Omega.cm^2$ . Room temperature Ti and Al contacts were reported on highly doped  $(3x10^{20}~cm^{-3})$  n-type 3C-SiC back in 1995 [3], although with a considerable resistivity spread of over  $6x10^{-5}~\Omega.cm^{-2}$ . The literature shows that Al contacts generally have the lowest  $\rho_c$  value, which can be explained by the negligible SBH between Al and 3C-SiC (~0 eV) compared with Ti (0.4 eV) and Ni (0.55 eV) [4]. However, both Al and Ti easily get oxidised in air and Al has a melting point below 600 °C. On the other hand, Ni has a slow oxidation rate at room temperature and very high melting point. Although reacting with SiC above 500 °C, the silicide products help to reduce the interface SBH, leading to a lower  $\rho_c$  value. As a result, Ni has been the mostly used contact metal for n-type SiC and is applied for the study here.

#### II. DEVICE FABRICATION

The material used in this work was a 10 µm thick unintentionally doped (<1x10<sup>16</sup> cm<sup>-3</sup>) 3C-SiC film epitaxial grown on a 4-inch Si(100) substrate by NOVASiC. Nitrogen was implanted for creating high impurity concentration regions. A post-implantation annealing (PIA) at 1375 °C (Si melting point 1412 °C [8]) for 1 hour was carried out to activate the dopants, no surface capping layer was used. The samples were then all solvent cleaned, followed by a standard RCA cleaning procedure. Conventional transmission line method (TLM) structures with 1 µm mesa were patterned using photolithography and ICP etcher. 100 nm Ni was deposited as the contact metal in an e-beam evaporator at a low pressure of 2x10<sup>-7</sup> Torr with a thin Ti interlayer (20 nm) to improve the contact adhesion. Lateral n-channel MOSFETs were fabricated using a double implantation scheme, P base (~1x10<sup>18</sup> cm<sup>-3</sup>, Al) for channel and N+ (~5x10<sup>20</sup> cm<sup>-3</sup>, N) for source/drain. The same PIA process used before was applied to activate both dopants. Prior to gate oxidation, the MOSFET samples went through an extra piranha clean (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>=3:1). The gate oxide was thermally grown at 1300 °C (O<sub>2</sub> 1 L/min), after that source/drain contacts were fabricated with as-deposited Ti/Ni contacts. For comparison purposes, devices with a PMA step (1 min at 1000 °C) were also fabricated. 500 nm Al was deposited on the channel region to form the gate contact. The final MOSFET has a channel length of 150 μm and width of 290 μm.

#### III. RESULTS AND DISCUSSIONS

## A. Non-annealed Ohmic contacts to 3C-SiC

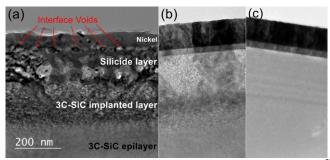

Fig. 1. TEM cross section views of the fabricated contact interfaces, (a)  $5 \times 10^{20}$  cm<sup>-3</sup> after 1 min 1000 °C PMA, (b)  $5 \times 10^{20}$  cm<sup>-3</sup> as-deposited, and (c)  $5 \times 10^{19}$  cm<sup>-3</sup> as-deposited

Ohmic behaviour was obtained for the as-deposited Ti/Ni contacts on the 5x10<sup>20</sup> cm<sup>-3</sup> implanted 3C-SiC films. The room temperature average  $\rho_c$  of  $\sim 3x10^{-5}$   $\Omega.cm^2$  is higher than the annealed one ( $\sim 9 \times 10^{-6} \ \Omega.\text{cm}^2$ ), but still low enough for power device fabrications. Here the average is taken from 4 TLM structures fabricated on each sample with little spread (as shown later in Fig. 2b) and performed using standard cleanroom deposition technology, which is an improvement from [3]. The voids (labelled in Fig.1a) are silicon vacancies formed by severe silicon diffusion into nickel, known as Kirkendall effect [9]. Whereas they do not affect much the contact electrical performance [10], they were known to degrade the contact reliability [11]. From Fig. 1b and 1c, it can be seen that without the SiC-Ni reaction, the contact interface is much more abrupt and the interface voids are not present. Fig. 1b shows that the 5x10<sup>20</sup> cm<sup>-3</sup> implantation significantly damaged the 3C-SiC top layer. This would only occur in the Ohmic contact region and should not be a concern for most device fabrications, yet it is worth trying lowering the implantation dose and see if the Ohmic behaviour can be preserved. The same fabrication procedure (without PMA) was carried out on a 5x10<sup>19</sup> cm<sup>-3</sup> implanted sample, and again Ohmic behaviour was obtained, whereas  $\rho_c$  now increased to  $\sim 7 \times 10^{-4} \Omega \cdot \text{cm}^2$ . Further reducing the implantation level to ~1x10<sup>19</sup> cm<sup>-3</sup> led to a rectifying contact, which became Ohmic after the PMA.

Metallic contacts were known to be formed when metal was deposited onto a semiconductor surface with high density dislocations, which can then shunt the space-charge layer and make field emission the dominant mechanism [12, 13] regardless of the semiconductor doping levels. Considering the 3C-SiC layer used in this study was grown on Si thus contains a large amount of defects, they may have helped towards a lower contact resistance. However, the 'metal shunts' requires the dissolution and recrystallization of semiconductor in metal, namely additional heat treatment [14]. We believe the as-deposited Ohmic contacts were obtained more likely by the formation of an impurity band caused by the excessive doping. In our previous study [15], the activation energy E<sub>a</sub> of nitrogen for 1x10<sup>19</sup> cm<sup>-3</sup> implanted sample is approaching zero (15

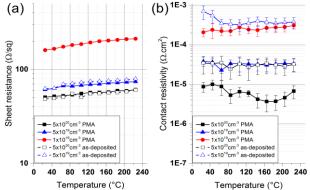

meV). It is reasonable to assume that  $E_a$  becomes zero for  $5x10^{19}~\text{cm}^{-3}$  and  $5x10^{20}~\text{cm}^{-3}$  samples and they behave as degenerated semiconductors [16]. The increasing sheet resistance with temperature in Fig. 2a also favours this idea.

Fig. 2. Temperature dependence of (a) sheet resitance and (b) contact resistivity extracted from the TLMs

All the Ohmic contacts show very low temperature dependence from 25 °C up to 225 °C as shown in Fig. 2b. As-deposited contacts on the 5x10<sup>20</sup> cm<sup>-3</sup> and 5x10<sup>19</sup> cm<sup>-3</sup> implanted samples readily behave as temperature independent, which means the PMA (similarly "metal shunts") did not play a big role in this. Also, the 1x10<sup>19</sup> cm<sup>-3</sup> doped sample has as-deposited rectifying behaviour, therefore not degenerated by the implantation process, whereas after PMA the  $\rho_c$  is also thermally stable, namely ruling out the degeneracy being the main cause. With the 3C-SiC electron effective mass of conductivity 0.32m<sub>0</sub> [17], dielectric constant 9.72 [18] known, the characteristic energy  $E_{00}/kT$  for the non-degenerated  $1x10^{19}$ cm<sup>-3</sup> doped 3C-SiC/metal interface is calculated [19] to be  $\approx$ 1.3, which means the contact interface should be dominated by thermionic-field emission, and the  $\rho_c$  value should decrease considerably with increasing temperature. This is, however, conflicting with the Fig. 2b curves, which, if anything, appear more field-emission dominated. It was recently reported [20] that the metal/semiconductor interface band bending can be caused by dopant-induced dipole field between the interface and the dopant site. We then believe the thermal stable  $\rho_c$  is due to the Schottky barrier elimination caused by the interface band bending.

#### B. 3C-SiC MOSFETs without Ohmic contact annealing

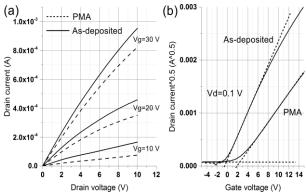

Apart from the improved contact interface which will lead to higher reliability, as-deposited Ohmic contacts may also benefit device fabrications where annealing can degrade other key features such as MOS and Schottky contacts [3]. To confirm this, lateral MOSFETs were fabricated as described in section II. All devices have typical forward features with well observed gate effects shown in Fig. 3a. Device without a PMA step clearly demonstrates higher forward current under all gate biases. Since the annealed contacts have lower resistance, the resultant higher total on-resistance of PMA processed devices must come from the channel.

Fig. 3. (a) Forward conducting curves and (b) transfer curves  $(I_{ds}^{-0.5} \, vs \, V_{gs})$  for as-deposited and PMA processed MOSFET devices

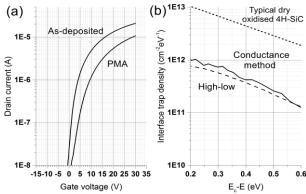

The device transfer curve  $(I_{ds}^{0.5} \text{ versus } V_g)$  is shown in Fig. 3b and the leakage current observed in device off state (Vg<-2 V) should be caused by the stacking faults, which were identified as the main origin of leakage currents in 3C-SiC devices and can be greatly reduced by latest advanced growth techniques [21, 22]. The threshold voltages V<sub>th</sub> extracted from Fig. 3b are ~-0.5V and ~2.5V for as-deposited and PMA processed devices, respectively. The commonly observed [21, 23, 24] negative V<sub>th</sub> of 3C-SiC MOS devices can be explained by the carbon-cluster interface traps model [25], which describes that due to the smaller band gap, only donor-like interface states (carbon clusters/dangling bonds) are present at the 3C-SiC/SiO<sub>2</sub> interface. Consequently, as-grown dry oxidized 3C-SiC MOS interface is positively charged and demonstrates a negative V<sub>th</sub> [26], which can be shifted to positive if wet gate oxidation/post-oxidation annealing is applied [27] since wet oxidation is known to induce negative charges near the SiC/SiO<sub>2</sub> interface [28, 29]. Accordingly, the positive V<sub>th</sub> shift of the PMA processed device observed in Fig. 3b should be caused by an additional build-up of negative charges at/near the MOS interface rather than a reduction of the donor-like interface states, since otherwise it would have improved the device conduction performance. These facts agree well with the devices subthreshold features shown in Fig. 4a. The subthreshold swing S estimated from drain current of  $10^{-8}$  to  $10^{-7}$  A are  $\sim 1.7$  V/dec and  $\sim 3.3$  V/dec for as-deposited and PMA processed devices, respectively. This is much higher than the ideal value (~0.06 V/dec for a MOSFET) and is caused by the unoptimised device parameters (i.e. oxide thickness ~92 nm and channel doping ~1x10<sup>18</sup> cm<sup>-3</sup>), yet a comparison shows that an, almost 50% reduction of the subthreshold swing can be achieved by using as-deposited Ohmic contacts. The interface trap densities Dit can be estimated from S [30] with the oxide thickness 92 nm known. For the weak inversion region, C<sub>b</sub> was assumed to be zero, which caused the overestimation of Dit, and the values are determined as  $\sim 6.6 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> for as-deposited devices and  $\sim 1.3 \times 10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> for PMA devices. The 10<sup>13</sup> order D<sub>it</sub> values were previously reported for dry oxidised 3C-SiC MOS capacitors [26, 31]. Here lateral MOS capacitors were also fabricated following the same gate oxidation process as MOSFETs and Dit is found to be below 1x10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> close to the conduction band as seen in Fig. 4b, determined by both high-low and conductance methods. This is

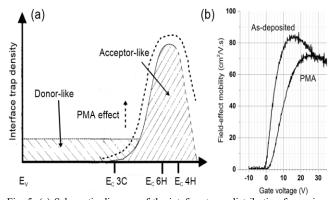

one magnitude lower than the values [32, 33] for 4H-SiC without further post oxidation annealing. The lower  $D_{it}$  value for devices with as-deposited Ohmic contacts confirms the PMA step leads to additional interface traps (schematic diagram shown in Fig. 5a) as previously reported for Si MOS devices, which was mostly explained by the mechanical stress induced at the MOS interface by the rapid temperature change and thermal expansion coefficients difference [34-36]. The channel field-effect mobility are calculated from the MOSFET trans-conductance and shown in Fig. 5b. Clearly the extra PMA step results in a lower peak channel mobility value ( $\sim$ 70 cm<sup>2</sup>/V.s) than the as-deposited case ( $\sim$ 80 cm<sup>2</sup>/V.s).

Fig. 4. (a) Subthreshould characteristics ( $V_d$ =0.1 V) of MOSFETs fabricated with as-deposited and PMA ohmic contacts and (b)  $D_{it}$  of capacitors fabricated on n-type 3C-SiC epilayer with same gate oxidaiotn as MOSFET.

Fig. 5. (a) Schematic diagram of the inteface traps distribution for various SiC polytypes and (b) field-effect mobility of farbricated MOSFETs.

In power MOSFET designs, p-body and source are shorted by sharing the contact. Alloyed Ni is commonly used for both in 4H-SiC power devices [37, 38], similarity we believe the as-deposited Ti/Ni bilayer proposed here can also be integrated. The low thermal budget of the process demonstrated in this work opens new doors to the application of SiC transistors with other low temperature technologies, including high k dielectrics atomic layer deposited (e.g.  $Al_2O_3$  or  $HfO_2$ ) with relative low temperature of growth, ferroelectric polymers a classical example being polyvinylidene fluoride, organic semiconductors such as polythiophenes that can become conducting owing to their conjugated  $\pi$ -orbitals, fullerenes or carbon nanotubes, organic trihalide perovskites, and classic heterojunction or wafer bonded devices.

#### REFERENCES

- [1] Z. Wang, S. Tsukimoto, M. Saito, and Y. Ikuhara, "Introducing Ohmic Contacts into Silicon Carbide Technology," in Silicon Carbide -Materials, Processing and Applications in Electronic Devices, M. Mukherjee, Ed., InTech, pp. 283-308, 2011. DOI: 10.5772/20481

- [2] C. Jacob, P. Pirouz, H. I. Kuo, and M. Mehregany, "High Temperature Ohmic Contacts to 3C–Silicon Carbide Films," Solid-State Electronics, vol. 42, pp. 2329-2334, 1998. DOI: <u>10.1016/S0038-1101(98)00234-2</u>

- [3] A. Moki, P. Shenoy, D. Alok, B. J. Baliga, K. Wongchotigul, and M. G. Spencer, "Low Resistivity As-deposited Ohmic Contacts to 3C-SiC," Journal of Electronic Materials, vol. 24, pp. 315-318, 1995. DOI: 10.1007/BF02659693

- [4] M. Satoh, E. Taguchi, Y. Suzuki, and S. Nagata, "Evaluation of Specific Contact Resistance of Al, Ti, and Ni Contacts to N Ion Implanted 3C-SiC (100)," Materials Science Forum, vol. 556-557, pp. 705-708, 2007. DOI: 10.4028/www.scientific.net/MSF.556-557.705

- [5] J. S. Shor, R. A. Weber, L. Provost, D. Goldstein, and A. D. Kurtz, "High Temperature Ohmic Contact Metallizations for N-Type 3C-SiC," Journal of the Electrochemical Society, vol. 141, pp. 579-581, 1994. DOI: 10.1149/1.2054771

- [6] J. Wan, M. A. Capano, and M. R. Melloch, "Formation of Low Resistivity Ohmic Contacts to N-type 3C-SiC," Solid-State Electronics, vol. 46, pp. 1227-1230, 2002. DOI: 10.1016/S0038-1101(02)00013-8

- [7] A. E. Bazin, J. F. Michaud, C. Autret-Lambert, F. Cayrel, T. Chassagne, M. Portail, M. Zielinski, E. Collard, D. Alquier, "Ti–Ni Ohmic Contacts on 3C–SiC Doped by Nitrogen or Phosphorus Implantation," Materials Science and Engineering: B, vol. 171, pp. 120-126, 2010. DOI: 10.1016/j.mseb.2010.03.084

- [8] G. L. Pearson and R. G. Treuting, "Surface Melt Patterns on Silicon," Acta Crystallographica, vol. 11, pp. 397-399, 1958. DOI: 10.1107/S0365110X58001080

- [9] T. Kirkendall, L. Thomassen, and C. Upthegrove, "Rates of Diffusion of Copper and Zinc in Alpha Brass," AIME TRANS, vol. 133, pp. 186-203, 1939.

- [10] J. Biscarrat, X. Song, J. F. Michaud, F. Cayrel, M. Portail, M. Zielinski, T. Chassagne, E. Collard, D. Alquier, "Ti Thickness Influence for Ti/Ni Ohmic Contacts on N-type 3C-SiC," Materials Science Forum, vol. 711, pp. 179-183, 2012. DOI: 10.4028/www.scientific.net/MSF.711.179

- [11] T. Marinova, A. Kakanakova-Georgieva, V. Krastev, R. Kakanakov, M. Neshev, L. Kassamakova, O. Noblanc, C. Arnodo, S. Cassette, C. Brylinski, B. Pecz, G. Radnoczi, Gy. Vincze, "Nickel Based Ohmic Contacts on SiC," Materials Science and Engineering: B, vol. 46, pp. 223-226, 1997. DOI: 10.1016/S0921-5107(96)01981-2

- [12] T. V. Blank, Y. A. Goldberg, and E. A. Posse, "Flow of The Current Along Metallic Shunts in Ohmic Contacts to Wide-Gap III-V Semiconductors," Semiconductors, vol. 43, pp. 1164-1169, 2009. DOI: 10.1134/S1063782609090115

- [13] F. Iucolano, G. Greco, and F. Roccaforte, "Correlation between Microstructure and Temperature Dependent Electrical Behavior of Annealed Ti/Al/Ni/Au Ohmic Contacts to AlGaN/GaN heterostructures," Applied Physics Letters, vol. 103, p. 201604, 2013. DOI: 10.1063/1.4828839

- [14] T. V. Blank and Y. A. Gol'dberg, "Mechanisms of Current Flow in Metal-Semiconductor Ohmic Contacts," Semiconductors, vol. 41, pp. 1263-1292, 2007. DOI: <u>10.1134/S1063782607110012</u>

- [15] F. Li, Y. Sharma, V. Shah, M. Jennings, A. Pérez-Tomás, M. Myronov, C. Fisher, D. Leadley, P. Mawby, "Electrical Activation of Nitrogen Heavily Implanted 3C-SiC(100)," Applied Surface Science, vol. 353, pp. 958-963, 2015. DOI: 10.1016/j.apsusc.2015.06.169

- [16] M. Vivona, G. Greco, F. Giannazzo, R. Lo. Nigro, S. Rascunà, M. Saggio and F. Roccaforte, "Thermal Stability of The Current Transport Mechanisms in Ni-based Ohmic Contacts on N- and P-implanted 4H-SiC," Semiconductor Science and Technology, vol. 29, p. 075018, 2014. DOI: 10.1088/0268-1242/29/7/075018

- [17] Y. Goldberg, M. Levinshtein and S. Rumyantsev, "Silicon Carbide (SiC)" in Properties of Advanced Semiconductor Materials: GaN, AIN, InN, BN, SiC, SiGe. John Wiley & Sons, pp. 93-149, 2001.

- [18] L. Patrick and W. J. Choyke, "Static Dielectric Constant of SiC," Physical Review B, vol. 2, pp. 2255-2256, 1970. DOI: <u>10.1103/PhysRevB.2.2255</u>

- [19] A. Y. C. Yu, "Electron Tunnelling and Contact Resistance of Metal-Silicon Contact Barriers," Solid-State Electronics, vol. 13, pp. 239-247, 1970. DOI: 10.1016/0038-1101(70)90056-0

- [20] Y. Jiao, A. Hellman, Y. Fang, S. Gao, and M. Käll, "Schottky Barrier Formation and Band Bending Revealed by First Principles Calculations," Scientific Reports, vol. 5, p. 11374, 2015. DOI: <u>10.1038/srep11374</u>

- [21] H. Nagasawa, M. Abe, K. Yagi, T. Kawahara, and N. Hatta, "Fabrication of High Performance 3C-SiC Vertical MOSFETs by Reducing Planar Defects," Physica Status Solidi (b), vol. 245, pp. 1272-1280, 2008. SOI: 10.1002/pssb.200844053

- [22] H. Nagasawa, T. Kawahara, K. Yagi, and N. Hatta, "Propagation of Stacking Faults in 3C-SiC," Materials Science Forum, vol. 679-680, pp. 282-285, 2011. DOI: <u>10.4028/www.scientific.net/MSF.679-680.282</u>

- [23] L. K. Kiong, Y. Ishida, T. Ohshima, K. Kojima, Y. Tanaka, T. Takahashi, H. Okumura, K. Arai, and T. Kamiya, "N-channel MOSFETs Fabricated on Homoepitaxy-Grown 3C-SiC Films," IEEE Electron Device Letters, vol. 24, pp. 466-468, 2003. DOI: <u>10.1109/LED.2003.815006</u>

- [24] H. Uchida, A. Minami, T. Sakata, H. Nagasawa, and M. Kobayashi, "High Temperature Performance of 3C-SiC MOSFETs with High Channel Mobility," Materials Science Forum, vol. 717-720, pp. 1109-1112, 2012. DOI: 10.4028/www.scientific.net/MSF.717-720.1109

- [25] V. V. Afanas' ev, F. Ciobanu, S. Dimitrijev, G. Pensl, and A. Stesmans, "SiC/SiO2 interface states: properties and models," Materials Science Forum, vol. 483-485, pp. 563-568, 2005. DOI: 10.4028/www.scientific.net/MSF.483-485.563

- [26] R. Esteve, A. Schoner, S. A. Reshanov, C. M. Zetterling, and H. Nagasawa, "Comparative Study of Thermally Grown Oxides on N-type Free Standing 3C-SiC (001)," Journal of Applied Physics, vol. 106, pp. 044513, 2009. DOI: 10.1063/1.3204642

- [27] M. Kobayashi, H. Uchida, A. Minami, T. Sakata, R. Esteve, and A. Schöner, "3C-SiC MOSFET with High Channel Mobility and CVD Gate Oxide," Materials Science Forum, vol. 679-680, pp. 645-648, 2011. DOI: 10.4028/www.scientific.net/MSF.679-680.645

- [28] H. Yano, F. Katafuchi, T. Kimoto, and H. Matsunami, "Effects of Wet Oxidation/Anneal on Interface Properties of Thermally Oxidized SiO<sub>2</sub>/SiC MOS System and MOSFET's," IEEE Transactions on Electron Devices, vol. 46, pp. 504-510, 1999. DOI: <u>10.1109/16.748869</u>

- [29] Y. Ebihara, K. Chokawa, S. Kato, K. Kamiya, and K. Shiraishi, "Intrinsic Origin of Negative Fixed Charge in Wet Oxidation for Silicon Carbide," Applied Physics Letters, vol. 100, p. 212110, 2012. DOI: 10.1063/1.4722782

- [30] D. K. Schroder, "Oxide and Interface Trapped Charges, Oxide Thickness", in Semiconductor Material and Device Characterization, 3rd Edition, John Wiley & Sons, pp. 359-361, 2006. DOI: 10.1002/0471749095

- [31] M. Bakowski, A. Schöner, P. Ericsson, H. Strömberg, H. Nagasawa, and M. Abe, "Development of 3C-SiC MOSFETs," Journal of Telecommunication and Information Technology, vol. 2, pp. 49-56, 2007. DOI: bwmetal.element.baztech-article-BAT8-0008-0010

- [32] G. Y. Chung, J. R. Williams, C. C. Tin, K. McDonald, D. Farmer, R. K. Chanana, S.T. Pantelides, O.W. Holland, L.C. Feldman, "Interface State Density and Channel Mobility for 4H-SiC MOSFETs with Nitrogen Passivation," Applied Surface Science, vol. 184, pp. 399-403, 2001. DOI: 10.1016/S0169-4332(01)00684-5

- [33] P. Zhao, Rusli, Y. Liu, C. C. Tin, W. G. Zhu, and J. Ahn, "Investigation of 4H-SiC MOS Capacitors Annealed in Diluted N<sub>2</sub>O at Different Temperatures," Microelectronic Engineering, vol. 83, pp. 61-64, 2006. DOI: 10.1016/j.mee.2005.10.026

- [34] M. H. Jung, K. S. Kim, and W. J. Cho, "Characterization of the Back Interface in Strained-Silicon-on-Insulator Channel and Enhancement of Electrical Properties by Heat Treatment," IEEE Electron Device Letters, vol. 29, pp. 1356-1359, 2008. DOI: <u>10.1109/LED.2008.2006412</u>

- [35] D. C. Murray, J. C. Carter, A. G. R. Evans and J. L. Altrip, "The Inferior Quality of RTA MOSFET Interfaces," Journal of Physics: Condensed Matter, vol. 1, pp. SB219-220, 1989. DOI: <u>10.1088/0953-8984/1/SB/050</u>

- [36] W. Cho and S. Lee, "Gate Depletion in WSi<sub>x</sub> /Polysilicon Gate Stack and Effects of Phosphorus Ion Implantation," Japanese Journal of Applied Physics, vol. 42, p. 2615, 2003. DOI: <u>10.1143/JJAP.42.2615</u>

- [37] R. Huang, Y. Tao, S. Bai, G, Chen, L. Wang, A. Liu, N. Wei, Y. Li and Z. Zhao, "Design and Fabrication of a 3.3 kV 4H-SiC MOSFET," Journal of Semiconductors, vol. 36, p. 094002, 2015. DOI: <u>10.1088/1674-4926</u>

- [38] C. F. Huang, C. L. Kan, T. L. Wu, M. C. Lee, Y. Z. Liu, K. Y. Lee, F. Zhao, "3510V 390mΩ.cm² 4H-SiC Lateral JFET on a Semi-Insulating Substrate," IEEE Electron Device Letters, vol. 30, pp. 957-959, 2009. DOI: 10.1109/LED.2009.2027722