#### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/90139

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Reliability Assessment and Modelling of Power Electronic Devices for Automotive Application and Design

By Roozbeh Bonyadi

Dissertation Submitted for the Degree of  $Doctor\ of\ Philosophy$

School of Engineering

September 2016

## Content

| List  | of Figu | res . |                                      | iv   |

|-------|---------|-------|--------------------------------------|------|

| List  | of Tabl | es    |                                      | xiii |

| Decla | ration  |       |                                      | xiv  |

| Ackn  | owledg  | geme  | ent                                  | xvi  |

| Publi | cation  | List  | t                                    | xvii |

| Abstr | act     |       |                                      | xix  |

| List  | of Abbr | evia  | ations                               | xx   |

| 1     | Intro   | oduc  | tion                                 | 1    |

|       | 1.1     | Int   | troduction to the EV Power Converter | 4    |

|       | 1.2     | Po    | wer Devices for EV Drivetrains       | 6    |

|       | 1.3     | Ra    | tionale for Current Work             | 7    |

|       | 1.4     | Co    | ontribution to Knowledge             | 10   |

|       | 1.5     | Ov    | verview of Dissertation              | 12   |

| 2     | Intro   | oduc  | etion to Electrical Drive System     | 18   |

|       | 2.1     | Ov    | verview                              | 18   |

|       | 2.2     | Ele   | ectric Powertrain                    | 19   |

|       | 2.5     | 2.1   | eMachines                            | 20   |

|       | 2.5     | 2.2   | EV Battery                           | 20   |

|       | 2.5     | 2.3   | Power Inverter                       | 21   |

|       | 2.2     | 2.4   | Power Devices                        | 23   |

|       | 2.3     | Po    | wer Device Modelling                 | 36   |

|       | 2.4     | Re    | liability of Power Inverters         | 39   |

|       | 2.4     | 4.1   | Electro-Thermal Reliability          | 40   |

|       | 2.4     | 4.2   | Thermo-Mechanical Reliability        | 41   |

| 3     | Intro   | oduc  | etion to Modelling                   | 50   |

|       | 3.1     | Co    | mpact Device Models                  | 50   |

|       | 3.2     | Se    | miconductor Physics                  | 50   |

|       | 3.3     | Po    | wer Electronic Devices               | 51   |

|       | 3.5     | 3.1   | P-N Junction                         | 51   |

|       | 9 9     | 2.0   | DiM Diodo                            | EE   |

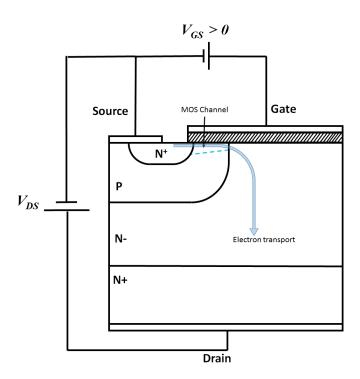

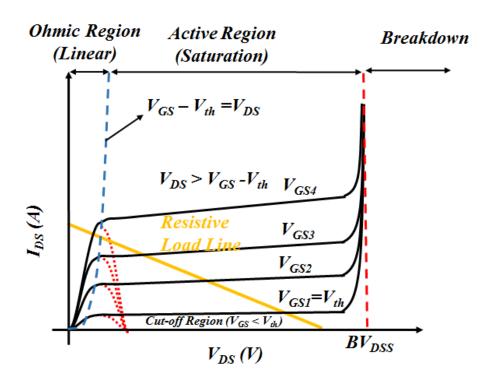

|   | 3.3   | 3.3   | MOSFET                                                      | 74  |

|---|-------|-------|-------------------------------------------------------------|-----|

|   | 3.3   | 3.4   | IGBT                                                        | 85  |

| 4 | Bipol | lar L | atch-up in Power MOSFETs                                    | 96  |

|   | 4.1   | Inti  | roduction                                                   | 97  |

|   | 4.2   | Bod   | ly Diode Model Validation                                   | 101 |

|   | 4.3   | ВЈТ   | Γ Electro-Thermal Model                                     | 113 |

|   | 4.3   | 3.1   | Drain-to-Body Capacitance Displacement Current              | 115 |

|   | 4.3   | 3.2   | BJT Latch-up Mechanism                                      | 118 |

|   | 4.3   | 3.3   | BJT Ebers-Moll Model                                        | 121 |

|   | 4.3   | 3.4   | Electro-Thermal Model Positive Feedback Loop                | 122 |

|   | 4.4   | Res   | ults and Discussion                                         | 130 |

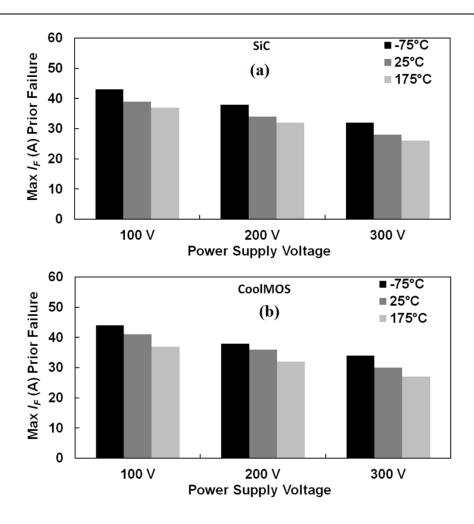

|   | 4.4   | ł.1   | SiC and CoolMOS Latch-up Waveforms                          | 130 |

|   | 4.4   | 1.2   | Latch-up Temperature and Voltage Dependency                 | 132 |

|   | 4.4   | 1.3   | BJT Latch-up Dynamics                                       | 133 |

|   | 4.5   | Con   | nclusions                                                   | 143 |

| 5 | Paras | sitic | Induced Gate Switching in Power Devices                     | 145 |

|   | 5.1   | Par   | asitic Gate Turn-On                                         | 147 |

|   | 5.2   | Par   | asitic Gate Turn-On Model Development and Experimental Setu | 150 |

|   | 5.2   | 2.1   | Results and Discussion                                      | 153 |

|   | 5.3   | Par   | asitic Gate Turn-Off                                        | 176 |

|   | 5.3   | 3.1   | Reverse Recovery Induced Parasitic Gate Turn-Off            | 178 |

|   | 5.3   | 3.2   | Experimental Results and Discussions                        | 185 |

|   | 5.3   | 3.3   | Modelling Parasitic Gate Turn-off                           | 194 |

|   | 5.4   | Con   | nclusions                                                   | 196 |

| 6 | Curre | ent S | Sharing of Parallel IGBTs                                   | 199 |

|   | 6.1   | Inti  | roduction                                                   | 199 |

|   | 6.2   | Exp   | perimental Setup                                            | 209 |

|   | 6.3   | Res   | ults and Discussion                                         | 210 |

|   | 6.4   | Con   | nclusions                                                   | 216 |

| 7 | Desig | gn ar | nd Fabrication of an Automotive Power Inverter              | 218 |

|   | 7.1   | Inti  | roduction                                                   | 218 |

|   | 7 2   | Pac   | kaging Process                                              | 221 |

|     | 7.3     | Packaging SiC MOSFET                             | 234 |

|-----|---------|--------------------------------------------------|-----|

|     | 7.4     | Packaging a Power Inverter                       | 242 |

|     | 7.5     | Prototyping a Double Side Cooling Power Inverter | 253 |

| 8   | Conc    | clusion and Suggestions for Future Work          | 265 |

|     | 8.1     | Conclusions                                      | 265 |

|     | 8.2     | Suggestions for Further Work                     | 271 |

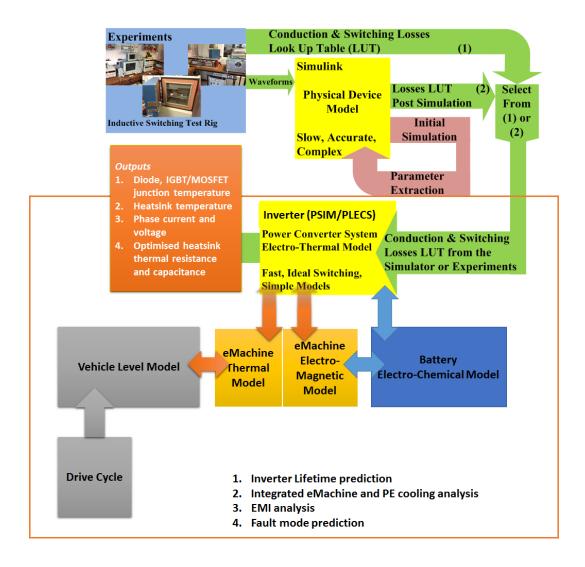

|     | 8.2     | 2.1 Electro-Thermal Modelling of Inverter        | 271 |

|     | 8.2     | 2.2 Testing the Double-Sided Cooled Inverter     | 273 |

| Ref | erenc   | es                                               | 274 |

| App | endiz   | x                                                | 284 |

| Puk | olicati | ions                                             | 322 |

# List of Figures

| Fig. 1.1 Power conversion system for Hybrid Electric and Electric Vehicles from Toyota Prius.                                                                     | 5  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.2 Picture of Toyota Prius IGBT inverter module and a circuit schematic take at Warwick.                                                                    | n  |

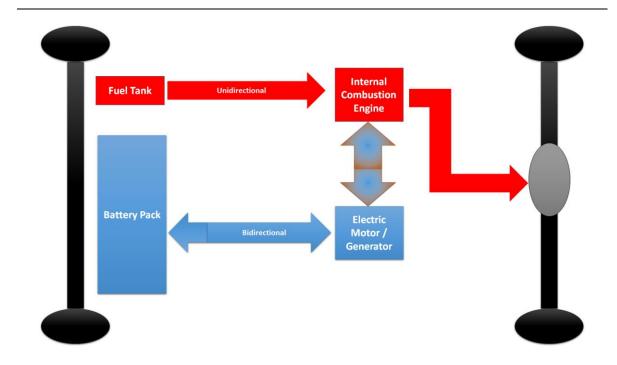

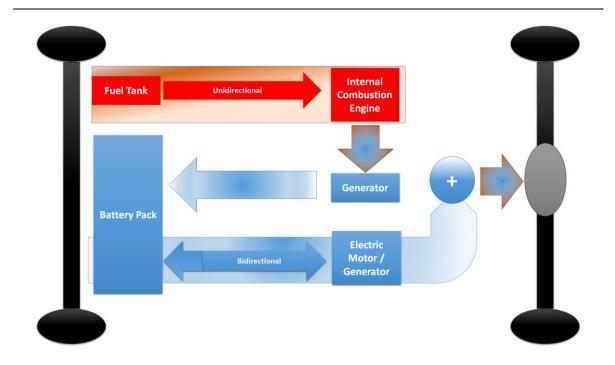

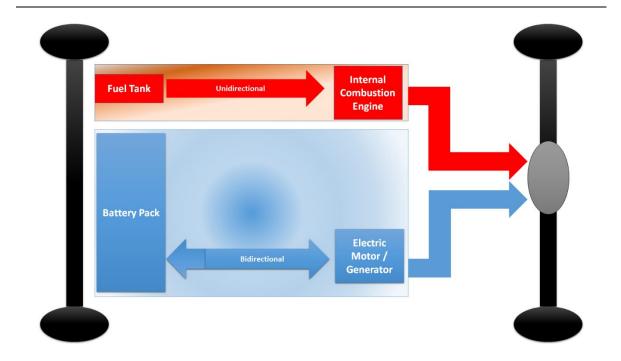

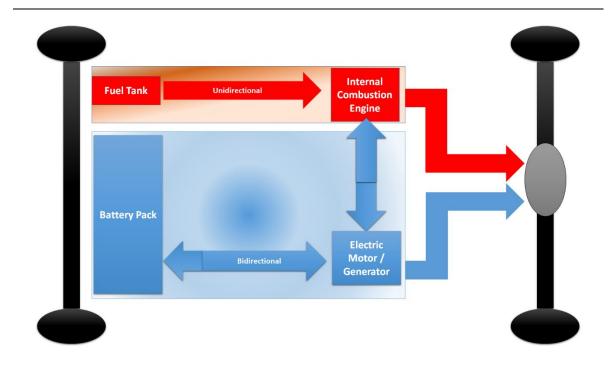

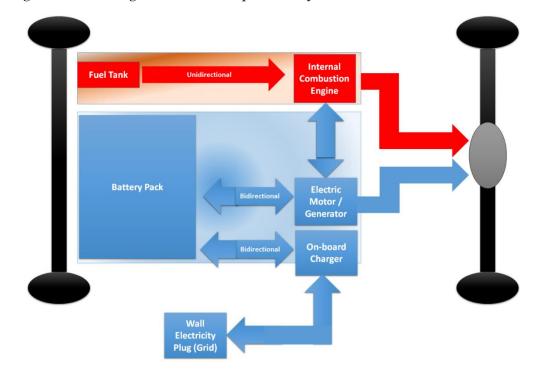

| Fig. 2.1 Schematic of a hypothetical hybrid electric vehicle with two powertrains                                                                                 | 19 |

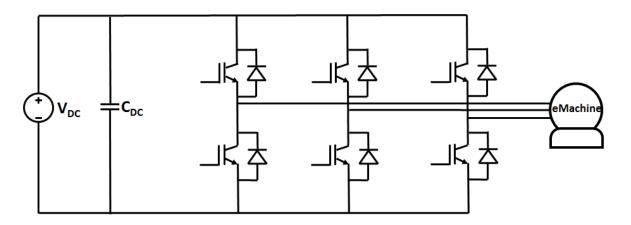

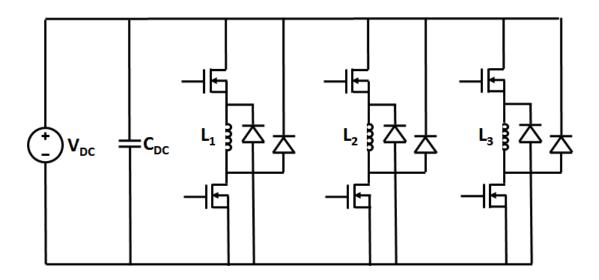

| Fig. 2.2 Circuit diagram of a 3-phase full bridge inverter.                                                                                                       | 22 |

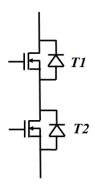

| Fig. 2.3 A half bridge topology.                                                                                                                                  | 22 |

| Fig. 2.4 Commercially available power inverter of (Left) Toyota Prius (HEV) and (Right) Nissan Leaf (BEV).                                                        | 24 |

| Fig. 2.5 Power inverter of Nissan Leaf including the gate driver, DC link capacitors power bridge, filters and cooling system.                                    |    |

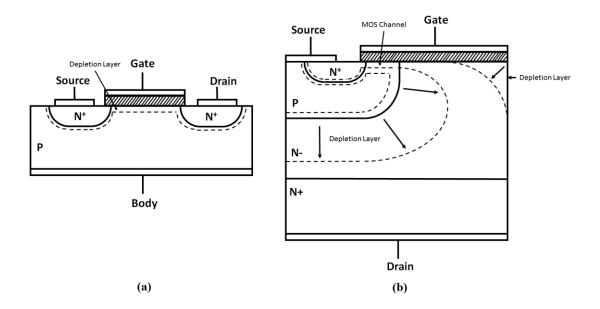

| Fig. 2.6 Cross-section view of (a) a lateral MOSFET and (b) a vertical power MOSF                                                                                 |    |

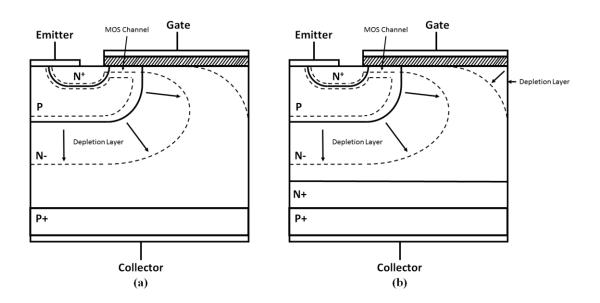

| Fig. 2.7 Cross section view of a vertical (a) NPT IGBT and (b) PT IGBT                                                                                            |    |

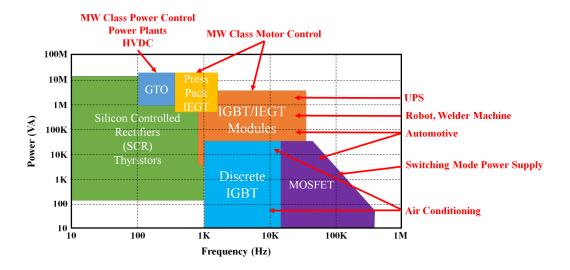

| Fig. 2.8 Power vs. Frequency graph for different power switching devices                                                                                          | 29 |

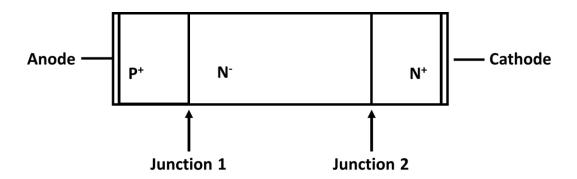

| Fig. 2.9 A schematic of PiN diode structure.                                                                                                                      | 30 |

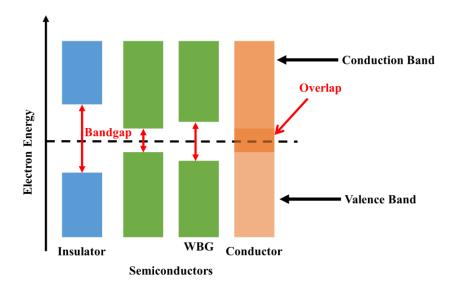

| Fig. 2.10 Energy bandgap in insulators, semiconductors and conductors                                                                                             | 34 |

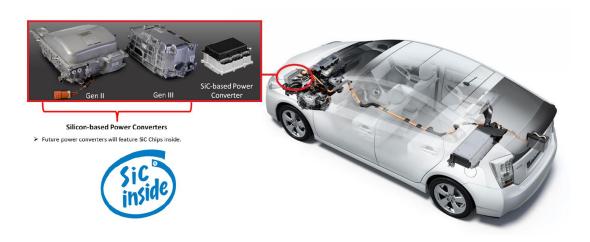

| Fig. 2.11 Evolution of Toyota Prius hybrid traction power inverter and reduction of inverter size over time and the future of commercial SiC-based power inverter |    |

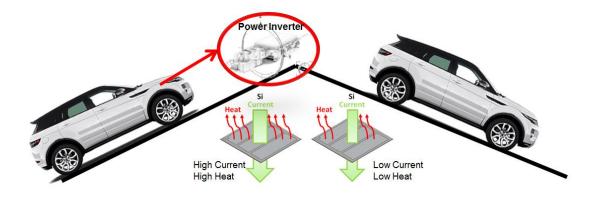

| Fig. 2.12 The impact of road and driving conditions on the heat generated in power electronic devices in a hypothetical HEV.                                      |    |

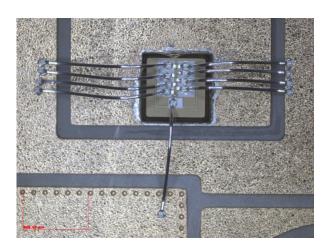

| Fig. 2.13 A SiC MOSFET die packaged on AlN DBC substrate with electroless NiPdAu surface coating assembled at Warwick                                             | 43 |

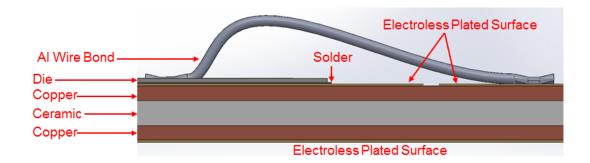

| Fig. 2.14 A cross section view of a conventional power module packaging showing stack of different materials on top of each other.                                | 45 |

| Fig. 2.15 Solder voids at zero power cycling.                                                                                                                     | 46 |

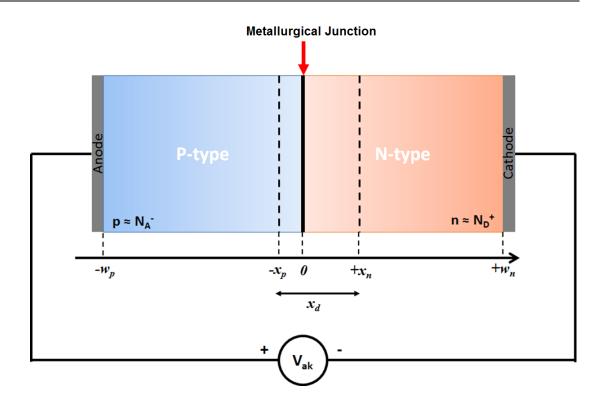

| Fig. 3.1 A diagram of P-N junction structure.                                                                                                                     | 52 |

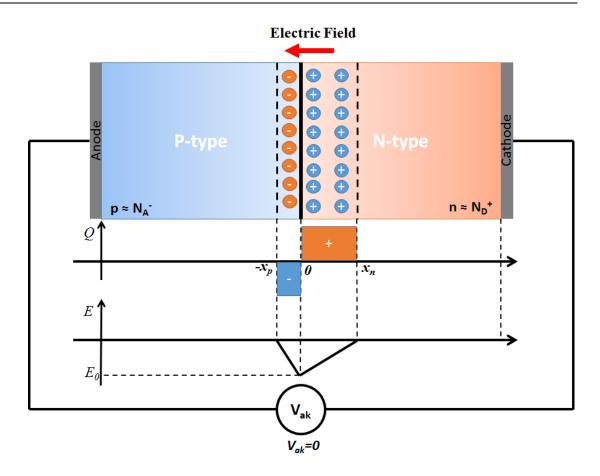

| Fig. 3.2 Built-in potential at P-N junction when no voltage is applied to the ends of structure.                                                                  |    |

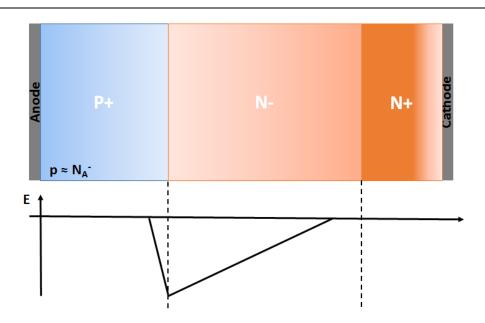

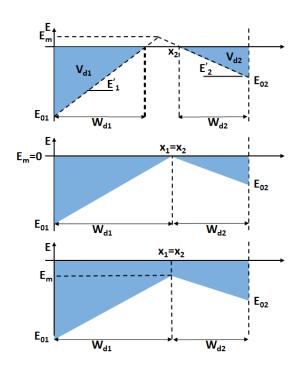

| Fig. 3.3 PiN diode structure and the electric field across the device                                                                                             | 56 |

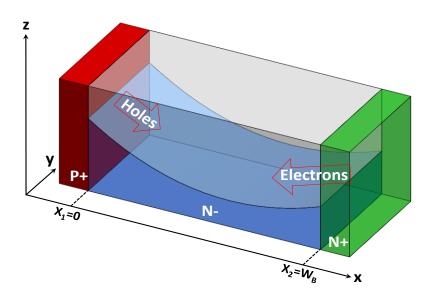

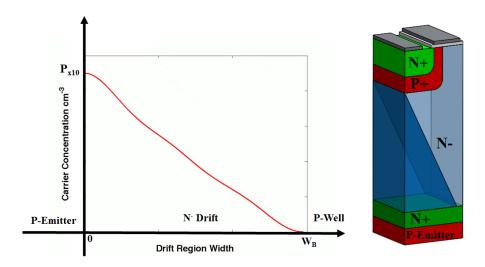

| Fig. 3.4.3D diagram of a PiN diode with formation of charge storage region                                                                                        | 56 |

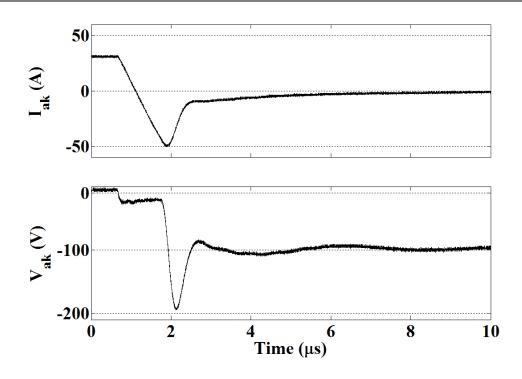

| Fig. 3.5 A typical PiN diode (IRF HF50D120ACE) current and voltage turn-off switching waveforms measured at Warwick                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

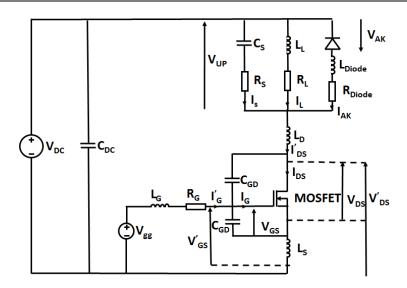

| Fig. 3.6 Clamped inductive switching circuit.                                                                                                                                                                                                                                                                              |

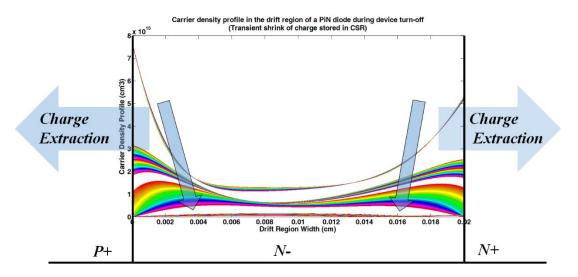

| Fig. 3.7 Extraction of charge from the drift region during turn-off of PiN diode64                                                                                                                                                                                                                                         |

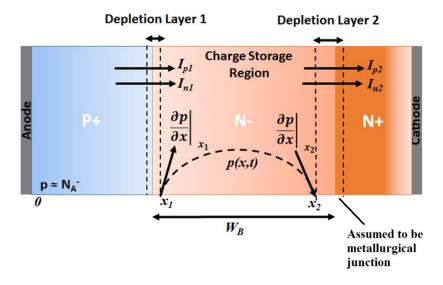

| Fig. 3.8 Charge storage region in a hypothetical PiN diode65                                                                                                                                                                                                                                                               |

| Fig. 3.9 Electric field at the boundaries of the depletion region under normal operation and punch-through                                                                                                                                                                                                                 |

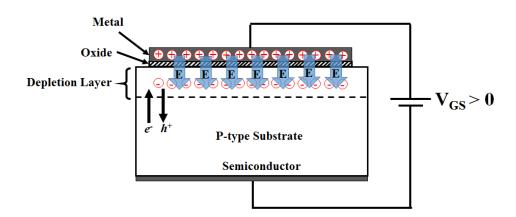

| Fig. 3.10 P-type substrate MOS capacitor under forward bias and formation of depletion region.                                                                                                                                                                                                                             |

| Fig. 3.11 Formation of channel when the MOSFET is biased and is conducting77                                                                                                                                                                                                                                               |

| Fig. 3.12 Static forward characteristic of a MOSFET at different gate-source voltages                                                                                                                                                                                                                                      |

| Fig. 3.13 Charge storage region in an IGBT with 3D view of the device cell structure.                                                                                                                                                                                                                                      |

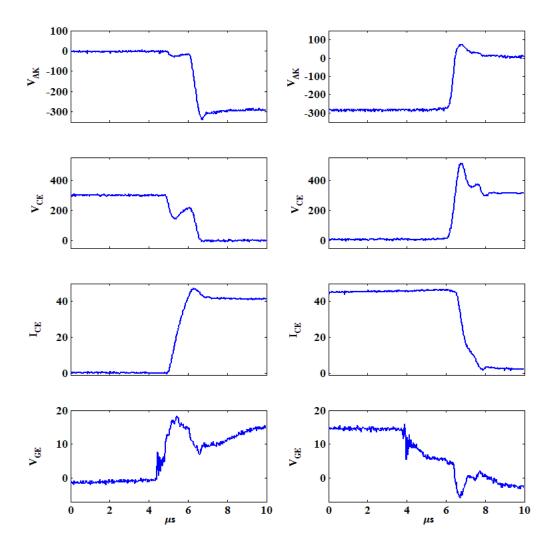

| Fig. 3.14 Measured IGBT turn-on and turn-off switching waveforms                                                                                                                                                                                                                                                           |

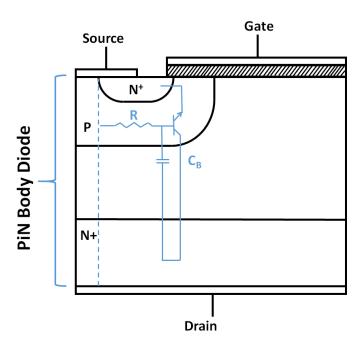

| Fig. 4.1 Block diagram of a vertical MOSFET with parasitic components99                                                                                                                                                                                                                                                    |

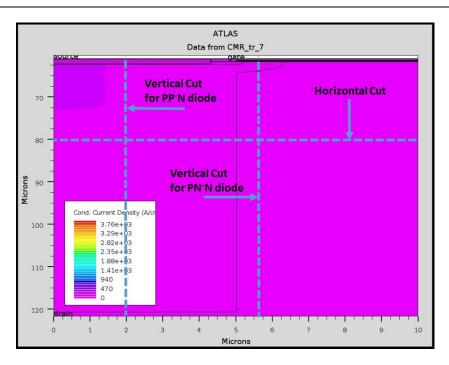

| Fig. 4.2 A super-junction device structure built in Silvaco also with the cross section cuts which were used to show the carrier concentration gradient in the vertical and horizontal axis.                                                                                                                               |

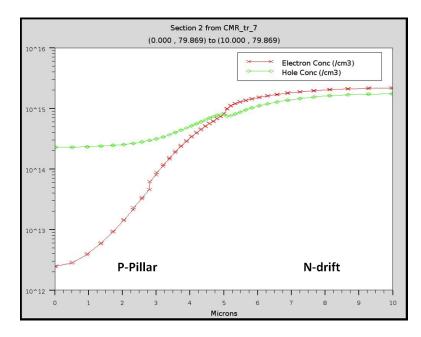

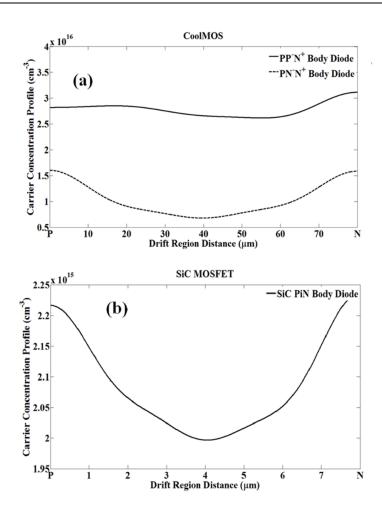

| Fig. 4.3 Electrons and holes concentration in the horizontal axis of the device showing small lateral gradient for carrier concentration                                                                                                                                                                                   |

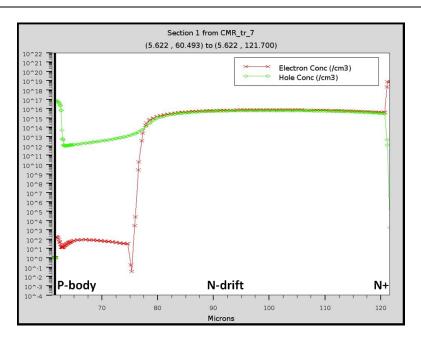

| Fig. 4.4 Electrons and holes concentration in the PN-N diode showing high vertical gradient in the carrier concentration in comparison with the lateral cross section view                                                                                                                                                 |

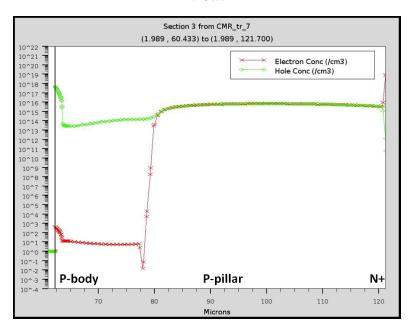

| Fig. 4.5 Electrons and holes concentration in the PP-N diode showing high vertical gradient in the carrier concentration in comparison with the lateral cross section view                                                                                                                                                 |

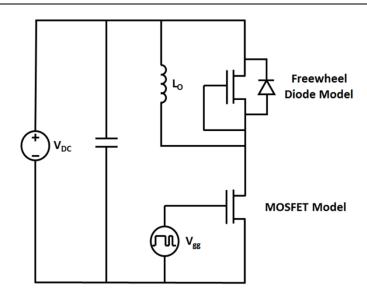

| Fig. 4.6 Chopper cell circuit used to model the switching dynamics of body diode of a MOSFET and CoolMOS                                                                                                                                                                                                                   |

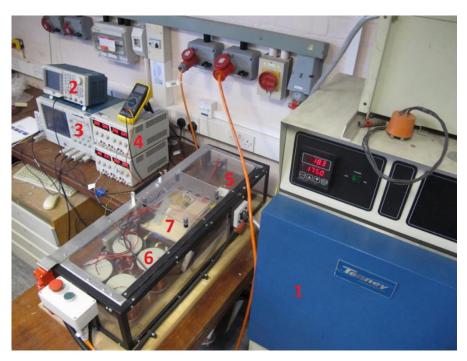

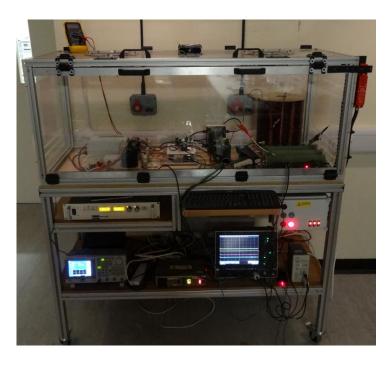

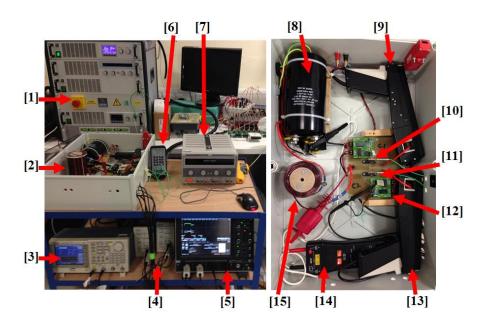

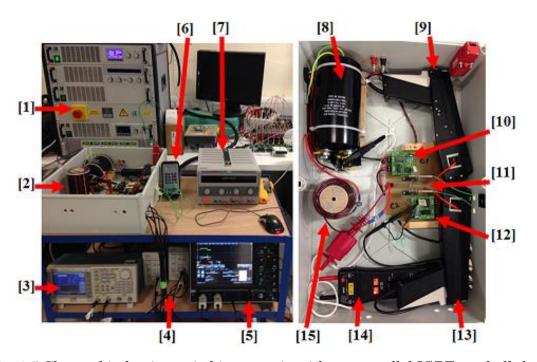

| Fig. 4.7 Experimental setup. 1. The environmental chamber where the device temperature can be changed between -75°C to 175°C, 2. Function generator to produce double pulse, 3. Oscilloscope, 4. DC power supply for the gate driver and gate input signal, 5. DC link capacitor, 6. Inductive load, 7. Gate drive circuit |

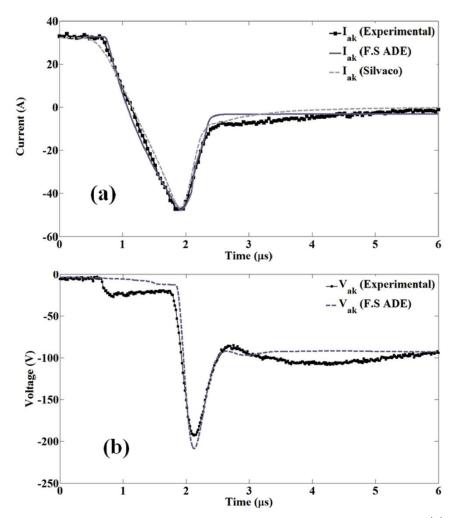

| Fig. 4.8 Simulation validation: Diode reverse recovery current waveform (a) and voltage waveform (b) from the experimental results, Silvaco Finite Element device simulation and Fourier Series ADE reconstruction simulation at the room temperature using $22~\Omega$ gate resistance                                    |

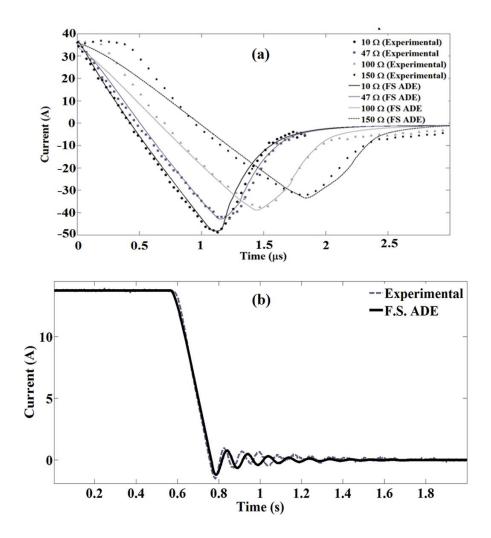

| Fig. 4.9 (a) PiN diode reverse recovery waveform for different IGBT gate resistances (different dI/dt) - Comparison between the experimental results and the simulation results using the Fourier Series ADE reconstruction. Fig. 4.9 (b). Measured and modelled reverse recovery characteristics of the SiC MOSFET body-diode109 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

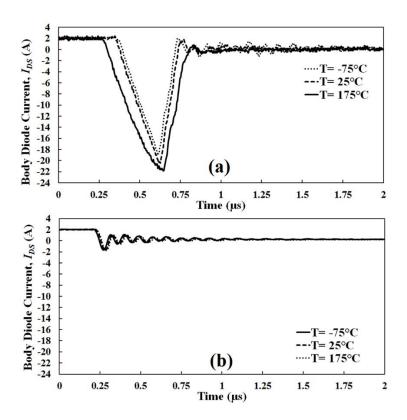

| Fig. 4.10 (a) Measured reverse recovery current as a function of time for the CoolMOS body diode at different temperatures. Fig. 5(b) Measured reverse recovery current as a function of time for the SiC MOSFET body diode at different temperatures111                                                                          |

| Fig. 4.11 (a) a vertical MOSFET structure, (b) CoolMOS structure including the parasitic BJT and a body diode. (c) Equivalent circuit of a MOSFET with the parasitic BJT and a body diode                                                                                                                                         |

| Fig. 4.12 Carrier concentration profile in the drift region of a PP-N and PN-N body diodes of a CoolMOS (a) and the carrier concentration profile of a SiC MOSFET body diode during the high level injection of these devices before switching off (b)113                                                                         |

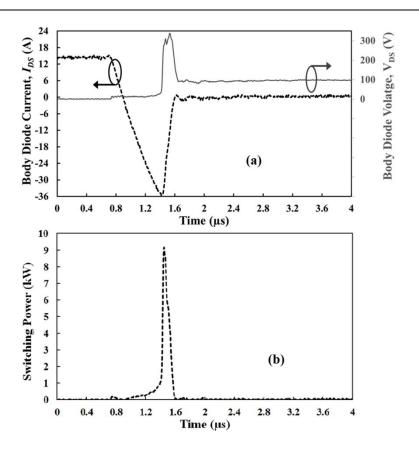

| Fig. 4.13 (a) CoolMOS switching-off current and voltage waveform showing high dI/dt and dV/dt at the same instant of time (b) Instantaneous switching power of CoolMOS during the switching-off                                                                                                                                   |

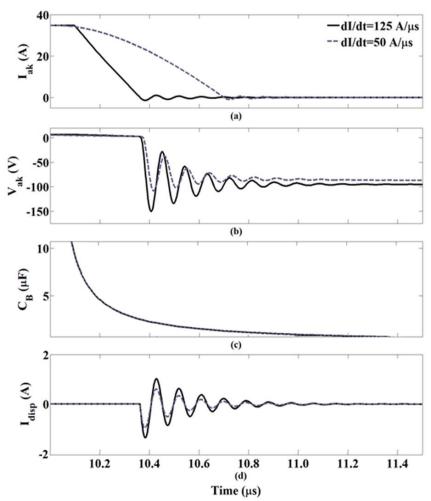

| Fig. 4.14 Fourier series ADE simulation of the SiC MOSFET body diode displacement current, parasitic BJT base capacitance and electric field at P+N- junction during turn-off                                                                                                                                                     |

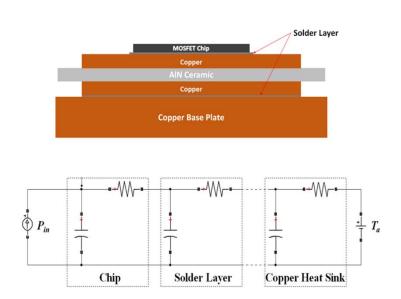

| Fig. 4.15 Cross section view of a basic hypothetical die mounted on top of a DBC and soldered to a base plate and the corresponding Cauer-network of this power module.                                                                                                                                                           |

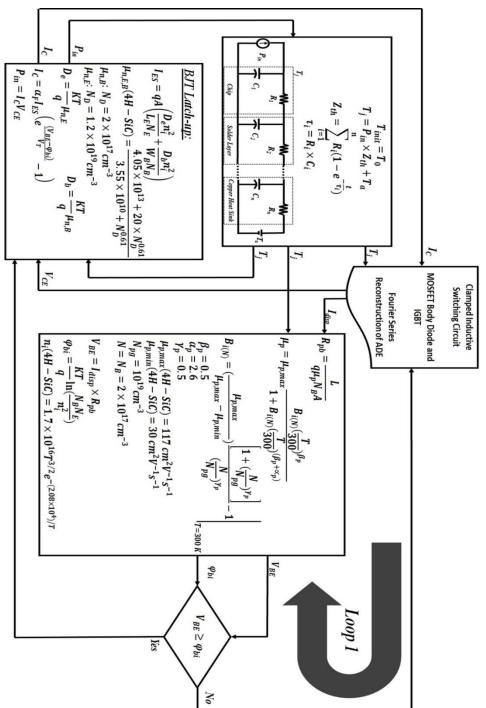

| Fig. 4.16 Block diagram of the electro-thermal parasitic BJT latch-up coupled with the clamped inductive switching circuit model for a MOSFET body diode                                                                                                                                                                          |

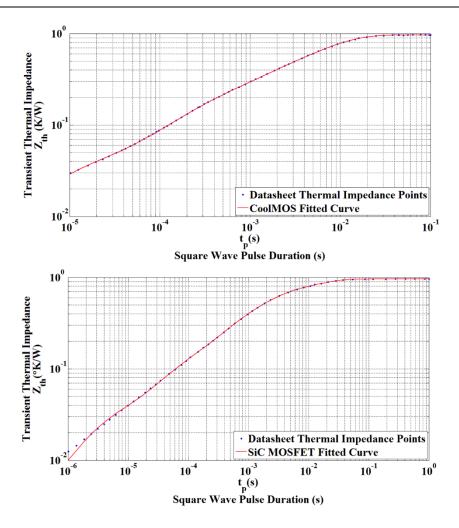

| Fig. 4.17 Fitted curve of the transient thermal impedance of Infineon CoolMOS and Cree SiC MOSFET                                                                                                                                                                                                                                 |

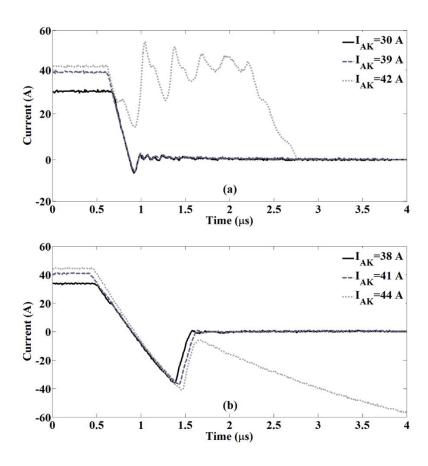

| Fig. 4.18 (a) Experimental results showing SiC MOSFET body diode reverse recovery at varied forward currents. (b) Experimental results showing CoolMOS body diode reverse recovery at varied forward current                                                                                                                      |

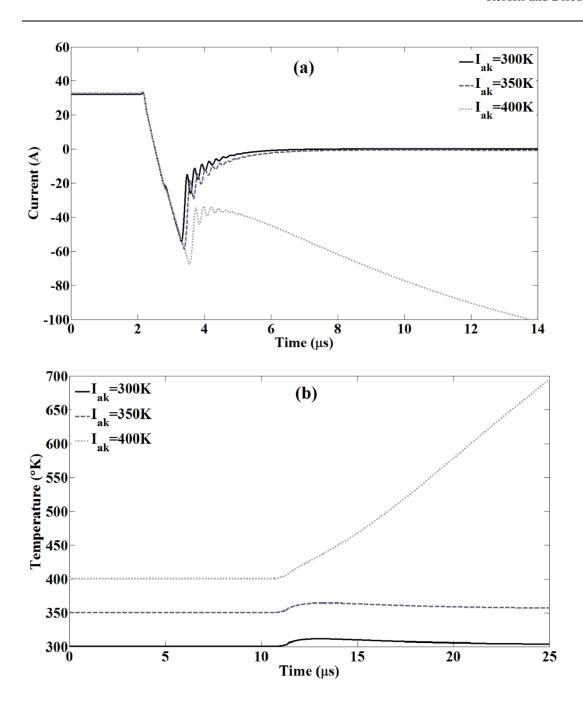

| Fig. 4.19 (a) Parasitic BJT latch-up current at different temperatures (SiC MOSFET). (b) Parasitic BJT latch-up at different temperatures (CoolMOS)                                                                                                                                                                               |

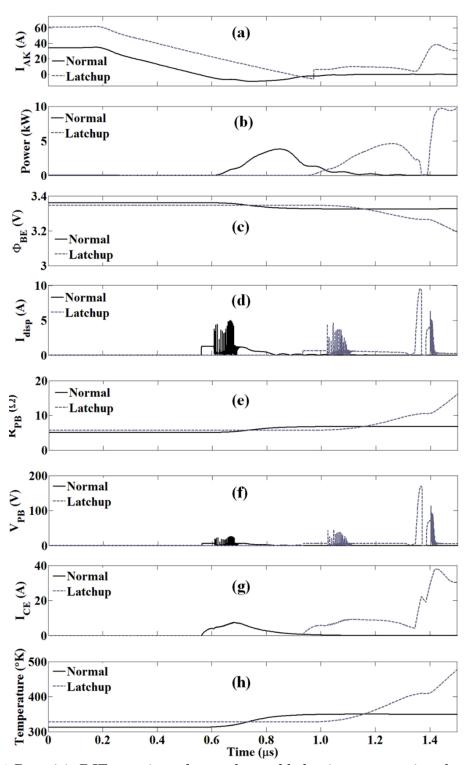

| Fig. 4.20 Parasitic BJT transient electro-thermal behaviour; comparison between the SiC MOSFET PiN diode under normal switching condition and under BJT latch-up.                                                                                                                                                                 |

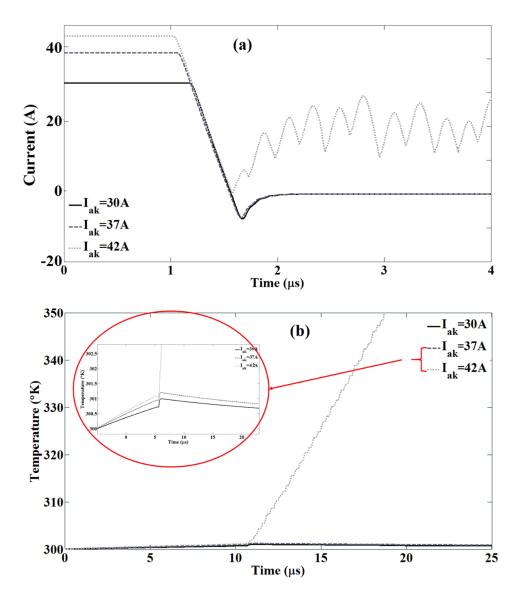

| Fig. 4.21 (a) Simulation results showing reverse recovery waveform of SiC MOSFET body diode for varied forward current. (b) Temperature rise within the device during the body diode reverse recovery                                                                                                                             |

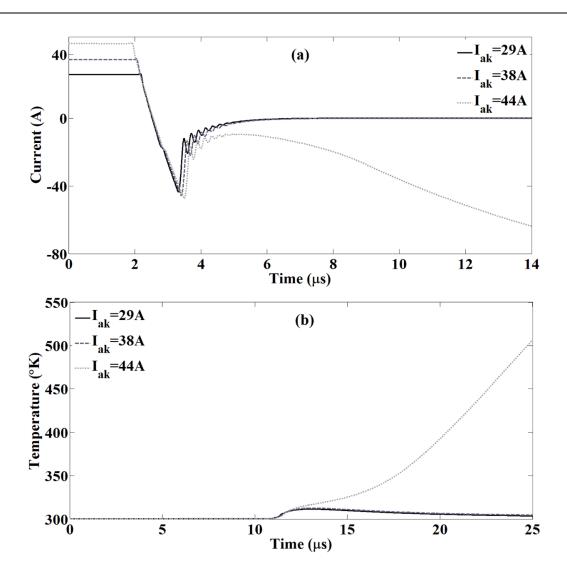

| Fig. 4.22 (a) Simulation results showing reverse recovery waveform of CoolMOS body diode for varied forward current. (b) Temperature rise within the device during the body diode reverse recovery.                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

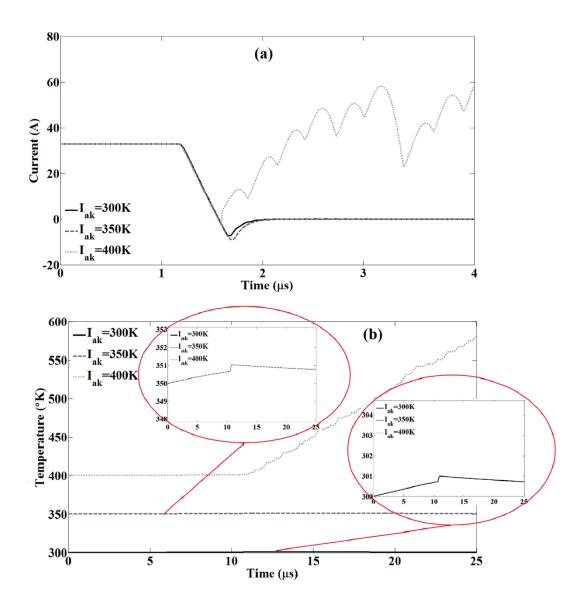

| Fig. 4.23 (a) Simulation results showing reverse recovery waveform of SiC body diode for varied temperature. (b) Temperature rise within the device during the body diode reverse recovery                                                                                        |

| Fig. 4.24 (a) Simulation results showing reverse recovery waveform of CoolMOS body diode for varied temperature. (b) Temperature rise within the device during the body diode reverse recovery                                                                                    |

| Fig. 4.25 Actual die sizes for SiC MOSFET and CoolMOS devices                                                                                                                                                                                                                     |

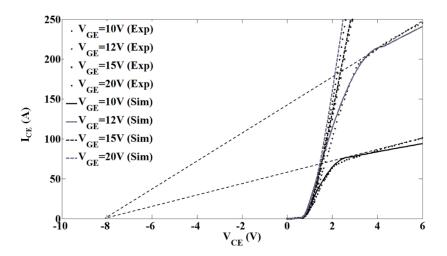

| Fig. 5.1 Forward characteristic of DM2G100SH12AE power module and comparison of the datasheet forward characteristic with the device model results151                                                                                                                             |

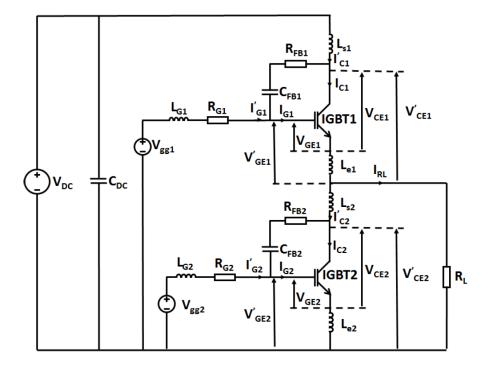

| Fig. 5.2 Schematic of a half-bridge topology in a voltage source inverter used to investigate the parasitic turn-on effect                                                                                                                                                        |

| Fig. 5.3 Experimental setup for the parasitic turn-on                                                                                                                                                                                                                             |

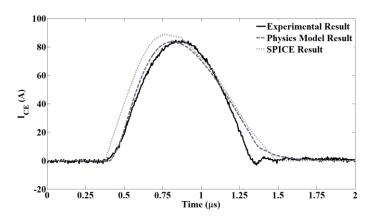

| Fig. 5.4 ICE current waveform of the bottom IGBT during the cross-talk, comparison between the experiment, the physics-based model and SPICE                                                                                                                                      |

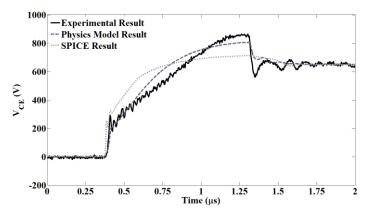

| Fig. 5.5 VCE voltage waveform of the bottom IGBT during the cross-talk, comparison between the experiment, the physics-based model and SPICE                                                                                                                                      |

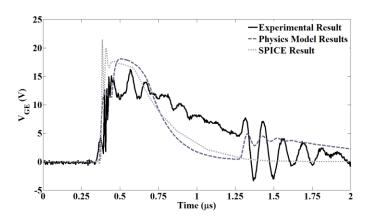

| Fig. 5.6 VGE voltage waveform of the bottom IGBT during the cross-talk, comparison between the experiment, the physics-based model and SPICE156                                                                                                                                   |

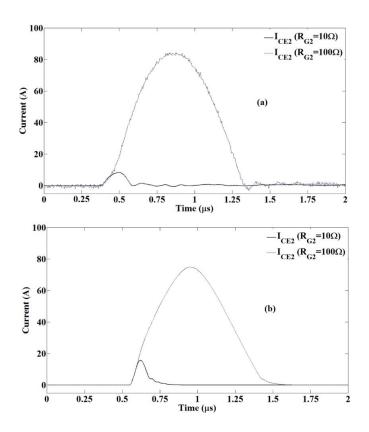

| Fig. 5.7 ICE current waveform of the bottom IGBT during the cross-talk for two different gate resistances; (a) Experimental results (b) Physics-based model results.                                                                                                              |

| Fig. 5.8 VCE voltage waveform of the bottom IGBT during the cross-talk for two different gate resistances; (a) Experimental results (b) Physics-based model results.                                                                                                              |

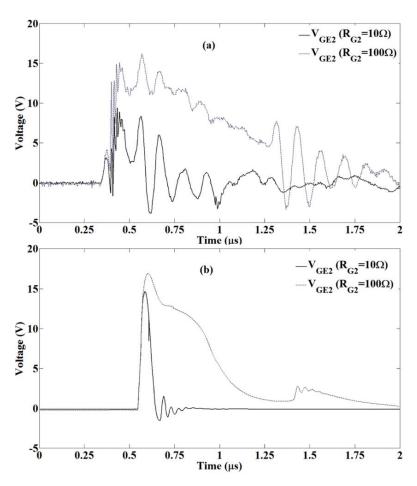

| Fig. 5.9 VGE voltage waveform of the bottom IGBT during the cross-talk for two different gate resistances; (a) Experimental results (b) Physics-based model results.                                                                                                              |

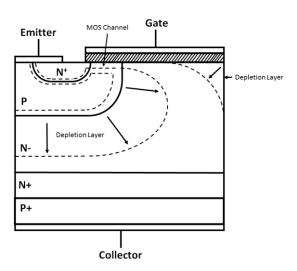

| Fig. 5.10 Cross section view of an IGBT showing the process of depletion layer formation.                                                                                                                                                                                         |

| Fig. 5.11 Parasitic turn-on process.                                                                                                                                                                                                                                              |

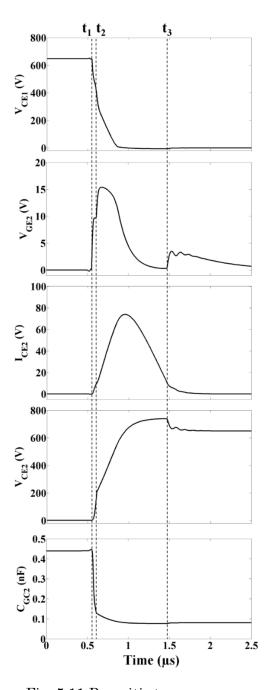

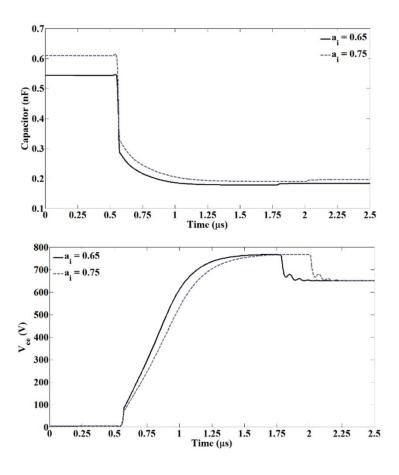

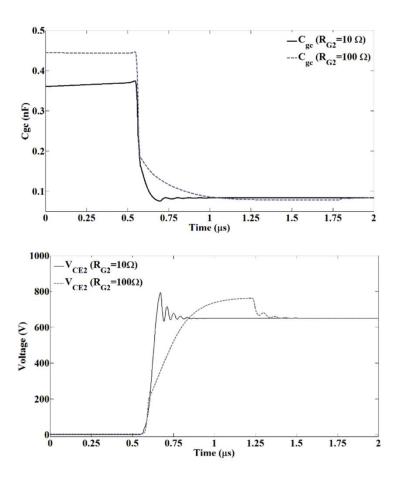

| Fig. 5.12 Simulation result showing (a) time dependent gate-collector capacitance for two different values of ratio of intercell area and active die area (ai) (b) collector-emitter voltage slope change for two different values of ratio of intercell area and active die area |

| active the area                                                                                                                                                                                                                                                                   |

| Fig. 5.13 Simulation result showing (a) time dependent gate-collector capacitance for three different values of Cox (b) collector-emitter voltage slope change for three different values of Cox                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 5.14 Simulation result showing (a) time dependent gate-collector capacitance for two gate resistances (b) collector-emitter voltage slope change for two gate resistances                                                  |

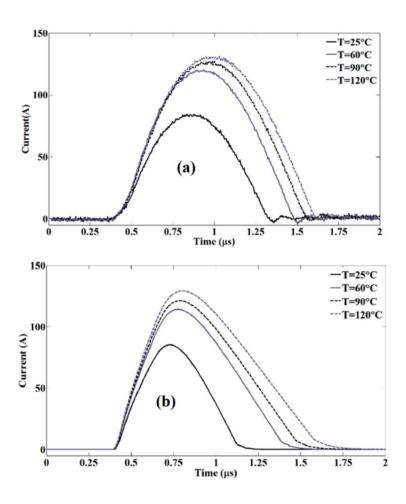

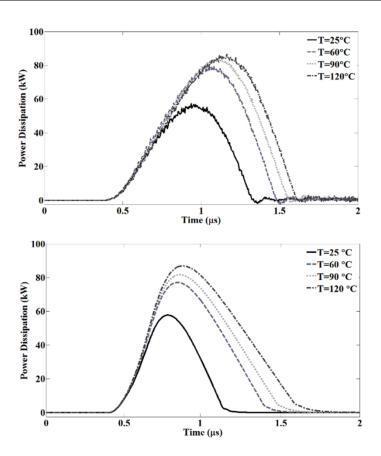

| Fig. 5.15 Shoot-through current at different temperature; (a) Experimental result and (b) Simulation results                                                                                                                    |

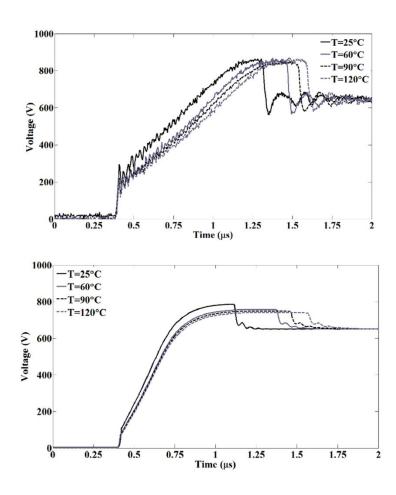

| Fig. 5.16 Collector-emitter voltage at different temperature. (a) Experimental result and (b) Simulation results                                                                                                                |

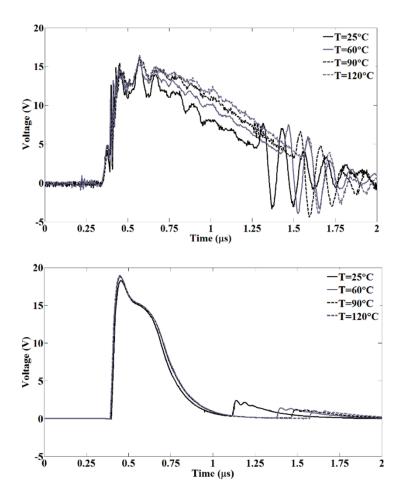

| Fig. 5.17 Gate-emitter voltage at different temperature. (a) Experimental result and (b) Simulation results                                                                                                                     |

| Fig. 5.18 Experimental result showing shoot-through current and voltage and switching power dissipation                                                                                                                         |

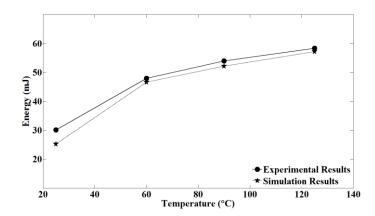

| Fig. 5.19 Shoot-through switching power dissipation in (a) experiments and (b) simulation                                                                                                                                       |

| Fig. 5.20 Shoot-through switching power dissipation comparison between experiments and simulation                                                                                                                               |

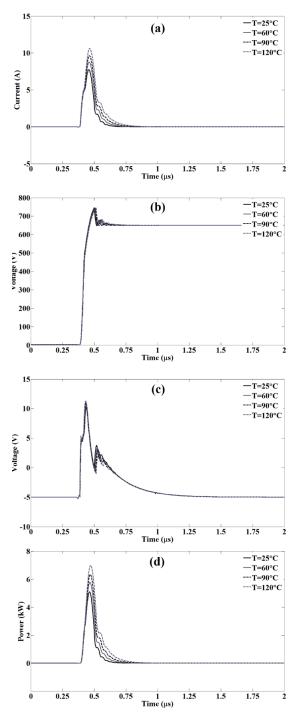

| Fig. 5.21 Simulation result showing (a) shoot through current (b) collector-emitter voltage (c) gate-emitter voltage (d) power losses due to cross-talk for a single switching event for different temperatures                 |

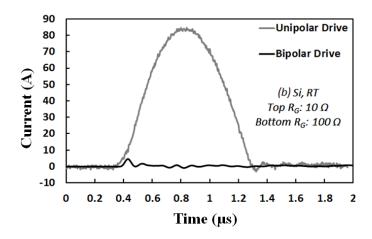

| Fig. 5.22 Experimental result showing the comparison between the shoot-through current using unipolar gate drive and bipolar gate drive                                                                                         |

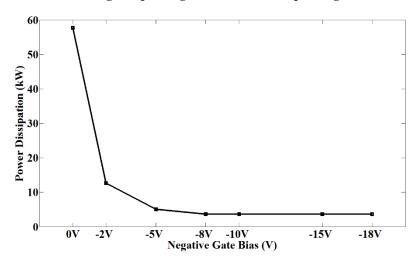

| Fig. 5.23 Simulation result showing the peak power dissipation as a function of negative gate voltage at room temperature for $10\Omega$ gate resistance at the top switch and $100\Omega$ gate resistance at the bottom switch |

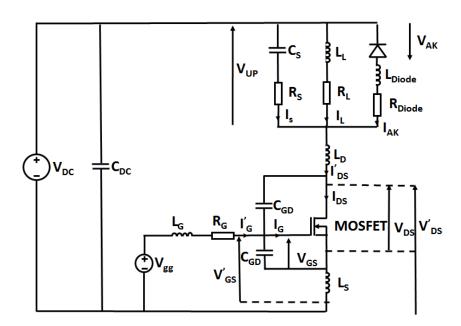

| Fig. 5.24 Clamped inductive switching circuit compromising with a top side PiN diode and bottom side SiC MOSFET with all the parasitic components used to investigate the parasitic gate turn-off                               |

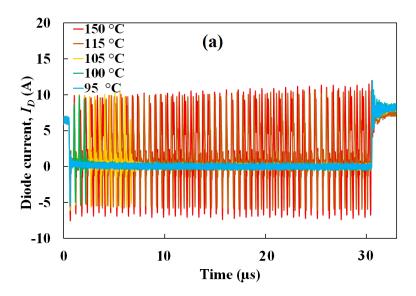

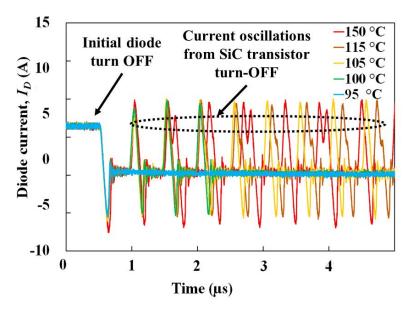

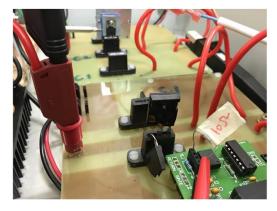

| Fig. 5.25 Zoomed in view of the parasitic gate turn-off at different junction temperatures                                                                                                                                      |

| Fig. 5.26 Zoomed in view of the parasitic gate turn-off at different junction temperatures.                                                                                                                                     |

| Fig. 5.27 Clamped inductive switching test rig setup                                                                                                                                                                            |

| Fig. 5.28 Catastrophic breakdown of SiC MOSFET due to parasitic gate turn-off phenomenon induced by the high recombination rate of the top antiparallel diode184                                                                |

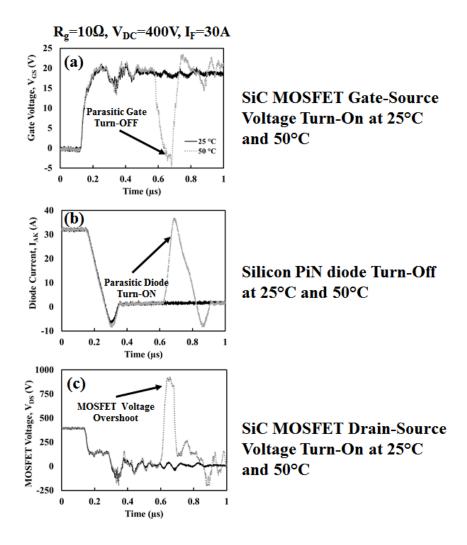

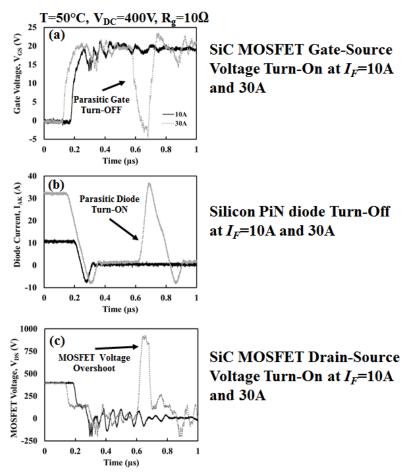

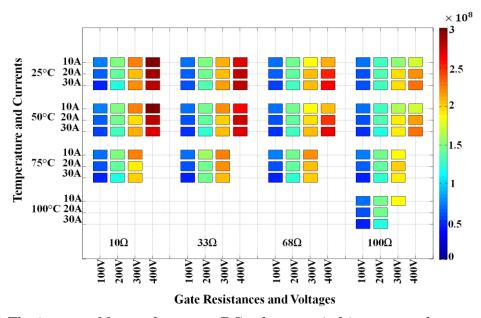

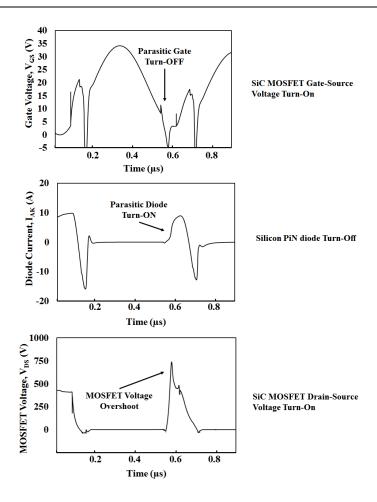

| Fig. 5.29 (a) SiC MOSFET gate-source voltage during turn-on (b) Silicon PiN diode turn-off (c) SiC MOSFET drain-source voltage turn-on waveform at 25°C and 50°C.                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                 |

| Fig. 5.30 Reverse recovery waveform of the PiN diode during turn off for (a) different MOSFET switching rates (b) different diode junction temperatures                                                                                                                                                         |

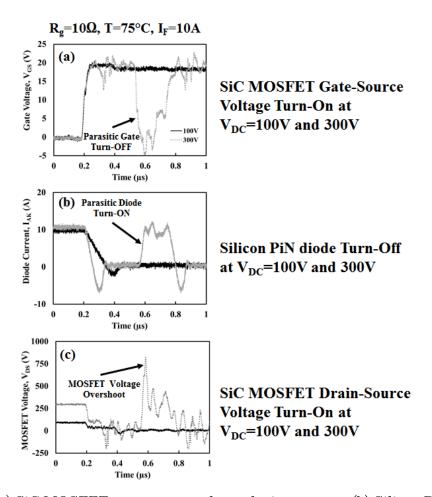

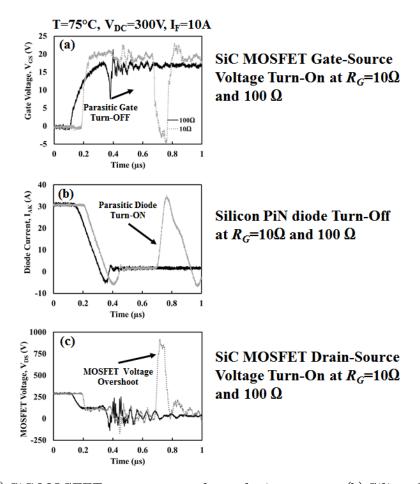

| Fig. 5.31 (a) SiC MOSFET gate-source voltage during turn-on (b) Silicon PiN diode turn-off (c) SiC MOSFET drain-source voltage turn-on waveform at VDC=100V and 300V                                                                                                                                            |

| Fig. 5.32 (a) SiC MOSFET gate-source voltage during turn-on (b) Silicon PiN diode turn-off (c) SiC MOSFET drain-source voltage turn-on waveform at IF=10A and 30A.                                                                                                                                              |

| Fig. 5.33 (a) SiC MOSFET gate-source voltage during turn-on (b) Silicon PiN diode turn-off (c) SiC MOSFET drain-source voltage turn-on waveform at RG= $10\Omega$ and $100\Omega$                                                                                                                               |

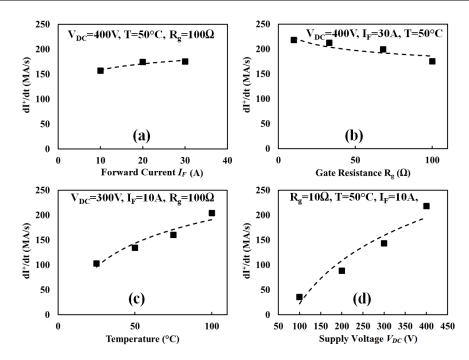

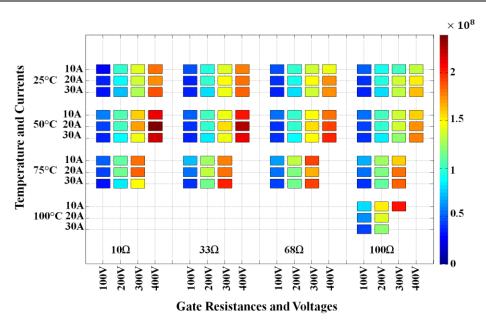

| Fig. 5.34 The recombination dI/dt as a function of (a) Forward current, (b) Gate resistance, (c) Junction temperature and (d) The supply voltage192                                                                                                                                                             |

| Fig. 5.35 The impact of forward current, DC voltage, switching rate and temperature on the positive dI/dt during the reverse recovery                                                                                                                                                                           |

| Fig. 5.36 The impact of forward current, DC voltage, switching rate and temperature on the negative dI/dt during the reverse recovery                                                                                                                                                                           |

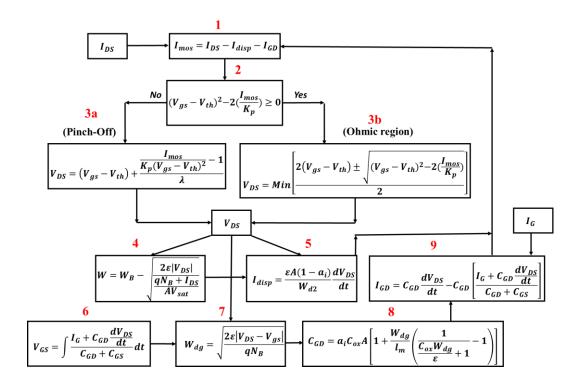

| Fig. 5.37 SiC MOSFET model block diagram and physics-based equations194                                                                                                                                                                                                                                         |

| Fig. 5.38 Simulation results showing parasitic gate turn-off (a) Gate-source turn-on voltage waveform, (b) PiN diode turn-off current waveform, (c) MOSFET drain-source turn-on voltage.                                                                                                                        |

| Fig. 6.1 (a) Nissan Leaf power inverter with 4 parallel IGBTs for each top and bottom switches in three phase voltage source converter, (b) Infineon power module (FF1000R17IE4) with 1.7kV/1 kA power rating showing 6 parallel IGBTs with a very long gate path and unbalanced gate resistance and inductance |

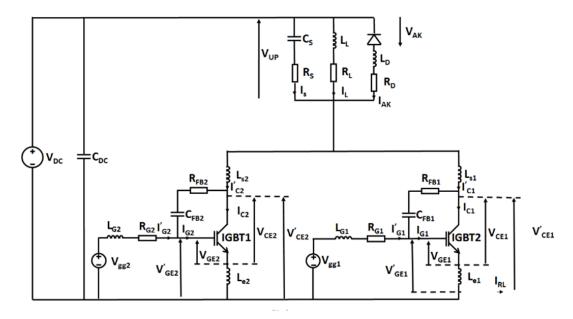

| Fig. 6.2 Schematic of the clamped inductive switching circuit with all the parasitic inductances                                                                                                                                                                                                                |

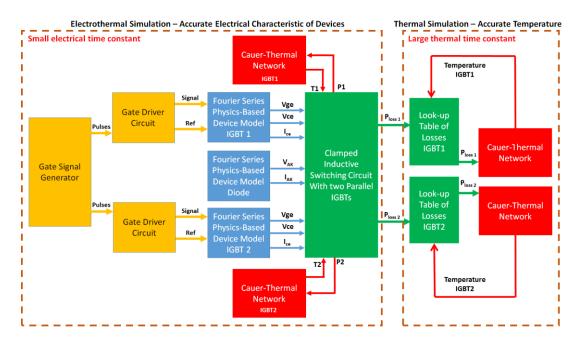

| Fig. 6.3 Block diagram of the electro-thermal simulation                                                                                                                                                                                                                                                        |

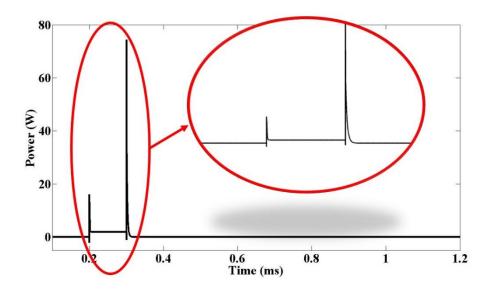

| Fig. 6.4 A typical power loss during the repetitive clamped inductive switching for one period with duty cycle of 10%                                                                                                                                                                                           |

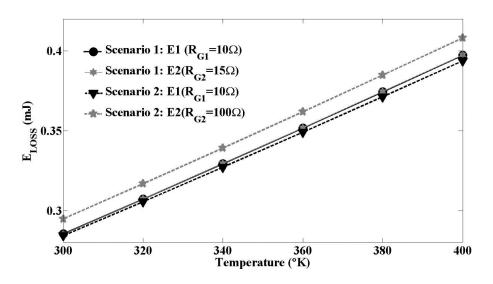

| Fig. 6.5 Energy losses for two scenarios - scenario 1: RG1=10 $\Omega$ and RG2=15 $\Omega$ and scenario 2: RG1=10 $\Omega$ and RG2=100 $\Omega$ .                                                                                                                                                               |

| Fig. 6.6 CAD design for the discrete TO247 IGBT package and the cross-section view of the material stack                                                                                                                                                                                                        |

| Fig. 6.7 Clamped inductive switching test rig with two parallel IGBTs and all the circuit components                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

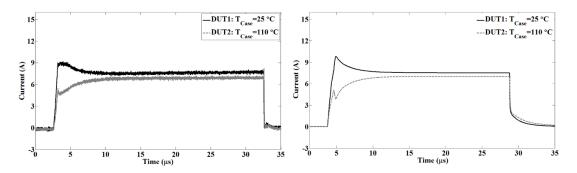

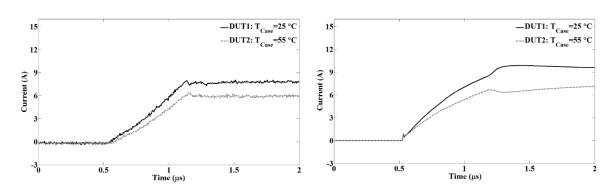

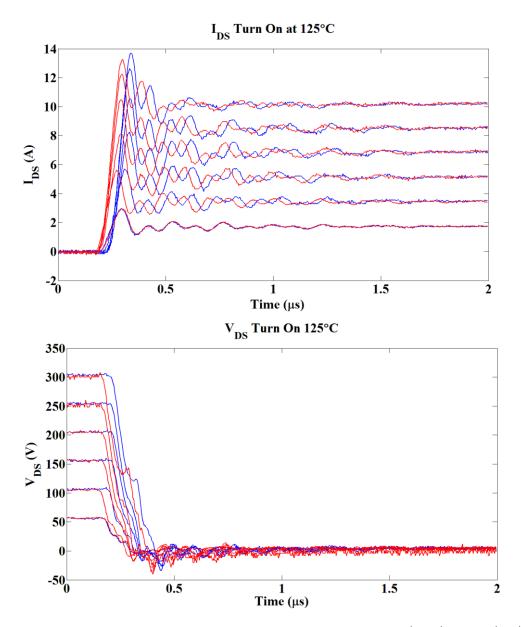

| Fig. 6.8 Experimental results (Left) and Simulation results (Right) of turn-on and turn-off switching current waveforms of two parallel IGBTs working at different junction temperature.        |

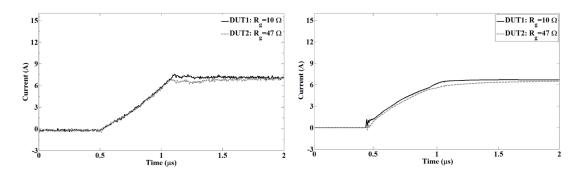

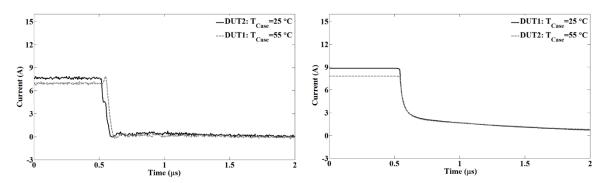

| Fig. 6.9 Experimental results (Left) and Simulation results (Right) of turn-on switching current waveform of two parallel IGBTs working with two different gate resistances.                    |

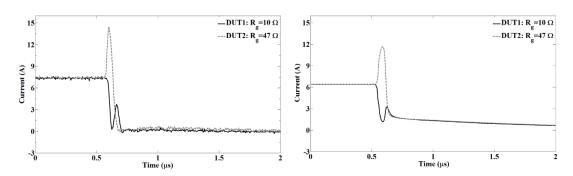

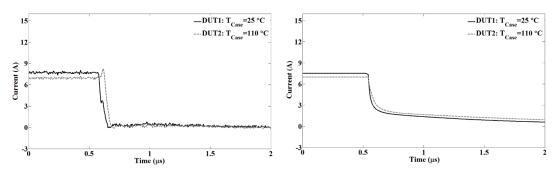

| Fig. 6.10 Experimental result (Left) and Simulation results (Right) of turn-off switching current waveform of two parallel IGBTs working with two different gate resistances.                   |

| Fig. 6.11 Experimental result (Left) and Simulation result (Right) of turn-on switching current waveform of two parallel IGBTs working at different case temperature (25°C and 55°C)            |

| Fig. 6.12 Experimental results (Left) and Simulation results (Right) of turn-off switching current waveform of two parallel IGBTs working at different case temperatures (25°C and 55°C)        |

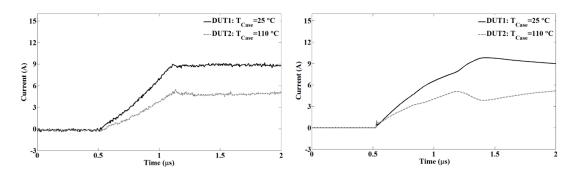

| Fig. 6.13 Experimental results (Left) and Simulation results (Right) of turn-on switching current waveform of two parallel IGBTs working at different case temperatures (25°C and 110°C).       |

| Fig. 6.14 Experimental results (Left) and Simulation results (Right) of turn-off switching current waveform of two parallel IGBTs working at different case temperatures (25°C and 110°C).      |

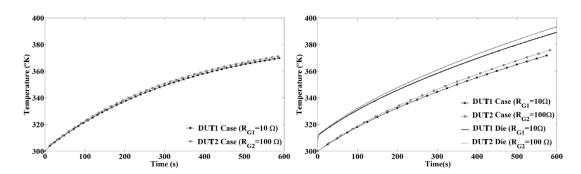

| Fig. 6.15 Experimental results (Left) and simulation results (Right) of temperature rise within two parallel IGBTs with different gate resistances under repetitive clamped inductive switching |

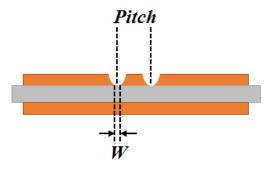

| Fig. 7.1 Minimum pitch and minimum width of spacing between conductors on a DBC substrate                                                                                                       |

| Fig. 7.2 Al stencil for solder screening process with thickness of 6 thou                                                                                                                       |

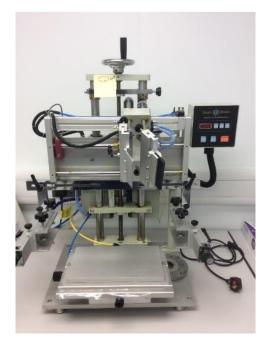

| Fig. 7.3 Bench-top Mascoprint S200HFC semi-automatic solder screen printing machine with stencil holder                                                                                         |

| Fig. 7.4 Cammax Precima EDB65 Eutetic pick and place die bonder, including N2 cover gas                                                                                                         |

| Fig. 7.5 a PiN diode contaminated due to exposure to air                                                                                                                                        |

| Fig. 7.6 ATV SRO-704 programmable solder reflow/thermal processing, rapid thermal annealing (RTA) oven with 950°C processing capability                                                         |

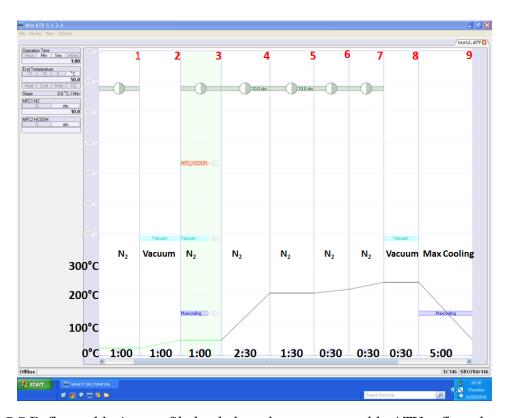

| Fig. 7.7 Reflow soldering profile loaded on the programmable ATV reflow chamber 230                                                                                                             |

| Fig. 7.8 Sample in the ATV oven during stage 6 of the Indium 8.9HF Pb-Free solder reflow profile                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

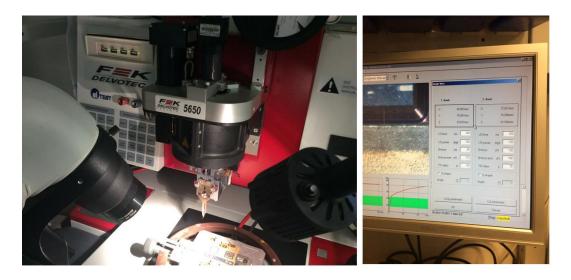

| Fig. 7.9 Orthodyne model 20 heavy wire bonder                                                                                                                  |

| Fig. 7.10 FEK Delvotec 5650 heavy automatic wire bonder and a wire bonded IGBT made at Warwick                                                                 |

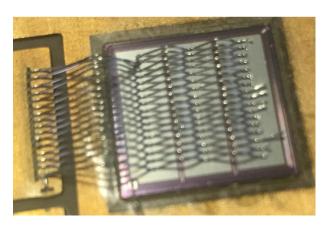

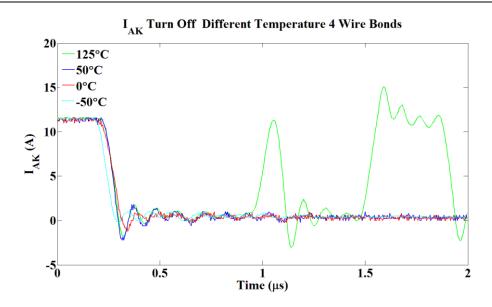

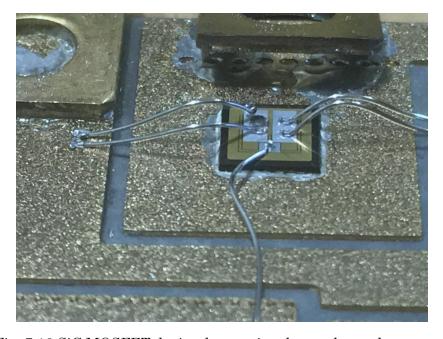

| Fig. 7.11 SiC MOSFET packaged using different number of wire bonds236                                                                                          |

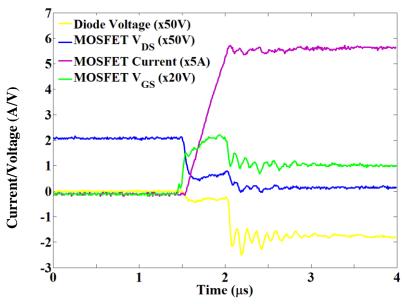

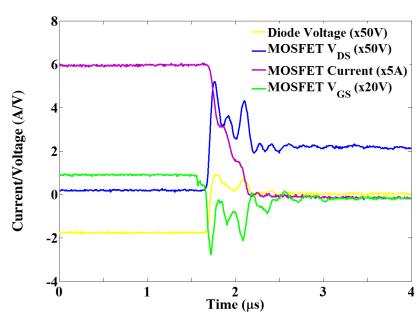

| Fig. 7.12 Turn-on switching waveform of the SiC MOSFET with SiC Schottky diode at 100V and 30A Forward current at 125°C.                                       |

| Fig. 7.13 Turn-off switching waveform of the SiC MOSFET with SiC Schottky diode at 100V and 30A Forward current at 125°C.                                      |

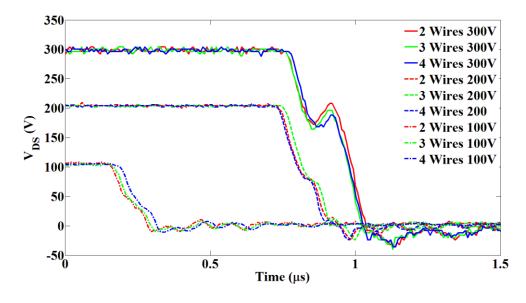

| Fig. 7.14 Turn-on drain-source voltage waveform for SiC MOSFET packaged using 2, 3 and 4 wire bonds on the source pads                                         |

| Fig. 7.15 Turn-off drain-source voltage waveform for SiC MOSFET packaged using 2, 3 and 4 wire bonds on the source pads                                        |

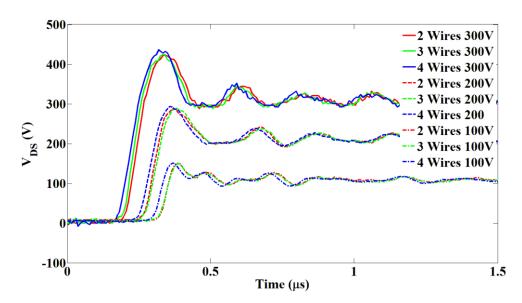

| Fig. 7.16 Turn-on switching waveforms of SiC MOSFET with 2 (blue) and 4 (red) wire bonds at $125^{\circ}$ C240                                                 |

| Fig. 7.17 Reverse recovery induced parasitic gate turn-off at elevated temperature.241                                                                         |

| Fig. 7.18 SiC MOSFET device destruction due to thermal runaway241                                                                                              |

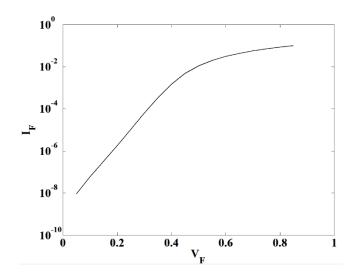

| Fig. 7.19 I-V curve of the PiN diode.                                                                                                                          |

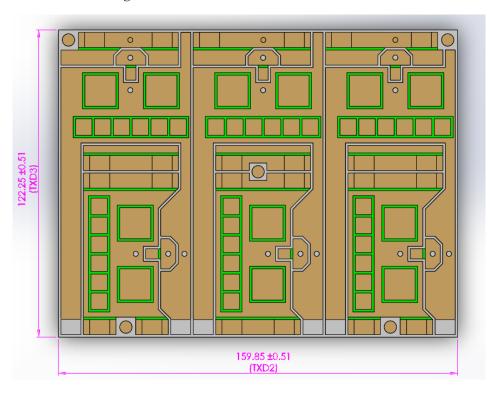

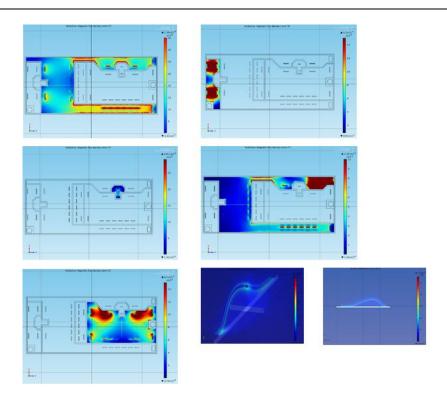

| Fig. 7.20 DBC layout for three phase inverter.                                                                                                                 |

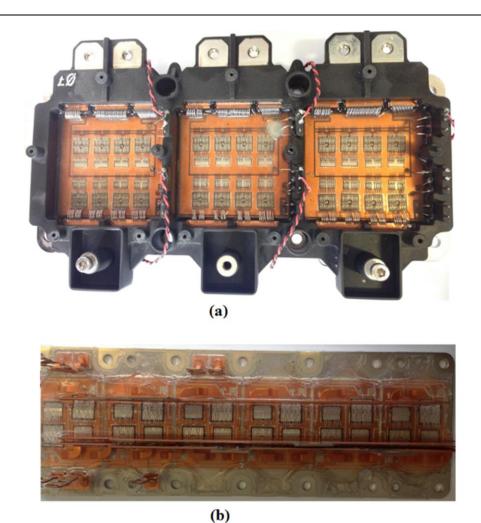

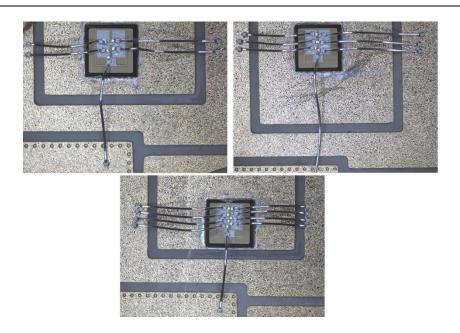

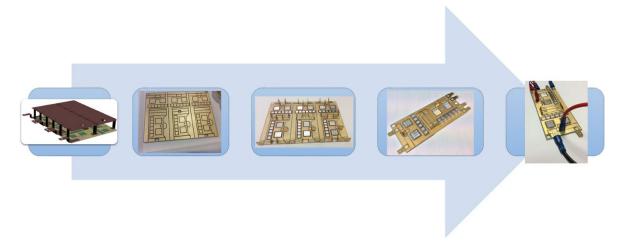

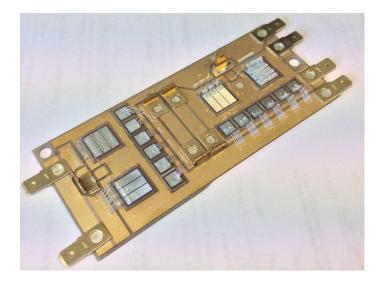

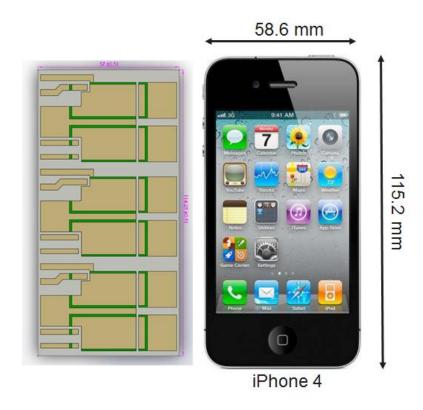

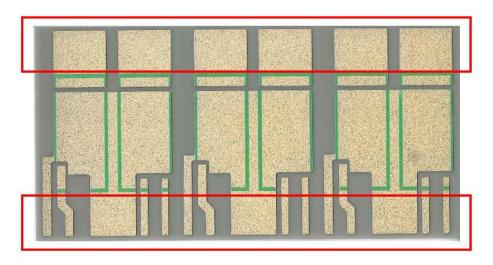

| Fig. 7.21Process of fabricating the power bridge: (i) design, (ii) fabricating the layout of DBC, (iii) soldering devices (iv) wire bonding and (v) testing244 |

| Fig. 7.22 One leg of the 3 phase power stage, showing parallel devices244                                                                                      |

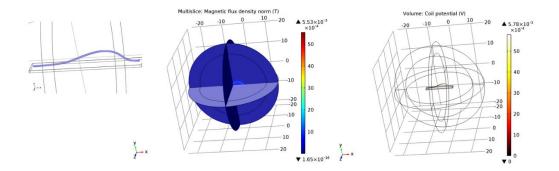

| Fig. 7.23 Parasitic inductance modelling in COMSOL for a single wire bond. $\dots 245$                                                                         |

| Fig. 7.24 Magnetic flux density of each island on the DBC during operation of top or bottom side IGBT/diode                                                    |

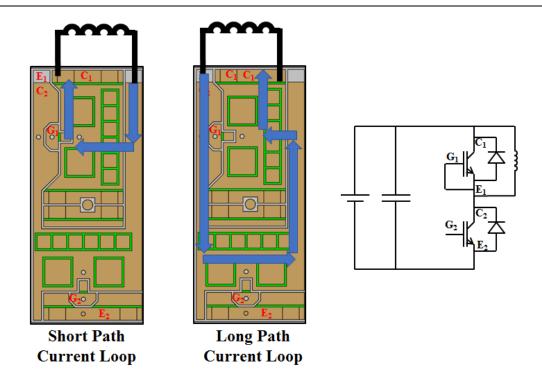

| Fig. 7.25 Circuit configuration for long and short current paths for repetitive clamped inductive switching test                                               |

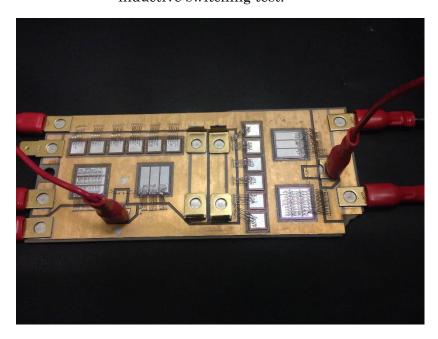

| Fig. 7.26 Test rig setup for repetitive clamped inductive switching test249                                                                                    |

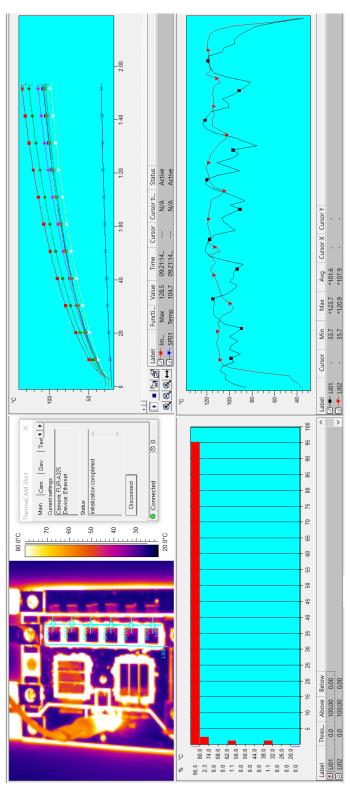

| Fig. 7.27 Temperature imbalance for the long path current loop test250                                                                                         |

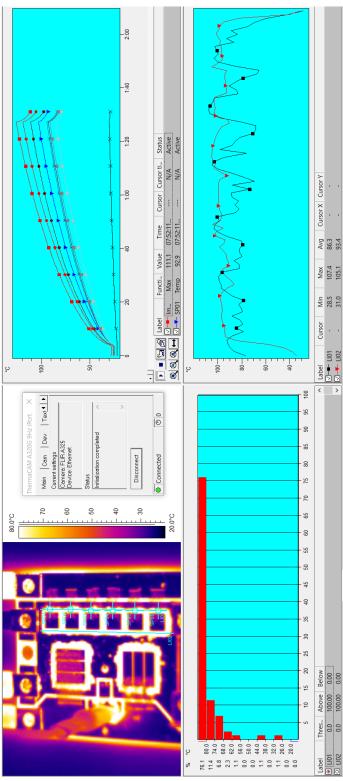

| Fig. 7.28 Temperature imbalance during for the small current loop test251                                                                                      |

| Fig. 7.29 Flip-die and die-up configurations254                                                                                                                |

| Fig. 7.30 Flip die and die up DBC substrate layout design                                                                                                      |

| Fig. 7.31 Bottom side DBC layout design of a 3-phase double sided cooled inverter. 256                                                                         |

| Fig. 7.32 DBC substrate and the area to apply solder mask                                                                                                      |

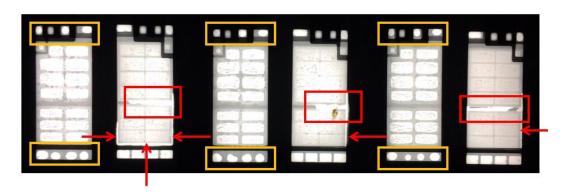

| Fig. 7.33 X-Ray image of the solder layer with 10% smaller stencil size258                                       |

|------------------------------------------------------------------------------------------------------------------|

| Fig. 7.34 X-Ray image of the solder layer with 15% smaller stencil size258                                       |

| Fig. 7.35 X-Ray image of the solder layer with 20% smaller stencil size258                                       |

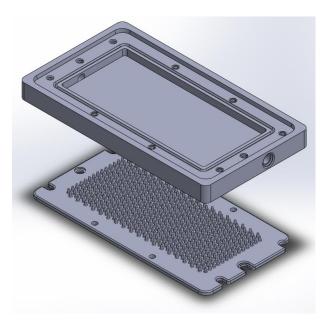

| Fig. 7.36 Bottom side AlSiC baseplate with pin fin and Al cold-plate with water inlet and outlet                 |

| Fig. 7.37 Top side baseplate and coldplate                                                                       |

| Fig. 7.38 Packaging process of the double side cooling power inverter prototype262                               |

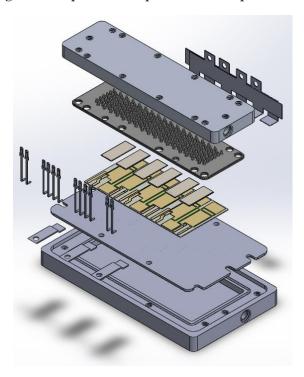

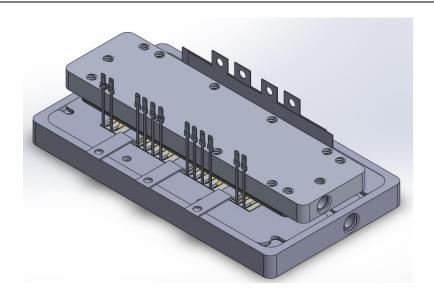

| Fig. 7.39 Assembled power inverter prototype                                                                     |

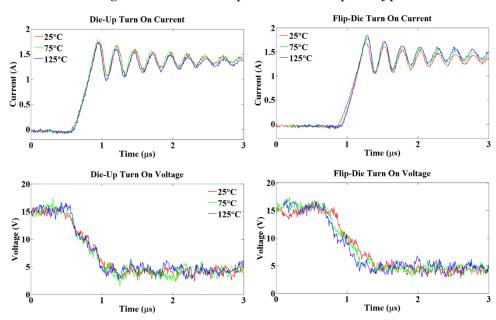

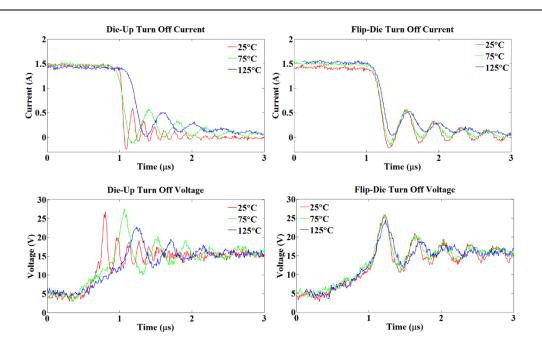

| Fig. 7.40 Turn-on voltage and current waveforms of die-up and flip-die configuration at different temperatures.  |

| Fig. 7.41 Turn-off voltage and current waveforms of die-up and flip-die configuration at different temperatures. |

| Fig. 8.1 Modelling block diagram                                                                                 |

## List of Tables

| Table 2.1 Material properties of different semiconductors                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2 Ceramic DBC substrate material properties                                                                               |

| Table 2.3 Thermal properties of different materials used in power electronics packaging [30]                                      |

| Table 4.1 Thermal resistance and thermal capacitance for devices calculated from the transient thermal impedance curve of devices |

| Table 6.1 Thermal parameters for materials used in power electronics packaging210                                                 |

| Table 6.2 Calculated 5 level Cauer-thermal network for TO247 Package210                                                           |

| Table 7.1 Pitch and width (spacing) between conductors for different thickness of DBC substrate.                                  |

| Table 7.2 Parasitic inductance and resistance of the DBC layout246                                                                |

| Table 7.3 Material properties of AlSiC-9.                                                                                         |

Declaration

This thesis is submitted to the University of Warwick in support of the application

for the degree of Doctor of Philosophy. It has not been submitted in part, or in whole,

for a degree or other qualification at any other University. Parts of this thesis are

published by the author in peer-reviewed research papers listed. Apart from commonly

understood and accepted ideas, or where reference is made to the work of others, the

work described in this thesis is carried out by the author in School of Engineering of

the University of Warwick.

Roozbeh Bonyadi

2012-2016

xiv

To mum and dad.

#### Acknowledgement

I would like to thank my lead PhD supervisor, Prof. Phil Mawby for his invaluable guidance and support throughout my studies. Phil has always been supportive and provided me with useful advices related to my studies and life. I really enjoyed my whole duration of study, our discussions and I always admired your broad knowledge in every topic that we were discussing. The doors of opportunity that has swung open for me in the past few years would not have been possible without you, Phil. Thank you for choosing me to undertake the JLR project, providing me with an international scholarship and being caring like a father.

Next, I would like to thank my second supervisor, Dr. Olayiwola Alatise, whom without none of these papers and publications would be possible. Layi, I really enjoy every minute of talking and discussing physics, semiconductors, motors, all the way to politics and creation of earth with you. I enjoyed every moment that we spent writing equations on the board and finding explanations for every problem we faced. I am truly thankful for your help. You are my role model of success and hardworking and the example of a smart and bright person. I would also like to express my gratitude to Prof. Li Ran for his invaluable technical advice and sharing his broad knowledge with me.

I would like to thank Dr. Alexandros Michaelides for providing me with the opportunity to undertake the project with Jaguar Land Rover and the CASE award scholarship allowance for the very best overseas student. Alex, I would also like to thank you again for choosing me to be part of your team at JLR midway through my PhD studies. None of my papers and patent would be possible without you. I am honoured to be a member of your team and I am very grateful that you trusted, encouraged and tutored me throughout these years. These words are carved in my brain and I will always remember them: "Alex is always right".

I would also like to thank my friends and colleagues, Siavash, Maani, Soheil, Hamid, Ali, Saeed, Ji, Petros, Tian Qu, Fan, Han, Yuan, Jose, Zohreh, all the PEATER group and a much longer list that can't fit here for all the support and happiness that you brought.

In the end, I would like to thank my lovely family and devote this work to all of you. I can't find any word to thank my mom, Manijeh, and my dad, Siamak, for supporting me throughout my life. I am speechless and can't describe how much I love you. You devoted your lives to me without wanting anything in return. The last thing that I can do is to make you happy and proud. I hope that so far I could deliver this small duty and please continue staying next to me healthy and happy. I would also like to thank my sisters, Yeganeh and Roxana for supporting me constantly and caring for me. I would like to thank my brother in law, Aydin, for being there like a true brother whenever I needed him. Last but not least, I would also like to thank my beautiful fiancé, Zarina, for staying next to me in all the happy and sad times and supporting me constantly by encouraging me throughout all these years. I wouldn't be where I am right now if it wasn't for you. I love you all.

#### **Publication List**

- Bonyadi, R.; Alatise, O.; Jahdi, S.; Hu, J.; Ortiz Gonzalez, J.; Ran, L.; Mawby, P., "Compact Electro-Thermal Reliability Modelling and Experimental Characterisation of Bipolar Latch-up in SiC and CoolMOS Power MOSFETs," Power Electronics, IEEE Transactions on, vol. 30, no. 12, pp. 6978-6992, Dec. 2015.

- 2. Jahdi, S.; Alatise, O.; **Bonyadi, R.**; Alexakis, P.; Fisher, C.A.; Ortiz Gonzalez, J.A.; Li Ran; Mawby, P., "An Analysis of the Switching Performance and Robustness of Power MOSFETs Body Diodes: A Technology Evaluation," *Power Electronics, IEEE Transactions on*, vol.30, no.5, pp.2383,2394, May 2015.

- 3. Jahdi, S.; Alatise, O.; Gonzalez, J.A.O.; **Bonyadi, R.**; Ran, L.; Mawby, P., "Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules," in *Industrial Electronics, IEEE Transaction on*, vol. 63, no. 2, pp. 849-863, Feb. 2016.

- 4. Hu, J.; Alatise, O.; Ortiz Gonzalez, J.; **Bonyadi, R.**; Ran, L.; Mawby, P.A., "The Effect of Electrothermal Non-Uniformities on Parallel Connected SiC Power Devices under Unclamped and Clamped Inductive Switching," in *Power Electronics, IEEE Transaction on*, vol. 31, no. 6, pp. 4526-4535, June 2016.

- 5. Hu, J.; Alatise, O.; Gonzalez, J.A.O.; **Bonyadi, R.**; Alexakis, P.; Ran, L.; Mawby, P., "Robustness and Balancing of Parallel Connected Power Devices: SiC vs. CoolMOS," in *Industrial Electronics, IEEE Transactions on*, vol. 63, no. 4, pp. 2092-2102, April 2016.

- 6. **Bonyadi, R.**; Alatise, O.; Jahdi, S.; Hu, J.; Evans, L.; Mawby, P.A., "Investigating the reliability of SiC MOSFET body diodes using Fourier series modelling," *Energy Conversion Congress and Exposition (ECCE)*, 2014 IEEE, pp.443,448, 14-18 Sept. 2014.

- 7. **Bonyadi, R.**; Alatise, O.; Jahdi, S.; Gonzalez, J.O.; Ran, L.; Michaelides, A.; Mawby, P.A., "Physics Based Modelling and Experimental Characterisation of Parasitic Turn-On in IGBTs," in *Power Electronics and Applications (EPE'15 ECCE-Europe)*, 2015 17th European Conference on, pp.1-9, 8-10 Sept. 2015.

- 8. **Bonyadi, R.**; Alatise, O.; Jahdi, S.; Gonzalez, J.O.; Ran, L.; Mawby, P.A., "Modeling of Temperature Dependent Parasitic Gate Turn-On in Silicon

- IGBTs," in *Power Electronics and ECCE Asia (ICPE-ECCE Asia), 2015, 9th International Conference on*, pp.560-566, 1-5 June 2015.

- 9. **Bonyadi, R**; Alatise, O; Hu, J; Davletzhanova, Z; Bonyadi, Y; Ortiz-Gonzalez, J; Ran, L; Mawby, P.A, "Compact electrothermal models for unbalanced parallel conducting Si-IGBTs," *2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Long Beach, CA, 2016, pp. 253-260.

- 10. Bonyadi, Y; Gammon, P. M; Bonyadi, R; Shah, V. A; Fisher, C.A; Martin, D. M; Mawby, P. A, "Characterization of 4H-SiC PiN Diodes Formed on Defects Identified by PL Imaging", Materials Science Forum, Vol. 858, pp. 405-409, 2016, DOI: 10.4028/www.scientific.net/MSF.858.405.

- 11. Davletzhanova, Z; Alatise, O; Gonzalez, J. A. O; **Bonyadi, R**; Ran, Li; Mawby, P, "Output harmonic analysis as a potential method of condition monitoring," 8<sup>th</sup> International Conference on Power Electronics, Machines and Drives (PEMD 2016) IET Conference Proceedings, 2016, p. 6.-6., DOI: 10.1049/cp.2016.0266IET.

- 12. Bonyadi, Y.; Gammon, P. M; **Bonyadi, R**; Alatise, O; Hu, J; Hindmarsh. S; Mawby, P.A., "The Impact of Triangular Defects on Electrical Characteristics and Switching Performance of 4H-SiC PiN Diodes," Energy Conversion Congress and Exposition (ECCE), 2016 IEEE, Sept. 2016 (Accepted for presentation).

#### Abstract

The emergence of the hybrid electric vehicle and electric vehicles (HEV and EV) requires the reliability assessment of power electronic devices used in the inverters. This includes the electro-thermal reliability of bipolar devices such as IGBTs and PiN diodes and more recently, the SiC MOSFETs since the SiC technology is not as mature as their bipolar counterparts. This research, in its own capacity, through the use of accurate compact models, investigates the switching performance and characteristics of silicon IGBTs, PiN diodes and SiC MOSFETs. The need for higher power densities and fast device switching causes certain concerns in the performance and terminal characteristics of the converter.

SiC MOSFET is a potential power device for implementing EV drivetrain inverters. One of the major advantages of SiC MOSFET is the possibility of using their body diodes for reverse current conduction, thereby obviating the need for lossy silicon PiN diodes. The primary goal of using SiC MOSFETs is to enable high frequency switching since the significantly lower switching losses coupled with the high dI/dt and dV/dt can increase the power density. This research has investigated and modelled the use of the SiC body diode for current commutation under high dV/dt conditions. Since the body diode is not designed to operate under such conditions, the electrothermal robustness of SiC body diode is investigated by simulating parasitic BJT latch-up that results from hard current commutation under high dV/dt. In a power MOSFET, high switching rates coupled with the drain-body capacitance brings about a displacement current passing through the resistive path of the P-body in the MOSFET structure which creates a voltage at the base of the parasitic BJT within the device. This BJT latch-up under certain thermal conditions is capable of destruction of the device.

Another problem induced by high switching speed is that of the electrical coupling between complementing devices in the same leg of the inverter which is known as crosstalk or parasitic gate turn-on. In this research, the unintentional switching of IGBTs and the resulting short circuit current surge passing through the devices as a consequence of reducing the dead-time as well as increasing the switching rate is investigated and modelled. This is due to the discharge of the Miller capacitance which feeds back a current into the gate of the transistor. The result is that both transistors are switching on in the same phase leg.

The other problem which is addressed in this research is modelling the switching transients of parallel connected IGBTs for the purpose of delivering high current conduction capability. The electrothermal energy balancing between the parallel connected IGBTs is important as the electrothermal variation between the parallel connected devices can cause temperature imbalance, thereby, accelerating the degradation of the power module. This research investigates the variations in the electrical time constants and the thermal time constants between the parallel connected devices and models the switching behaviours.

Lastly, this research has focused on designing and fabricating power modules suitable for EV application and has tried to address methods to improve the electrothermal performance of the device and has investigated the impact of parasitic inductance of the layout on the electrothermal performance of the power module.

#### List of Abbreviations

ADE Ambipolar diffusion equation

BJT Bipolar Junction Transistor

CAE Computer Aided Engineering

CFD Computational Fluid Dynamic

CMOS Complementary Metal Oxide Semiconductor

CSR Charge Storage Region

CTE Coefficient of Thermal Expansion

UAC Undepleted accumulation layer capacitance

DUT Devices under test

ECCE Energy Conversion Congress and Exposition

EDU Electric drive units

EMC Epoxy moulding compound

EV Electric Vehicle

EVB Electric vehicle battery

FEM Finite Element Models

FMEA Failure Mode and Effect Analysis

GaN Gallium Nitride

GTO Gate Turn-Off

HEV Hybrid Electric Vehicle

HV High Voltage

ICE Internal combustion engine

IGBT Insulated Gate Bipolar Transistor

JFET Junction Field Effect Transistors

KVL Kirchhoff's current and voltage laws

LED Light Emitting Diodes

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistors

NPT Non-Punch Through

PHEV Plug-in Hybrid Electric Vehicle

PMSM Permanent magnet synchronous machine

PT Punch Through

RTA Rapid thermal annealing

SiC Silicon Carbide

SOA Safe Operating Area

SPWM Sinusoidal Pulse Width Modulation

SRM Switched reluctance motor

SSM Six Step Mode

SVM Space Vector Modulation

THIPWM Third Harmonic Injection Pulse Width Modulation

VSC Voltage source converters

VSI Voltage source inverter

### List of Symbols

Active die area (cm²)  $\boldsymbol{A}$ BJT base area (cm<sup>2</sup>)  $A_{\scriptscriptstyle B}$  $a_i$ Ratio of intercell area to active die area  $C_{\scriptscriptstyle B}$ Drain-base capacitance of BJT (F)  $C_{DIC}$ Depleted intercell drift region capacitance (F)  $C_{GD}$ Gate-drain capacitance (F)  $C_{ox}$ Oxide capacitance per unit area (Fcm<sup>-2</sup>)  $C_{p}$ Specific heat (W.kg<sup>-1</sup>.K<sup>-1</sup>)  $C_{th}$ Thermal capacitance (J/K) Undepleted accumulation layer capacitance (F) DAmbipolar diffusivity (cm<sup>2</sup>s<sup>-1</sup>)  $D_b$ Diffusion coefficient in the emitter (cm<sup>2</sup>s<sup>-1</sup>)  $D_{e}$ Diffusion coefficient in the base (cm<sup>2</sup>s<sup>-1</sup>)  $D_n$ Electron diffusivity (cm<sup>2</sup>s<sup>-1</sup>)  $D_{p}$ Hole diffusivity (cm<sup>2</sup>s<sup>-1</sup>)  $D_{pH}$ Hole diffusivity in IGBT buffer layer (cm<sup>2</sup>s<sup>-1</sup>) EElectric field (Vcm<sup>-1</sup>)  $E_0$ Impact ionisation coefficient for Göhler/Sigg model (Vcm<sup>-1</sup>)  $E_{01}$ Electric field at anode junction (Vcm<sup>-1</sup>)  $E_{02}$ Electric field at cathode junction (Vcm<sup>-1</sup>)  $E_{\scriptscriptstyle 1}^{'}$ Electric field gradient of anode depletion layer (Vcm<sup>-2</sup>)  $E_{2}^{'}$ Electric field gradient of cathode depletion layer (Vcm<sup>-2</sup>)  $E_{m}$

Electric field at centre boundary during diode punch-through (Vcm<sup>-1</sup>)

- $G_p$  Hole generation rate (cm<sup>-3</sup>s<sup>-1</sup>)

- $h_n$  N+ emitter recombination parameter (cm<sup>4</sup>s<sup>-1</sup>)

- $h_p$  P emitter recombination parameter (cm<sup>4</sup>s<sup>-1</sup>)

- $I_{AK}$  Anode-cathode current (A)

- $I_{CE}$  Collector-emitter current (A)

- $I_{displ}$  Displacement current at anode boundary of charge storage region (A)

- $I_{disp2}$  Displacement current at cathode boundary of charge storage region (A)

- $I_{DS}$  Drain-source current (A)

- *I*<sub>g</sub> Gate terminal current (A)

- $I_{GD}$  Gate-drain current (A)

- $I_{mos}$  MOS channel current (A)

- $I_n$  Electron current (A)

- $I_{n1}$  Electron current at P emitter (anode) boundary of charge storage region (A)

- $I_{n2}$  Electron current at cathode end of charge storage region (A)

- $I_p$  Hole current (A)

- $I_{p1}$  Hole current at P emitter (anode) boundary of charge storage region (A)

- $I_{p2}$  Hole current at cathode end of charge storage region (A)

- J Current density due to electrons and holes ( $cm^2V^{-1}s^{-1}$ )

- $J_{CE}$  Collector-emitter current density (Acm<sup>-2</sup>)

- $J_n$  Electron current density (A.cm<sup>-2</sup>)

- $J_p$  Hole current density (A.cm<sup>-2</sup>)

- k Harmonic index for charge storage region carrier density Fourier series representation

- $K_{\scriptscriptstyle FV}$  Feedback gain relating depletion layer voltage to boundary carrier density (Vcm³)

- $K_p$  MOS transconductance (AV-2)

- $K_{p0}$  MOS Transconductance at room temperature (AV-2)

- $K_{th}$  Thermal conductivity (Wm<sup>-1</sup>K<sup>-1</sup>)

- L Length of inversion layer (cm)

- $L_{\scriptscriptstyle E}$  Emitter length (cm)

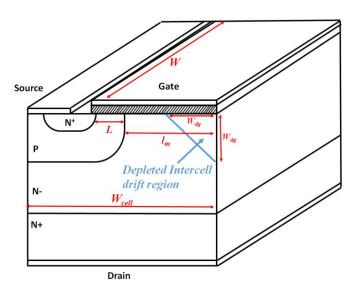

- $l_m$  MOSFET/IGBT intercell half-width ( $\mu$ m)

- M Total number of segments in calculation of drift region voltage drop

- *n* Electron concentration (cm<sup>-3</sup>)

- $N_A$  Acceptor (P-type) doping concentration (cm<sup>-3</sup>)

- $N_B$  Drift region doping N-type concentration (cm<sup>-3</sup>)

- $N_D$  Donor (N-type) doping concentration (cm<sup>-3</sup>)

- $N_E$  Emitter doping (cm<sup>-3</sup>)

- $N_{eff}$  Effective depletion layer carrier density (cm<sup>-3</sup>)

- $N_H$  Buffer layer doping (cm<sup>-3</sup>)

- $n_i$  Intrinsic carrier concentration (cm<sup>-3</sup>)

- *p* Free hole concentration (cm<sup>-3</sup>)

- $p_{b1}$  Carrier concentration at the P-emitter junction

- $p_k$  k-th Fourier series component of charge storage region carrier density profile (cm<sup>-3</sup>)

- $p_{x1}$  Ambipolar carrier density at anode end of CSR (cm<sup>-3</sup>)

- $p_{x2}$  Ambipolar carrier density at cathode end of charge storage region (cm<sup>-3</sup>)

- *q* Unit electron charge ( $\approx 1.6 \times 10^{-19}$ C)

- $Q_{channel}$ Charge in the inversion layer (C)

- $Q_H$  Buffer layer stored hole charge (C)

- $R_p$  Hole recombination rate (cm<sup>-3</sup>s<sup>-1</sup>)

- $R_{pb}$  P-body resistance ( $\Omega$ )

- $R_{th}$  Thermal resistance (K/W)

- Temperature (K)

- $T_0$  Reference temperature ( $\approx 300$ K)

- $t_{ox}$  Oxide thickness (nm)

- $t_r$  Travel time for electrons in the channel (s)

- V Volume (m<sup>3</sup>)

- $V_{ak}$  Anode-Cathode voltage (V)

- $V_{\scriptscriptstyle R}$  Drift region voltage drop (V)

- $V_d$  Depletion voltage (V)

- $V_{d1}$  Depletion voltage at anode end of the charge storage region (V)

- $V_{d2}$  Voltage across depletion layer at cathode end of charge storage region (V)

- $V_{DS}$  Drain-source voltage (V)

- $V_{GS}$  Gate-source voltage (V)

- $V_{j2}$  Forward N<sup>-</sup>N<sup>+</sup> junction voltage at cathode end of charge storage region (V)

- $v_{sat}$  Carrier saturation velocity (cms<sup>-1</sup>)

- $V_{\scriptscriptstyle T}$  Thermal voltage (V)

- $V_{th}$  Threshold voltage (V)

- $V_{th0}$  Threshold voltage at room temperature (V)

- W Width of inversion layer (cm)

- $W_B$  Carrier storage region width (µm)

- $W_{cell}$  MOS cell width (µm)

- $W_{d1}$  Width of the depletion layer at anode end of the charge storage region (µm)

- $W_{dg}$  Width of the depletion region (µm)

- $W_H$  IGBT buffer layer width ( $\mu$ m)

- $x_1$  Boundary position at anode end of charge storage region ( $\mu$ m)

- $x_2$  Boundary position at cathode end of charge storage region ( $\mu$ m)

- $X_d$  Total depletion width (cm)

- $X_n$  Depletion width in N-type (cm)

- $x_p$  Depletion width in P-type (cm)

- $Z_{th}$  Thermal impedance (K/W)

- $\alpha_F$  Forward transfer ratio (typically  $\approx 0.98$ )

- $\mu_{i,\text{max}}$  Maximum mobility of electron/hole (cm<sup>2</sup>V-1s-1)

- $\mu_n$  Electron mobility (cm<sup>2</sup>V-1s-1)

- $\mu_p$  Free hole mobility (cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>)

- $\frac{\partial p}{\partial x}$  Gradient of free hole carrier density (cm<sup>-4</sup>)

- $\rho$  Density (kg.m<sup>-3</sup>)

- au High-level carrier lifetime (s)

- $\tau_{HL}$  High-level carrier lifetime (s)

- $\tau_{HL0}$  High-level carrier lifetime at room temperature (s)

- $\tau_n$  Electron lifetime (s)

- $\tau_p$  Hole lifetime (s)

- ε Permittivity (Fcm<sup>-1</sup>)

- $\mathcal{E}_{ox}$  Silicon oxide permittivity (Fcm<sup>-1</sup>)

- $\mathcal{E}_s$  Semiconductor permittivity (Fcm<sup>-1</sup>)

- $\mathcal{E}_{si}$  Silicon permittivity (Fcm<sup>-1</sup>)

- $\Phi_{bi}$  Built-in potential (V)

- $\phi_F$  Bulk reference potential (V)

Chapter

Introduction

1

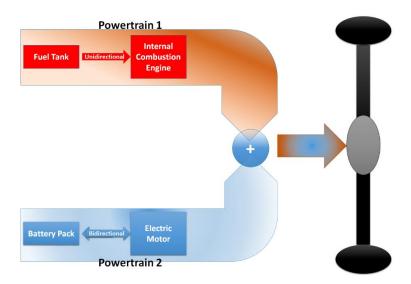

In the recent years, due to the significant increase of the greenhouse gas emission, global warming has become a major concern with governments across the world. This is expected to cause a rise of the sea level and cause the glaciers melt which will have huge impact on the life and habitat of all animals and human beings. Most of the technologically advanced countries around the globe have started to pay a close attention to this environmental problem and recently president Obama, of the United States, has addressed this issue by proposing an action plan to mitigate the worst effects of global warming [1, 2]. Consequently, the United States has developed a challenging plan to address the threat of climate change and are taking a leading role in combating CO<sub>2</sub> emissions especially from power plants [3]. The UK government established the world's first legally binding climate change target in 2008 with the Climate Change Act and aims to reduce the UK's greenhouse gas emissions by at least 80% by 2050 [4, 5].

The European parliament has also voted to revise EU rules on greenhouse gas emissions in general. Specifically, for the automotive sector, CO<sub>2</sub> emission limits for passenger cars for 2020 aim to ensure that the average new car produced will emit no more than 95 g CO<sub>2</sub>/km [6]. This means that the average reduction in fuel consumption needs to be reduced by 27 per cent which is the toughest challenge that the major car manufacturers are facing. The electrification of transportation is widely recognised as a critical step in decarbonisation of modern industrial societies for the purpose of mitigating green-house gas emissions as well as ensuring energy security. Replacing the internal combustion engine with an electrical machine is a critical step in this direction.

The reduction of CO<sub>2</sub> emission is a challenging task as the demand for energy is increasing rapidly and the electricity sector is the major responsible source of total global CO<sub>2</sub> emissions. One of the ways to meet the UK greenhouse emission reduction targets is using renewable energy in form of wind turbine energy harvesting and PV solar cells. Moreover, building HVDC lines between UK and EU enables transcontinental energy exchange in a more efficient way and hence, can reduce the CO<sub>2</sub> emissions. The second responsible source after electricity sector is transportation sector and specifically automotive industry which is the main focus of this thesis.

The EU has introduced the new fuel economy test which is called "World Harmonised Light Duty Vehicle Test Procedure", also known as WLTP, which aims to represent real-world driving conditions and has been developed from a database of

460,000 miles of global driving data. In order for a car to be able to pass the WLTP drive cycle, it needs to have a high peak power and quick acceleration for short periods of time and at the same time the size of the internal combustion engine (ICE) needs to be reduced in order to reduce the CO<sub>2</sub> emission [7]. Moreover, to be able to save fuel and increase the efficiency of the car, the engine needs to work at optimal operating points and the engine needs to operate at low speed. One of the methods that contributes in the reduction of the CO<sub>2</sub> emissions is deploying a regenerative braking system. The regenerative braking system will increase the fuel efficiency of a vehicle, however, these are not enough to satisfy the new WLTP fuel economy test and new technologies that show potential for decreasing energy use and carbon emission needs to be assessed. Among these new technologies which can be used in transportation, Hybrid Electric Vehicle (HEV), Plug-in Hybrid Electric Vehicle (PHEV) and Electric Vehicle (EV may also referred to as BEV or battery electric vehicles) can be named.

An electric power train increases the efficiency of the system and reduces the need of larger internal combustion engine (ICE). It also can provide high peaks of power and quick acceleration from zero speed which significantly contributes to reduction of fuel consumption. Consequently, due to the presence of the electric powertrain, these vehicles have better fuel economy and better overall performance than the conventional vehicles [8]. The Toyota Prius is an example and is the world's best-selling HEV and Toyota has over seven million global hybrid sales. PHEVs are the next generation of HEVs which can offer advantages over HEV including lower fuel consumption and the ability to charge the batteries from electric gird from any typical home outlet. This can

significantly extend the electrical range of the car and reduce the emissions as well. In general, the larger the battery pack, the further these vehicles will run in electric mode, after which the vehicle swaps to the ICE. If PHEVs are adapted by a large population, additional benefits will arise: for example, the batteries of these cars when they are plugged into the gird can be used as local energy storage when power demand at the grid is high.

# 1.1 Introduction to the EV Power Converter

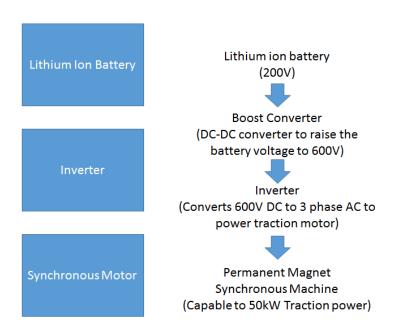

Electrical machines convert electrical energy into mechanical energy using a rotating electromagnetic field that generates torque. This rotating electromagnetic field is generated by a 3-phase DC-to-AC voltage source inverter (VSI) powered by a DC link. Using a vector control, the torque and speed characteristics of the machine can be controlled from a user interface determined by the drive cycle.

Modern electric vehicle architectures are comprised of a DC battery (which is typically a lithium ion battery), a DC-DC boost converter required to step the battery voltage up, a 3 phase voltage source inverter and an electric machine for traction. Modern electric drivetrains are also capable of regenerative breaking, which simply means that vehicle retardation is initiated not by converting mechanical energy into heat via friction, but instead by running the motor as a generator. The AC power generated by the traction motor is then rectified by the converter and used to re-charge

the battery thereby improving the energy efficiency of the overall system. Fig. 1.1 shows a typical example of such a drivetrain from Toyota. In this drivetrain schematic, the battery voltage is 200V, the boost-converter output voltage is 650V and the maximum power deliverable by the machine is 50kW motoring and 30kW generating.

Fig. 1.1 Power conversion system for Hybrid Electric and Electric Vehicles from Toyota Prius.

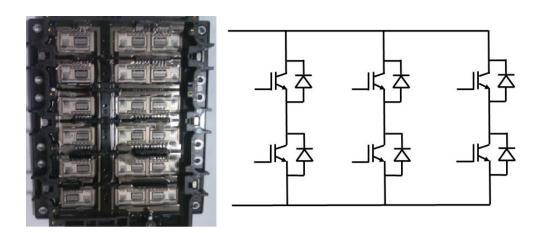

The power electronic converter is critical to the efficiency and power density of the electric drivetrain system. The converter is voltage sourced since the DC side voltage is constant and the DC side current determines the direction of power flow. It is also a self-commutated converter since the phase-to-phase commutation of the current within the converter is determined by the switching of the power electronic devices. The simplest VSI is a 2 level converter comprised of 6 power devices each with an antiparallel diode. This converter has 8 possible switching states with 2 being redundant

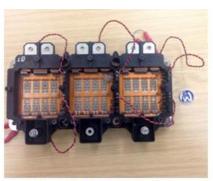

and 6 being active. The control strategy of the converter can be optimised to enable reduced power conversion losses. A typical power module is shown in Fig. 1.2 where a number of transistors and diodes can be seen on a DBC substrate.

Fig. 1.2 Picture of Toyota Prius IGBT inverter module and a circuit schematic taken at Warwick.

### 1.2 Power Devices for EV Drivetrains

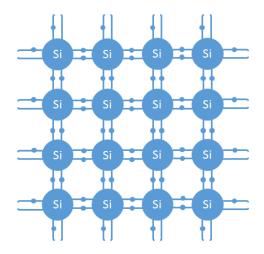

Currently, these power electronic converters are implemented using silicon insulated gate bipolar transistors (IGBTs) for electrical power inversion (DC to AC) and silicon PiN diodes for rectification (AC to DC). Silicon IGBTs are the technology of choice because the voltage levels required for power conversion are too high for silicon power MOSFETs. MOSFETs have more desirable characteristics than IGBTs; however, the on-state losses are prohibitive in silicon at voltages exceeding 200V.

The power electronic devices are not only limited to the motor control and electric vehicles, they are also used in a very wide range of applications such as wind turbine

and photovoltaic solar cells, high voltage DC transmission lines (HVDC), traction of trains and propulsion system of marine and in aviation sector.

To date, all major EV and HEV manufacturers use silicon IGBT and PiN diodes in their power electronic converters; however, the blocking voltage, switching frequency and current rating of these devices are reaching their limits and emergence of SiC power devices has generated interest for their use in EV drivetrains. Toyota has announced that they will start using this material by 2020. The reason is predicted on the need for high power densities for energy efficient ultra-compact drivetrains. Increasing the switching frequency of the power converter can enable this by reducing the size of the passive components that accompany the power converters. However, the recombination and reverse recovery currents of IGBTs and PiN diodes limit the maximum switching frequency. Hence, as a result, the use of wide bandgap unipolar devices like SiC MOSFETs and Schottky diodes is an attractive proposition for EV manufacturers.

#### 1.3 Rationale for Current Work

The work presented in this thesis is mainly focused on modelling and parameterising electro-thermal failure modes in power electronic devices within an inverter which may cause thermal runaway and destruction of the devices or can cause long term reliability issues such as solder delamination or wire bond lift-off which can reduce the lifetime of the power inverter. Also, SiC devices are going to be adopted by

the automotive industry, this work additionally studies some of the reliability aspects of these devices in an inverter.

Physics-based modelling of bipolar power electronic devices such as IGBTs and PiN diodes have been carried out in several works [9]. The focus of previous research was the creation of fast modelling tools to simulate the switching transient of power electronic devices. However, these models lack the transient thermal behaviour of the device and assume a quasi-static temperature throughout the simulation. Moreover, these models were often used to simulate single turn-on and turn-off transients of the devices. 3D heat flow models which can accurately predict the temperature of the packaging of the device has been developed which are based on Fourier series reconstruction of ambipolar diffusion equation of heat transfer in the material [10]. However, these models are very complicated and they cannot be integrated with fast converter simulator such as PLECS which consider ideal switching of the devices and can supply the heat losses from the defined power losses look up tables.

In this work we employ accurate compact models, which describe the switching performance and characteristics of silicon IGBTs and PiN diodes, as well as SiC MOSFETs for EV drivetrains. The desire for higher power densities makes device switching much more critical. The models developed here are a key tool in investigating the associated problems which will be described later in this thesis.

Increasing the power density means that switching speeds will need to increase, allowing passive component sizes to be reduced. This places much higher strain on the power devices, which will lead to reliability issues. Hence, it is critical to be able to

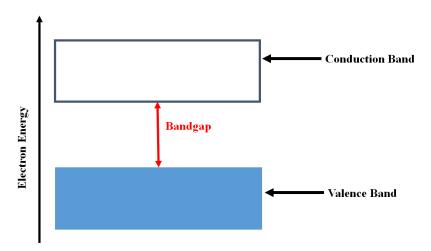

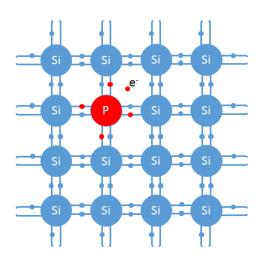

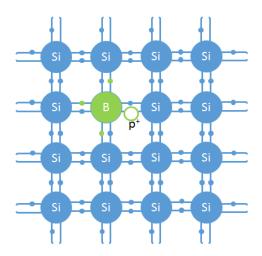

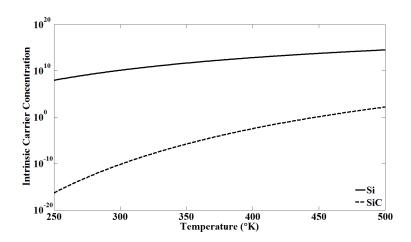

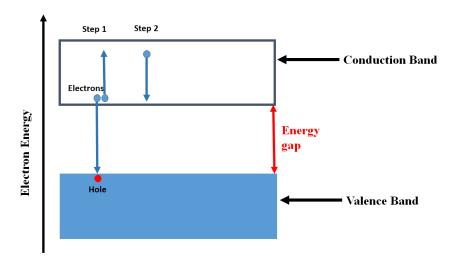

accurately model both the electrical and thermal behaviour of the full converter including the power devices and the cooling system and understand the failure mechanisms.