University of Warwick institutional repository: http://go.warwick.ac.uk/wrap This paper is made available online in accordance with publisher policies. Please scroll down to view the document itself. Please refer to the repository record for this item and our policy information available from the repository home page for further information.

To see the final version of this paper please visit the publisher's website. Access to the published version may require a subscription.

Author(s): J. Parsons, E. H. C. Parker, D. R. Leadley, T. J. Grasby and A. D. Capewell

Article Title: Misfit strain relaxation and dislocation formation in

supercritical strained silicon on virtual substrates

Year of publication: 2007

Link to published version: http://dx.doi.org/ 10.1063/1.2769751

Publisher statement: None

## Misfit strain relaxation and dislocation formation in supercritical strained silicon on virtual substrates

J. Parsons, a) E. H. C. Parker, D. R. Leadley, and T. J. Grasby *University of Warwick, Coventry CV4 7AL, United Kingdom*

## A. D. Capewell

AdvanceSis Ltd., Sir William Lyons Road, Coventry CV4 7EZ, United Kingdom

(Received 29 March 2007; accepted 17 July 2007; published online 10 August 2007)

Relaxation of strained silicon on 20% linear graded virtual substrates was quantified using high resolution x-ray diffraction and a defect etching technique. The thickness of strained silicon was varied between 10 and 180 nm. Relaxation was observed in layers below the critical thickness but increased to only 2% relaxation in the thickest layers even with annealings up to 950 °C. Cross-sectional transmission electron microscopy revealed stacking faults present in layers thicker than 25 nm, and nucleated 90° Shockley partial dislocations forming microtwins in the thickest layer. These features are implicated in the impediment of the relaxation process. © 2007 American Institute of Physics. [DOI: 10.1063/1.2769751]

Tensile strained silicon used in the channel region of transistors has been demonstrated to produce an improvement in the charge carrier transport properties above that of bulk silicon. The most widely used method of fabricating globally strained silicon for device processing employs SiGe virtual substrates as growth templates. In order to be acceptable for use in industry, strained layers must ideally be defect free and maintain strain during device processing.

Due to relaxation processes of the virtual substrate, threading dislocations are grown into the strained silicon layer. Relaxation of the layer will proceed by the strain-induced glide of these threading dislocations, forming misfit dislocations at the strained interface. The critical thickness of strained silicon is therefore described by the Matthews and Blakeslee mechanical equilibrium theory for relaxation via preexisting dislocations. For the case of silicon on 20% Ge content virtual substrates, the critical thickness is approximately 13 nm.

Linearly graded virtual substrates of 20% Ge composition were grown using low pressure chemical vapor deposition. The SiGe was graded at a rate of 10%  $\mu$ m<sup>-1</sup> with a 2  $\mu$ m final constant composition layer. Each virtual substrate was capped with strained silicon in the range of 10–180 nm at 700 °C. An accurate measurement of the thickness of the strained silicon layers was obtained by cross-sectional transmission electron microscopy (XTEM).

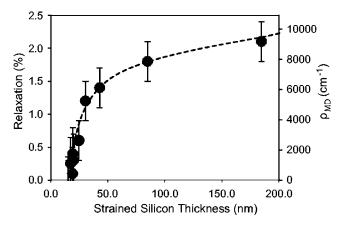

Reciprocal space maps using high resolution x-ray diffraction (HRXRD) around the (224) and (004) reflections were employed to ascertain the relaxation of the strained silicon layers. The relaxation of the final constant composition layer of the virtual substrates and their exact Ge contents were also determined, which dictates the amount of strain the strained silicon layers are subjected to. The results of the strained silicon relaxation are shown in Fig. 1. The relaxation is shown to saturate at around 2%, and is overall very low, compared to the relaxation of compressively strained SiGe layers under the same degree of strain.<sup>4</sup>

HRXRD reciprocal space maps display peak broadening of the strained silicon peak due to mosaicity<sup>5</sup> caused by the

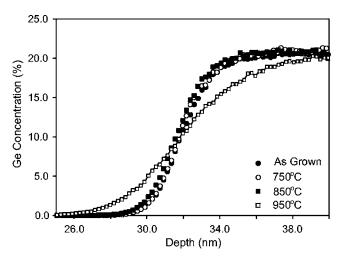

Annealing of strained silicon layers is known to induce Ge diffusion from the virtual substrate, <sup>6</sup> which will reduce its thickness. In order to determine a suitable range of temperatures over which to conduct annealings, secondary ion mass spectroscopy (SIMS) performed a 32 nm strained silicon layer in the as-grown state and after it had been subjected to annealings for 1 h at 750, 850, and 950 °C (Fig. 2). The Ge concentration gradient into the strained silicon layer does not deviate much from the as-grown state for the 750 and 850 °C annealings. Relaxation measurements performed using these annealing conditions assumed the layer thickness to be unchanged.

FIG. 1. Measured relaxation of strained silicon layers using HRXRD from 15 to 180 nm.

presence of misfit dislocations at the strained silicon interface, which warp the diffraction planes. The effect is more pronounced in thicker samples, where the misfit dislocation density (MDD) is greater. Peak broadening limits the accuracy for determining strain (this gives the error bars in Fig. 1). For the thinner strained silicon layers, detectable x-ray intensities are close to the background noise level, making resolution of the peak even more prone to error. Scans were conducted over a 22 h period to maximize the signal-to-noise ratio, but the technique still only yields sufficient x-ray intensity for layers thicker than 15 nm.

a) Electronic mail: j.parsons@warwick.ac.uk

FIG. 2. SIMS profile for a 32 nm strained silicon layer in the as-grown state, and annealed at 750, 850, and 950  $^{\circ}C$  for 1 h.

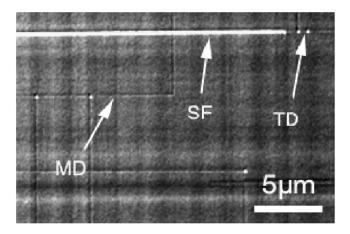

Misfit dislocations at the strained silicon/virtual substrate interface were revealed with a dilute Schimmel etchant. The etched surface could then be imaged using a differential interference contrast microscope which images an area of  $75\times100~\mu m$ . The etch rate was found to be 5 nm s $^{-1}$  in silicon layers and 20 nm s $^{-1}$  in 20% SiGe layers from step measurements. Each sample was exposed to the etchant for 10~s to reveal dislocations at the strained interface and not from deeper in the structure. Figure 3 shows a magnified section of a typical etch image, revealing the additional presence of extended stacking faults in the layers.

The total plastic strain relief  $\delta$  in an (etched) image area can be determined by measuring the misfit dislocation line density  $\rho_{\rm MD}$  (total length of misfit dislocations per unit area). For strained silicon, dislocations are typically of 60° type. Relaxation is therefore given by 9

$$\delta = \frac{a_{\rm Si}}{2\sqrt{2}}\rho_{\rm MD},\tag{1}$$

where  $a_{si}$  is the lattice constant of bulk Si.

In materials under tensile strain, it is known that strain can dissociate 60° perfect dislocations into 90° and 30° Shockley partial dislocations. <sup>10</sup> For sufficiently large strain, the 90° partial will break away from the 30°, creating an

FIG. 3. Close-up of a typical etch image from a 20 nm strained silicon layer, showing misfit and threading dislocations and extended stacking faults.

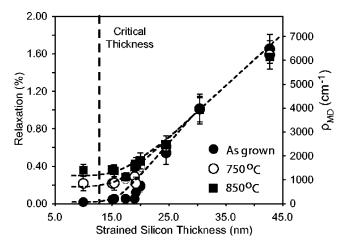

FIG. 4. Strained silicon relaxation variation with thickness and anneal. Lines are for guidance only. Errors are determined by standard deviation of the averaged results.

adjoining stacking fault. As the 90° partial leads, the relaxation of the line density of stacking faults  $\rho_{SF}$  in the considered area is given by

$$\delta = \frac{a_{\rm Si}}{3\sqrt{2}}\rho_{\rm SF}.\tag{2}$$

HRXRD results for the residual strained state of the underlying virtual substrate and its exact Ge fraction gives the maximum amount of strain each silicon layer is subjected to, allowing  $\delta$  to be expressed as a percentage.

The MDD of each etched sample was determined by measuring the total length of misfit dislocations in 75  $\times\,100~\mu m$  image areas and averaging over ten different images randomly taken from the sample surface. Using this data combined with HRXRD measurements on the virtual substrate composition and relaxation, the relaxation of the strained silicon could be determined as a function of thickness using Eqs. (1) and (2) (Fig. 4). This analysis was performed on each sample before and after annealing at 750 and 850 °C for 1 h in nitrogen ambient.

The threading dislocation density (TDD) was evaluated to be  $2(\pm 1) \times 10^5$  cm<sup>-2</sup> for all the layers up to 20 nm. Stacking fault densities (SFD) remained at  $5(\pm 1)$  cm<sup>-1</sup> for thicknesses up to 20 nm, and increased sharply to  $400(\pm 30)$  cm<sup>-1</sup> as the thickness exceeded 25 nm. The increase in SFD was accompanied by an expected rise in TDD, but only to  $3(\pm 1) \times 10^5$  cm<sup>-2</sup>. No increases in TDD or SFD were observed after annealing.

Defect etch analysis was found to be useful only for layers up to 50 nm thick. Thicker layers exhibited a rapid rise in SFD, which made the accurate assessment of TDD and relaxation impossible. The stacking fault trenches become wider as the layer gets thicker, which increases the likelihood of these broader features masking other dislocation structures. This has profound implications for the material quality of thicker layers; as such a rise in SFD is accompanied by an increase in TDD.

Misfit dislocations (and low levels of relaxation) are observed even below the critical thickness, an anomaly that has been noted previously. As expected, the annealing process creates misfit dislocation segments by initiating glide of threading dislocations. This effect seems to be more pronounced in the thinner layers; samples below 20 nm show a ALB license or convigint; see http://apl.gip.org/apl/convigints.

FIG. 5. Cross-sectional TEM image of a 180 nm strained silicon layer showing (a) a stacking fault and (b) a microtwin. Nucleated 90° Shockley partial dislocations are arrowed.

clear increase in relaxation with increasing annealing temperature. Minimal increases in relaxation in layers thicker than 20 nm are observed after annealing.

The overall relaxation implied by defect etching agrees to within the experimental uncertainty of the HRXRD results (Fig. 1). An explanation for the apparently limited relaxation has been offered by Freund through a mechanism of dislocation blocking where the glide of threading dislocations is impeded by preexisting orthogonal misfit dislocations. Studies conducted into dislocation blocking have been mostly confined to compressively strained SiGe/Si heteroepitaxy, where relaxation is observed to progress to a much higher degree. There is evidently a difference in the relaxation behavior between the compressive and tensile strained cases. It is thought that extended stacking faults, which only form in layers under tensile strain, play a much larger role in dislocation blocking than misfit dislocations, leading to lower levels of relaxation.

XTEM analysis confirms the presence of stacking faults in the strained silicon layers (Fig. 5). In the 180 nm layer microtwins were also observed, which can form in tensile strained layers when the strain energy is sufficiently large. <sup>13</sup> 90° partial dislocations nucleate from the surface and glide as half-loops to the strained interface. The nucleation of a

second 90° partial dislocation on the same glide plane will repel the initial partial dislocation into the virtual substrate. Additional nucleation events will force other partial dislocations deeper into the structure, forming a microtwin.

The existence of microtwins in the 180 nm layer shows that the strain is no longer being sufficiently relieved by the glide of preexisting threading dislocations, and higher energy dislocation nucleation processes occur. This trend is expected to increase as the layers become thicker, with the eventual nucleation of perfect 60° dislocations around the critical thickness derived by People and Bean. 14

In conclusion, strained silicon layers on virtual substrates many times the critical thickness have been shown to exhibit limited levels of relaxation, even after high temperature annealing. The possibility of stacking faults impeding dislocation glide in thicker layers is offered as an explanation for the apparent disparity between relaxation of compressive and tensile strained layers, which will be subject to further study. Despite the low levels of relaxation and TDD, the rapid increase in SFD and nucleation of microtwins in thicker layers may compromise the performance of electronic devices.

<sup>1</sup>D. J. Paul, Adv. Mater. (Weinheim, Ger.) 11, 191 (1999).

<sup>2</sup>D. Hull and D. J. Bacon, *Introduction to Dislocations*, 4th ed. (Butterworth-Heinemann, London, 2002), p. 122.

<sup>3</sup>J. W. Matthews and A. E. Blakeslee, J. Cryst. Growth 27, 118 (1974).

<sup>4</sup>D. C. Houghton, J. Appl. Phys. **70**, 2136 (1991).

<sup>5</sup>M. Erdtmann and T. A. Langdo, J. Mater. Sci.: Mater. Electron. **17**, 137 (2006).

<sup>6</sup>N. Sugii, J. Appl. Phys. **89**, 6459 (2001).

<sup>7</sup>V. D. Archer, J. Electrochem. Soc. **129**, 2074 (1982).

<sup>8</sup>K. R. Bray, W. Zhao, L. Kordas, R. Wise, McD. Robinson, and G. Rozgonyi, J. Electrochem. Soc. 152, C310 (2005).

S. B. Samavedam, W. J. Taylor, J. M. Grant, J. A. Smith, P. J. Tobin, A. Dip, A. M. Philips, and R. Liu, J. Vac. Sci. Technol. B 17, 1424 (1999).

P. M. J. Marée, J. C. Barbour, J. F. van der Veen, K. L. Kavanagh,

C. W. T. Bulle-Lieuwma, and M. P. A. Viegers, J. Appl. Phys. **62**, 4413 (1987).

<sup>11</sup>L. B. Freund, J. Mech. Phys. Solids **38**, 657 (1990).

<sup>12</sup>E. A. Stach, R. Hull, R. M. Tromp, F. M. Ross, M. C. Reuter, and J. C. Bean, Philos. Mag. A 80, 2159 (2000).

<sup>13</sup>M. L. Lee, D. A. Antoniadis, and E. A. Fitzgerald, Thin Solid Films 508, 136 (2006)

<sup>14</sup>R. People and J. C. Bean, Appl. Phys. Lett. **47**, 322 (1985).