# A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/97339

# **Copyright and reuse:**

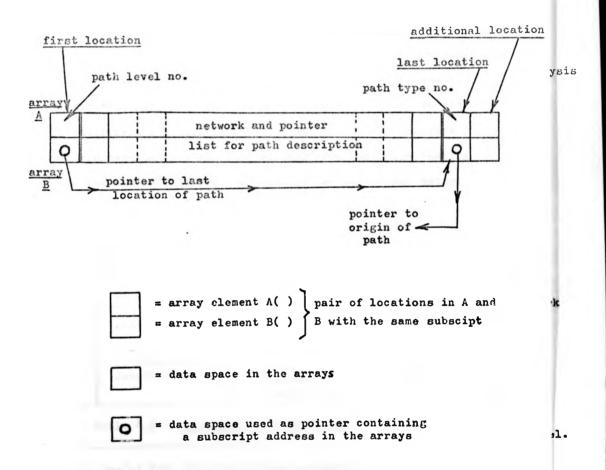

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

Attention is drawn to the fact that the copyright of this thesis rests with its author.

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the author's prior written consent.

D 18344/77 \*

VOII

Harchent, Bg

pp 392

Folded Pages

Interactive Computer Programs

for the

Computer Aided Design

of

Linear Microwave Circuits

Author Brian G. Marchent, B.Sc. (Hons.)

> A thesis submitted at the University of Warwick for the degree of Doctor of Philosophy.

Date: July 1973

and almost any microwave circuit could be handled by the method of analysis used in this program.

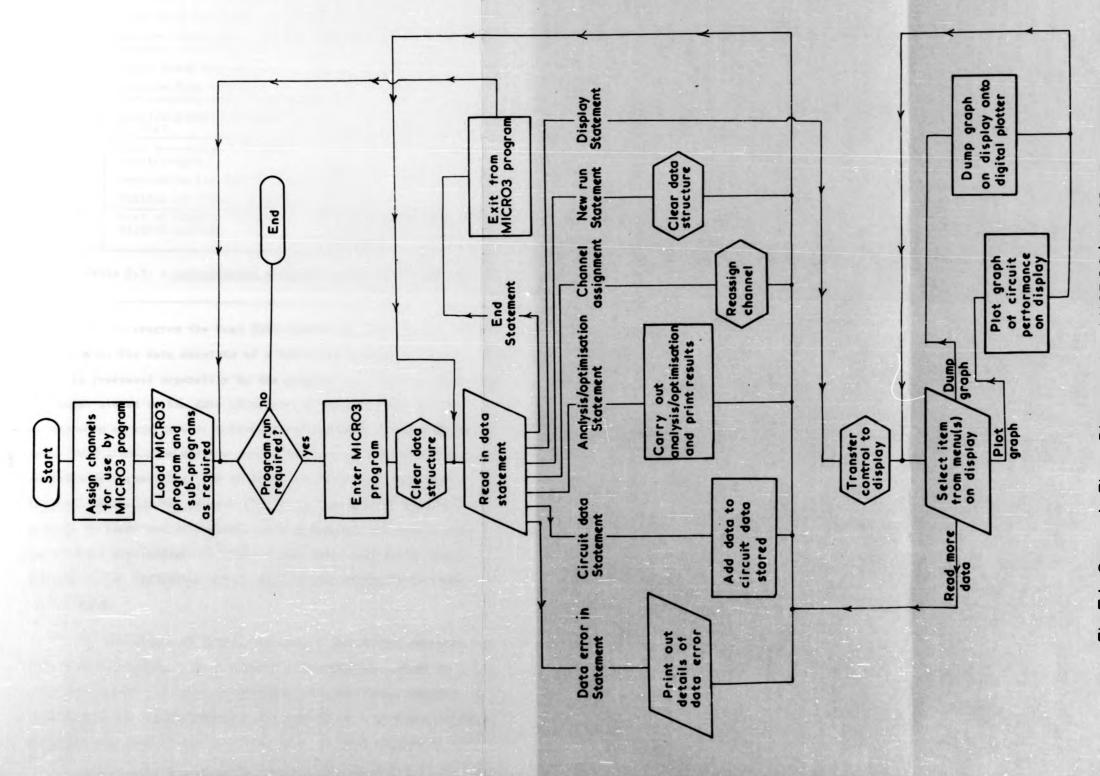

buring the development of the programs, as each new program was developed, more facilities were included for the interactive on-line use of the programs. In the MICRO3 program a list processing approach to the data structure in the program and a full syntactical analysis of the data was included. This made it possible to generate very complex data structures in the program thus making the program ideal for interactive on-line use on a computer. The data for this program was more like a programming language than normal data and any data error could be correct on-line during the run of the program. The program could be used on batch processing, on a remote teletype interactively or with a graphical display to display the results of an analysis in graphical form.

An investigation into the equations describing microwave components and optimisation techniques was carried out. The MICRO3 program was prepared for these facilities but there was not sufficient time to include these facilities completely.

# Preface

the control of the co

representative and a second continued of the second continued co

The idea for the research work cont led in this Ph. D. thesis originated from a suggestion to the author by Mr. M.K. McPhun at the University of Warwick in November 1968 that research work in the field of the Computer Aided Design of Microwave Circuits would be a very useful research topic for a Ph. D. thesis. The research work on this topic started in May 1969 when the author started working with Microwave Associated Ltd., Luton whilst waiting for a Science Research Council grant to start in October 1969. Then a move was made to the School of Engineering Science at the University of Warwick where the main part of the research work was carried out up to October 1972. Also in February 1970 the Science Research Council grant was changed to an industrial studentship grant between the Science Research Council and Redac Software Ltd.. The writing of this thesis was completed in the author's spare time whilst working with Redac Software Ltd., Tewkesbury after October 1972.

At Microwave Associates Ltd., Luton experience was obtained in the theorectical design of microwave integrated circuits.

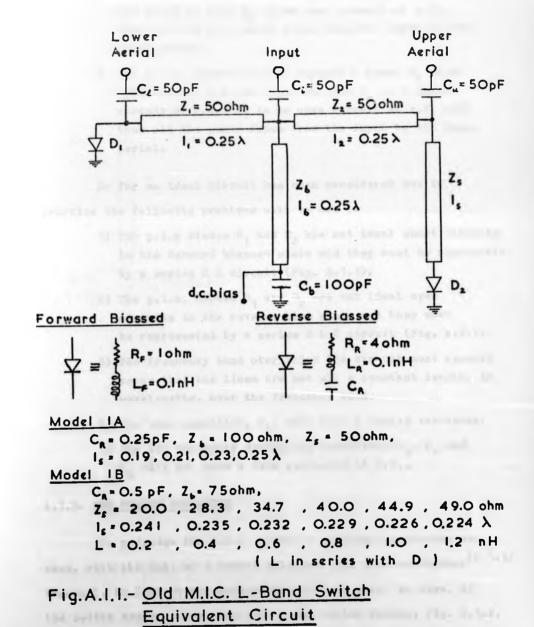

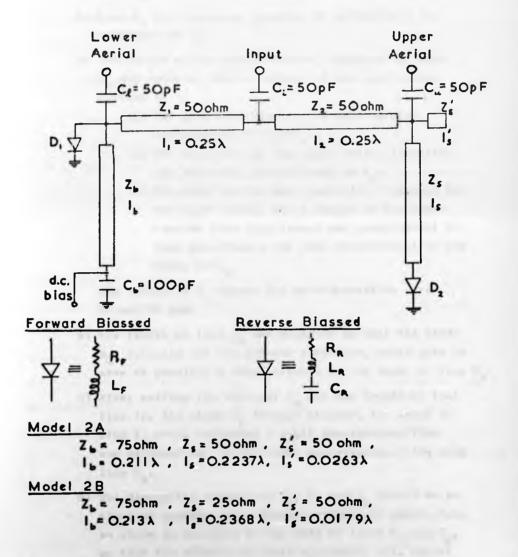

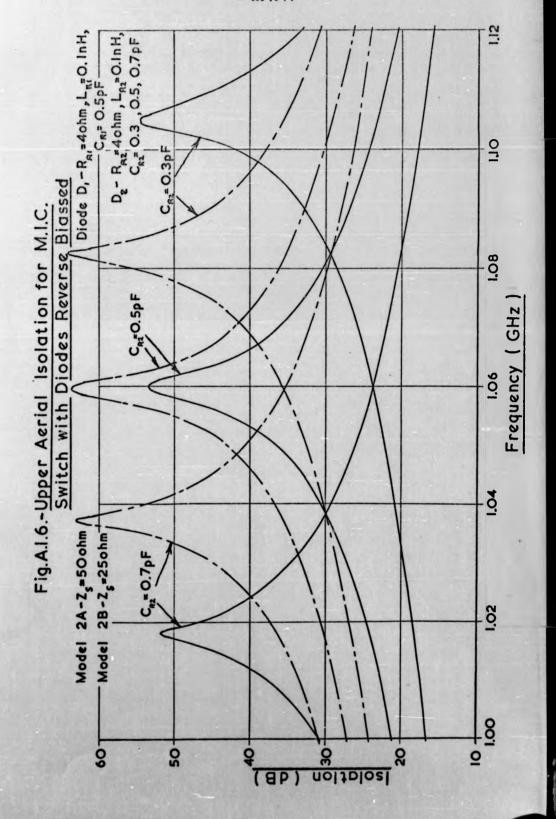

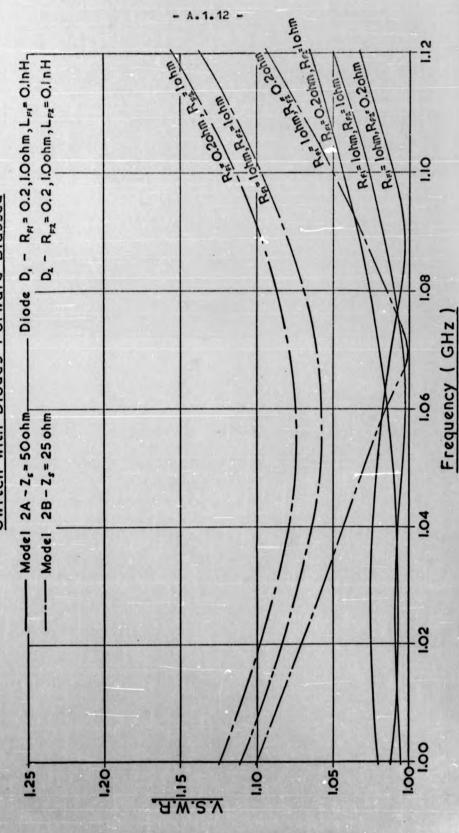

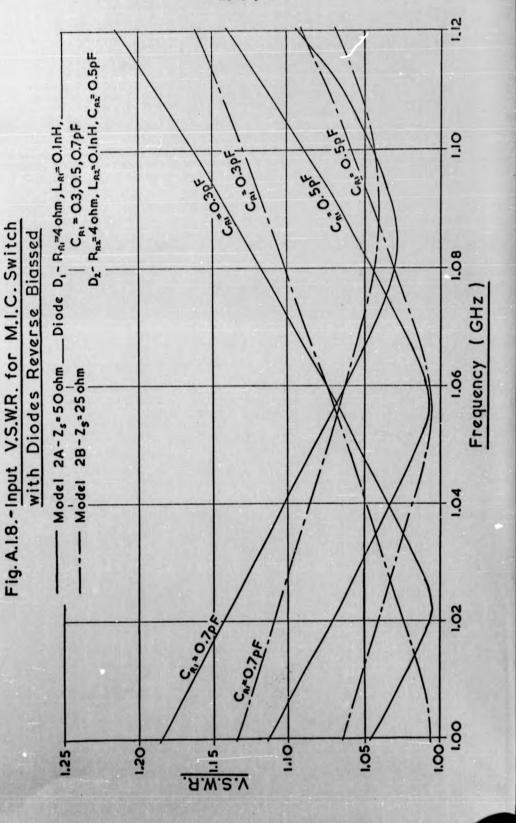

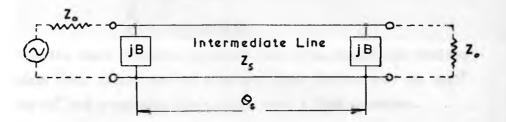

To assist with this work a remote teletype terminal for a time sharing computer was used at Luton for microwave circuit synthesis whilst the computer program written by McPhun (0.1) using chain matrix analysis was used for circuit analysis on the Elliott 4130 computer at the University of Warwick. Two problems were investigated with Microwave Associates Ltd.. The first problem consisted of checking and, if possible, improving the design of an L-band microwave integrated circuit switch (0.2) as described in Appendix A.1. The second problem consisted of carrying out a theorectical investigation into various types of microwave phase shifter circuits for their possible production in the form of microwave integrated circuits described in Appendix A.2. For the

second problem it was found that McPhun's computer program (0.1) was not suitable for the types of circuits to be analysed. Thus a new computer program, BGMA (0.4), had to be written by the author for this work to extend the ideas contained in McPhun's program.

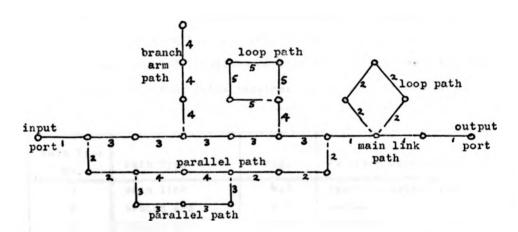

On arriving at the University of Warwick in October 1969 a year was spent almost entirely on extending the appication of the chain matrix method of analysis for the analysis of general microwave circuits. During this period the CHATN1 program (0.5) was written by the author using chain matrix analysis for the analysis of general microwave circuits. This program analysed a circuit consisting of an assembly of 2-port networks and it broke this assembly down into a simpler assembly of cascades of 2-port networks forming a main link between the input and output port of the circuit and branch arms, loop paths and parallel paths built to any level on this main path.

Towards the completion of the work on developing the CHAIN1 program it was realised that the use of the chain matrix method of analysis had been taken just about to its limit but it could still not analyse all microwave circuits. Also at that time the use of the chain matrix method of analysis for general microwave circuits was being critised by Dr. Larcombe, University of Warwick and Mr. Wolfendale, Redac Software Ltd.. Thus at that time it became necessary to completely rethink the method of analysis being used. The result of this was that it was decided to use a previously untried method for the analysis of microwave circuits.

The new method used was the mixed matrix method of analysis for general microwave circuits considered as an assembly of n-port networks (0.6) This method was found to be far more

suitable. The MICRO2 computer program (0.7) was written by the author to use this method of analysis. This program took about a year to write and was later replaced by the MICRO3 computer program which incorporated more facilities ( see Appendix A.5 ).

During the course of the research work for this thesis there was a considerable amount of interest shown by the University of Warwick in the use of computer programs in an interactive mode. Thus a large portion of the time spent in writing the BGMA, CHAIN1, MICRO2 and MICRO3 programs was spent on developing interactive applications for these programs with each program including more interactive facilities than the last one. This work involved developing techniques for a full syntax analysis of the data, the use of complex, but very versatile, data structures and the use of the program interactively on a remote teletype possibly with a graphical display to display the results of a circuit analysis in graphical form. The result was that in the MICRO3 program all these facilities were included and the data for the program had more the form of a computer programming language that the normal data for a program.

Some time was spent during the course of the research for this thesis investigating the range of microwave components which should be included in a computer program for the analysis of microwave circuits. Also an investigation into how optimisation could be included in this type of program was carried out.

The organisation of this thesis is as follows. In chapter 1 various types of microwave circuits are looked at to decide what problems are involved in the analysis of microwave circuits on a computer and the way these problems should be tackled. In chapter 2

three possible methods of analysis are discussed with the intention of deciding on the best method for the analysis of microwave circuits. Chapter 3 forms a supporting chapter for chapter 2 describing the various matrix methods involved in analysis and the best way these can be organised. Chapters 4 and 5 describe the CHAIN1 program with chapter 4 describing the path topological analysis used to break the circuit into paths consisting of cascades of 2-port networks and chapter 5 describes the erganisation of the CHAIN1 program. Chapters 6 and 7 describe the MICRO2 and MICRO3 programs with chapter 6 describing the data structure used and chapter 7 describing the organisation of the program. Chapter 8 describes the interactive facilities included in the programs whilst chapters 9 and 10 describe the work done on microwave components and optimisation respectively. Finally chapter 11 gives the conclusions of the whole thesis.

#### References

- 0.1) N.K. McPhun, 'A Computer Program for the Analysis of Branched Distributed and Lumped Circuits', IEE Conference Publication No. 25, 1966, pp. 89-124

- O.2) B.G. Marchent, 'Computer Aided Design of an L-Band M.I.C.

Switch', Microwave Associates Ltd., Luton, 1969, Technical

Report No. 160, ( see also Appendix A.1 )

- 0.3) B.G. Marchent, 'A Comparative Study of the Iterative, Hybrid Ring and Switched Line Microwave Phase Shifters', Microwave Associates Ltd., Luton, 1969, private communication, ( see also Appendix Λ.2 )

- 0.4) B.G. Marchent, 'A Computer Program (BGMA) for the Analysis of

Lumped and Distributed Networks', University of

Warwick, Nov. 1969, School of Engineering Science Report No. 50

- O.5) B.G. Marchent, 'CHAIN1, A Frequency Domain Circuit Analysis

Program using Chain Matrices', University of Warwick,

July 1970, School of Engineering Science Report No. 64,

( see also Appendix A.4 )

- O.6) B.G. Marchent, 'The Computer Aided Design of Microwave Circuits', IREE Czechoslovakia, Summer School on Circuit Theory 1971, Short Contributions Vol. 2, pp.255-263 (see also Appendix A.6)

- O.7) B.G. Marchent, 'MICRO2, A Frequency Domain Circuit Analysis

Program for Microwave Circuits using Mixed Matrices',

University of Warwick, June 1971, School of Engineering

Science Report No. 65

#### ACKNOWLEDGER ENTS

The author would like to thank the following for their assistance during the course of the research work and preparation of this thesis.

- 1) Mr. M.K. McPhun, University of Warwick

For the initial idea for a Ph. D. research topic

on the Computer Aided Design of Microwave Circuits

and his supervision of the research work.

- 2) Microwave Associates Ltd., Luton

For supplying the author with experience in the

design of microwave integrated circuits, and also

an income, whilst waiting for a Science Research

Council grant to start.

- 5) Science Research Council For their financial support during the course of the research work for the author's maintenance and costs for the author to attend conferences.

- 4) Redac Software Ltd., Tewkesbury

For their financial support and the use of their

experience in the design of general purpose

interactive computer programs for electronic

circuit design.

- 5) Dr. M.H.E. Larcombe, University of Warwick

For his advice on syntax analysis, a list processing

approach to data structure and matrix analysis.

- 6) Dr. W.R. Laxon, Lanchester Polytechnic

For his ideas on the organisation of a list

processing approach to data structure for

complex structures.

- 7) Mrs. Sonia Marchent, wife

For her support during the writing and typing of

this thesis through many lost weekends and holidays.

- 8) Lucy Jane Marchent, daughter, born 25th October 1972

One of the conclusions to this thesis.

# Contents

| Library Officer |     |

|-----------------|-----|

|                 |     |

|                 |     |

|                 |     |

|                 |     |

|                 | Tes |

## CONTENTS

Chapter 1

| SPECIFICATION OF THE PROBLEM FOR THE COMPUTER                  |      |

|----------------------------------------------------------------|------|

| AIDED DESIGN OF MICROWAVE CIRCUITS                             | pare |

| 1.1 FICROWAVE CIRCUITS                                         | 1.1  |

| 1.1.1 Definition                                               | 1.1  |

| 1.1.2 Circuit Ports                                            | 1-3  |

| 1.1.3 Description of Circuit Performance                       | 1.4  |

| 1.1.4 Practical Microwave Circuits                             | 1.7  |

| 1.1.4.1 Practical Experience in Circuit Synthesis and Analysis | 1.7  |

| 1.1.4.2 Coaxial Plunger                                        | 1.7  |

| 1.1.4.3 Microwave Integrated Circuit                           |      |

| Phase Shifter                                                  | 1.9  |

| 1.2 MICROWAVE CIRCUIT ANALYSIS                                 | 1.12 |

| 1.2.1 Assemblies of n-port Networks                            | 1.12 |

| 1.2.2 Wave and Power Scattering Matrices                       | 1.16 |

| 1.2.2.1 Wave Scattering Matrix                                 | 1.17 |

| 1.2.2.2 Power Scattering Matrix                                | 1.17 |

| 1.2.2.3 Wave/Power Scattering Conversion                       | 1.18 |

| 1.2.3 Presentation of Results                                  | 1.18 |

| 1.3 COMPUTER AIDED DESIGN OF MICROWAVE CIRCUITS                | 1.22 |

| 1.3.1 Introduction                                             | 1.22 |

| 1.3.2 Microwave Circuit Description                            | 1,22 |

| 1.3.3 Circuit Analysis Procedure                               | 1.23 |

| 1.3.4 Optimisation                                             | 1.23 |

| 1.3.5 The Computer Program                                     | 1.24 |

| 1.4 PRESENT PROGRAMS FOR MICROWAVE CIRCUIT                     |      |

| ANALYSIS                                                       | 1.26 |

| 1.4.1 Introduction                                             | 1.26 |

| 1.4.2 Chain Matrix Analysis Programs                           | 1.27 |

| 1.4.2.1 MKMcPH                                                 | 1.27 |

| 1.4.2.2 FILTAN                                                 | 1.28 |

| 1.4.2.3 DIPNET                                                 | 1.28 |

| 1.4.3 Electronic Circuit Analysis Programs                     | 1.29 |

| 1.4.3.1 ECAP                                                   | 1.29 |

| 1.4.3.2 REDAP31                                                | 1.29 |

| 1.4.3.3 BELNAP                                                 | 1.30 |

| 1.5 CONCLUSIONS                                                | 1.31 |

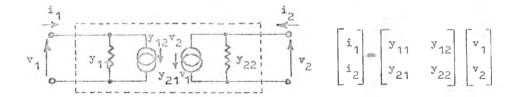

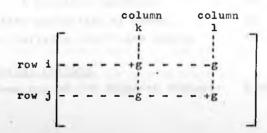

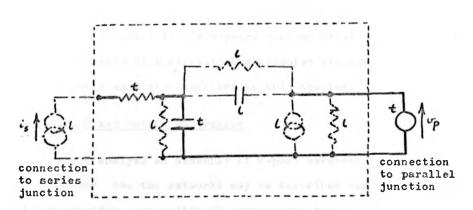

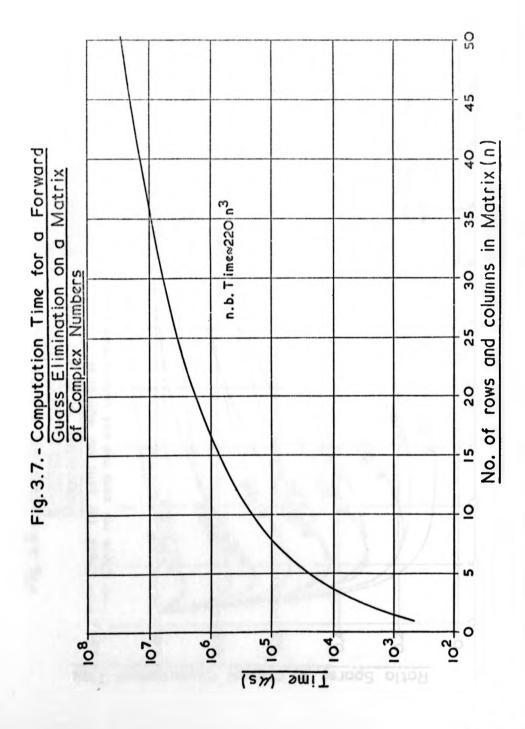

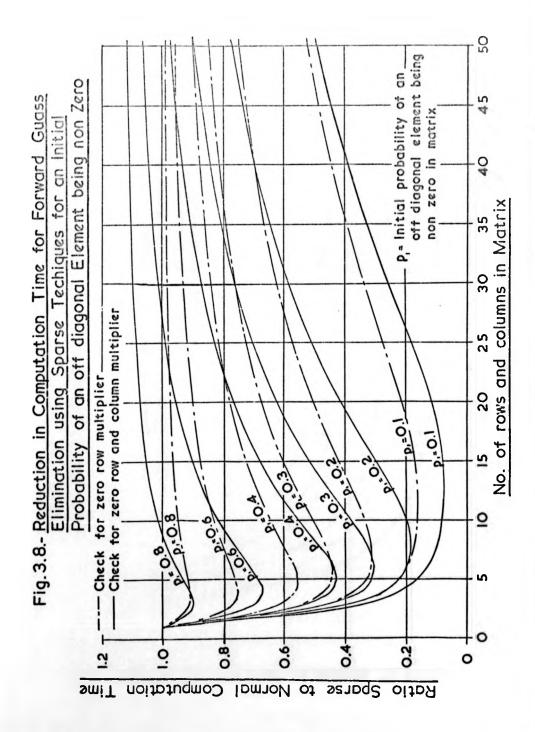

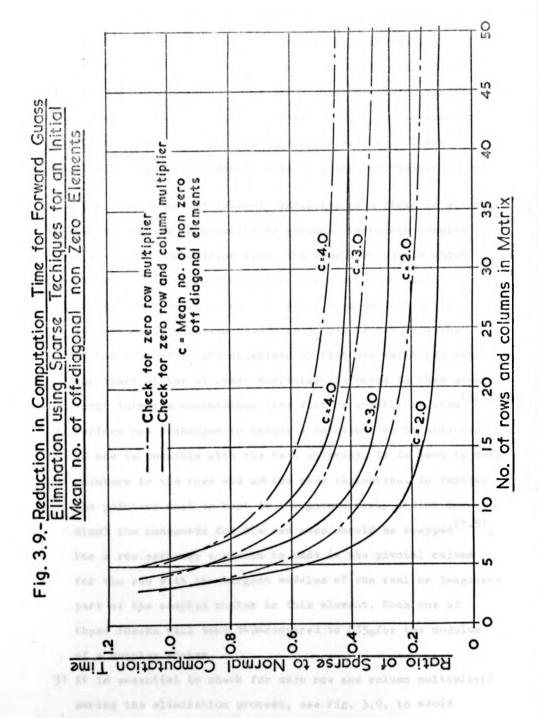

Chanter 2 CINCULT ANALYSIS FOR MICROMAVE CIRCUITS page 2.4 INTRODUCTION 2.1 2.6 2.2 CHAIN HATRIX ANALYSIS 2.2.1 Introduction 2.6 2.6 2.2.2 Simple Cascade of 2-port Networks 2.8 2.2.3 Simple 2-port Networks 2.8 2.2.4 Branch Arms 2.2.5 Parallel Paths 2.11 2.2.6 Loop Paths 2.14 2.2.7 Conversion of Chain to Scattering Matrix 2.15 2.2.8 Practical Computation Times 2.16 2.3 LUMPED ELEMENT ANALYSIS 2.17 2.3.1 Lumped Equivalent Circuits for n-port Networks 2.17 2.19 2.3.2 Nodal Analysis 2.3.2.1 Basic Principles 2.19 2.20 2.3.2.2 N-port Networks in Nodal Analysis 2.3.2.3 Computation Times and Matrix Filling2.22 2.3.2.4 Practical Computation Times 2.24 2.3.3 Mixed Mesh and Cutset Analysis 2.26 2.4 MIXED MATRIX ANALYSIS 2.26 2.4.1 Introduction 2.4.2 Mixed Matrix Generation 2.26 2.4.3 Mixed Matrices for Networks 2.29 2.29 2.4.3.1 1-port Networks 2.4.3.2 2-port Networks 2.29 2.31 2.4.3.3 Transmission Lines 2.4.3.4 n-port Networks 2.31 2.4.4 Conversion Mixed to Scattering Matrix 2.32 2.4.4.1 Power Scattering 2.32 2.4.4.2 Wave Scattering 2.33 2.4.5 Conversion Scattering to Mixed Matrix 2.33 2.4.5.1 Power Scattering 2.33 2.34 2.4.5.2 Wave Scattering 2.4.6 Mixed Matrices for Transmission Lines 2.35 2.36 2.4.7 Practical Computation Times 2.5 CONCLUSIONS 2.37

| Chapter 3                                         |       |

|---------------------------------------------------|-------|

| MATRIX METHODS FOR CIRCUIT ANALYSIS               | page  |

| 3.1 EXCHANGE OF VARIABLES                         | 3.1   |

| 3.2 SOLUTION OF A SET OF LINEAR EQUATIONS         | 3.2   |

| 3.2.1 Introduction                                | 3.2   |

| 3.2.2 Forward Elimination                         | 3.2   |

| 3.2.3 Back Substitution                           | 3.5   |

| 3.3 ELIMINATION OF INTERNAL VARIABLES IN ANALYSIS | 3.8   |

| 3.3.1 Introduction                                | 3.8   |

| 3.3.2 Elimination Process                         | 3.9   |

| 3.3.3 Elimination Process on a Sparse Matrix      | 3.11  |

| 3.3.4 Elimination of a Single Variable            | 3.12  |

| 3.3.5 Mean Forward Elimination Time for a         |       |

| Sparse Matrix                                     | 3.15  |

| 3.4 CONCLUSIONS                                   | 3.21  |

| Chapter 4                                         |       |

| PATH TOPOLOGICAL ANALYSIS FOR CHAIN MATRIX        |       |

| ANALYSIS PROGRAM                                  | page  |

| 4.1 INTRODUCTION                                  | 4.1   |

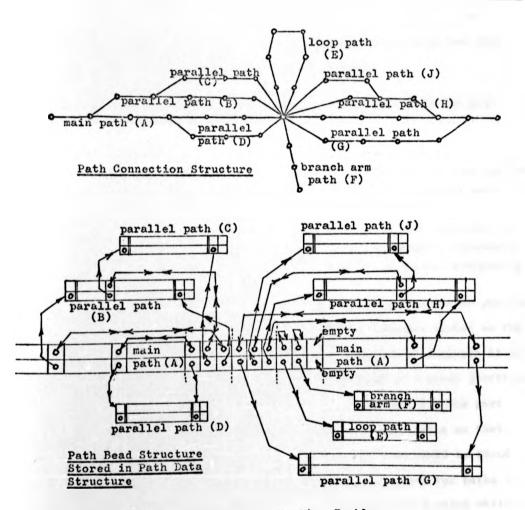

| 4.2 PATH TOPOLOGICAL STRUCTURE                    | 4.3   |

| 4.2.1 Single Path                                 | 4.3   |

| 4.2.2 Path Types                                  | 4.5   |

| 4.2.3 Use of Path Topology During Analysis        | 4.5   |

| 4.2.4 Path Nescing                                | 4.8   |

| 4.3 PATH TOPOLOGICAL ANALYSIS                     | 4.10  |

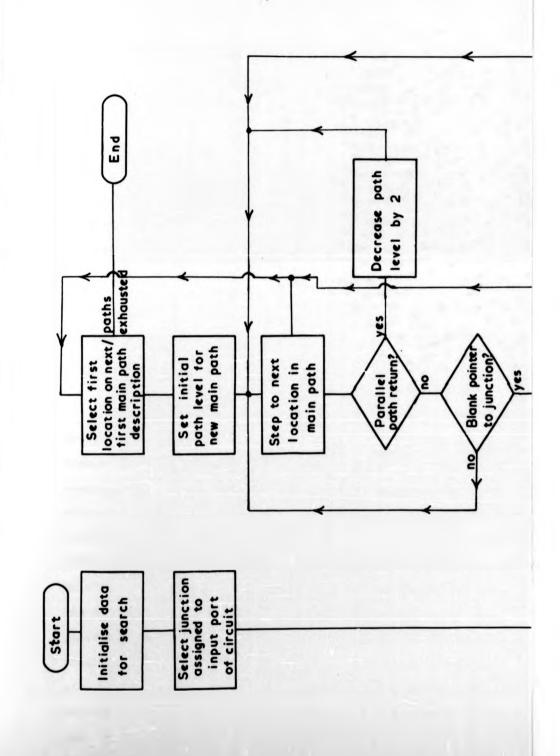

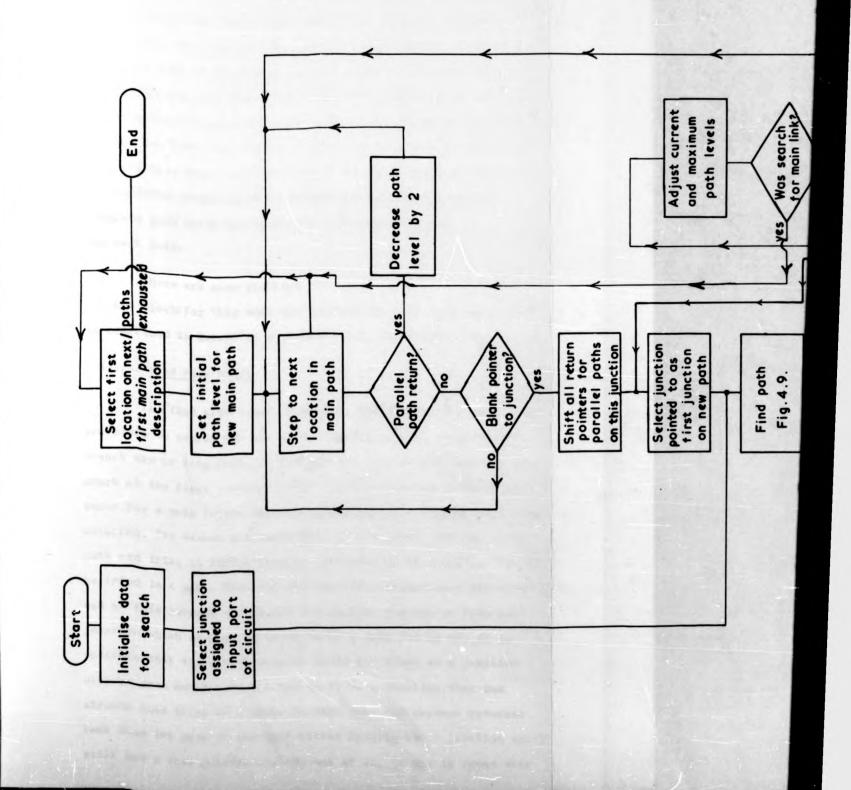

| 4.3.1 Objective                                   | 4.10  |

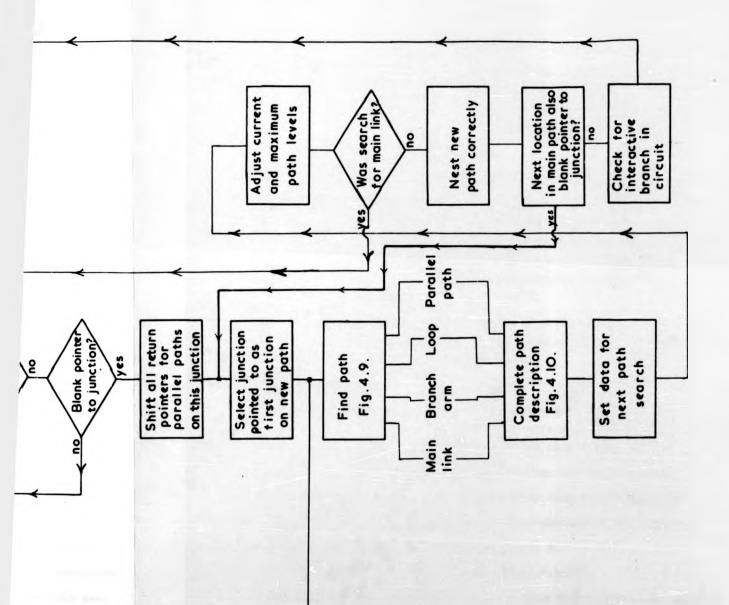

| 4.3.2 Path Search Organisation                    | 4.11  |

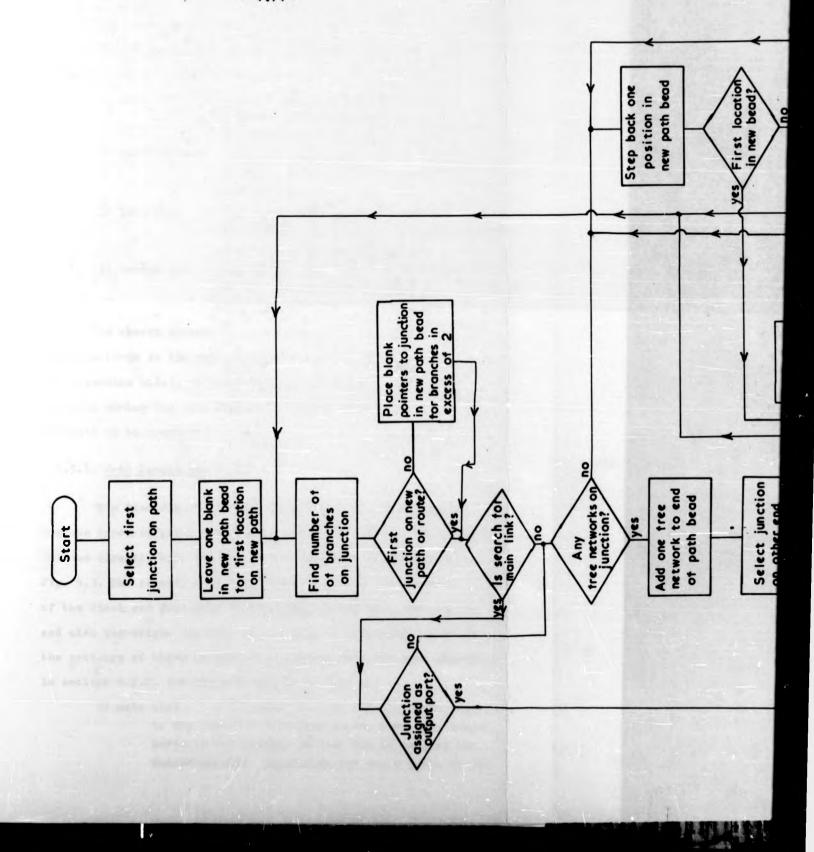

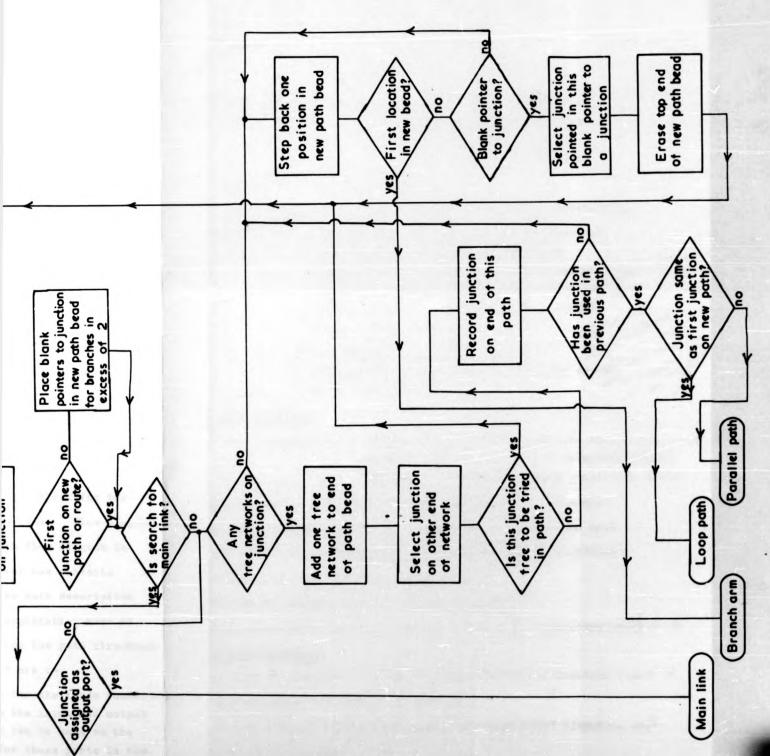

| 4.3.3 Find Path Block                             | 4.13  |

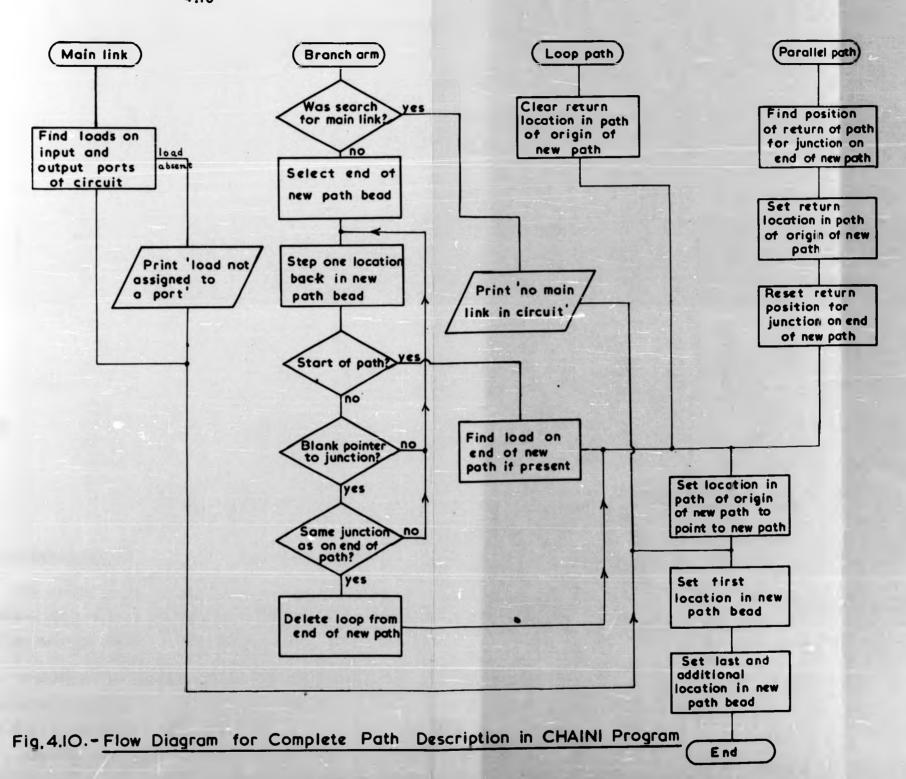

| 4.3.4 Path Completion Block                       | 4.15  |

| 4.3. Path Nesting                                 | 4.17  |

| 4.3.5 Check for Parallel Paths Crossing           | 4.20  |

| 4.4 CONCLUSIONS                                   | 4.22  |

| Chapter 5                                         |       |

| CHAIN MATRIX ANALYSIS CHAIN1 PROGRAM              | page  |

| 5.1 INTRODUCTION                                  | 5.1   |

| 5.2 DATA FORMAT                                   | 5.3   |

| 5.2.1 Introduction                                | 5.3   |

| 5.2.2 Syntactical Definition of Data for CHAI:    | 115.4 |

| 5.2.3 Syntax Analysis Procedures for CHAIN1       | 5.6   |

|                                                  | page |

|--------------------------------------------------|------|

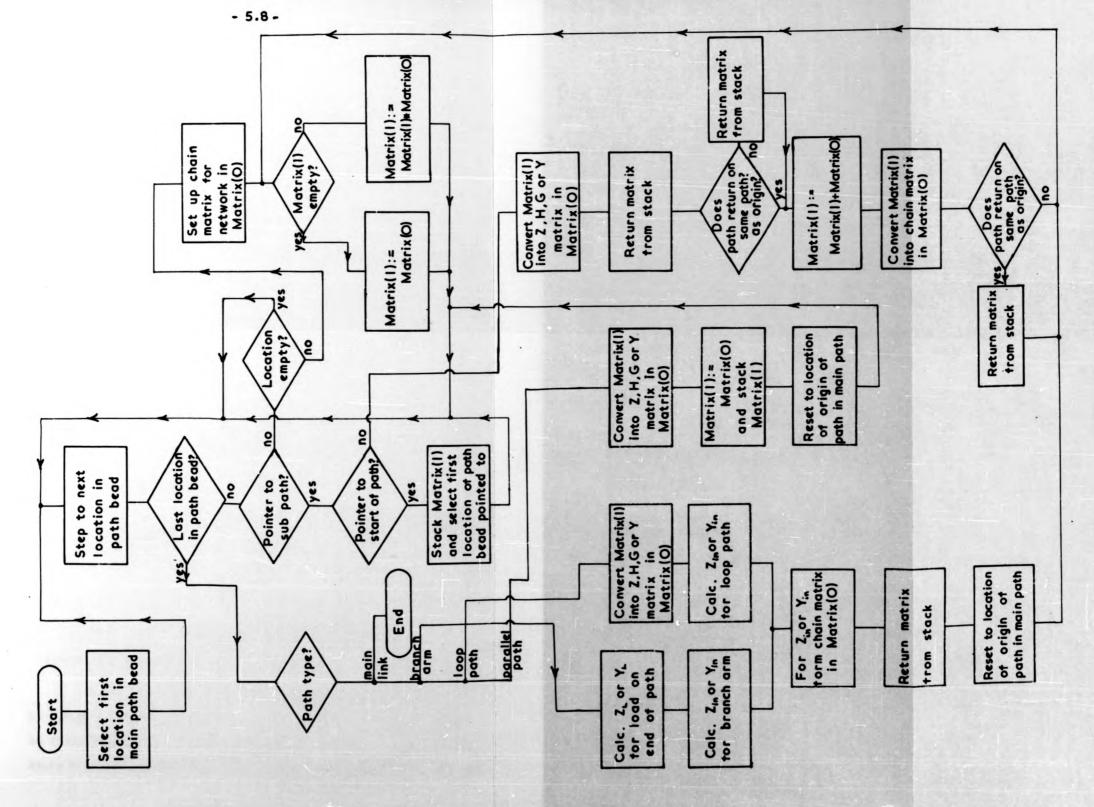

| 5.3 CHAIN MATRIX ANALYSIS PROCEDURE              | 5.7  |

| 5.3.1 Introduction                               | 5.7  |

| 5.3.2 Main Link Path                             | 5.7  |

| 5.3.3 Sub-paths                                  | 5.9  |

| 5.3.4 Branch Arm                                 | 5.10 |

| 5.3.5 Loop Path                                  | 5.10 |

| 5.3.6 Parallel Path                              | 5.10 |

| 5.3.7 Setting up Chain Matrices for Networks     | 5.12 |

| 5.3.8 Conversion Chain to ZHGY Matrices          | 5.12 |

| 5.3.9 Matrix Stack and Workspace                 | 5.12 |

| 5.3.10 Complex Number Arithmetic                 | 5.14 |

| 5.4 CONCLUSIONS                                  | 5.15 |

| Chapter 6                                        |      |

| LIST PROCESSING APPROACH TO DATA STRUCTURE FOR   |      |

| MIXED MATRIX ANALYSIS PROGRAM                    | page |

| 6.1 INTRODUCTION                                 | 6.1  |

| 6.2 A LIST PROCESSING APPROACH TO DATA STRUCTURE | 6.3  |

| 6.2.1 Introduction                               | 6.3  |

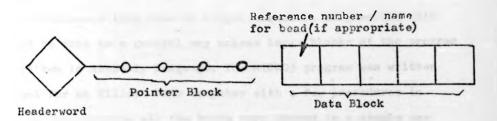

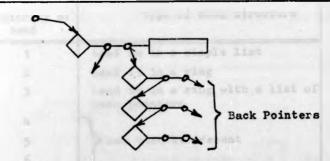

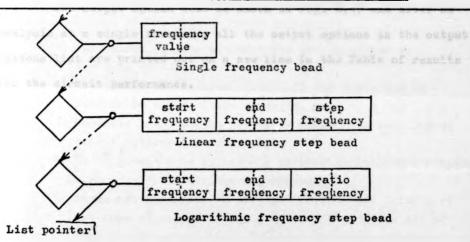

| 6.2.2 Bead Structure                             | 6.3  |

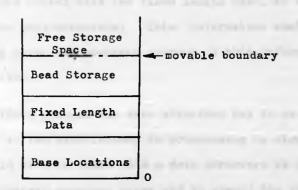

| 6.2.3 Bead Storage                               | 6.3  |

| 6.2.4 Bead Interconnection                       | 6.5  |

| 6.2.5 Storage of Circuit Topology                | 6.8  |

| 6.2.6 Headerword Formation and Access            | 6.10 |

| 6.2.7 Pointers and Data in Bead                  | 6.10 |

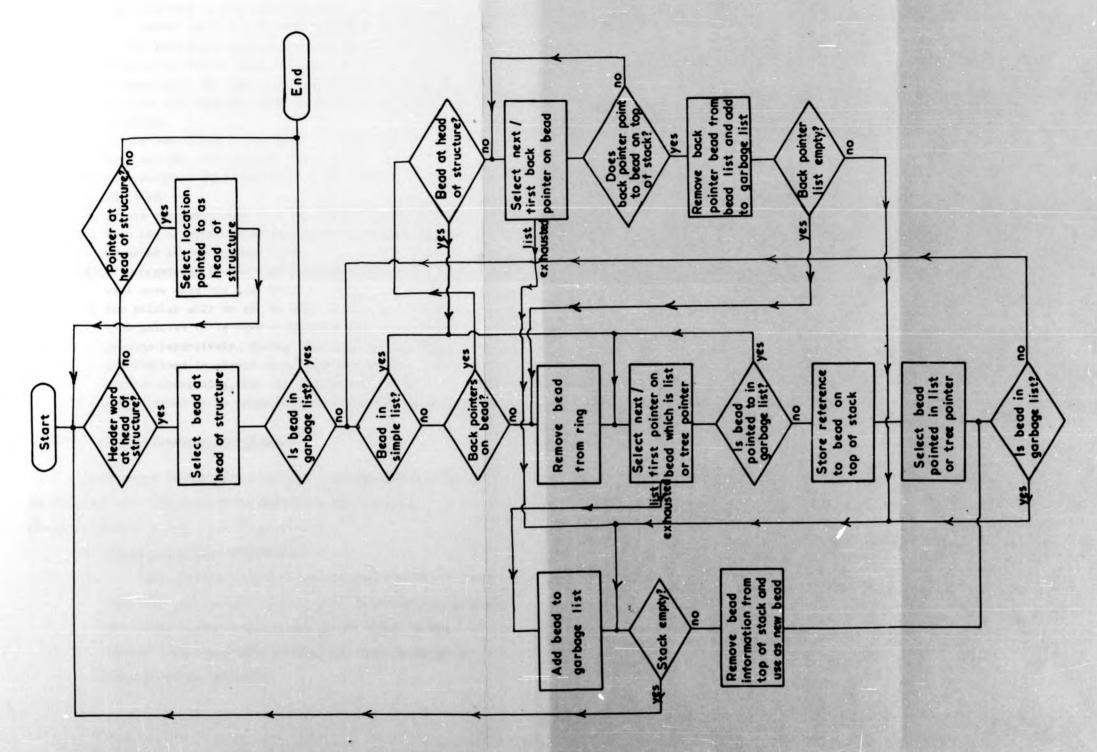

| 6.2.8 Garbage Collection                         | 6.10 |

| 6.2.9 Allocation of Space for New Beads          | 6.11 |

| 6.2.10 Insert Bead in Data Structure             | 6.12 |

| 6.2.11 Locate Bead                               | 6.12 |

| 6.2.12 Bead Structure Elimination                | 6.12 |

| 6.2.13 Circuit Topology Procedures               | 6.15 |

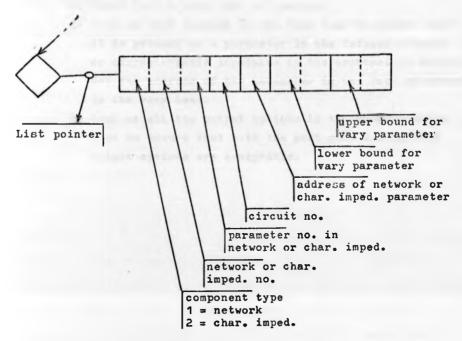

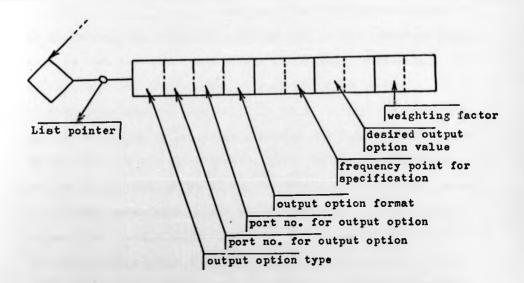

| 6.3 DATA STRUCTURE FOR MICRO3                    | 6.17 |

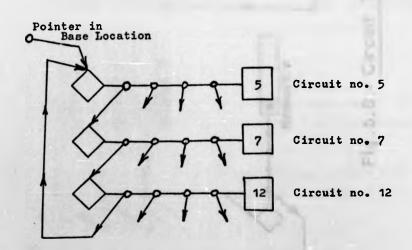

| 6.3.1 Use of Base Locations                      | 6.17 |

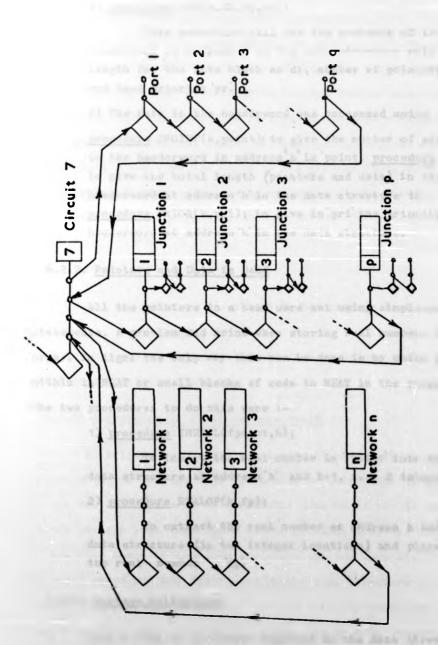

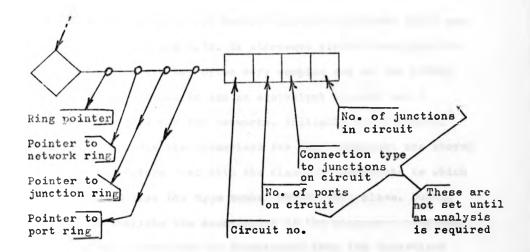

| 6.3.2 Circuit Bead                               | 6.17 |

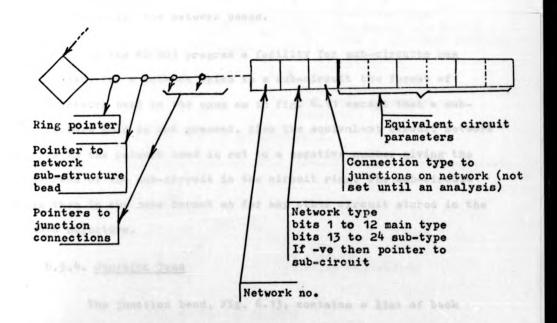

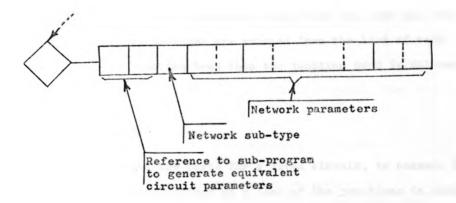

| 6.3.3 Network Bead                               | 6.19 |

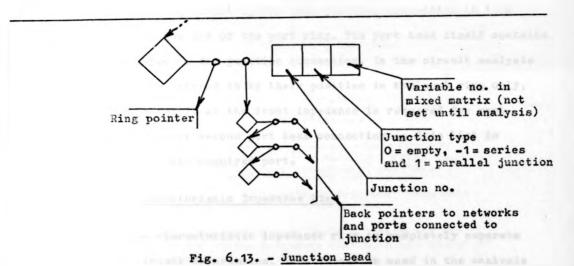

| 6.3.4 Junction Bead                              | 6.19 |

| 6.3.5 Port Bead                                  | 6.21 |

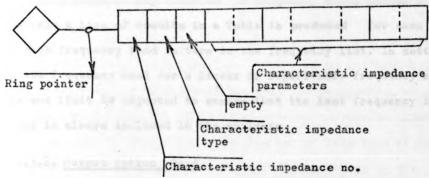

| 6.3.6 Characteristic Impedance Bead              | 6.21 |

| 6.3.7 Frequency Bead                             | 6.21 |

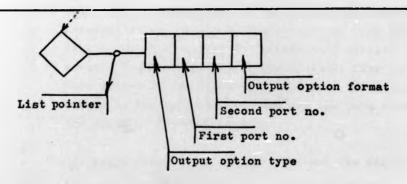

| 6.3.8 Output Option Bead                         | 6.23 |

| 6.4 CONCLUSIONS                                  | 6.24 |

|                                                  |      |

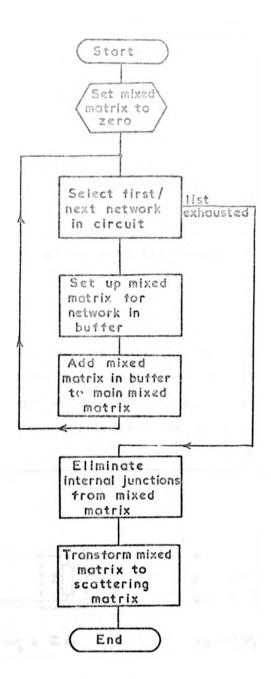

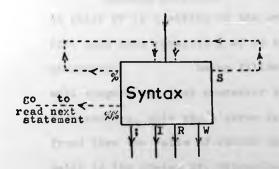

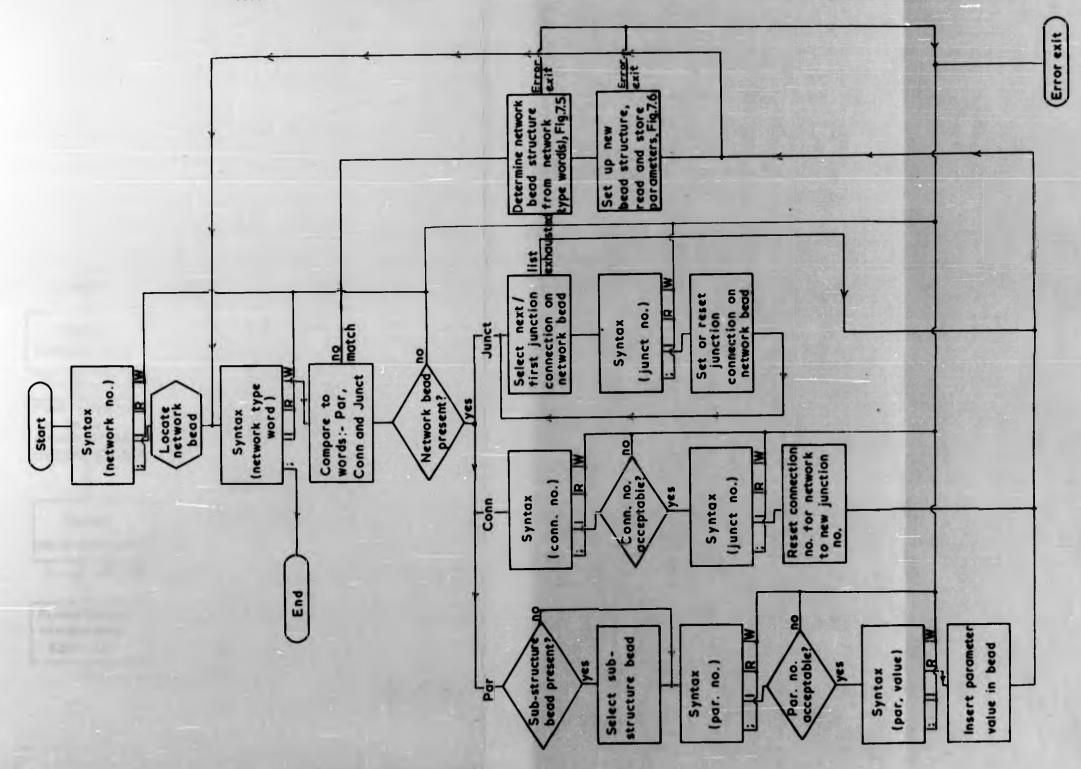

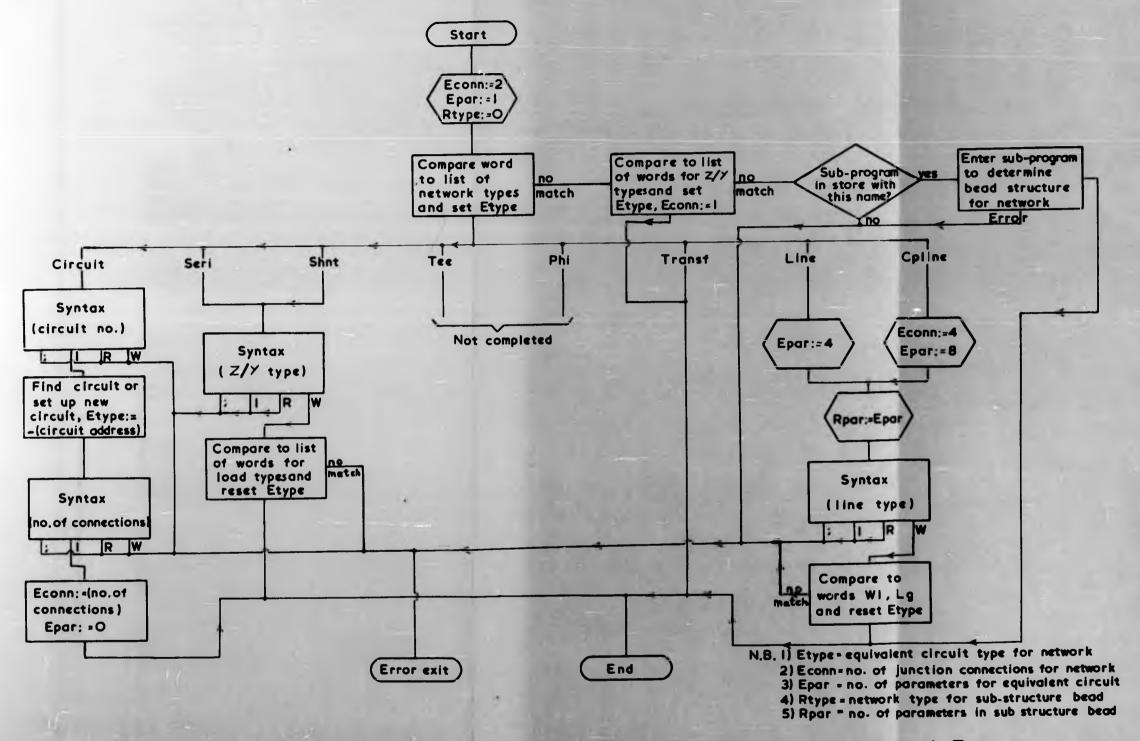

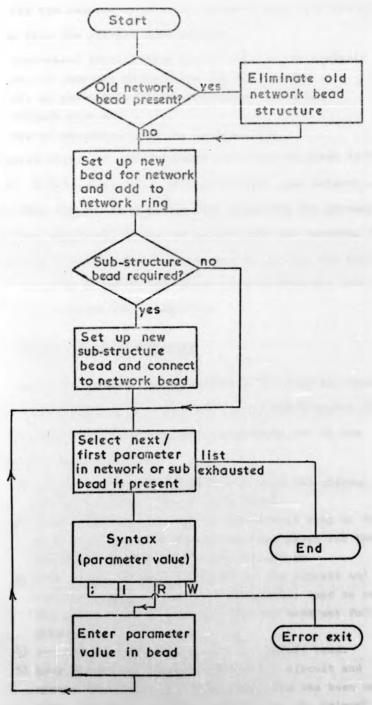

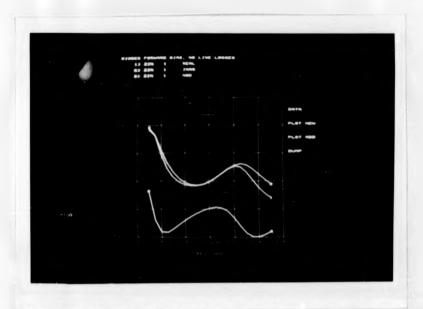

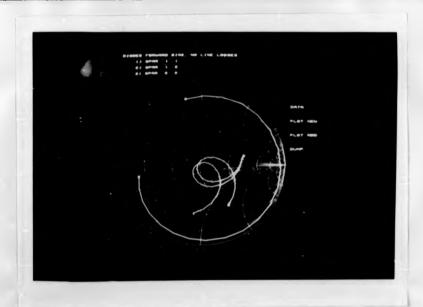

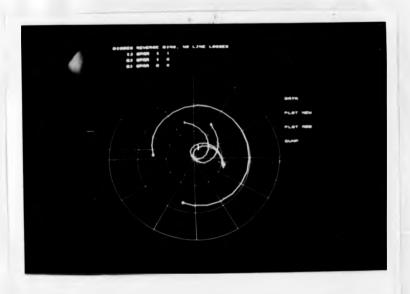

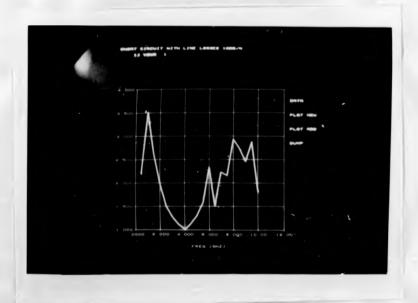

#### Chapter 7 MIXED MATRIX ANALYSIS MICRO3 PROGRAM pare 7.1 7.1 INTRODUCTION 7.5 7.2 SYNTAX ANALYSIS 7.5 7.2.1 Introduction 7.6 7.2.2 Statement Structure of Data 7.2.3 Syntax Analysis Procedures 7.6 7.8 7.2.4 String Comparisons 7.9 7.2.5 Data Errors 7.10 7.3 DATA PROCESSING 7.3.1 Introduction 7.10 7.10 7.3.2 Syntactical Definition of Data 7.3.3 Statement Processing 7.15 7.3.4 Example of Data Processing on a Network 7.16 Statement 7.20 7.3.5 Check Circuit Desciption 7.21 7.3.6 Check Data for Analysis 7.22 7.4 CIRCUIT ANALYSIS 7.22 7.4.1 Introduction 7.24 7.4.2 Circuit Analysis Procedure 7.26 7.4.3 Hixed Hatrices for Networks 7.26 7.4.3.1 Equivalent Circuit for Network 7.4.3.2 Mixed Matrices from Equivalent 7.26 Circuit 7.4.4 Variable Elimination and Equation 7.28 Solution 7.4.5 Exchange of Variables 7.30 7.4.6 Convert Scattering to Mixed Matrix 7.30 7.31 7.4.7 Complex Number Procedures 7.5 CONCLUSIONS 7.33 Chapter 8 INTERACTIVE USE OF MICRO3 PROGRAM page 8.1 INTRODUCTION 8.1 8.2 TELETYPE ON-LINE 8.3 8.2.1 Objective 8.3 8.3 8.2.2 Data Processing 8.6 8.2.3 Channel Assignment 8.3 USE OF GRAPHICAL DISPLAY 8.9 8.3.1 Use of Display 8.9 8.3.2 Results on Graphical Display 8.11 8.4 THE COMPUTER FOR INTERACTIVE WORK 8.16

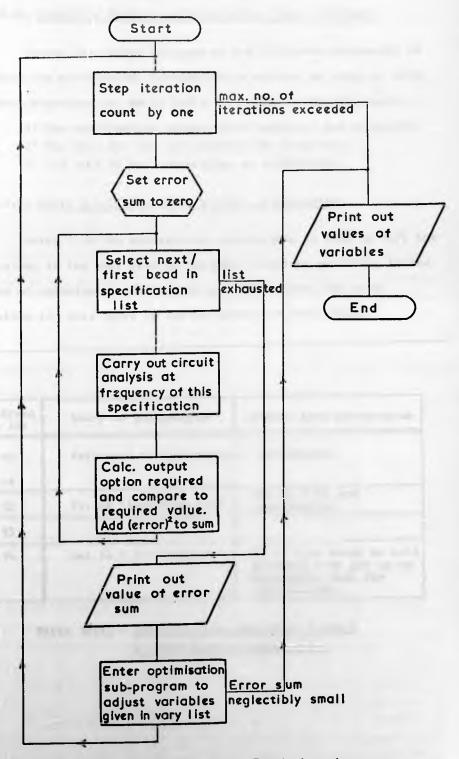

MALE T ALLEYS WERDY

#### Chapter 9 MICROWAVE COMPONENTS IN CIRCUIT ANALYSIS PROGRAM page 9.1 INTRODUCTION 9.1 9.2 SUB-PROGRAMS FOR MICROWAVE COMPONENTS 9.3 9.2.1 General Principles 9.3 9.2.2 Entry O - Check Network Type 9.3 9.2.3 Entry 1 - Intermediate Results for Equivalent Circuit 9.5 9.2.4 Entry 2 - Complete Equivalent Circuit 9.5 9.3 PROBLEMS OF INCLUDING HICROWAVE COMPONENTS 9.7 9.4 MICROWAVE COMPONENT SUB-PROGRAMS 9.9 9.4.1 Rectangular Waveguide, Program WGRECT 9.9 9.4.2 Circular Waveguide, Program WGCIRC 9.12 9.4.3 Coaxial Line. Program COAX 9.12 9.4.4 Two Wire Line, Program WIRE2 9.12 9.4.5 Microstrip, Program MICSTRIP 9.13 9.4.6 Triplate, Program TRIPLATE 9.13 9.4.7 Table of Parameters, Program TABLE 9.15 Chapter 10 OPTIMISATION IN MICROWAVE ANALYSIS PROGRAM page 10.1 INTRODUCTION 10.1 10.2 INPUT DATA 10.2 10.2.1 Syntactical Definition 10.2 10.2.2 Specification Statement 10.2 10.3 10.2.3 Vary Statement 10.4 10.2.4 Optimise Statement 10.3 DATA STRUCTURE 10.5 10.3.1 Specification Bead 10.5 10.3.2 Vary Bead 10.5 10.3.3 Check Data for Optimisation 10.5 10.8 10.4 OPTIMISATION 10.4.1 Circuit Analysis for Optimisation 10.8 10.4.2 Entry O - Initialise Optimisation Data Structure 10.10 10.4.3 Entry 1 - Optimisation of Circuit Parameters 10.10 10.5 OPTIMISATION TECHNIQUES 10.11 Chapter 11 CONLUSIONS OF THESIS page 11.1 CONCLUSIONS 11.1

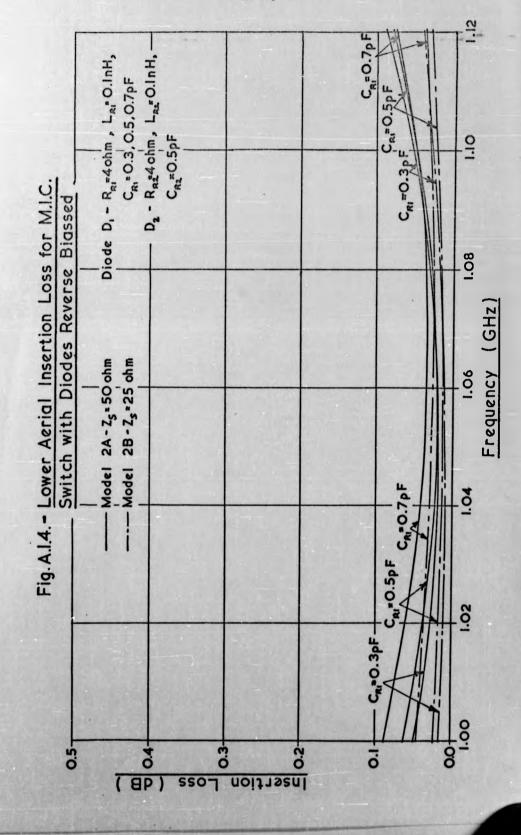

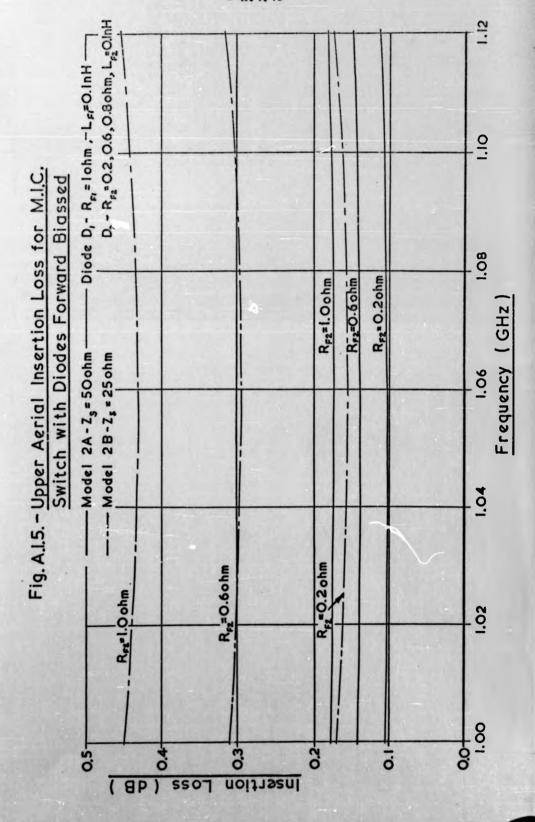

| Appendix A.1                               |        |

|--------------------------------------------|--------|

| L-BAND MICROWAVE INTEGRATED CIRCUIT SWITCH | page   |

| A.1.1 INTRODUCTION                         | A.1.1  |

| A.1.2 OLD SWITCH DESIGN                    | A.1.1  |

| A.1.3 NEW DESIGN PROCEDURE                 | A.1.3  |

| A.1.4 SWITCH PERFORMANCE                   | A.1.6  |

| A.1.5 CONCLUSIONS                          | A.1.6  |

| Appendix A.2                               |        |

| COMPARATIVE STUDY OF MICROWAVE INTEGRATED  |        |

| CIRCUIT PHASE SHIFTERS                     | page   |

| A.2.1 INTRODUCTION                         | A.2.1  |

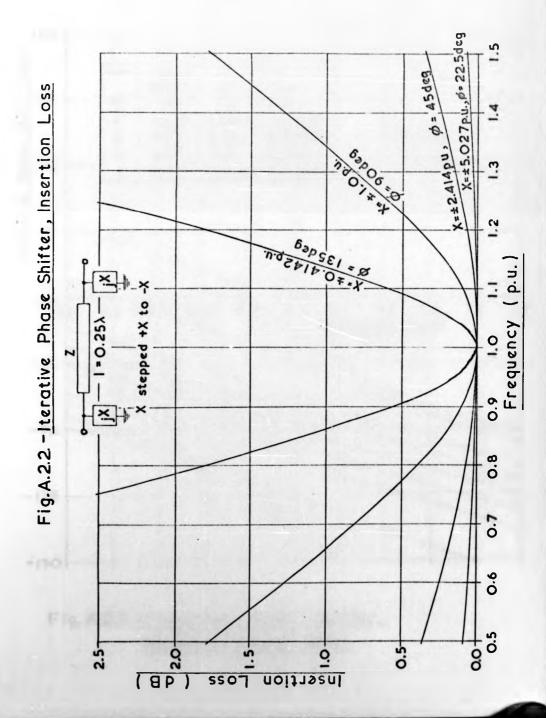

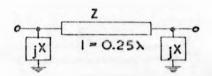

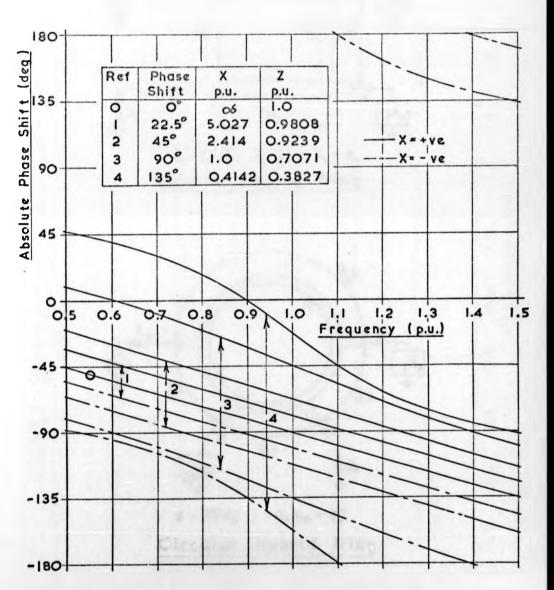

| A.2.2 ITERATIVE PHASE SHIFTER              | A.2.1  |

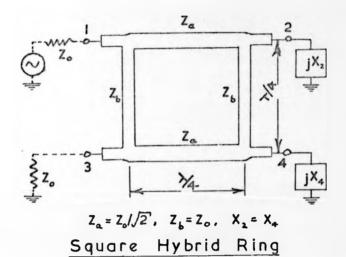

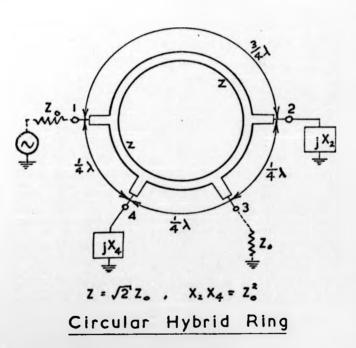

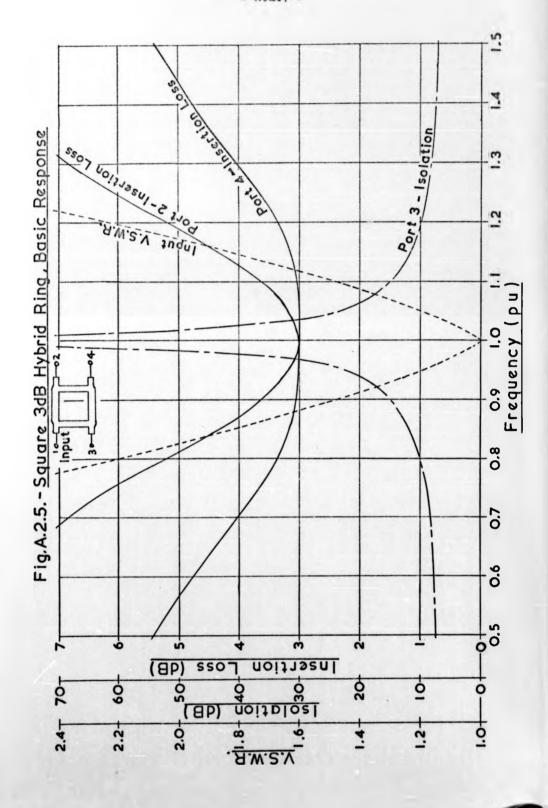

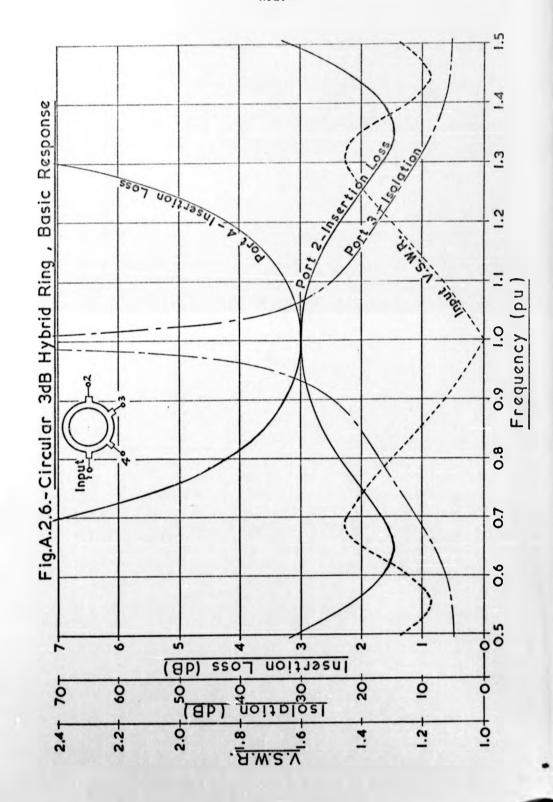

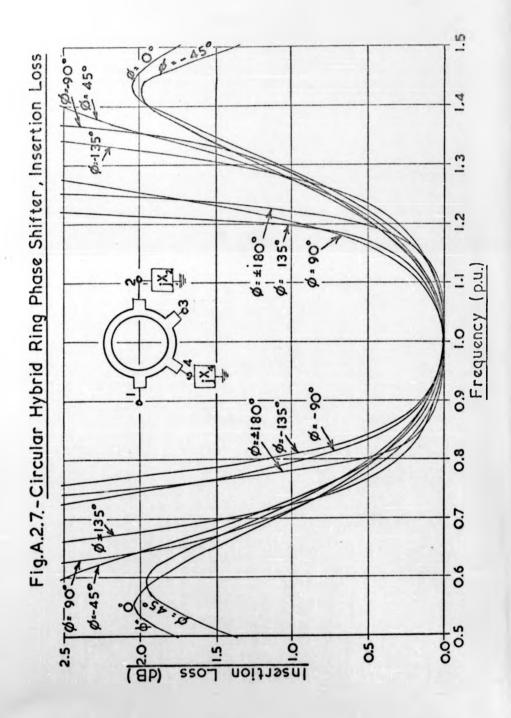

| A.2.3 HYBRID RING PAHSE SHIFTER            | A.2.3  |

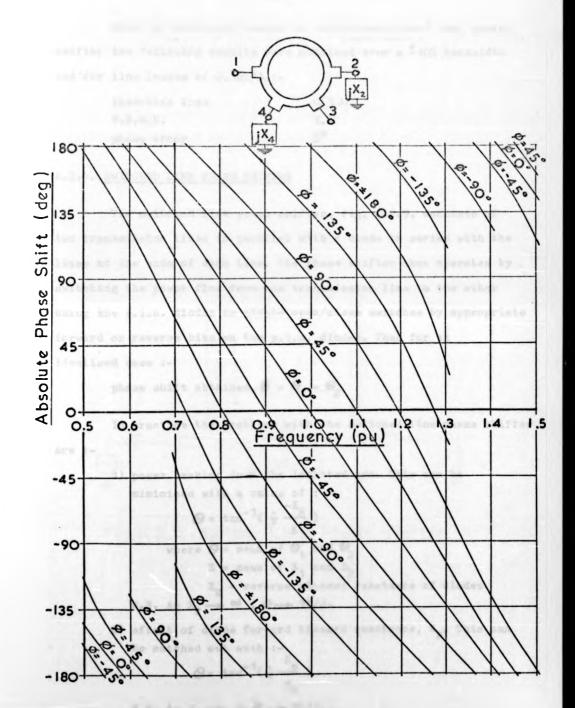

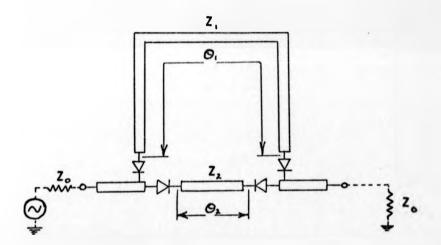

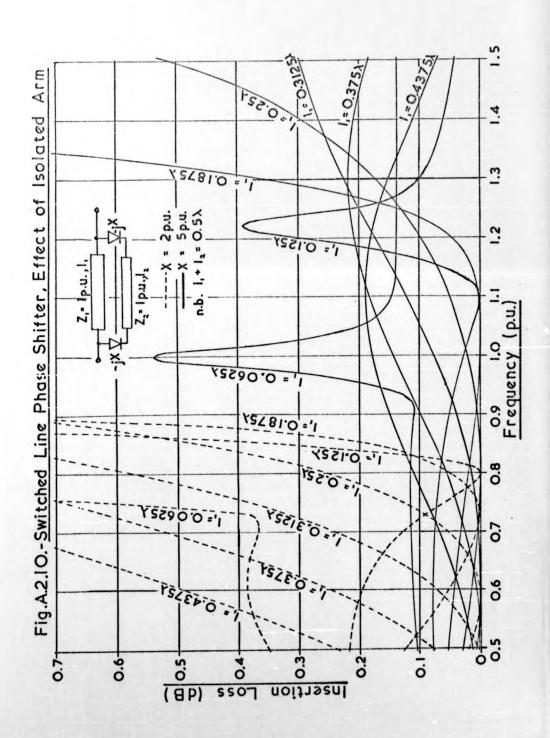

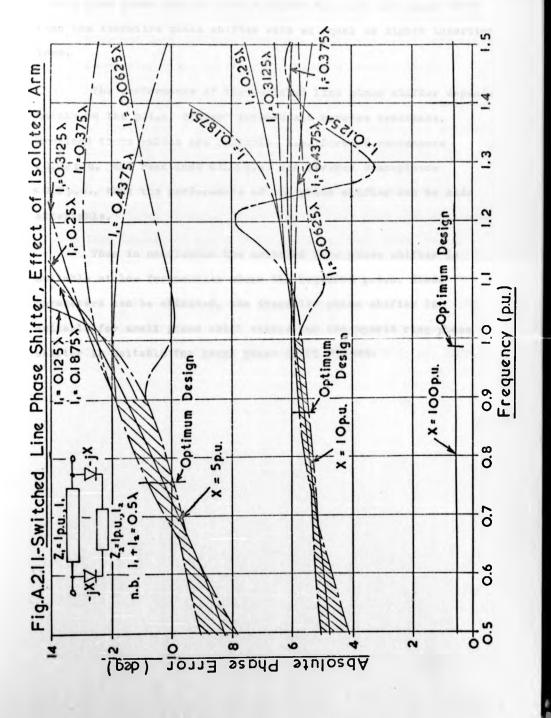

| A.2.4 SWITCHED LINE PHASE SHIFTER          | A.2.12 |

| A.2.5 CONCLUSIONS                          | A.2.14 |

| Appendix A.3                               |        |

| COMPUTATION TIMES ON ELLIOTT 4130 COMPUTER | page   |

| A.3.1 COMPUTATION TIMES                    | A.3.1  |

| A.3.1.1 Introduction                       | A.3.1  |

| A.3.1.2 Integer Operations                 | A.3.1  |

| A.3.1.3 Real Operations                    | A.3.2  |

| A.3.1.4 Complex Operations                 | A.3.2  |

| A.3.1.5 Mathematical Functions             | A.3.3  |

| A.3.1.6 Array Operations                   | A.3.3  |

| A.3.1.7 Data Structure Access              | A.3.4  |

| Appendix A.4                               |        |

| USER MANUAL FOR CHAIN MATRIX ANALYSIS      |        |

| CHAIN1 PROGRAM                             | page   |

| A.4.1 INTRODUCTION                         | A.4.1  |

| A.4.2 DECLARATION OF CIRCUIT SIZE          | A.4.1  |

| A.4.2.1 Main Title                         | A.4.1  |

| A.4.2.2 Maximum Size of Circuit            | A.4.2  |

| A.4.3 CIRCUIT TOPOLOGY STATEMENTS          | A.4.2  |

| A.4.3.1 Types of Circuit Acceptable        | A.4.2  |

| A.4.3.2 Network Statement                  | A.4.5  |

| A.4.3.3 Junction Statement                 | A.4.5  |

| A.4.3.4 Load Statement                     | A.4.7  |

| A.4.3.5 Ports Statement                    | A.4.9  |

| A.4.4 OUTPUT STATEMENT                     | A.4.10 |

| A.4.5 FREQUENCY STATEMENT                  | A.4.10 |

| 1434 fab littleman                         |        |

|                                            | nnge           |

|--------------------------------------------|----------------|

| A.4.6 VARIABLE STATEMENT                   | Page<br>A.4.10 |

| A.4.7 CIRCUIT STATEMENT                    | A.4.13         |

| A.4.8 TITLE STATEMENT                      | A.4.1+         |

| A.4.9 ANALYSIS STATEMENT                   | A.4.15         |

| A. 1. 10 TERMINATION STATEMENT             | A.4.15         |

| A.4.11 EXECUTION OF PROGRAM                | A.4.15         |

| A.4.12 RUN TIME ERRORS                     | A.4.16         |

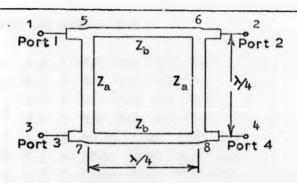

| A.4.13 EXAMPLE, 3dB BRANCH ARM HYBRID RING | A.4.17         |

| A.4.14 EXAMPLE, COAXIAL SHORT CIRCUIT      | A.4.22         |

| Appendix A.5                               |                |

| USER MANUAL FOR MIXED MATRIX ANALYSIS      |                |

| MICRO3 PROGRAM                             | page           |

| A.5.1 INTRODUCTION                         | A.5.1          |

| A.5.2 CIRCUIT TOPOLOGY STATEMENTS          | A.5.4          |

| A.5.2.1 Circuits                           | A.5.4          |

| A.5.2.2 Networks                           | Λ.5.4          |

| A.5.2.3 Junctions                          | A.5.9          |

| A.5.2.4 Ports                              | A.5.10         |

| A.5.2.5 Characteristic Impedances          | A.5.10         |

| A.5.2.6 Deletions                          | A.5.11         |

| A.5.3 FREQUENCY STATEMENT                  | A.5.11         |

| A.5.4 OUTPUT OPTIONS STATEMENT             | A.5.12         |

| A.5.5 ANALYSIS                             | A.5.14         |

| A.5.6 OTHER STATEMENTS                     | A.5.14         |

| A.5.6.1 End Statement                      | A.5.14         |

| A.5.6.2 Newrun Statement                   | A.5.14         |

| A.5.6.3 Label Statement                    | A.5.15         |

| A.5.6.4 Nofault Statement                  | A.5.15         |

| A.5.6.5 Structure Statement                | A.5.15         |

| A.5.7 CHANNEL ASSIGNMENT                   | A.5.15         |

| A.5.8 JOB PREPARATION                      | A.5.16         |

| A.5.8.1 Data                               | A.5.16         |

| A.5.8.2 Storage Requirements               | A.5.17         |

| A.5.8.3 Batch Processing                   | A.5.17         |

| A.5.8.4 Interactive use on Remote Teletype | A.5.18         |

| A.5.9 DATA ERRORS                          | A.5.20         |

| A.5.9.1 Data Preparation                   | A.5.20         |

| A.5.9.2 Syntax Errors                      | A.5.20         |

| A.5.9.3 Circuit Errors                     | A.5.21         |

| A.5.9.4 Messages                           | A.5.21         |

|                                                 | page   |

|-------------------------------------------------|--------|

| A.5.10 SYNTAX ERRORS                            | A.5.22 |

| A.5.11 CIRCUIT ERRORS                           | A.5.24 |

| A.5.12 RUN TIME MESSAGES                        | A.5.24 |

| A.5.13 EXAMPLE, 3dB BRANCH ARM HTBRID RING      | A.5.26 |

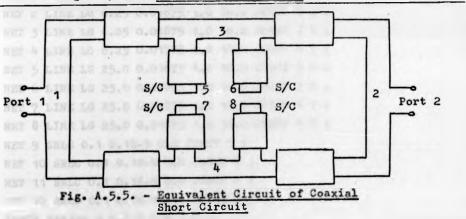

| A.5.14 EXAMPLE, COAXIAL SHORT CIRCUIT           | Λ.5.29 |

| Appendix A.6                                    |        |

| THE COMPUTER AIDED DESIGN OF MICROWAVE CIRCUITS | page   |

| paper presented at the Summer School on Circuit |        |

| Theory, Czechoslovakia, 1971                    | A.6.1  |

# Chapter 1

Specification of the Problem for the

Computer Aided Design of Microwave

Circuits

#### 1.1. MICROWAVE CIRCUITS

#### 1.1.1. Definition

The first question to ask is "What is a microwave circuit?". The first answer to this question could be that a microwave circuit is an assembly of components which carry electrical signals in the normal microwave region, i.e. 1GHz to 100GHz. This may appear to be a fairly good description but it is not really sufficient for this thesis.

For this thesis a microwave circuit could better be described as an assembly of components which require microwave techniques for their analysis. At low frequencies all electronic components can be characterised, at least for a small signal analysis, by an assembly of lumped components consisting of resistors, inductors, capacitors, dependant and independant voltage and current generators. This is not possible at microwave frequencies when disturbances in the circuit take a long time, comparable to the period of oscillation at the frequency being considered, to reach every part of the circuit. The microwave components thus become distributed in their nature and will propagate electromagnetic waves within their physical size and/or radiate electromagnetic energy into the surrounding medium. The terms voltage and current no longer have any well defined meaning and energy will travel to every part of the microwave circuit in the form of electromagnetic waves.

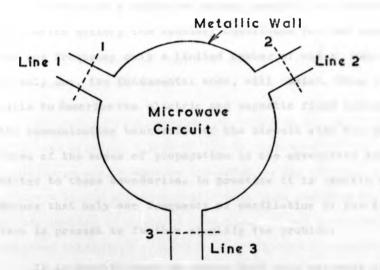

The definition of a microwave circuit given by Montgomery (1.1) states: "A microwave circuit is a region enclosed by a metallic wall of any shape and communicates with the exterior by way of a number of transmission lines or waveguides which may be called

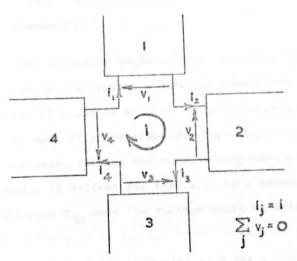

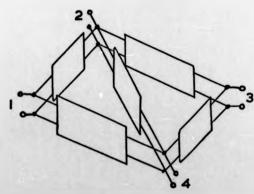

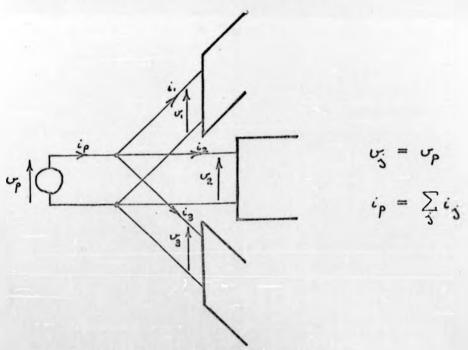

the terminals of the circuit.". This is illustrated for a 3-port microwave circuit in Fig. 1.1. At this stage we are dealing with a very generalised microwave circuit.

The next problem is to provide a complete description of the performance of the microwave circuit between the terminals, or ports, of the circuit. At low frequencies it is usually possible to relate voltages and currents at all the nodes in the circuit but for a microwave circuit, in general, this is not possible. The problem is that a microwave circuit communicates with the exterior by means of time varying electric and magnetic fields in the form of electromagnetic waves propagating in the lines or waveguides connecting the circuit to the exterior. Thus it is necessary to describe the circuit performance in terms of these fields on the boundary of the microwave circuit with the exterior. Thus the analysis of a microwave circuit involves the solution of a dynamic field problem where it is necessary to solve Maxwell's

Fig. 1.1. - Generalised 3-port Microwave Circuit

Equations (1.2), within the metallic walls forming the boundary of the microwave circuit, to give a relationship between the time varying electric and magnetic fields on all the communicating boundaries of the circuit with the exterior. In practice this dynamic field problem, except for trivial microwave circuits, is impossible to solve and thus it is necessary to try to simplify the problem so it can be solved.

#### 1.1.2. Circuit Ports

So far it has been necessary to talk in terms of the field patterns across the boundaries of the microwave circuit and the exterior and this requires some simplification. A microwave circuit usually communicates with the exterior via waveguides of some kind, e.g. coaxial lines, normal waveguides, striplines, etc., and we can usually assume that these lines extend to infinity outside the microwave circuit and have a uniform cross section. The field patterns in any waveguide of this type can be simplified into a summation of a number of modes, possibly an infinite number, which satisfy the boundary conditions for the waveguide. At any one frequency only a limited number of modes exist and often only one, the fundamental mode, will exist. Thus it is possible to describe the electric and magnetic field patterns on the communicating boundaries of the circuit with the exterior in terms of the modes of propagation in the waveguides externally connected to these boundaries. In practice it is usually necessary to assume that only one frequency of oscillation of the field pattern is present to further simplify the problem.

It is usually best to assume that only one mode of propagation is present in the waveguide connected to this circuit

with the orientation of that made defined but it may not be possible to completely define the circuit response in this way. An example of this is a circular waveguide which, in general, may carry, at one frequency, a number of modes at any orientation. This problem may be overcome by considering this type of problem as the superposition of a number of separate ports on the circuit

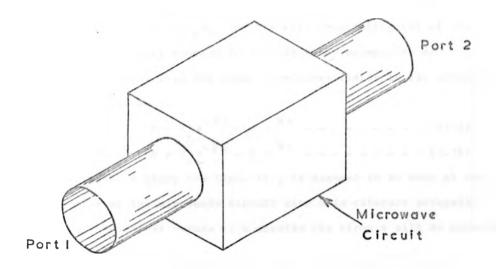

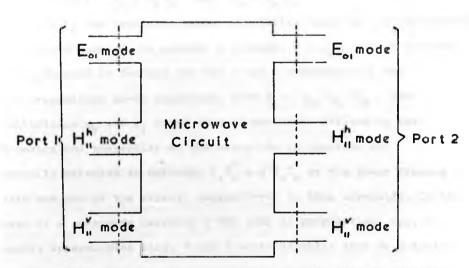

one port for each mode of propagation in the waveguides connected to the circuit. This is illustrated in Fig. 1.2 where in the exterior circular waveguides an  $E_{01}$  mode and an  $H_{11}$  mode may be present with the latter mode having a horizontal,  $H_{11}^h$ , and vertical,  $H_{11}^v$ , component. Thus the 2-port circuit in Fig. 1.2 could be considered as a 6-port circuit with one port for each mode of propagation in the circular waveguides as shown in Fig. 1.3.

#### 1.1.3. Description of Circuit Performance

So far we have arrived at describing a microwave circuit as an n-port network with each port carrying a given mode of propagation in the waveguides connecting it to the exterior. Now it is necessary to define the amplitudes of each mode and to describe the connection between all these modes on all the ports of the microwave circuit.

Initially it is necessary to consider the amplitudes of the electric and magnetic fields of the electromagnetic waves propagating in the waveguides connected to the circuit. In this case a single electromagnetic wave mode consists of two waves propagating in opposite directions in the waveguide with propagation constant, Y, which, in general, will be complex to include the attenuation of the waveguide or the presence of evanscent modes. Also the electric and magnetic fields transverse

Fig. 1.2. - Microwave Circuit Connecting

Circular Waveguides

Fig. 1.3. - Equivalent Circuit for Microwave Circuit in Fig. 1.2.

to the direction of propagation are related by the wave impedance for the waveguide, Z,, so that :-

$E_{+}=Z_{_{W}}H_{+}\quad\text{for the wave propagating into the circuit}$  and  $E_{-}=Z_{_{W}}H_{-}\quad\text{for the wave propagating out of the circuit}$  with  $Z_{_{W}}$  in general complex to include lossy waveguides or evanscent modes. Thus the total transverse fields in the waveguide for this mode is :-

$$E = E_{+} e^{-\mathbf{y}_{X}} + E_{-} e^{\mathbf{y}_{X}} - - - - - - - - (1.1a)$$

and

$$H = H_{+} e^{-\mathbf{y}_{X}} - H_{-} e^{\mathbf{y}_{X}} - - - - - - - - - (1.1b)$$

for distance x along the line. If x is assumed to be zero at the interface of the microwave circuit with this exterior waveguide then all practical values of x outside the circuit will be negative.

A more convenient way to write equations (1.1) for a circuit analysis is:

V, I and Z now represent scalar quantities which may be represented by complex numbers. In general a voltage,  $V = g_v E$ , and a current,  $I = g_i H$ , could be defined for the + and - components of the two propagating waves separately with  $Z_o = (g_v / g_i) Z_w$ . The multipliers  $g_v$  and  $g_i$  would then be constants defined by the geometry and properties of the waveguide in question and normally selected to maintain  $V_+ I_+^*$  and  $V_- I_-^*$  as the power flowing into and out of the circuit respectively in this waveguide. In the case of a waveguide carrying a TEM mode of propagation, i.e. a simple transmission line, V and I would normally also be selected as the voltage and current respectively on this line by suitable selection of  $g_v$  and  $g_i$ .

The most convenient way to describe a microwave circuit is to describe the electromagnetic wave or mode amplitudes flowing out of the microwave circuit as a function of the wave or mode amplitudes flowing into the circuit in every waveguide connected to the circuit. This is termed—the scattering parameter description of the circuit and this will be described in detail in section 1.2.2.

#### 1.1.4. Practical Mircowave Circuits

In this section a number of practical microwave circuits will be described from which a better understanding of the problems involved in the analysis of microwave circuits can be arrived at.

#### 1.1.4.1. Practical Experience in Circuit Synthesis and Analysis

The first 5 months on the thesis was spent at Microwave Associates Ltd., Inton and during this period experience in the synthesis and analysis of Microwave Integrated Circuits was obtained. The first problem involved the design of an L-band microwave integrated circuit switch (1.3) and this is described in Appendix A.1. The second problem involved a comparative study of various types of microwave integrated circuit phase shifters (1.4) and this is described in Appendix A.2.

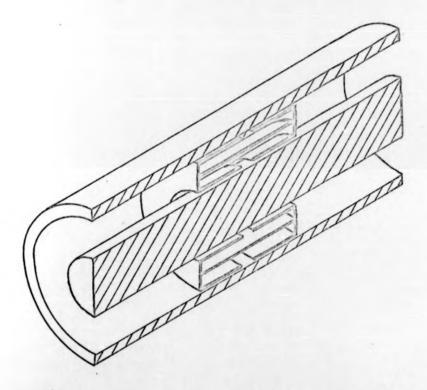

#### 1.1.4.2. Coaxial Plunger

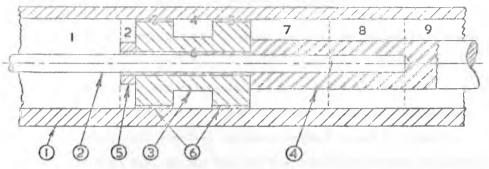

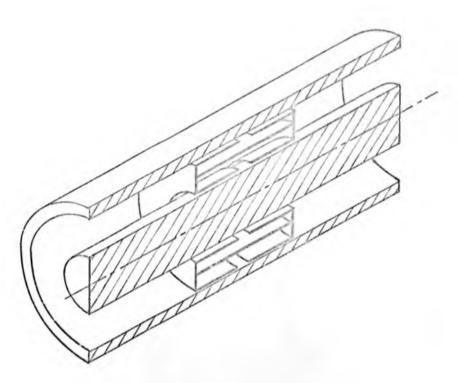

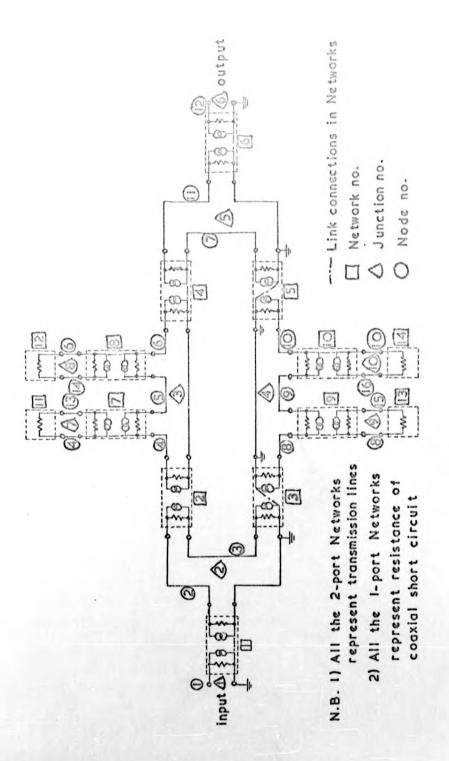

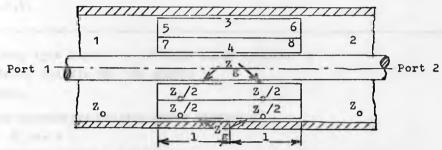

Fig. 1.4 shows a possible design for an adjustable coaxial plunger which is radially symmetric about its centre line and Fig. 1.5 shows its equivalent circuit for a TEM mode analysis. In the equivalent circuit the problem for analysis has been broken down into 9 separate sections consisting of a short section

N.B. The numbers in circles are the part numbers in the assembly whilst the others are for the equivalent circuit Fig. I.4. - Adjustable Microwave Coaxial Plunger

Fig.1.5. - Equivalent Circuit for Adjustable Microwave Coaxial Plunger

from an infinite length of coaxial line, for sections 1 to 7, and an inhomogenously filled circular waveguide, for sections 8 and 9. Each of these sections can be considered as a simple distributed transmission line within a 2-port network.

For a predominately Total mode analysis in the coaxial lines the connections of the networks in the equivalent circuit can be considered as a direct connection of voltage and current from the port of one network into the next as the wave propagates down the line, e.g. junctions between network 2 and 3, 3 and 4, 4 and 5 in Fig. 1.5. In the case of the junctions between networks 1 and 2 and 6, 5 and 6 and 7 the wave propagating down the line has to split between two networks. Also at the end of network 7 the line changes from a coaxial line into an inhomogenously filled circular waveguide in which it is assumed that two modes may propagate. Thus the 3-port network between network 7 and 8 will split the THY mode wave into the appropriate amplitudes of these two modes. Similarly the 4-port network between networks 8 and 9 will modify the amplitudes of these two modes as the inhomogenous filling of the waveguide changes. The effects of the discontinuities in the circuit, e.g. change in the field pattern between various radii on the coaxial lines, can usually be taken into account by including a 1-port network, e.g. a shunt susceptance, on the junctions between the networks in question.

### 1.1.4.3. Microwave Integrated Circuit Phase Shifter

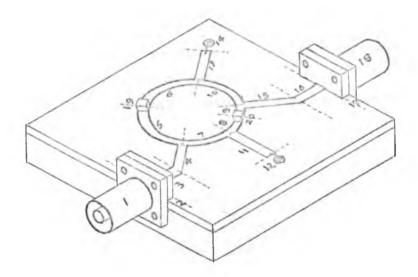

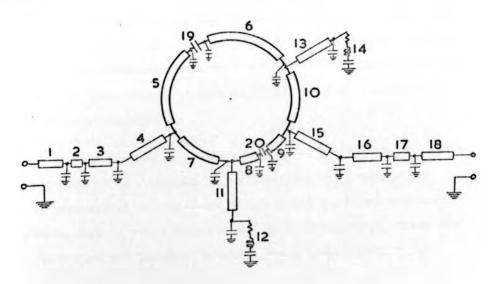

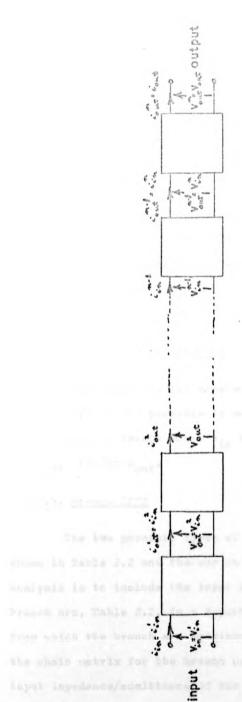

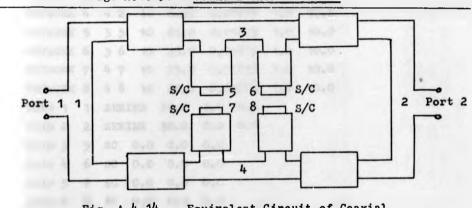

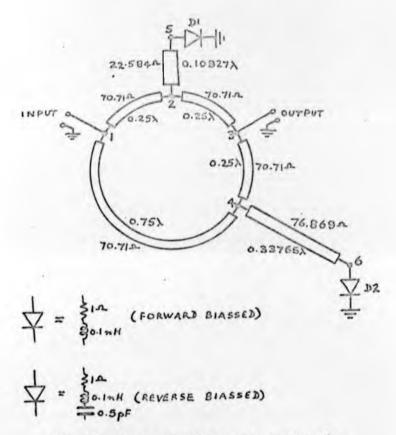

A practical microwave integrated circuit phase shifter is shown in Fig. 1.6. with its equivalent circuit in Fig. 1.7.

Fig.I.6.- Microwave Integrated Circuit

Phase Shifter

Fig.1.7.- Equivalent Circuit of Phase Shifter

This equivalent circuit consists of the following :-

- 1) Licrostrip transmission lines for networks 2 to 11,

13 and 15 to 17. N.B. It is often assumed that only a

TEM mode of propagation is present on the microstrip line.

- 2) p.i.n. diodes for networks 12 and 14.

- 3) d.c. isolating capacitors for networks 19 and 20.

#### 1.2. NICTOL V. CI-CUIT AND SIS

## 1.2.1. Annemblies of n-port Networks

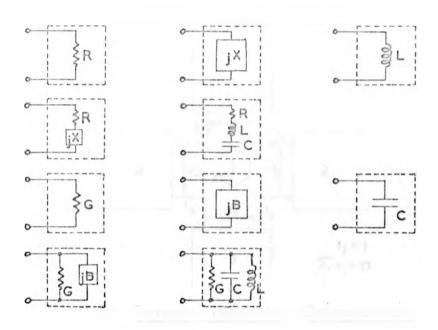

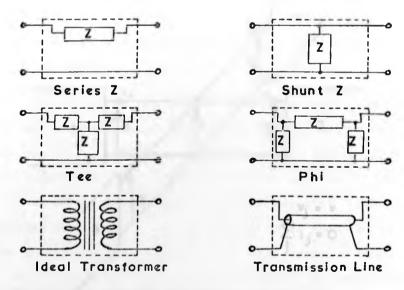

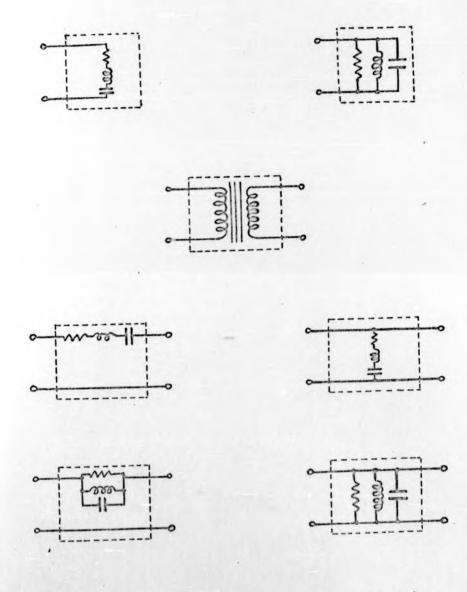

In section 1.1.4. various types of microwave circuits were presented and broken down for analysis. The complete circuit consisted of a single n-port network which could be broken down into an assembly of n-port networks each one of which was simpler to analyse on its own than the complete circuit. In a number of cases these n-port networks have a simple equivalent or approximate to a simple equivalent circuit, e.g. Tables 1.1 and 1.2. It should be noted that in a number of cases an equivalent circuit may only represent correctly the microwave component over a limited frequency range and often the component values in the equivalent circuit may vary in a complex manner with frequency.

In the analysis of assemblies of n-port networks, and in the final circuit, we are only interested in the amplitudes of the modes of propagation of the electromagnetic waves on each port of an n-port network. In practice it may be necessary to include an ideal transformer with unity turns ratio in cascade with each port on every n-port network to arrive at a more accurate equivalent circuit.

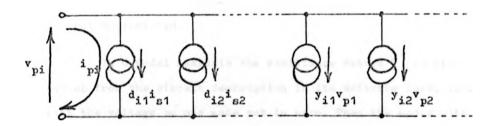

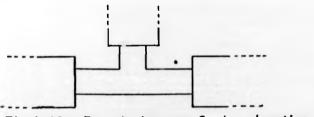

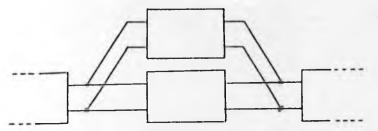

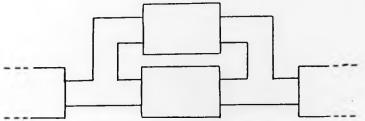

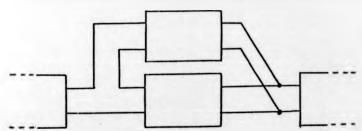

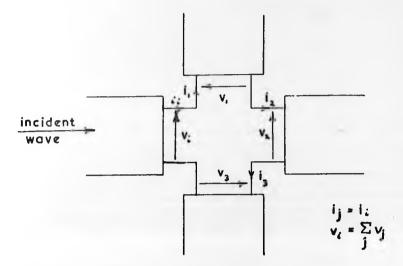

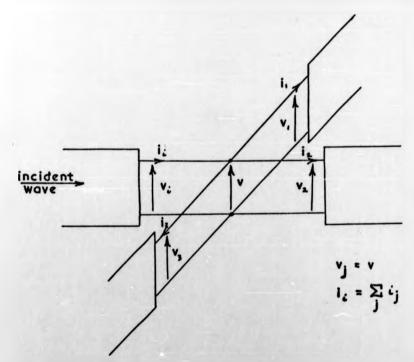

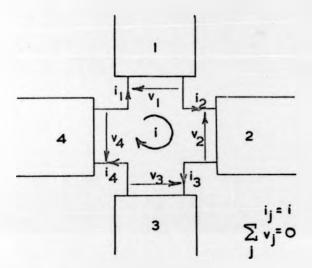

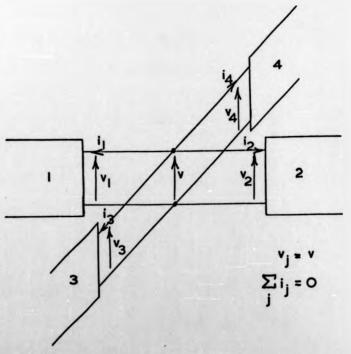

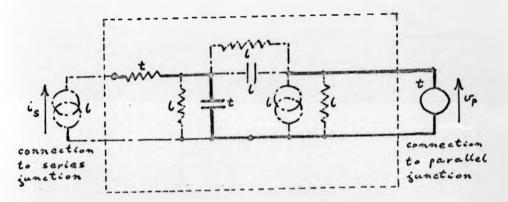

To analyse microwave circuits as an assembly of n-port networks it is necessary to consider how the networks are interconnected at junctions of the networks. There are two basic ways in which networks may be interconnected. These are the series and parallel junction connections as shown in Fig. 1.8 and 1.9 respectively. At a series junction the current is common and the voltages sum to zero whilst at a parallel junction the voltage is common and the currents sum to zero.

Table.I.I.- Simple I-Port Networks

Table. I.2. - Simple 2-Port Networks

Fig.I.8.- Series Junction Connection

Fig.1.9.- Parallel Junction Connection

There may be some types of junctions which may be a mixture of these two types but they can always be broken up into separate series and parallel junctions using 2-port connecting link networks as necessary.

For some microwave components an immediate relation between voltage and current at a junction connection can be seen either in terms of a series or parallel junction, e.g. for lines carrying a Tra. mode of propagation. For the interconnection of waveguides the terms voltage and current only have a meaning in so far as a meaning is defined for them, e.g. in a rectangular waveguide carrying H node the voltage could be defined as the voltage from the centre of the top of the waveguide to the centre of the bottom of the waveguide with the current defined so that vi represents the power flowing in the waveguide at that point. Thus the compatibility of the equivalent circuits of a number of microwave components must be decided before they are interconnected. In some cases another network, possibly an ideal transformer, may have to be included to make the networks compatible before they are interconnected at a junction in an equivalent circuit.

The results of interest to microwave engineers from a microwave circuit analysis program normally concern the amplitudes of the electromagnetic waves propagating in the waveguides connected to the circuit. All these results can easily be obtained from the scattering matrix for the n-port microwave circuit (1.5). To derive the scattering matrix for a microwave circuit it is necessary to define a characteristic impedance for each mode of propagation in each waveguide connected to the circuit. In general for a waveguide carrying a TEM mode the characteristic impedance

just defines the ratio of voltage to current between the two conductors of the waveguide. For other modes in waveguides the definition of the characteristic impedance is more arbitary but it must be compatible with the voltage and current defined for that mode in the waveguide. In general the characteristic impedance may be a complex number to allow for lossy propagation in the waveguide or evanscent modes of power transfer.

## 1.2.2. Wave and Power Scattering Matrices

For the microwave engineer it is necessary to present the results of a microwave circuit analysis in the form of a scattering matrix for an n-port network for, in general, a different complex characteristic impedance for each port. The resulting scattering matrix is then in the form:-

b = Sa

where b = column vector of reflected wave amplitudes

a = column vector of incident wave amplitudes

S = n x n scattering matrix

A problem arises in describing the scattering matrix for complex characteristic impedances due to the possibility of two different scattering matrices. One describes the amplitudes of the waves in the waveguides connected to the circuit and the other is in terms of the power flowing into and out of the circuit. This is due to the fact that a waveguide terminated in its characteristic impedance will not reflect a wave at its termination but it may not absorb the maximum power available whilst a waveguide terminated in the conjugate of its characteristic impedance will absorb the maximum power available but a reflected wave may still be produced.

## 1.2.2.1. Wave Scattering Matrix

For the wave scattering matrix the scattering parameters refer to the amplitudes of the electromagnetic modes of propagation propagating separately in the two directions in the waveguides connected to the microwave circuit, i.e.:-

Equations (1.4) and (1.5) have been arranged so that the waves propagating in opposite directions can be separated out as:-

$$V_{+} = (Z_0 R_0^{-\frac{1}{2}})a$$

and  $I_{+} = R_0^{-\frac{1}{2}}a$  for the incident wave.

$V_{-} = (Z_0 R_0^{-\frac{1}{2}})b$  and  $I_{-} = R_0^{-\frac{1}{2}}b$  for the reflected wave.

#### 1.2.2.2. Power Scattering Matrix

For power scattering the scattering parameters refer to the amplitude of the reflected power out of each port as a ratio of the maximum power available from the waveguides connected to the circuit. This gives  $\left|S_{ij}'\right|^2$  as the transducer gain between ports j and i of the microwave circuit (1.6). Thus:-

b' = S'a' - - - - - - - (1.6)

where, in terms of matrices, :-

$$a' = \frac{1}{2} R_{o}^{-\frac{1}{2}} (V + Z_{o} I) - - - - - - - (1.7a)$$

$$b' = \frac{1}{2} R_{o}^{-\frac{1}{2}} (V - Z_{o}^{*} I) - - - - - - - - (1.7b)$$

or

$$I = R_{o}^{-\frac{1}{2}} (a' - b') - - - - - - - - - (1.8a)$$

$$V = Z_{o}^{*} R_{o}^{-\frac{1}{2}} a' + Z_{o}^{*} R_{o}^{-\frac{1}{2}} b' - - - - - - - (1.8b)$$

From equation (1.8) the power into port i (subscript i) is:-

$$= \operatorname{Re}(V_{\underline{i}} I_{\underline{i}})$$

$$= |a_{\underline{i}}|^2 - |b_{\underline{i}}|^2$$

If the input is pedance of port i is  $Z_{oi}^*$  then  $b_i = 0$  and thus for any input impedance on port i :-

$$\begin{vmatrix} a_i \end{vmatrix}^2$$

= incident power on port i

$\begin{vmatrix} b_i \end{vmatrix}^2$  = reflected power on port i

## 1.2.2.3. Mave/Power Scattering Conversion

Equating equations (1.5) and (1.8) and rearranging gives :-

## 1) Wave to Power Conversion

$$\begin{bmatrix} a \\ b \end{bmatrix} = \begin{bmatrix} R_0^2 & 0 \\ j R_0^{-1} X_0 & 2 \end{bmatrix} \cdot \begin{bmatrix} a \\ b \end{bmatrix} - - - - - (1.9)$$

substituting b and b from equations (1.4b) and (1.7b) gives:-

$$S' = (SR_0 + jX_0)Z_0^{-1} - - - - (1.10)$$

## 2) Power to Wave Conversion

$$\begin{bmatrix} \mathbf{a} \\ \mathbf{b} \end{bmatrix} = \begin{bmatrix} \mathbf{Z}_{\mathbf{o}}^{-1} \mathbf{R}_{\mathbf{o}} & \mathbf{0} \\ -\mathbf{j} \mathbf{Z}_{\mathbf{o}}^{-1} \mathbf{X}_{\mathbf{o}} & \mathbf{2} \end{bmatrix} \cdot \begin{bmatrix} \mathbf{a} \\ \mathbf{b} \end{bmatrix} - - - - - - (1.11)$$

substituting b and b from equations (1.4b) and (1.7b) gives :-

$$S = (S' Z_o - j X_o) R_o^{-1} - - - - - (1.12)$$

It should be noted that if all the terms in  $Z_0$  are real, i.e.  $Z_0 = R_0$  and  $X_0 = 0$ , then both the wave and power scattering parameters are the same, i.e. a = a, b = b and S = S.

#### 1.2.3. Presentation of Results

The main circuit performance results of interest to the microwave engineer are shown in Table 1.3 with the formulae for

|                                         | From Wave<br>Scattering Matrix                                                                        | From Power<br>Scattering Matrix                                             |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Wave Scattering Parameter, S            | S <sub>ij</sub>                                                                                       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                        |

| Wave Reflection<br>Coefficient, T       | S <sub>ii</sub>                                                                                       | (s <sub>ii</sub> z <sub>oi</sub> -jx <sub>oi</sub> ) R <sub>oi</sub>        |

| Voltage Standing Wave Ratio, VSWR       | 1 +  s <sub>ii</sub>  <br>1 -  s <sub>ii</sub>                                                        | $\frac{1 +  S_{ii} }{1 -  S_{ii} }$                                         |

| Input Impedance, Z <sub>INi</sub>       | Z <sub>oi</sub> 1 + S <sub>ii</sub> 1 - S <sub>ii</sub>                                               | $R_{0i} = \frac{1 + S_{ii}^{\dagger}}{1 - S_{ii}^{\dagger}} - jX_{0i}$      |

| Power Scattering Pararameter, S         | SRZ-1 for i ≠ j ( for i = j see T; )                                                                  | s <sub>ij</sub>                                                             |

| Reflection<br>Coefficient, $\Gamma_i^i$ | (S <sub>ii</sub> R <sub>oi</sub> + j X <sub>oi</sub> ) Z <sub>oj</sub>                                | s <sub>ii</sub>                                                             |

| Transducer Gain, P <sub>Tij</sub>       | $\left  R_{oj} Z_{oj}^{-1} S_{ij} \right ^2$                                                          | s <sub>ij</sub>   <sup>2</sup>                                              |

| Return Loss,                            | $\left  \left( s_{ii} R_{oi} + j X_{oi} \right) Z_{oj}^{-1} \right ^{2}$                              | (s <sub>ii</sub> ) <sup>2</sup>                                             |

| Power Gain, PGij                        | 1 - R <sub>Li</sub>                                                                                   | $\frac{ s'_{ij} ^2}{1 -  s'_{jj} ^2}$                                       |

| Available Gain,<br>P <sub>Aij</sub>     | 1 - R <sub>Lj</sub>                                                                                   | $\frac{ s'_{ij} ^2}{1 -  s'_{jj} ^2}$ $\frac{ s'_{ij} ^2}{1 -  s'_{ii} ^2}$ |

| Insertion Gain, P                       | $\left  \frac{z_{oi} + z_{oj}}{z_{oi} - z_{oj}^*} P_{Tij} \right ^2$                                  | $\left  \frac{z_{oi} + z_{oj}}{z_{oi} - z_{oj}^*} s_{ij}^* \right ^2$       |

| Insertion Phase,                        | Arg(S <sub>ij</sub> ) - Arg(Z <sub>oj</sub> )<br>+ Arg(Z <sub>oi</sub> + Z <sub>oj</sub> )<br>for i≠j | Arg(S <sub>ij</sub> ) + Arg(Z <sub>oi</sub> + Z <sub>oj</sub> )             |

N.B. The results of gain and return loss are often quoted in dB. To obtain these in dB then use 10 log(power ratio)

Table 1.3. - Results Obtainable from the Scattering Matrices

their derivation in terms of both the wave and power scattering parameters. For the evaluation of these parameters all the ports of the microwave circuit are terminated in the characteristic impedance for these ports unless otherwise stated.

The definitions of the results in Table 1.3 are as follows :-

- 1) wave scattering para eter,  $s_{ij} = \frac{\text{amplitude of wave reflected}}{\text{on port i}}$

- 2) wave reflection coefficient,  $T_i = \frac{\text{amplitude of wave reflected}}{\text{amplitude of wave incident}}$  on port i

- 3) voltage standing wave ratio, VSJR<sub>i</sub> = maximum electric field along line on nort i minimum electric field along line on port i

- $I_{+}$ ) input impedance,  $Z_{INi} = \frac{\text{voltage on port i}}{\text{current into port i}}$

- 5) power scattering parameter, S<sub>ij</sub> = amplitude of power wave reflected on port i amplitude of power wave incident on port j

- 6) reflection coefficient, T<sub>i</sub> = amplitude of power wave reflected on port i amplitude of power wave incident on port i

- 7) transducer sain, P<sub>Tij</sub> = power out of port i power available from port j

- 8) return loss,  $R_{Li} = \frac{\text{power out of port i}}{\text{power available from port i}}$

- 9) power gain, P<sub>Gij</sub> = power out of port i power into port j

- maximum power available from port i

10) available gain, FAij = maximum power available from port j

power available from port j

- 11) insertion gain, P<sub>Iij</sub> = power out of port i with network inserted power out of port i with ports i and j connected directly

- 12) insertion phase,  $\Theta_{\text{Iij}}$  = ( phase of current out of port i with the network inserted ) ( phase of current out of port i with ports i and j connected directly )

The Pleasure Clerk! The State of the

rents of placement appropriate in a second street of the second s

## 1.3. COLPUTER ADDID DESIGN OF BICROLLYS CIRCUITS

#### 1.3.1. Introduction

If we look at the possible requirements of a prospective user of computer aided design he would usually like the computer to design a microwave circuit to fulfil a set of performance requirements. In fact ideally he would like the computer to produce a suitable circuit design from a set of performance requirements. This can be done for special cases, e.g. for some filter circuits, where the equations for the synthesis are well defined for a given type of circuit but for general circuit design this is not possible. In practice the user would have to define or guess an initial circuit topology with the component values in that circuit. Then he could analyse this circuit on the computer to see if it fulfilled his performance requirements. If it did not then the circuit component values could be modified either manually or automatically in an optimisation routine to try to improve the circuit performance. In very complex circuits the user may prefer to design and analyse each part of the circuit in turn before analysing the entire circuit.

#### 1.3.2. Microwave Circuit Description

Ideally one would like to include provision for the entire range of microwave components in a computer program for the small signal linear analysis of microwave circuits. The main problem here is the very large number of microwave components which could be included most of which could best be described by their physical dimensions. In section 1.1.4. each microwave component was represented by an n-port network and thus this is the way microwave components should be entered in a computer program for the analysis of microwave circuits.

## 1.3.3. Circuit Analysis Frocedure

The objective of a circuit analysis procedure would be to provide results describing the circuit performance and, for microwave circuit analysis, it would have to consist of 2 parts as follows:-

- 1) From the data describing each microwave component form its description into an n-port network either in terms of a single matrix describing that n-port network or a simple equivalent circuit within an n-port network.

- 2) Use a circuit analysis method to analyse the circuit which now consists of an assembly of n-port networks.

For a circuit analysis on its own it is usually best to supply the user with a table of results of the circuit performance printed out for a set of frequencies defined by the user.

Alternatively if an optimisation procedure is to be used then it is necessary to analyse the circuit and compare its performance with the desired performance of the circuit from which the optimisation procedure can adjust the circuit component values to try and improve the performance of the circuit.

#### 1.3.4. Optimisation

In a circuit design it is usually impractical to let the user adjust the circuit component values manually to improve the circuit performance, particularly if a large number of component values may be adjusted. For this type of work there are a large number of optimisation procedures available which could be used and the main problem is to choose the best onc(s) to use for the optimisation of microwave circuits.

## 1.3.5. The Computer Program

design is on batch processing using the card or paper tape reader for the input data and the line printer for the results. Unfortunately the user often meets with problems in using this tyre of program. He will often make errors in preparing his data and he will normally take a long time to find and correct these errors. Thus often 2 or 3 runs are required on each problem and each run may take several hours, or even days, between the time it is handed in for a run on the computer and the time it is return with the results of the run. Also all he will get is the results in tabular from from which he will often have to plot graphs before he can decide whether the circuit performance is acceptable. Then, if the results of the circuit description and rerun the program with the new data.

An improvement to this method is the use of the program interactively on an on-line remote teletype. This has the advantage that the user can type all his data in directly to the program and have his results printed out directly on the remote teletype. This is extremely slow in terms of real time but if the computer is a multi-access machine then only about 2 to 3 times the processor time on batch processing will be used and the user will be able to see the results immediately after which he can decide to accept the present design or to try and improve the circuit design.

The remote teletype may seem very desirable but the user of it will soon ask for more interactive facilities from the

computer program. In using a remote teletype the user would often make errors in the data and he would like to be able to correct errors without terminating the run. Thus the user would like data checking to be included in the program to enable him to do this. Also he may wish to compose the input data as he types it in. In this case the data would have to be very meaningful to him and ideally he may prefer to use a complete problem orientated programming language for microwave circuit analysis which would be very easy for him to read and understand the data and would print out the details of any errors in the data for their immediate correction.

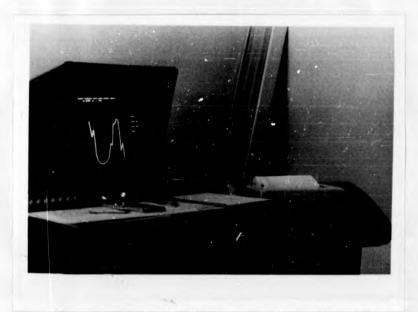

So far the results would still be printed out in a tabular form. This is not very convenient as it would normally take a long time to decide if the results are acceptable or to decide what to do to improve them by altering the circuit description. This problem could be overcome by the use of a visual display, normally placed next to the remote teletype, on which graphs of the circuit performance could be plotted.

In the programs described in this thesis, particularly the graphical display version of the MICRO3 program, most of these objectives have been achieved and the MICRO3 program can be used, with full data checking, on batch, interactively on a remote teletype, or on a remote teletype with a graphical display next to it.

## 1.4. PRESERVED RAIS FOR MIGROWAVE CIRCUIT MALMERS

## 1.4.1. Introduction

The programs previously written for the analysis of microwave circuits neatly fall into two classes.

The first class consists of the programs written for the analysis of microvave circuits which consist mainly of a cascade of 2-port networks. A large number of the simpler microwave circuits fall into this class as most microwave circuits involve the propagation of a wave or signal from the input port of the circuit to the output port with the signal being 'processed' by each part of the cascade in turn. It is usually fairly easy to transform this type of problem into a cascade of 2-port networks so a chain matrix method of analysis (1.7) can be used. In a number of programs using chain matrix analysis the method of analysis has been extended to include branch arms and/or parallel paths of cascades of 2-port networks on top of the main cascade of 2-port networks in the circuit.

The second class consists of programs written entirely for the analysis of lumped element circuits. In this case the circuit consists of a number of branch components connected between nodes in the circuit. Each branch may include a resistor, inductor, capacitor, independant and dependant voltage and current generators, mutual coupling for inductors etc.. The methods of analysis used are usually a nodal analysis (1.8) or, more recently, a mixed mesh and cutset analysis (1.9) in which a matrix equation relating all the variables in the circuit, e.g. node voltages and currents, is set up and reduced to give a set of equations relating the

voltages and currents in the independant voltage and current generators in the circuit. To maintain continuity some programs of this type have been extend for use in the microwave region by replacing the microwave components in the circuit by their lumped element equivalent circuits.

The main points of most of the previous programs for microwave circuit analysis have been outlined here but there is still a need to consider the ways in which the programs can be used, e.g. data format, results provided, interactive use, etc..

1.4.2. Chain latrix Analysis Programs

N.B. In this thesis the level of a program refers to the facilities provided by the program for design work.

1.4.2.1. MINICPH

This program was written by McPhun (1.10) and was designed for the analysis of microwave reflection amplifiers and later extended for other circuits. It is a low level program written in Algol for an Elliott 503 computer. It includes 2-port networks only containing single R, L or C components, stub transmission lines and tunnel diode equivalent circuits. The program will analyse circuits consisting of a cascade of 2-port networks with branch arms to any level either connected to the main cascade in series or shunt.

The order in which the data is read defines the topology of the circuit and this data consists entirely of numbers, except for one title string. Thus the program is difficult to use and very sensitive to data errors. The results are in tabular form giving the frequency response over a frequency range defined by the user with up to 10 possible options included consisting of input impedance, reflection coefficient and insertion loss.

## 1.4.2.2. FILTAN

This program was written by Green (1.11). It is a medium level program written for a time sharing computer using a remote teletype and the user can interact to a certain extent with the running of the program. The program includes 2-port networks only containing transmission lines, stub lines and series and shunt R. L. C combinations of components. The program will handle up to 60 networks assembled in a cascade between the input and output ports of the circuit with branch arms, series or shunt connected, and parallel paths, shunt connected only, to a level of 3 on the main cascade. The order of the input data defines the topology of the circuit and the input data includes 3 letter words to describe the network types and their topology. Command words are used in the data to control the running of the program and to edit the circuit description. Thus the program is easy to use and not too sensitive to data errors. The output is in tabular form over a frequency range defined by the user with a set number of output options, i.e. VSWR, transmission loss and phase and input resistance and reactance.

## 1.4.2.3. DIFNET

This program was written by Parker (1.12). It is a low to medium level program written for a time sharing computer using a remote teletype terminal and the user can interact to a certain extent with the running of the program. The main advantage of this program is the large number of network types in the program including 2-port networks containing current and voltage generators, ideal transformers, uniform and radial coaxial lines, strip lines, coaxial step discontinuities, composite lines, R, L and C components, chain and S parameters. The circuit may include branch arms and

parallel paths connected either in series or shunt. The order in which the data is read defines the topology of the circuit and the data consists of a title followed by a list of numbers. Thus the data is at a low level with a small amount of data checking in the program. The results output at each frequency consists of the frequency value followed by up to three selected output options printed out at selected points in the network.

## 1.4.3. Electronic Circuit Analysis Programs

#### 1.4.3.1. ECAP

This was possibly the original general purpose electronic circuit analysis program, written by IBM (1.13), designed, at least initially, for batch processing. It is a medium level program and it is complete package including linear, d.c., a.c. and transient analysis for a lumped element circuit and uses a nodal method for the a.c. analysis. The data for the program includes a number of words and data checking is included. Thus the program is simple to use and the circuit is defined by a number of branches connected between nodes in the circuit with each branch consisting of lumped components. The results from the program consist of all the voltages at every node and all the currents in every branch in the circuit. In addition extra facilities are available, e.g. sensitivity analysis, worst case analysis.

## 1.4.3.2. REDAP31

This program was developed by Redac Software Ltd. (1.14) for the analysis of electronic circuits. It is a high level program designed to analyse any meaningful lumped element electronic circuit. The program uses a mixed mesh and cutset analysis

developed by Branin (1.9). The circuit to be analysed consists of lumped components, transmission lines included as 3-terminal, 2-port networks described by an admittance or scattering matrix and several electronic components, e.g. transistor equivalent circuits, from a data bank may be include. The input data is at a high level including a large number of words with full data checking and the program is thus easy to use. The output is in tabular form over a frequency range defined by the user. Most of the output options included are those of interest to the designer of electronic circuits. Also there are a number of extra facilities included, e.g. sensitivity analysis, worst case analysis, monte carlo analysis and optimisation. A recent addition is that the program can be used on-line interactively on a remote teletype.

#### 1.4.3.3. BELNAP

This program was written by Davieau (1.15,1.16) and it appears to be a medium to high level program. It is designed for the analysis of a circuit consisting of a number of sub-circuits each one of which is described as an n-terminal device described by an admittance, imperance, scattering, h-parameter or chain matrix. Normal lumped components are also included. A nodal method of analysis is used to obtain a frequency response of the circuit over a defined frequency range. The data includes a numbers a number of words and thus the program is easy to use and the output is in tabular form or as a graph produced on a microfilm plotter.

as it is an elementary fraction program and sub-roughly an action of

## 1.5. CONCLUSIONS

The objective of this chapter was to outline the way in which the problem of the Computer Aided Design of Microwave Circuits should be tackled.

Firstly from an investigation into the general form of microwave circuits it was found that the entire microwave circuit could best be described as an n-port network. The results of interest to the microwave engineer in terms of the performance of this circuit is the relationship between the amplitudes of the modes of propagation on the waveguides or transmission lines connected to the ports of the circuit. These amplitudes can be best described in terms of the scattering parameters of the circuit.

The analysis of the circuit itself can be best tackled by breaking the general microwave circuit, as an n-port network, into an assembly of n-port networks. Each of these n-port networks representing a part or component used in the microwave circuit. Thus it is necessary to analyse an assembly of n-port networks and provide the results in terms of the scattering parameters of the circuit. The methods used so far for the analysis of electronic circuits including, in some cases, microwave circuits has been the chain matrix method of analysis or the nodal method of analysis. Thus it will be necessary to decide on the best method of analysis to use for microwave circuits.

The organisation of a computer program for microwave circuit analysis will be decided by the types of microwave circuits to be handled and the method of analysis used but in addition to this it is necessary to provide interactive facilities in the program so it is an interactive design program and not simply an analysis program.

#### References

- 1.1) C.G. Montgomery, R.H. Dicke, E.M. Purcell, 'Principles of Microwave Circuits', Dover, 1965

- 1.2) S. Ramo, J.R. Whinnery, T. Van Duzer, 'Fields and Waves in Communication Electronics', Wiley, 1965, Chapter 4, pp. 228-269

- 1.3) B.G. Marchent, 'Computer Aided Design of an L-Band M.I.C.

Switch', Microwave Associates Ltd., Luton, 1969, Technical

Report No. 160, (see also Appendix A.1)

- 1.4) B.G. Marchent, 'A Comparative Study of the Iterative, Hybrid Ring and Switched Line Microwave Phase Shifters', Microwave Associates Ltd., Luton, 1969, private communication, ( see also Appendix A.2 )

- 1.5) 'S-Parameters Circuit Analysis and Design', Hewlett Packard,

Application Note No. 95, Sept. 1968

- 1.6) L. Weinberg, 'Fundamentals of Scattering Matrices', Electro-Technology (USA), Vol. 80, July 1967, pp. 55-72

- 1.7) D.A. Calahan, 'Computer Aided Network Design', McGraw-Hill, 1968, pp. 36-39

- 1.8) E. Wolfendale, 'Computer-Aided Design Techniques', Iliffe, 1970, Chapter 2, pp. 15-50

- 1.9) F.H. Branin, 'Computer Methods of Network Analysis', Chapter 3 in F.F. Kuo, W.G. Magnuson, 'Computer Oriented Circuit Design', Prentice-Hall, 1969, pp. 71-122

- 1.10) M.K. McPhun, 'A Computer Program for the Analysis of Branched Distributed and Lumped Circuits', IEE Conference Publication No. 23, 1966, pp. 89-124

- 1.11) P.E. Green, 'General Furpose Programs for the Frequency

Domain Analysis of Microwave Circuits', IEEE Trans. on

Microwave Theory and Techniques, Vol. MTT-17, No. 8,

August 1969, pp. 506-514

- 1.12) W.H. Parker, 'DIPNET: A General Distributed Parameter

Network Analysis Program', IEEE Trans. on Microwave Theory

and Techniques, Vol. MTT-17, No 8, August 1969, pp 495-505

- 1.13) H.M. Wall, C.O. Harbourt, 'ECAP: A Matrix-Oriented Approach to Network Analysis', Chapter 1 in G.W. Zobrist, 'Network Computer Analysis', MacDonald, 1969, pp. 1-77

- 1.14) 'REDAP31: General Circuit Analysis Program (Redacal Version )',

Redacal Manual, Vol. 1, Redac Software Ltd., Tewkesbury

- 1.15) G.J. Herskowitz, 'Computer-Aided Integrated Circuit Design', McGraw-Hill, 1968, Chapter 4

- 1.16) M.A. Murray-Lasso, E.B. Kozemchak, 'Microwave Circuit Design by Digital Computer', IEEE trans. Microwave Circuits and Techniques, Vol. MTT-17, No. 8, Aug. 1969, pp. 514-526

# Chapter 2

Circuit Analysis for Microwave Circuits

#### 2.1. INTRODUCTION

In this chapter the methods of circuit analysis which any to used for the small simal linear analysis of microwave circuits in the frequency domain are considered. The objective is to choose the best method of analysis which:-

- 1) will handle all microwave circuits and components,

- 2) gives the correct, or at least an accurate, solution for any meaningful circuit,

- 3) uses the minimum number of operations and computation time on the computer and

- 4) is easy to program.

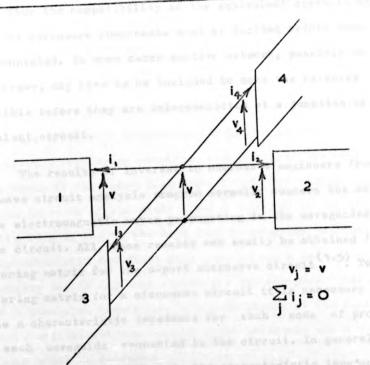

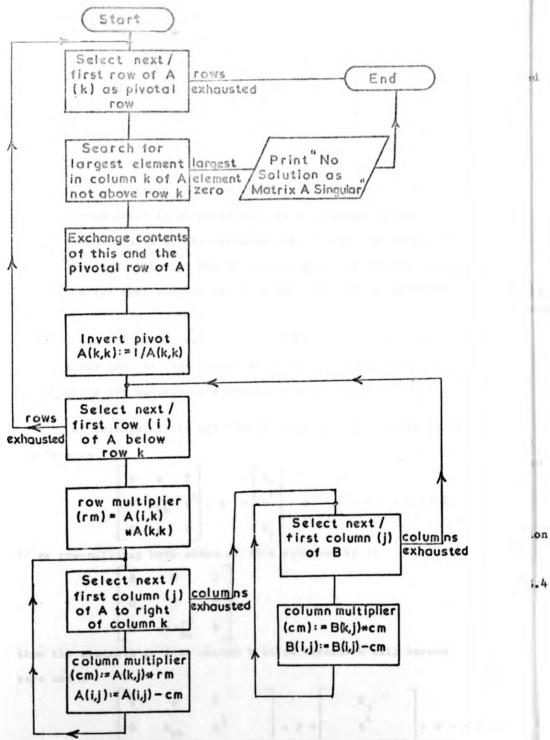

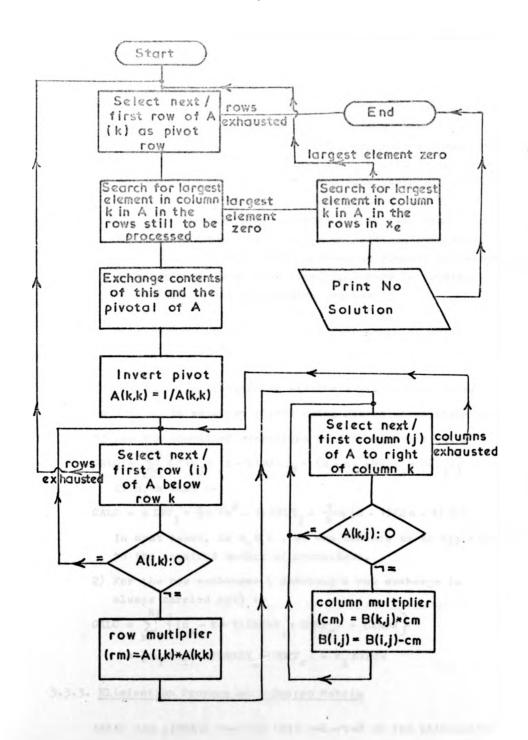

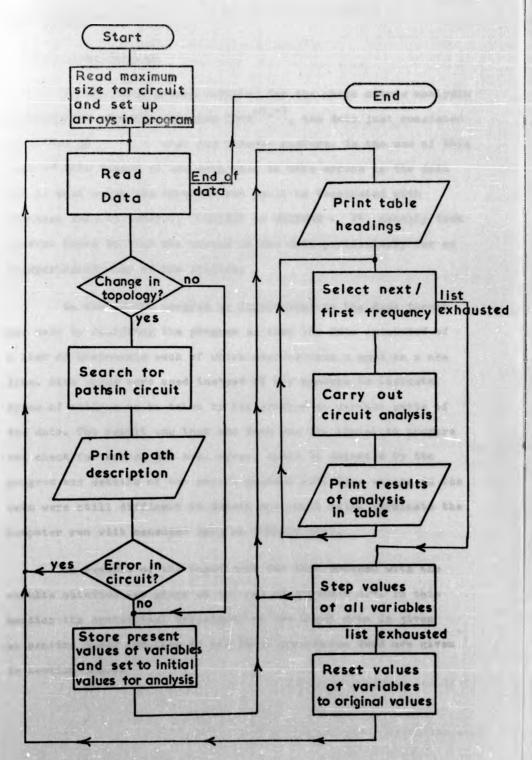

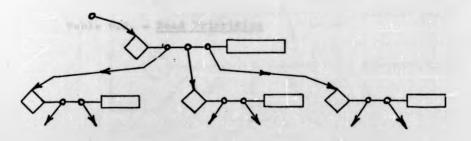

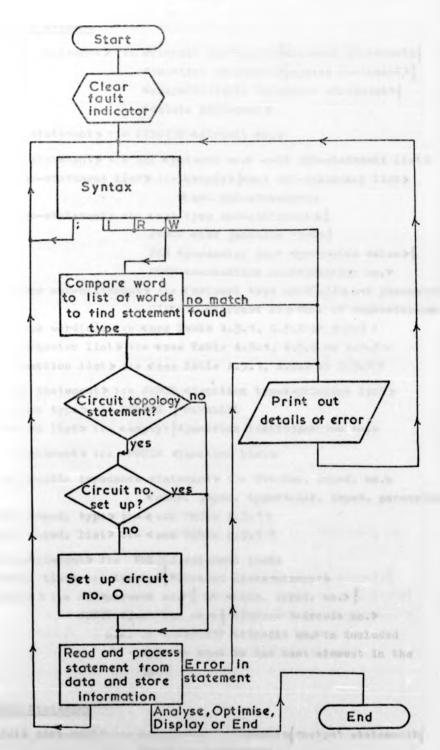

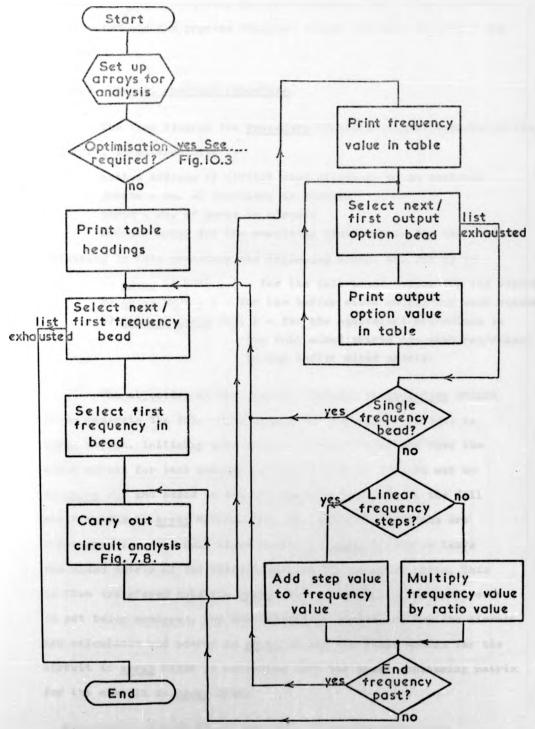

A flow diagram for a microwave circuit analysis program which will produce a table of results of the circuit performance is shown in Fig. 2.1. The method of analysis is not defined here but the flow diagram is applicable to most methods of analysis. The problems discussed in this chapter are the analysis part of the flow diagram shown within the dotted lines in Fig. 2.1.

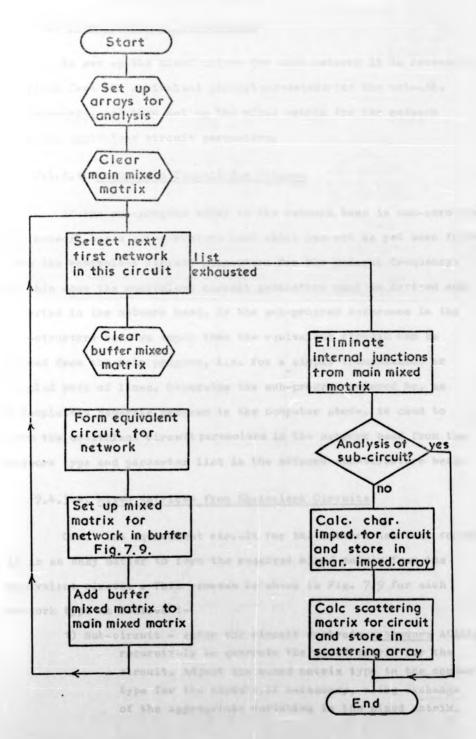

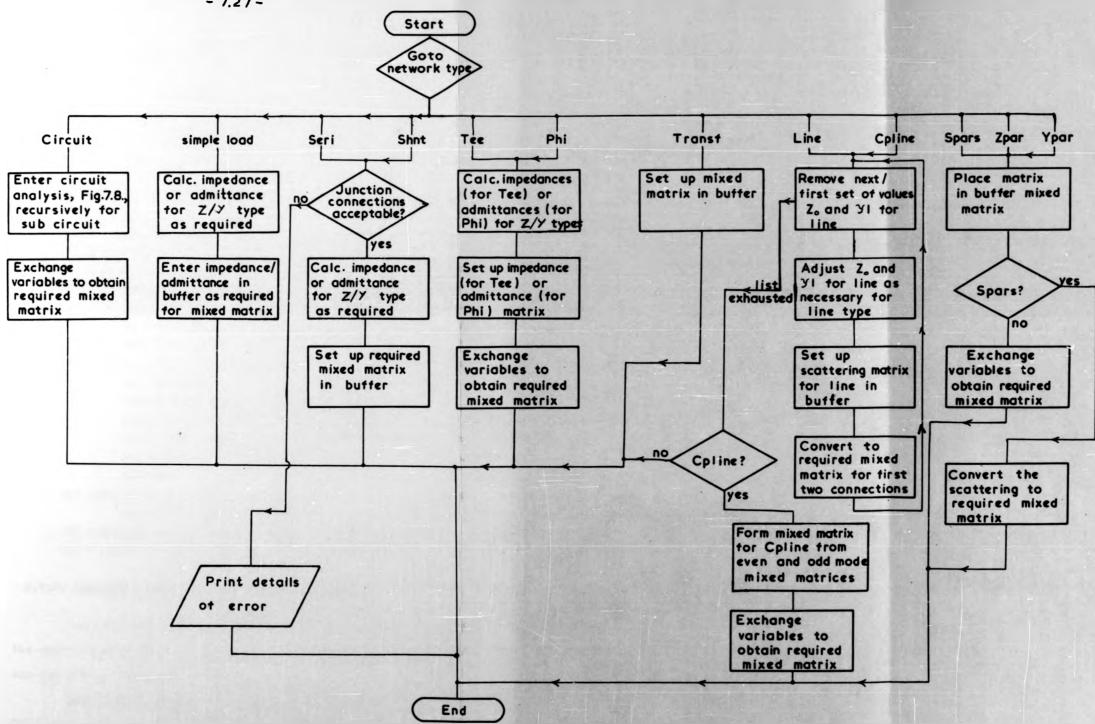

The previous programs for the computer aided design of microwave circuits, section 1.4, have either used a chain matrix method of analysis or a nodal method of analysis. In section 2.2 the chain matrix method of analysis is described and in section 2.3 the nodal method of analysis is described for microwave circuit analysis. In chapter 1 the problems involved in microwave circuit analysis were described in a very general way as the analysis of an assembly of n-port networks. In section 2.4 a new method of analysis termed mixed matrix analysis is described which was developed for the analysis of n-port networks. In this thesis the chain matrix method of analysis was used in the CHAIN1 program, described in chapter 5, and the mixed matrix method of analysis was used in the KICRO3 program described in chapter 7.

Fig. 2.1.-Flow Diagram for Microwave Circuit Analysis

In this chapter reference will often be made to the number of operations required in a calculation. For this an equation using the term CALC on the left hand side and a list of operations on the right hand side will be given. The CALC equation may also be followed by a TIME equation giving the time for this set of operations in  $\mathcal{M}s$  for the Elliott 4430 computer with a  $2\mathcal{M}s$  store. The meaning of the operations given in the CALC equations and their computation times are given in Appendix A.3. To simplify some of these expressions the times for array access have been ignored.

To compare the performance of the various methods of analysis the computation times have been derived for each method of analysis for two practical examples :-

- 1) a cascade of n 2-port networks, Fig. 2.4, and

- 2) a non-contacting coaxial short circuit, Fig. 2.2, with its equivalent circuit shown in Fig. 2.3.

- N.B. Most of the 2-port parameters and transformation for networks in this chapter are also described by Paul (2.1).

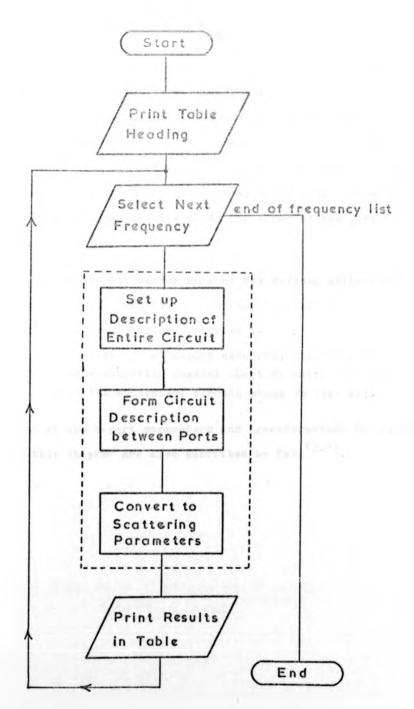

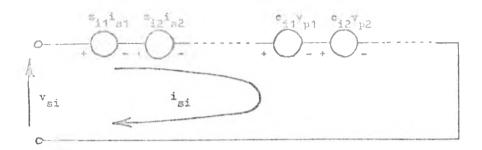

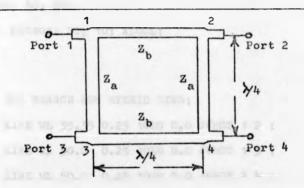

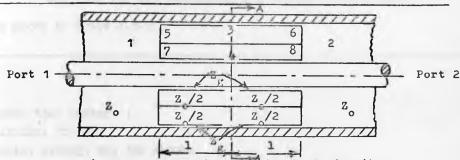

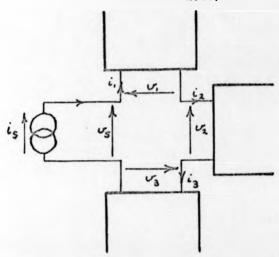

Fig. 2.2.- Non Contacting Coaxial

Short Circuit

Fig. 2.3.- Equivalent Circuit for Coaxial Short Circuit

## 2.2. CHAIN HATRIX ANALYSIS

#### 2.2.1. Introduction

The objective of a chain matrix method of analysis is to analyse a circuit as far as possible in terms of chain matrices. Chain matrix analysis is designed basically for the analysis of simple cascades of 2-port networks but it is possible to extend it application to more generalised circuits.

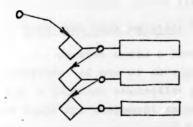

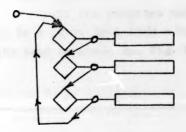

For a chain matrix analysis the circuit must consist initially of an assembly of 2-port networks. It is then necessary to break this assembly down into a simple cascade of 2-port networks between the input and output ports of the circuit.

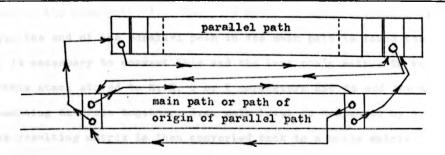

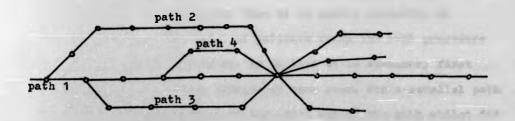

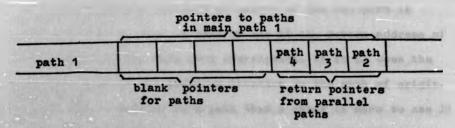

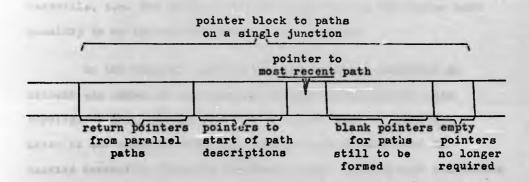

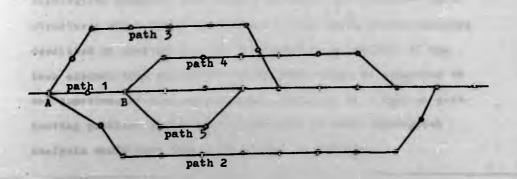

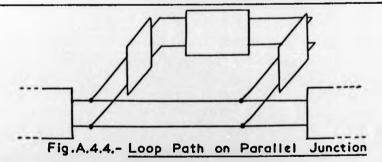

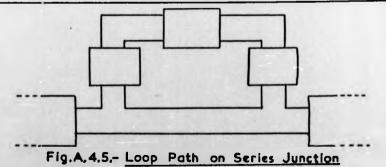

On top of this path, between the input and output ports, further paths of a similar form can be connected on this main path to any level. In section 2.2 the basic equations for a chain matrix analysis are described with the equations for all the path connection types as follows:-

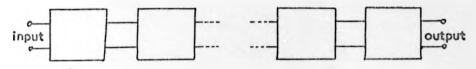

- 1) simple cascade of 2-port networks (Fig. 2.4),

- 2) branch arms ( Table 2.2 ),

- 3) parallel paths ( Table 2.3 ) and

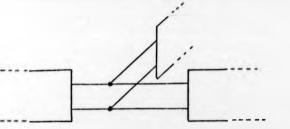

- 4) loop paths ( Table 2.5 ).

#### 2.2.2. Simple Cascade of 2-port Networks

The basic objective of chain matrix analysis is to analyse a circuit consisting of a cascade of 2-port networks, Fig. 2.4. The method used is to set up the 2x2 complex number chain matrix for each network in the cascade as:-