### A Thesis Submitted for the Degree of PhD at the University of Warwick

Permanent WRAP URL: <a href="http://wrap.warwick.ac.uk/102005/">http://wrap.warwick.ac.uk/102005/</a>

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright. Please scroll down to view the document itself. Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Design, simulation and analysis of RESURF Si/SiC power LDMOSFETs

By

**Chunwa Chan**

A thesis submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy

Supervisor: Dr Peter M. Gammon and Prof. Philip Mawby

School of Engineering, University of Warwick

March 2018

### Table of contents

| List             | of figures                                                              | vi   |

|------------------|-------------------------------------------------------------------------|------|

| List             | of tables                                                               | xi   |

| Ackı             | nowledgements                                                           | xii  |

| Decl             | aration                                                                 | xiv  |

| List             | of publications                                                         | XV   |

| Abst             | tract                                                                   | xvi  |

| List             | of symbols and abbreviations                                            | xvii |

| Chaj             | pter 1 Introduction                                                     | 1    |

| 1.1.             | Background                                                              | 3    |

| 1.2.             | Thesis outlines                                                         | 5    |

| Cha <sub>]</sub> | pter 2 High temperature power electronics                               | 7    |

| 2.1.             | Introduction of power electronics                                       | 7    |

| 2.2.             | Harsh environment operations                                            | 10   |

|                  | 2.2.1. High temperature environment                                     | 11   |

|                  | 2.2.2. Self-heating effects                                             | 11   |

|                  | 2.2.3. High junction temperature operation                              | 13   |

|                  | 2.2.4. High temperature reliability tests                               | 14   |

| 2.3.             | Semiconductor materials and technologies                                | 15   |

|                  | 2.3.1. Semiconductors of choice for high-temperature power applications | 20   |

|                  | 2.3.1.1 Silicon                                                         | 21   |

|                  | 2.3.1.2 GaAs                                                            | 23   |

|                  | 2.3.1.3 GaN                                                             | 24   |

|                  | 2.3.1.4 SiC                                                             | 24   |

|                  | 2.3.1.5 Ga <sub>2</sub> O <sub>3</sub>                                  | 25   |

|                  | 2.3.1.6 Diamond                                                         | 25   |

|                  | 2.3.1.7 AlN                                                             | 26   |

|                  | 2.3.2. Conclusions                                                      | 26   |

| 2.4.             | Others technologies for high-temperature devices                        | 27   |

|      | 2.4.1. Semi-insulator technologies                       | 27   |

|------|----------------------------------------------------------|------|

|      | 2.4.2. Vacuum technologies                               | 28   |

| Chaj | pter 3 Theory                                            | . 30 |

| 3.1. | Introduction of LDMOSFET                                 | 30   |

| 3.2. | The substrates of LDMOSFET/LIGBT                         | 32   |

|      | 3.2.1. Structures with substrate effects                 | 33   |

|      | 3.2.2. Structures without strong substrate effects       | 35   |

| 3.3. | LDMOS topology                                           | 36   |

| 3.4. | RESURF technologies                                      | 37   |

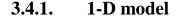

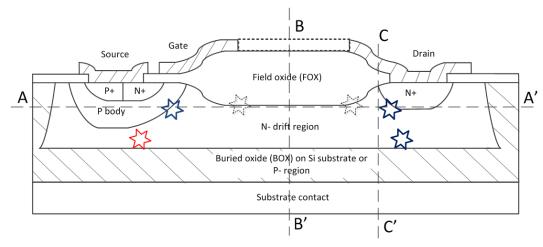

|      | 3.4.1. 1-D model                                         | 38   |

|      | 3.4.2. 2-D model                                         | 39   |

|      | 3.4.2.1 Bulk Si                                          | 42   |

|      | 3.4.2.2 SOI                                              | 45   |

| 3.5. | On-resistance & Saturation current                       | 48   |

| Chaj | pter 4 TCAD models verification and discussion           | . 50 |

| 4.1. | Introduction                                             | 50   |

| 4.2. | TCAD software                                            | 50   |

| 4.3. | Model benchmarking                                       | 51   |

|      | 4.3.1. The first benchmark structures (600 V)            | 53   |

|      | 4.3.1.1 Off-state characteristics                        | 55   |

|      | 4.3.1.2 On-state characteristics                         | 61   |

|      | 4.3.2. The second benchmark structure (~200 V)           | 62   |

|      | 4.3.3. Conclusion                                        | 64   |

| Chaj | pter 5 RESURF Si/SiC LDMOS designs and simulation setups | . 66 |

| 5.1. | Introduction                                             | 66   |

| 5.2. | Si/SiC non-RESURF PiN diodes                             | 66   |

|      | 5.2.1. Thermal simulation of the substrates              | 67   |

|      | 5.2.2. Electro-thermal modelling of PiN diodes           | 70   |

|      | 5.2.2.1 Simulated structures                             | 70   |

|      | 5.2.2.2 Simulation setup                                 | 71   |

|      | 5.2.2.3 Simulation results                               | 71   |

| 5.3. | Si/SiC RESURF LDMOS designs                              | 74   |

| 5.3.2. 600 V Si/SiC LDMOS with PN RESURF825.3.3. 190 V Si/SiC LDMOS with SOI RESURF825.4. Simulation setups875.4.1 Application of the physical-based models875.4.2. Simulated switching circuits875.4.2.1 Clamped inductive switching (600 V)885.4.2.2 Rectangular Power Pulse (600 V)925.4.2.3 Capacitive load switching and Zener-diode-clamped inductive<br>switching (190 V)92Chapter 6 TCAD study on the 600 V Si/SiC LDMOSFETs976.1. Introduction976.2. DC characteristics976.2.1. Si/SiC LDMOS in SOI RESURF technology VS SOI976.2.1.2 On-state behaviour996.2.2. Si/SiC LDMOS in PN RESURF technology VS Bulk Si1046.2.3. Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS1056.3. Dynamic characteristics1106.3.1.1 Overview of switching characteristics1116.3.2.2. Si/SiC, Philips SOI vs Si/SiC on inductive switching1126.3.2.1 Simulation results1156.3.2.1 Simulation results115Chapter 7 TCAD study on the 190 V Si/SiC LDMOS rETs121                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>5.4. Simulation setups</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4.1. Application of the physical-based models       87         5.4.2. Simulated switching circuits       87         5.4.2. Simulated switching circuits       87         5.4.2.1 Clamped inductive switching (600 V)       88         5.4.2.2 Rectangular Power Pulse (600 V)       92         5.4.2.3 Capacitive load switching and Zener-diode-clamped inductive switching (190 V)       93         Chapter 6 TCAD study on the 600 V Si/SiC LDMOSFETs         97       6.1. Introduction       97         6.2. DC characteristics       97         6.2.1. Si/SiC LDMOS in SOI RESURF technology VS SOI       97         6.2.1.2 On-state behaviour       99         6.2.1.2 On-state behaviour       99         6.2.3. Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS       102         6.3.1 Philips SOI vs Si/SiC on inductive switching       110         6.3.1.1 Overview of switching characteristics       111         6.3.1.2 Analysis of transient currents and power       113         6.3.2.1 Simulation results       115         6.3.2.1 Simulation results       115 |

| 5.4.2. Simulated switching circuits       87         5.4.2.1 Clamped inductive switching (600 V)       88         5.4.2.2 Rectangular Power Pulse (600 V)       92         5.4.2.3 Capacitive load switching and Zener-diode-clamped inductive switching (190 V)       92         6.1. Introduction       97         6.1. Introduction       97         6.2. DC characteristics       97         6.2.1. Si/SiC LDMOS in SOI RESURF technology VS SOI       97         6.2.1.1 Off-state behaviour       98         6.2.2. Si/SiC LDMOS in PN RESURF technology VS Bulk Si       104         6.2.3. Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS       105         6.3.1. Philips SOI vs Si/SiC on inductive switching       110         6.3.1.1 Overview of switching characteristics       111         6.3.1.2 Analysis of transient currents and power       112         6.3.2.1 Simulation results       119         6.3.2.1 Simulation results       119                                                                                                                         |

| 5.4.2.1       Clamped inductive switching (600 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.2.2       Rectangular Power Pulse (600 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4.2.3       Capacitive load switching and Zener-diode-clamped inductive switching (190 V)       93         Chapter 6 TCAD study on the 600 V Si/SiC LDMOSFETs         6.1       Introduction       97         6.2       DC characteristics       97         6.2.1       Si/SiC LDMOS in SOI RESURF technology VS SOI       97         6.2.1.2       On-state behaviour       98         6.2.2.       Si/SiC LDMOS in PN RESURF technology VS Bulk Si       104         6.2.3       Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS       105         6.3       Dynamic characteristics       110         6.3.1.1       Overview of switching characteristics       111         6.3.1.2       Analysis of transient currents and power       113         6.3.2.       Si/SiC, Philips SOI vs Bulk Si LDMOS on RPP circuit       115         6.3.2.1       Simulation results       115                                                                                                                                                                                                 |

| switching (190 V)       93         Chapter 6 TCAD study on the 600 V Si/SiC LDMOSFETs       97         6.1.       Introduction       97         6.2.       DC characteristics       97         6.2.1.       Off-state behaviour.       98         6.2.1.2       On-state behaviour.       98         6.2.2.       Si/SiC LDMOS in PN RESURF technology VS Bulk Si       104         6.2.3.       Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS       105         6.3.       Dynamic characteristics       110         6.3.1.       Philips SOI vs Si/SiC on inductive switching       110         6.3.1.1       Overview of switching characteristics       111         6.3.1.2       Analysis of transient currents and power       113         6.3.2.       Si/SiC, Philips SOI vs Bulk Si LDMOS on RPP circuit       119         6.3.2.1       Simulation results       119            |

| 6.1.       Introduction       97         6.2.       DC characteristics       97         6.2.1. Si/SiC LDMOS in SOI RESURF technology VS SOI       97         6.2.1.1       Off-state behaviour       98         6.2.1.2       On-state behaviour       99         6.2.2. Si/SiC LDMOS in PN RESURF technology VS Bulk Si       104         6.2.3. Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS       105         6.3.       Dynamic characteristics       110         6.3.1.       Philips SOI vs Si/SiC on inductive switching       110         6.3.1.1       Overview of switching characteristics       111         6.3.1.2       Analysis of transient currents and power       113         6.3.2. Si/SiC, Philips SOI vs Bulk Si LDMOS on RPP circuit       115         6.3.2.1       Simulation results       115                                                                                                                                                                                                                                                             |

| <ul> <li>6.2. DC characteristics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>6.2.1. Si/SiC LDMOS in SOI RESURF technology VS SOI</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

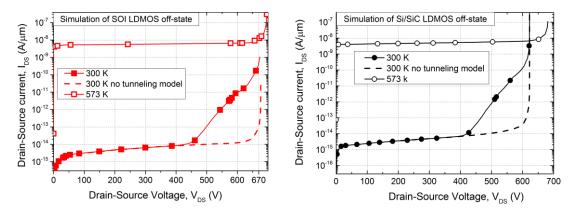

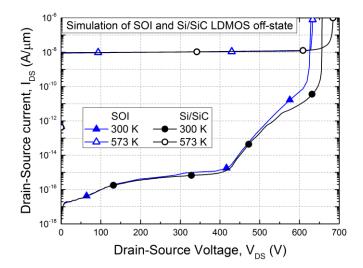

| 6.2.1.1       Off-state behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.2.1.2       On-state behaviour       99         6.2.2. Si/SiC LDMOS in PN RESURF technology VS Bulk Si       104         6.2.3. Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS       105         6.3. Dynamic characteristics       110         6.3.1. Philips SOI vs Si/SiC on inductive switching       110         6.3.1.1       Overview of switching characteristics       111         6.3.1.2       Analysis of transient currents and power       113         6.3.2. Si/SiC, Philips SOI vs Bulk Si LDMOS on RPP circuit       119         6.3.2.1       Simulation results       119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>6.2.2. Si/SiC LDMOS in PN RESURF technology VS Bulk Si</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>6.2.3. Temperature effects on the Si/SiC, SOI and Bulk Si LDMOS</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>6.3. Dynamic characteristics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>6.3.1. Philips SOI vs Si/SiC on inductive switching</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>6.3.1.1 Overview of switching characteristics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>6.3.1.2 Analysis of transient currents and power</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3.2. Si/SiC, Philips SOI vs Bulk Si LDMOS on RPP circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.3.2.1 Simulation results119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 7 TCAD study on the 190 V Si/SiC LDMOSFETs121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.2. DC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

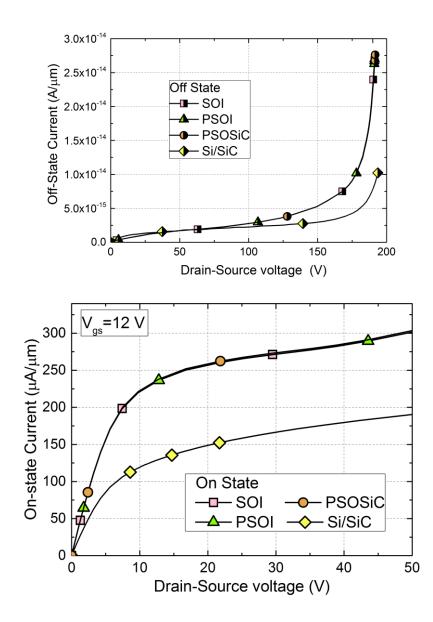

| 7.2.1. Off and on-state behaviour122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7.3. Dynamic characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

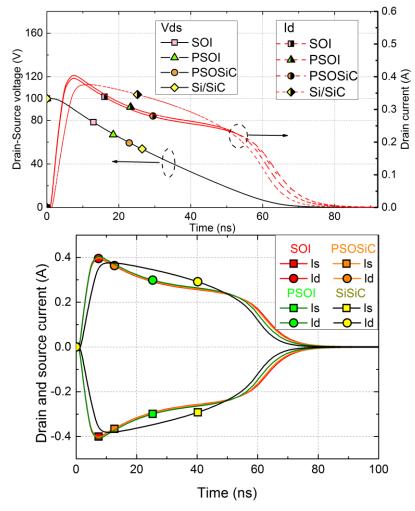

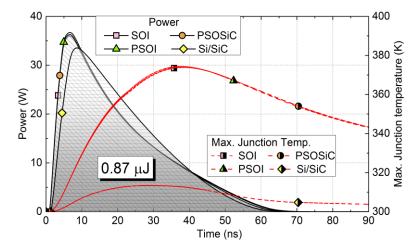

| 7.3.1. Capacitive load switching123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

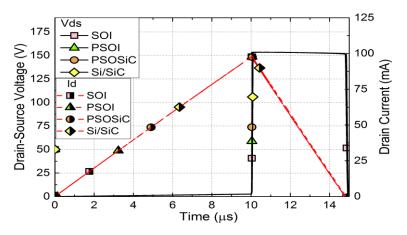

| 7.3.2. Zener-diode-clamped inductive switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.3.3. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 8 Conclusions and further work128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.1. | Conc  | lusions                                          | 128 |

|------|-------|--------------------------------------------------|-----|

| 8.2. | Futur | e work                                           | 133 |

|      | 8.2.1 | . Experimental results                           | 133 |

|      | 8.2.2 | . Physical-based TCAD models                     | 133 |

|      | 8.2.3 | RESURF design                                    | 134 |

|      | 8.2.4 | . Switching circuits                             |     |

|      | 8.2.5 | LIGBTs                                           | 136 |

| Appe | endix |                                                  |     |

|      |       |                                                  |     |

| А    | Ther  | nal models                                       | 137 |

|      | A.1   | Methodology                                      | 137 |

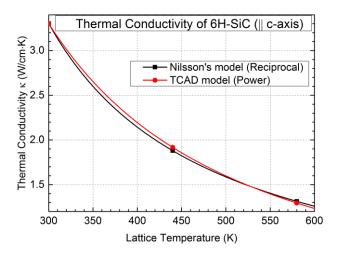

|      | A.2   | Thermal conductivity and heat capacitance        | 138 |

| В    | 3D R  | ESURF for Si/SiC                                 | 141 |

| С    | Expe  | rimental Si/SiC issues affecting TCAD simulation | 144 |

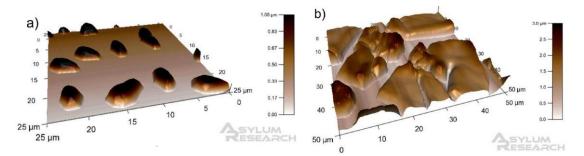

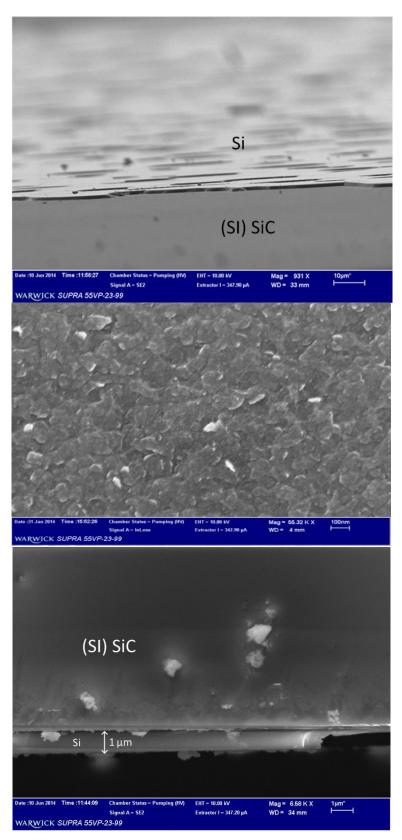

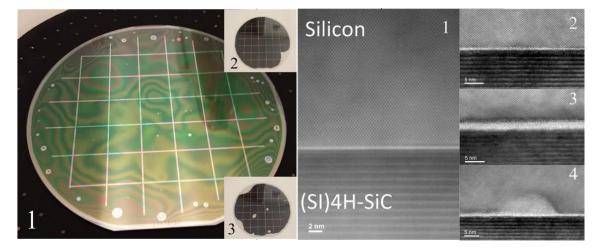

|      | C.1   | The quality of Si on SiC                         | 144 |

|      | C.2   | The (SI) SiC substrate                           | 149 |

|      | C.3   | The Si/SiC interface                             | 151 |

| Refe | rence | S                                                |     |

# List of figures

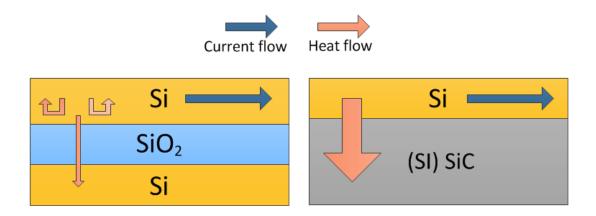

| Figure 1.1. The basic features of the SOI (left) and the Si/SiC substrate (right)                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

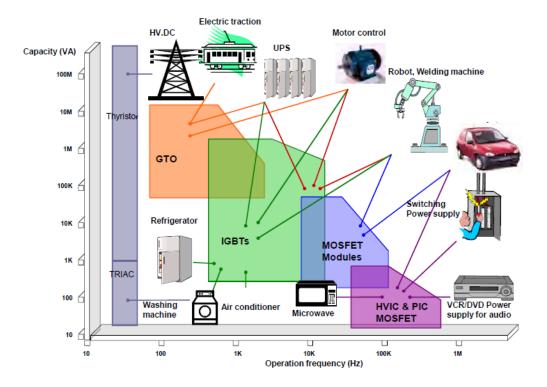

| Figure 2.1. Current applications of Si power electronics, taken from [18]                                                                                                                                                                       |

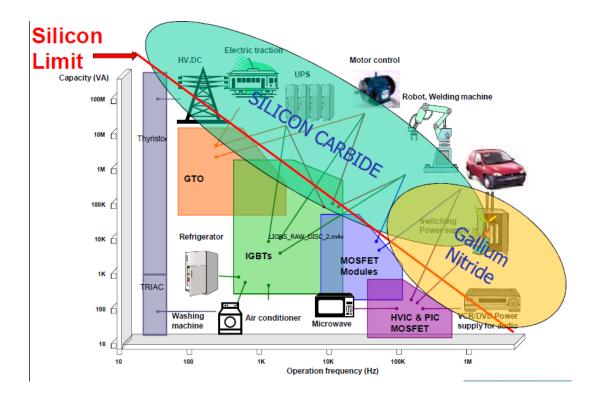

| Figure 2.2. Current applications of Si power electronics, with the new frontiers enabled by SiC and GaN, taken from [18]                                                                                                                        |

| Figure 2.3. Two simple diagrams for a power diode (left) and a power MOSFET (right)                                                                                                                                                             |

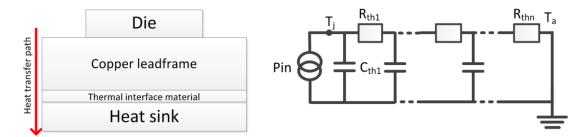

| Figure 2.4. A simplified side view of a power module (left) and a 1-D thermal circuit consisting of multiple RC sections to represent the thermal properties of different materials (right). Thermal radiation and advection are not considered |

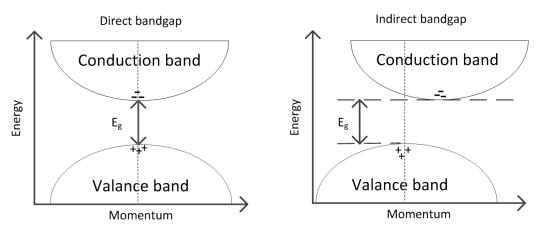

| Figure 2.5. Direct and indirect band structures for intrinsic semiconductors, with plus sign (+) and minus sign (-) indicating holes and electrons                                                                                              |

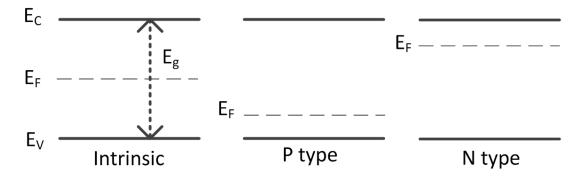

| Figure 2.6. The simplified bandgap structure of an intrinsic, P-type and N-type semiconductor                                                                                                                                                   |

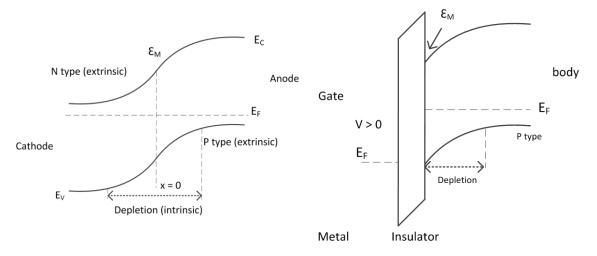

| Figure 2.7. The band diagrams of a PN junction (left) and Metal-insulator-semiconductor (MIS) structure (right)                                                                                                                                 |

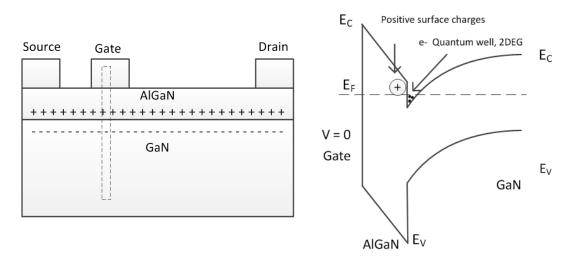

| Figure 2.8. The simplified AlGaN/GaN HEMT structure and the band diagram at the gate region                                                                                                                                                     |

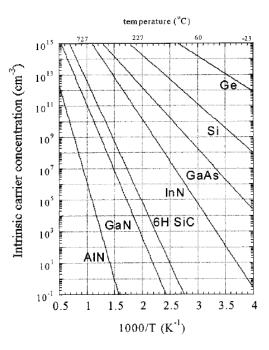

| Figure 2.9. Intrinsic carrier density vs Temperature for different materials, namely Ge, Si, GaAs, InN, 6H-SiC, GaN and AlN [41]                                                                                                                |

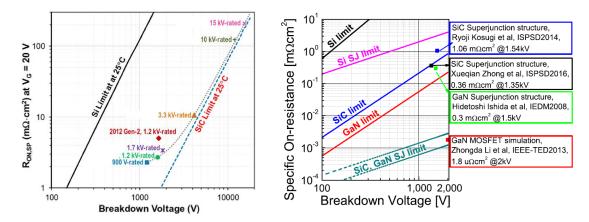

| Figure 2.10. The specific on-resistance vs breakdown voltage in [43] (left) and [44] (right), for vertical power MOSFETs made from Si, SiC and GaN23                                                                                            |

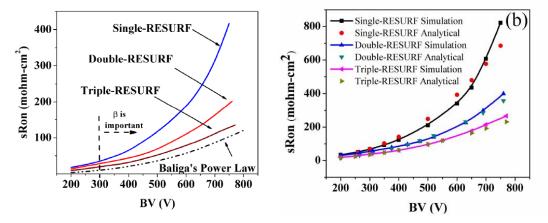

| Figure 2.11. The specific on-resistance and breakdown voltage for LDMOSFETs at 25 <sup>o</sup> C (left) and 125 <sup>o</sup> C (right), designed with different RESURF technologies [45]23                                                      |

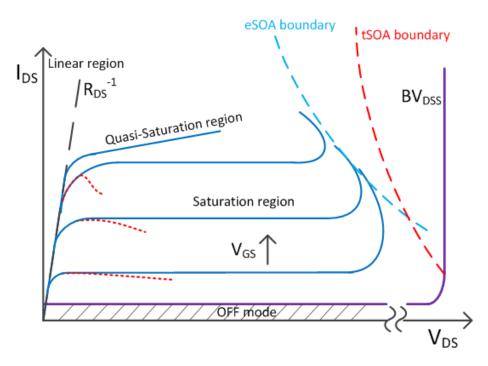

| Figure 3.1. I-V characteristics of a n-type LDMOSFET                                                                                                                                                                                            |

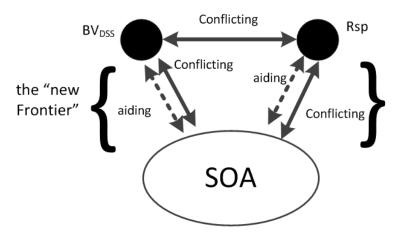

| Figure 3.2. A triangle relationship among BV <sub>DSS</sub> , R <sub>sp</sub> and safe operation area (SOA) for LDMOS design, taken from [64]                                                                                                   |

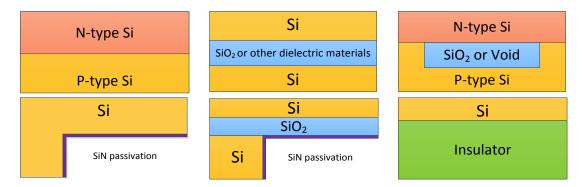

| Figure 3.3. The Si-based substrates where lateral power devices are fabricated. From left to right, top to bottom, are Bulk Si, SOI, PSOI, Membrane Bulk Si, Membrane SOI and Si on thick insulator (SOTI)                                      |

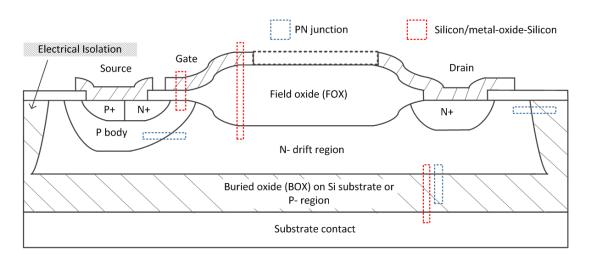

| Figure 3.4. The locations of PN junctions and/or silicon/metal-oxide-semiconductor layouts in a LDMOSFET                                                                                                                                        |

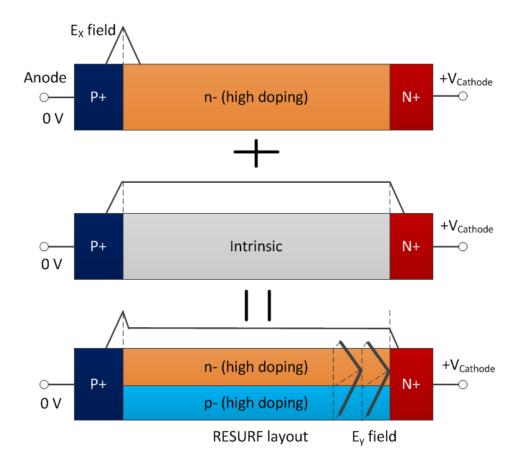

| Figure 3.5. A simple demonstration of the RESURF concept by using three PiN diodes differing in the settings of the drift region                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.6. A reverse-biased PiN diode (left) and its corresponding electrical field distribution (right)                                                                                                                                                                                        |

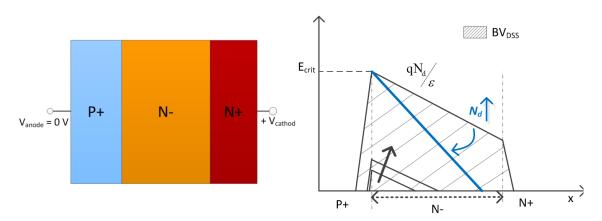

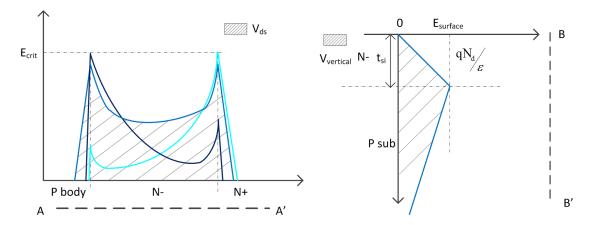

| Figure 3.7. A HV LDMOSFET with stars indicating possible breakdown locations. AA', BB' and CC' are the cutlines for analysing the E field along the surface, at the midpoint of drift region and under the N+ drain in vertical direction, respectively                                          |

| Figure 3.8. The electric field distribution along AA' (left) and BB' (right), for the 1 <sup>st</sup> order RESURF LDMOSFET                                                                                                                                                                      |

| Figure 3.9. The electric field distribution along cutline AA' (left) and BB' (right), when the avalanche breakdown point is tend to be reached                                                                                                                                                   |

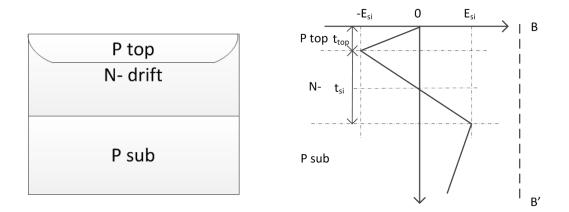

| Figure 3.10. Double RESURF Layout (left) and the corresponding electric field along BB' when the drift region is fully depleted (right)                                                                                                                                                          |

| Figure 3.11. Triple RESURF layout (left) and the corresponding electric field along BB' when the drift region is fully depleted (right)                                                                                                                                                          |

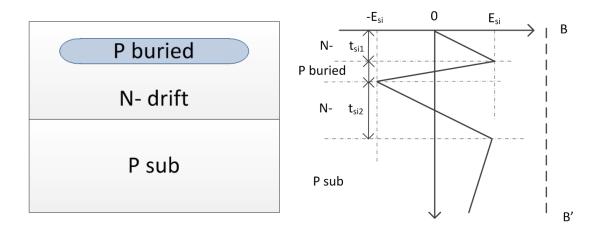

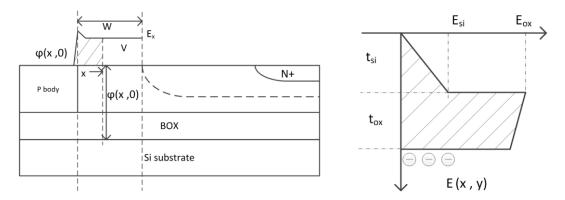

| Figure 3.12. A 2-D SOI diode with the optimal RESURF condition under a reverse voltage of $V$ , having an electric field $E_x$ in $x$ direction throughout a lateral depletion distance of about $W$ (left), and a electric field distribution at location $x$ highlighted in the device (right) |

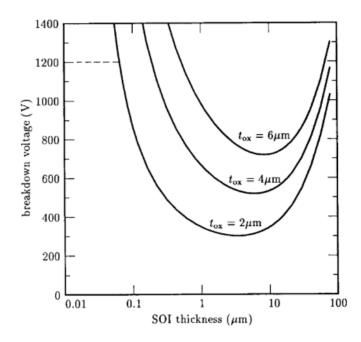

| Figure 3.13. The relationship between the breakdown voltage and thicknesses of the Si and BOX layer in SOI devices, taken from [100]                                                                                                                                                             |

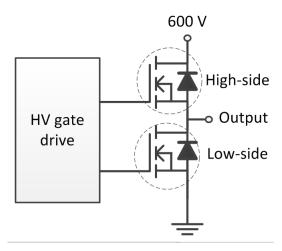

| Figure 3.14. A half bridge circuit consisting of a HV gate drive block, a low-side and high-side N channel LDMOSFET                                                                                                                                                                              |

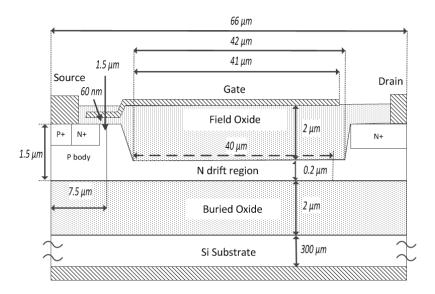

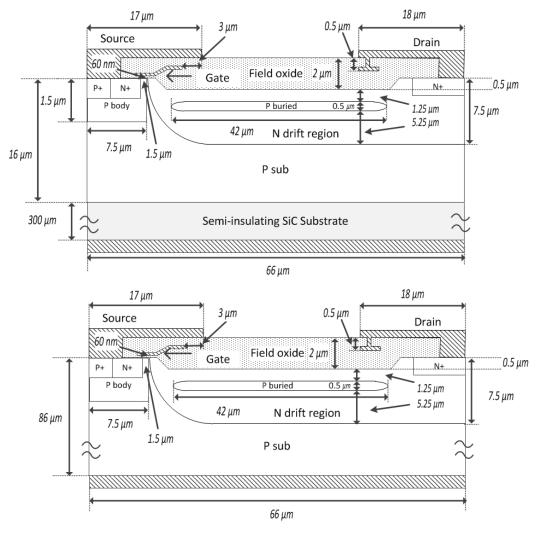

| Figure 4.1. One of the Philips SOI transistors [46] used in SILVACO for benchmarking, where the key parameters are indicated                                                                                                                                                                     |

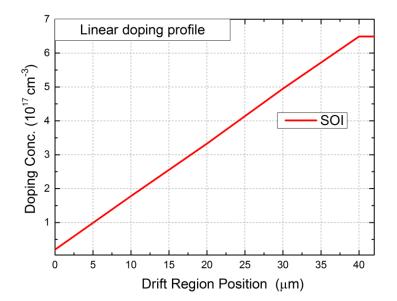

| Figure 4.2. The linear doping profile of the simulated SOI LDMOSFET                                                                                                                                                                                                                              |

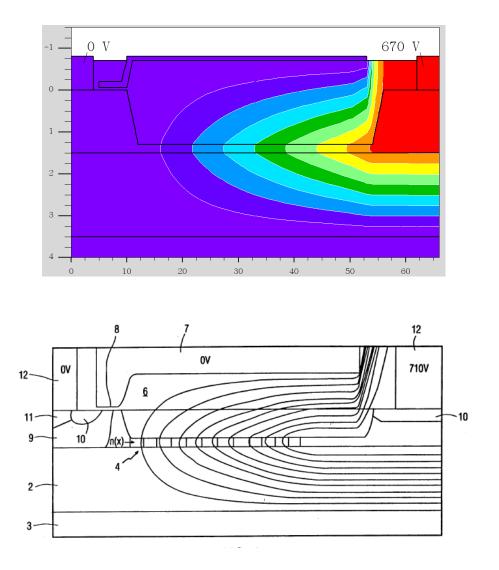

| Figure 4.3. The potential contours of the benchmark LDMOS (top), and the Philips SOI (bottom) [121], on the verge of avalanche breakdown. (axes units: µm)                                                                                                                                       |

| Figure 4.4. The potential and electric field at the middle of the N drift region, at the onset of avalanche breakdown                                                                                                                                                                            |

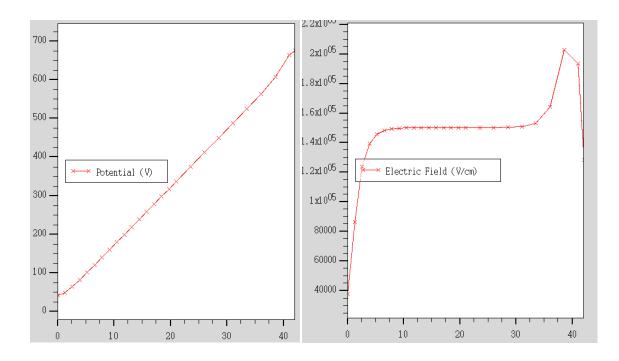

| Figure 4.5. Off-state characteristics of the simulation SOI (Left) and the Philips SOI (right) [46], at room temperature and 200 <sup>o</sup> C. The bottom graph from [110] is more similar to the simulation result                                                                            |

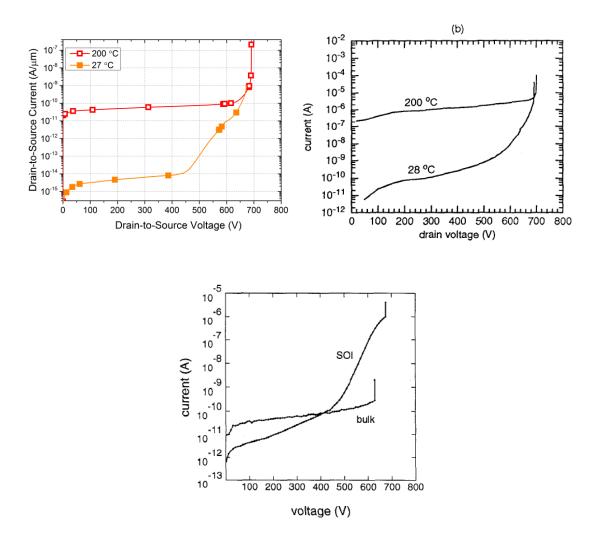

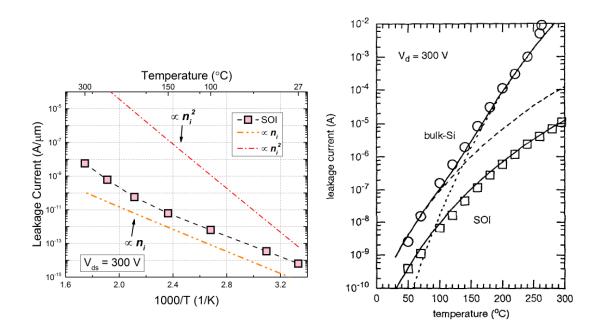

| Figure 4.6. The temperature dependency of leakage current at $V_{DS} = 300$ V for the simulated structure (left), and the Philips SOI [46] (right). In the right figure, the dotted and dashed line indicate the diffusion and generation component, respectively                                |

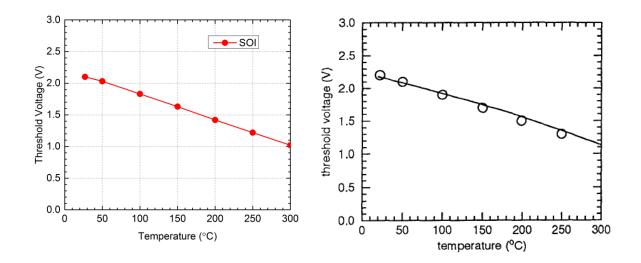

| Figure 4.7. The threshold voltage vs temperature for the simulated structure (left) and the Philips SOI (right) [46]                                                                                                                                                                             |

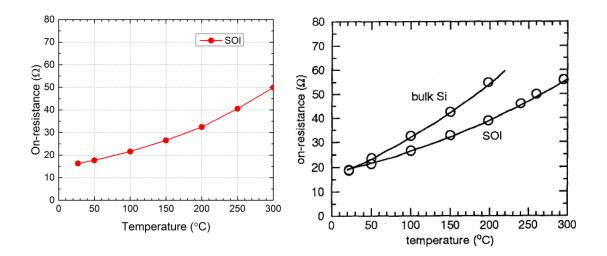

| Figure 4.8. The low-side resistance vs temperature for the simulated structure (left) and the Philips SOI (right) [46]                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

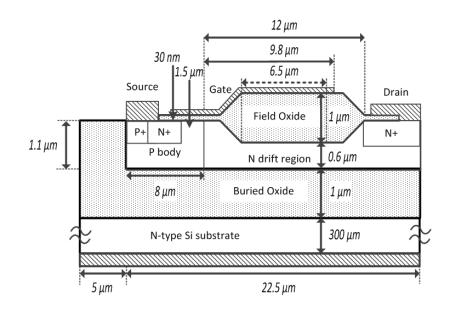

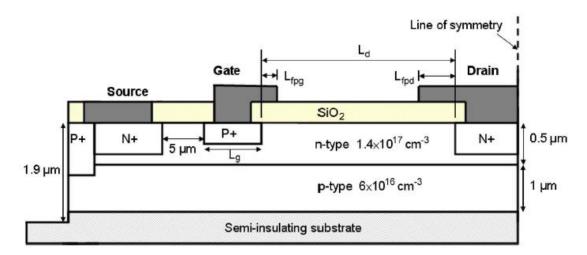

| Figure 4.9. The second benchmark structure based upon [129], with a blocking voltage of 190 V                                                                                                              |

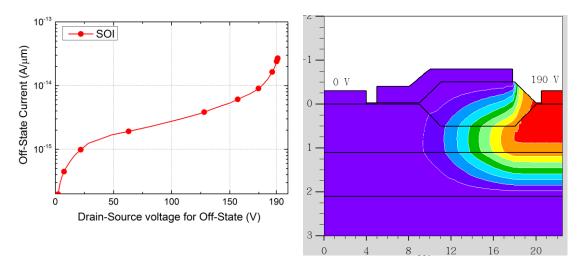

| Figure 4.10. The off-state I-V curve (left) and potential distribution (right) at the onset of avalanche breakdown and 300 K, for the simulated structure (axes unit: $\mu$ m)64                           |

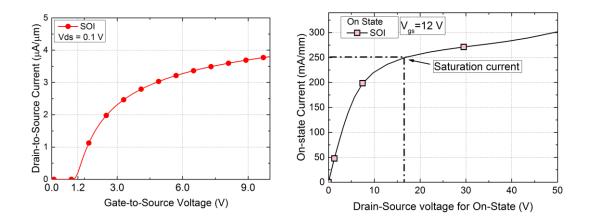

| Figure 4.11. The VGS-IDS curve at VDS = $0.1 \text{ V}$ (left) and the on-state characteristics at Vgs = $12 \text{ V}$ (right), for the simulated structure                                               |

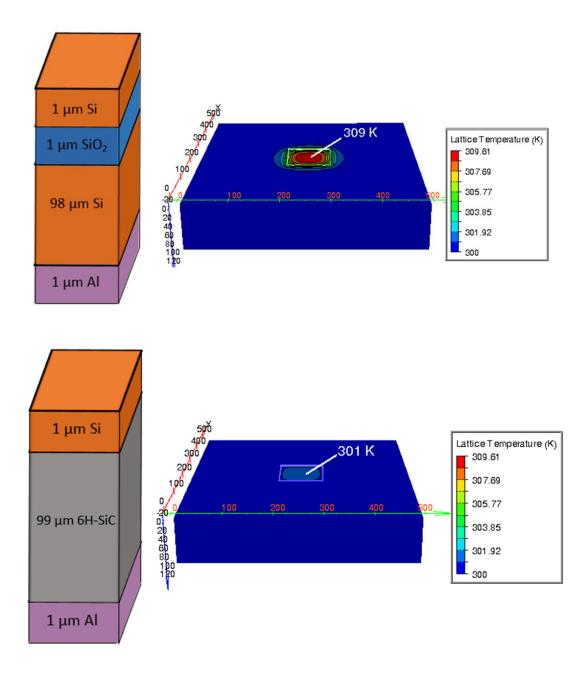

| Figure 5.1. The SOI (top) and Si/SiC (bottom) simulation models showing temperature distributions with a range of 300-309.61 K. Their maximum temperatures are 309 K (top) and 301 K (bottom) respectively |

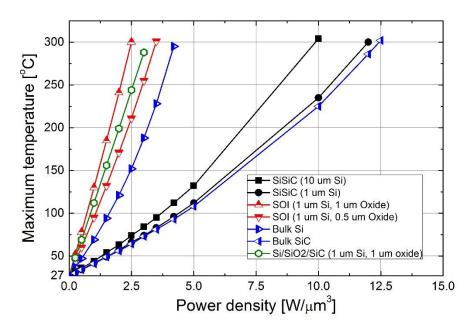

| Figure 5.2. Simulated max temperatures (27-300°C) vs. power density for different structures                                                                                                               |

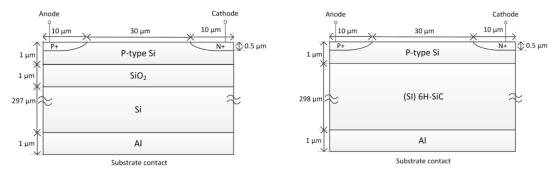

| Figure 5.3. The simulated SOI (left) and Si/SiC PiN diodes (right)70                                                                                                                                       |

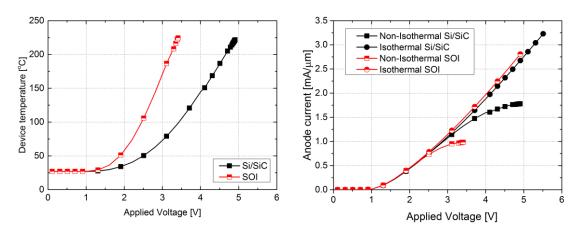

| Figure 5.4. Applied Voltage vs. Device temperature (left) and Anode current (right) for the Si/SiC and the SOI                                                                                             |

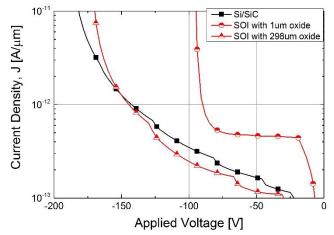

| Figure 5.5. Reverse I-V curves for Si/SiC and SOI structures72                                                                                                                                             |

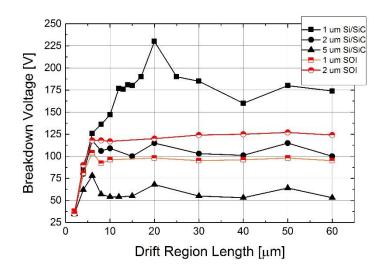

| Figure 5.6. Drift region length vs. Breakdown voltage73                                                                                                                                                    |

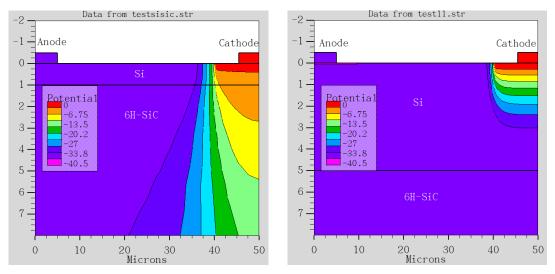

| Figure 5.7. The potential distributions of the Si/SiC with a 1 $\mu$ m (left) and 5 $\mu$ m thick Si layer (right), at an anode voltage of -40 V                                                           |

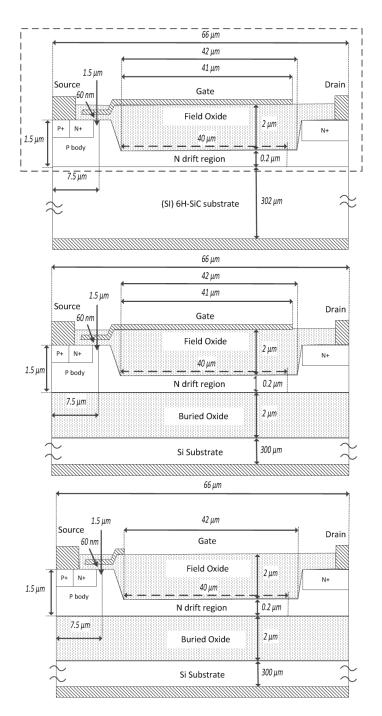

| Figure 5.8. The 600 V Si/SiC LDMOS design with a SOI RESURF layout (top) and its SOI counterparts in the Philips technology (middle) [46] and by Paul et al. (bottom) [133]                                |

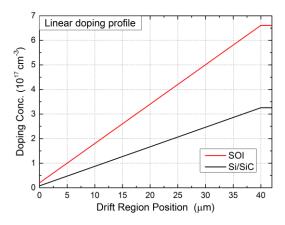

| Figure 5.9. The linear doping profiles in the drift regions of the Si/SiC and Philips SOI                                                                                                                  |

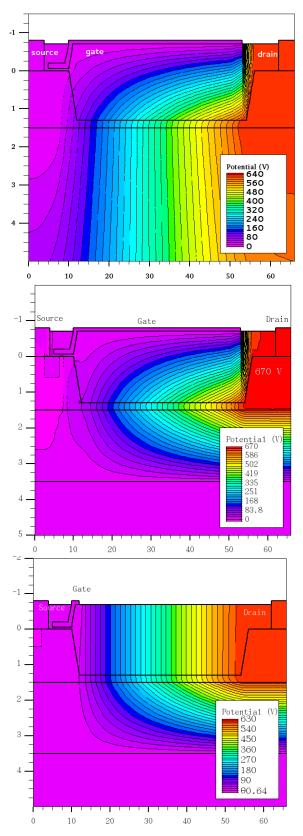

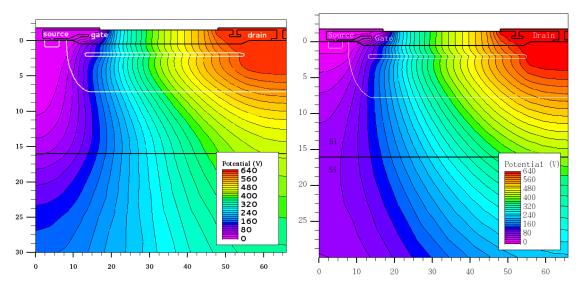

| Figure 5.10. The potential contours at 300 K and onset of breakdown, for (top) the Si/SiC and (middle) the Philips SOI and (bottom) the SOI without the field plate extension (axes units: $\mu$ m)        |

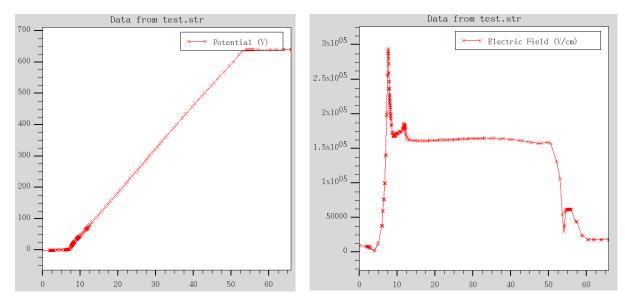

| Figure 5.11. The potential distribution (left) and electric field (right) at the bottom of the Si layer in the Si/SiC transistor, at the onset of avalanche breakdown and 300 K (axes units: $\mu$ m)      |

| Figure 5.12. Two 600 V LDMOSFETs with a triple RESURF layout, using the Si/SiC (top) and the bulk-Si substrate (bottom)                                                                                    |

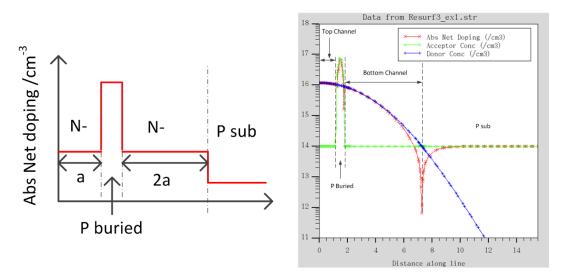

| Figure 5.13. The doping profiles in the ideal triple RESURF case (left) and in the TCAD simulation (right), for the two thick-film transistors                                                             |

| Figure 5.14. The potential distributions at 300 K and onset of breakdown, for the thick-film Si/SiC (left) and its bulk Si counterpart (right) (axes units: µm)                                            |

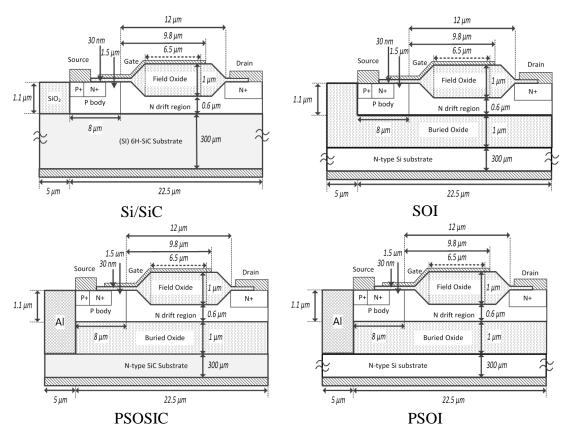

| Figure 5.15. 190 V LDMOSFETs using different substrates, namely Si/SiC, SOI, PSOSIC and PSOI                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

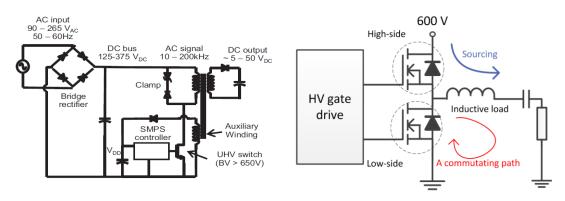

| Figure 5.16. A flyback topology for AC/DC conversion [137] (left) and a half bridge circuit with an inductive load (right)                                                                                                                                          |

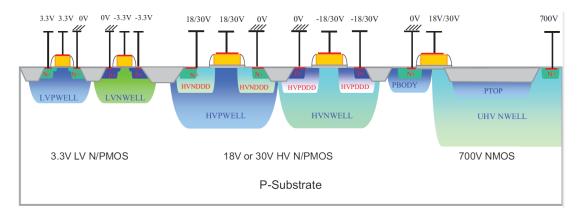

| Figure 5.17. The lateral MOSFETs in the JI technology optimised for fully integrated AC/DC Power ICs [137]                                                                                                                                                          |

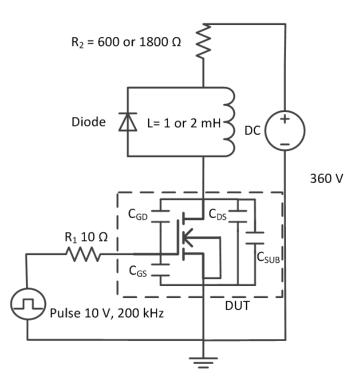

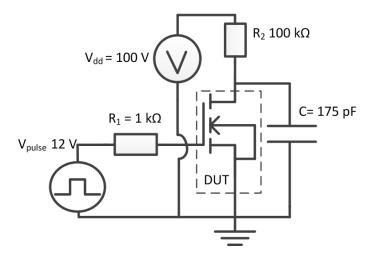

| Figure 5.18. A diode-clamped inductive switching circuit in the Mixed-Mode simulation                                                                                                                                                                               |

| Figure 5.19. The rectangle power pulse circuit used in the Mixed-mode simulation for the 600 V LDMOSFETs                                                                                                                                                            |

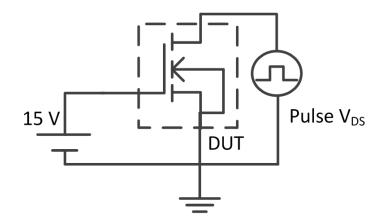

| Figure 5.20. The simulated capacitive discharge circuit based upon [62], for the 190 V LDMOSFETs in Si/SiC, SOI, PSOI and PSOSiC technology95                                                                                                                       |

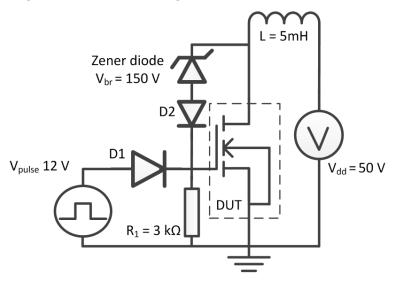

| Figure 5.21. The clamped inductive switching setup with a Zener diode, for the 190 V LDMOSFETs                                                                                                                                                                      |

| Figure 6.1. OFF-state I–V characteristics of the Philips SOI (left) and Si/SiC LDMOS (right)                                                                                                                                                                        |

| Figure 6.2. Off-state characteristics of the Si/SiC (black) and the SOI without the field plate extension (blue)                                                                                                                                                    |

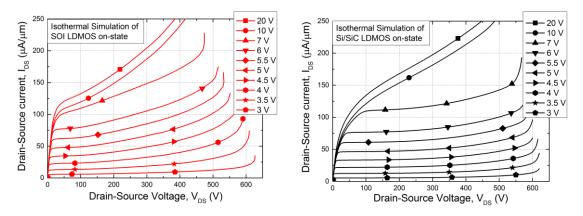

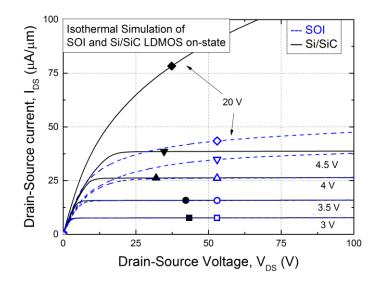

| Figure 6.3. On-state characteristics of the Philips SOI (left) and Si/SiC LDMOSFETs (right), under isothermal conditions at 300 K                                                                                                                                   |

| Figure 6.4. the ohmic regions of the I-V curves for the Philips SOI and Si/SiC at 300 K                                                                                                                                                                             |

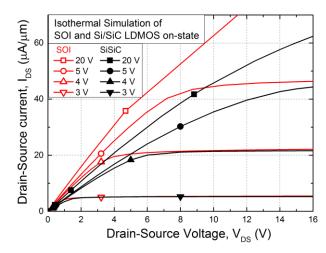

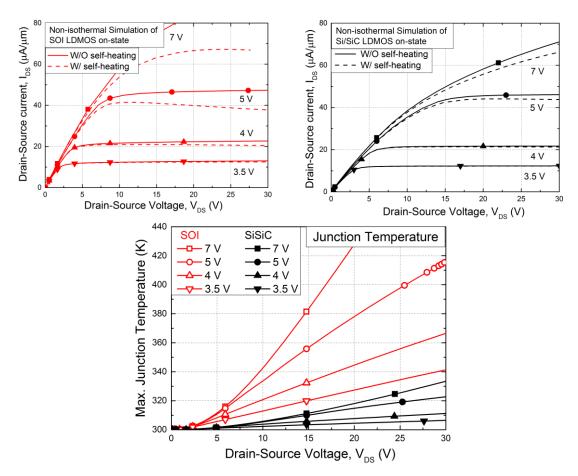

| Figure 6.5. The steady-state effect of self-heating on forward characteristics of SOI (left) and Si/SiC LDMOS (right), as well as their junction temperature (bottom)                                                                                               |

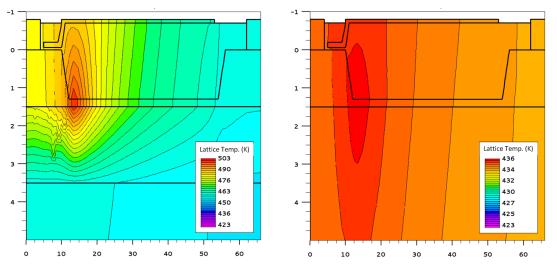

| Figure 6.6. Temperature contours of (left) SOI and (right) Si/SiC under $V_{DS} = 15$ V, $V_{GS} = 10$ V conditions (axes units: $\mu$ m)                                                                                                                           |

| Figure 6.7. On-state characteristics of the Si/SiC (black) and SOI without the field plate extension (blue), under isothermal conditions                                                                                                                            |

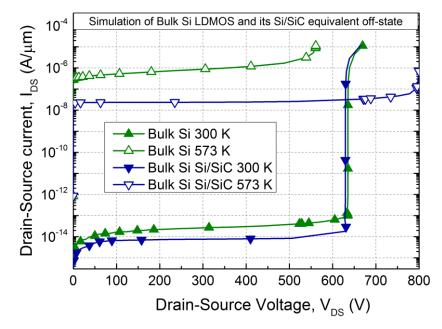

| Figure 6.8. Off-state characteristics of the Si/SiC (dark blue) and the Bulk Si counterpart (green), at 300 and 573 K104                                                                                                                                            |

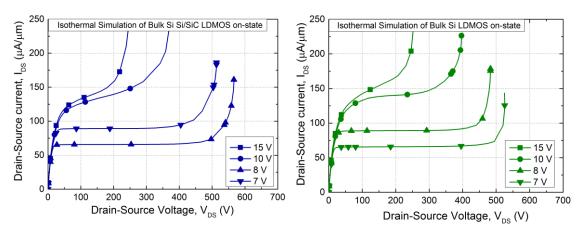

| Figure 6.9. On-state characteristics of the thick-film Si/SiC (left) and bulk Si LDMOSFETs (right), under isothermal conditions (300 K)105                                                                                                                          |

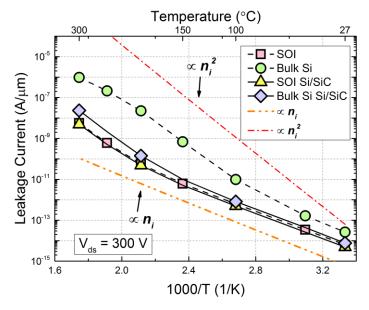

| Figure 6.10. Temperature dependence of leakage current for the SOI, Bulk-Si, SOI Si/SiC and Bulk-Si Si/SiC LDMOS at a drain voltage of 300 V, along with two lines ( $\propto n_i \& \propto n_i^2$ ) representing generation and diffusion component, respectively |

| Figure 6.11. Temperature dependence of low-side specific on-resistance for the SOI,                                                                                                                                                                                 |

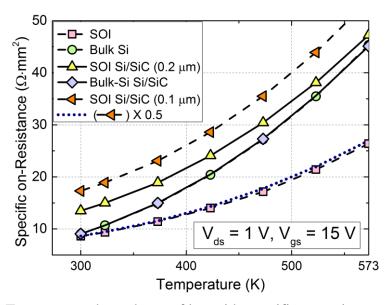

Figure 6.11. Temperature dependence of low-side specific on-resistance for the SOI, Bulk-Si, Bulk-Si Si/SiC and two SOI Si/SiC transistors that have differing Si layer

| thickness, namely 0.2 and 0.1 $\mu$ m. The dotted line is derived from halving the curve for the SOI Si/SiC LDMOS with a 0.1- $\mu$ m-thick Si film                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

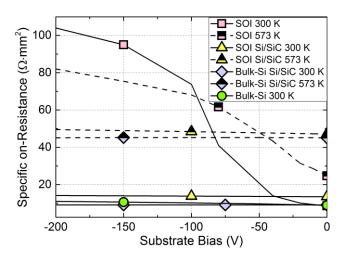

| Figure 6.12. Relationships between specific on-resistance and substrate bias for the simulated LDMOSFETs at 300 K and 573 K, excluding the one for the Bulk-Si at 573 K                                                                                                                |  |  |

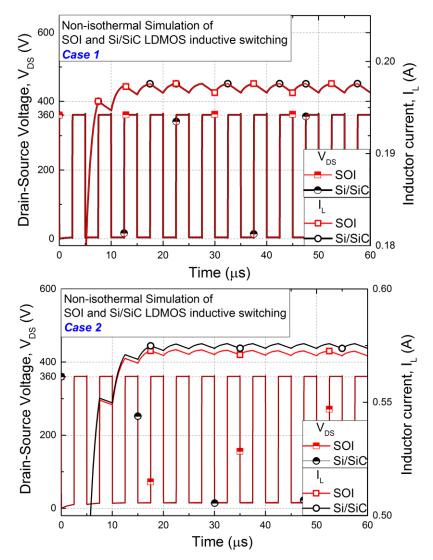

| Figure 6.13. Drain–source voltage and inductor current for the two transistors during $V_{GS}$ = 10 V, 200 kHz switching nonisothermal simulations. The inductor and current-limiting resistor are 2 mH and 1800 $\Omega$ in Case 1 (Top) and 1 mH and 600 $\Omega$ in Case 2 (Bottom) |  |  |

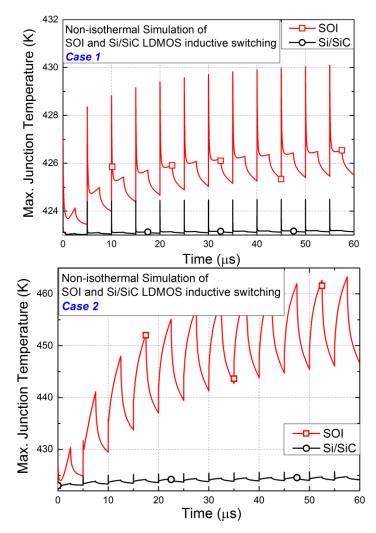

| Figure 6.14. Dynamic temperature response of the two transistors in the nonisothermal switching for Case 1 (top) and Case 2 (bottom)                                                                                                                                                   |  |  |

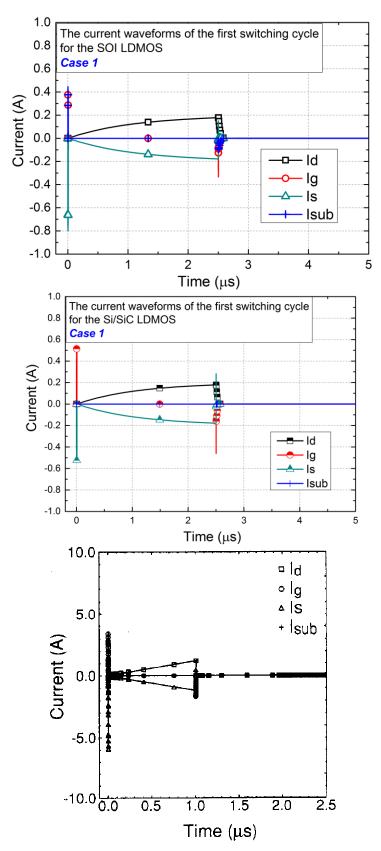

| Figure 6.15. The current waveforms of the first switching cycle for the 600 V Philips SOI (top), 600 V Si/SiC (middle) and the 200 V SOI LDMOSFET in [152] (bottom)114                                                                                                                 |  |  |

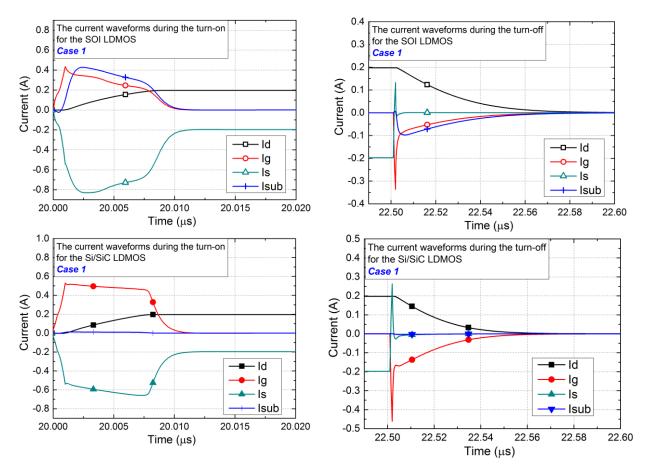

| Figure 6.16. The SOI and Si/SiC transient currents during the turn-on and off, in Case 1                                                                                                                                                                                               |  |  |

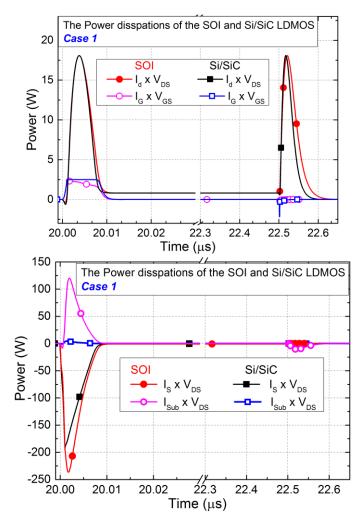

| Figure 6.17. Power disspations calculated by $I_D \times V_{DS}$ and $I_G \times V_{GS}$ (top), and by $I_S \times V_{DS}$ and $I_{SUB} \times V_{DS}$ (bottom) for the Philip SOI and Si/SiC in one cycle                                                                             |  |  |

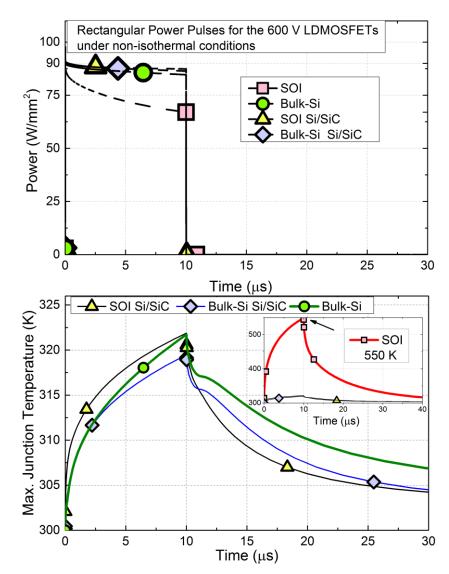

| Figure 6.18. The power pulses (top) and temperature responses (bottom) for the simulated 600 V structures                                                                                                                                                                              |  |  |

| Figure 7.1. On (top) and off-state I-V curves (bottom) for the simulated 190 V devices under isothermal conditions at 300 K                                                                                                                                                            |  |  |

| Figure 7.2. The I-V switching behaviour during the turn-on for the four LDMOSFETs (top) and their drain and source currents (bottom)                                                                                                                                                   |  |  |

| Figure 7.3. The instantaneous power and temperature responses during the capacitive discharge for the simulated LDMOSFETs                                                                                                                                                              |  |  |

| Figure 7.4. The V <sub>ds</sub> and I <sub>d</sub> curves under the conditions of V <sub>pulse</sub> = 12 V, V <sub>dd</sub> = 50 V, L = 5 mH, $BV_{Zener} = 150$ V, $R1 = 3$ k $\Omega$ and a ramp-up time of 10 µs, for the four simulated structures                                |  |  |

| Figure 7.5. The power and temperature curves of inductive switching, under (top) the conditions mentioned in Fig. 7.13, and (bottom) with the inductor value and ramp-up time changed to 500 mH and 100 $\mu$ s                                                                        |  |  |

| Figure A-1 Thermal conductivity of 6H-SiC as a reciprocal (black) and power function (red) of lattice temperature. The Nilsson's model is detailed in [160]                                                                                                                            |  |  |

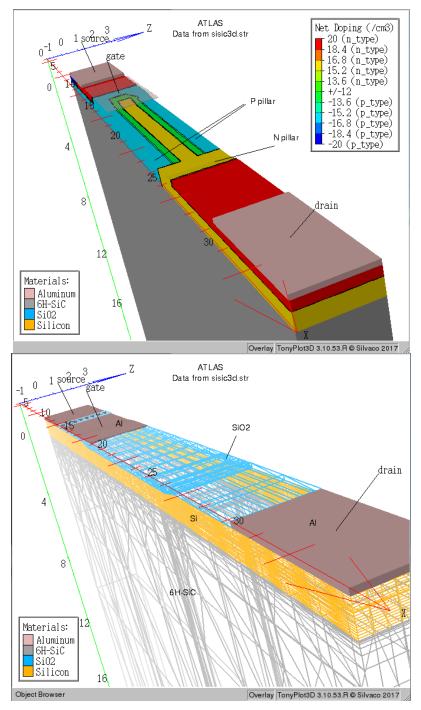

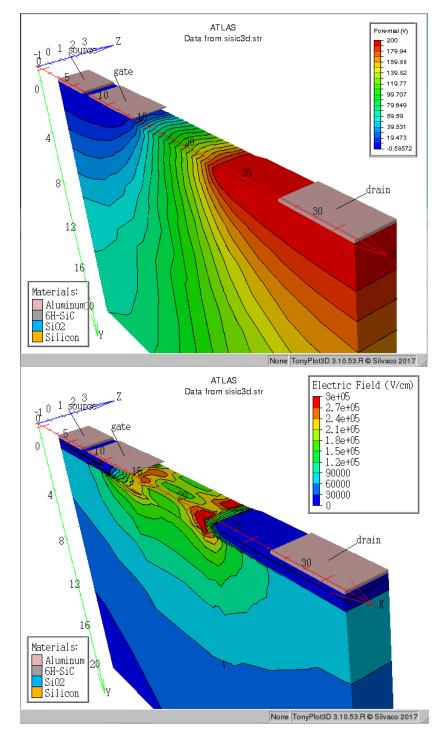

| Figure B-1 A 3D view of the Si/SiC LDMOSFET in 3D RESURF technology                                                                                                                                                                                                                    |  |  |

| Figure B-2 3-D potential (top) and electric field distribution (bottom) of the Si/SiC LDMOSFET at the onset of avalanche breakdown (200 V)143                                                                                                                                          |  |  |

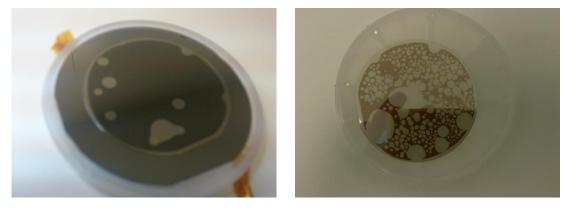

Figure C.1. Atomic force microscopy for the Si/SiC heterojunction layer by molecular beam epitaxy (MBE), designed to be 100 nm thick (left) and 1 µm thick (right) [38].145

## List of tables

### Acknowledgements

I would like to first thank Peter Gammon, who has been supervising me and offering academic support throughout my PhD. You are a true professional, enthusiastic about research with an ambition to achieve the best, and more importantly always having an optimistic 'aura' around. No matter how negative I am to one question, you never show a sense of gloomy view but look on the bright side. Without this, I would have published fewer papers than I did, gotten stuck at one point and struggled to move forwards. Not to mention how many Chinglish you spot in my writing, all these let me know how to be competent, confident and self-motivated.

To my second supervisor Phil Mawby, I thank you for your enlightenment and encouragement for my first journal paper. Also the Chinese dinner you and your wife host each year is truly impressive, and I really appreciate your hospitality.

I would like to express my acknowledgements to my family, who have been supporting me during my PhD study. Without doubt, this contributes significantly to my work and continues to be one of important factors to push me forwards.

A special thank goes to Mark Crouch and Corinne Maltby, who are the technicians working at Science City cleanroom. Your experience, expertise and patience in teaching helped me gain some helpful skills about semiconductor processes. It is a priceless memory to be guided by someone with industrial backgrounds, and indeed will be quite useful in my upcoming career. I also appreciate the instructions on the MBE machine from one of our legends: Vishal Shah, though I never had a chance to operate it during my PhD.

Last but not least, I would like to thank the other members of our PEATER group at the University of Warwick, those who are still there and those who have left for other companies: Fan Li, Rong Hua, Tianxiang Dai, Dean Hamilton, Mohammad Al-Amin, Robert Espley-Jones, Craig Fisher, Stephen Russell, Li Ran, Olayiwola Alatise, Mike Jennings, Roozbeh Bonyadi & Yeganeh Bonyadi, Blossom Mohammadi, Saeed Jahdi, Ji Hu and Petros Alexakis.

### **Declaration**

This thesis is submitted in partial fulfilment for the degree of Doctor of Philosophy under the regulations set out by the Graduate School at the University of Warwick. I certify that this thesis does not incorporate any material without acknowledgement previously submitted to any institution for a higher degree or previously published. The work is this thesis is my own except where stated, under the supervision of Dr Peter M. Gammon and Prof. Philip Mawby.

Chunwa Chan

March 2018

# List of publications

### Patent

P. M. Gammon and C. W. Chan, (WO2016132089) Power Semiconductor Device, 2015. Filed, USA and UK, International Application No.: PCT/GB2015/050467. Link: https://patentscope.wipo.int/search/en/detail.jsf?docId=WO2016132089

### Journal articles

- C. W. Chan, F. Li, A. Sanchez, P. A. Mawby and P. M. Gammon, "Comparative Study of RESURF Si/SiC LDMOSFETs for High-Temperature Applications Using TCAD Modelling," in IEEE Transactions on Electron Devices, vol. 64, no. 9, pp. 3713-3718, Sept. 2017.

- C. W. Chan, P. A. Mawby and P. M. Gammon, "Analysis of Linear-Doped Si/SiC Power LDMOSFETs Based on Device Simulation," in IEEE Transactions on Electron Devices, vol. 63, no. 6, pp. 2442-2448, June 2016.

### **Conference** papers

- C. W. Chan, F. Li, P. A. Mawby and P. M. Gammon, "Numerical study of energy capability of Si/SiC LDMOSFETs," 2016 European Conference on Silicon Carbide & Related Materials (ECSCRM), Halkidiki, Greece, Vol. 897, pp. 751-754, 2017.

- C.W. Chan, Y. Bonyadi, P. A. Mawby, P. M. Gammon, "Si/SiC Substrates for the Implementation of Linear-Doped Power LDMOS Studied with Device Simulation", Materials Science Forum, Vol. 858, pp. 844-847, 2016.

- C.W. Chan, P. M. Gammon, V. Al Shah, H. Chen, M.R. Jennings, C.A. Fisher, A. Pérez-Tomás, Maksym Myronov, P.A. Mawby, "Simulations of a Lateral PiN Diode on Si/SiC Substrate for High Temperature Applications", Materials Science Forum, Vols. 821-823, pp. 624-627, 2015

### Abstract

It is necessary for power laterally diffused MOSFETs (LDMOSFETs) to operate efficiently and reliably in high temperature (<300 °C), hostile environments such as those found in downhole, space, automotive and aerospace applications. Currently, silicon-oninsulator (SOI) technology is a dominant method to achieve this goal due to low leakage current and complete electrical isolation. However, the buried oxide (BOX) layer causes self-heating, which can impact device performance, cause thermal runaway and shorten device lifetime. To address this issue, one solution is to combine a silicon thin film with a semi-insulating (SI) SiC substrate, forming the Si/SiC architecture. LDMOSFETs built on this substrate are expected to deliver much better thermal performance, with electrical isolation comparable to the SOI case. However, the Si/SiC LDMOSFETs do not have a strong substrate assisted depletion effect, which can result in poorer electrical performance than those of the Reduced Surface Field (RESURF) bulk-Si and SOI LDMOSFETs. This thesis investigates the PN and SOI RESURF layouts and uses them to optimise 190 V and 600 V Si/SiC LDMOSFETs. DC and transient modelling will be conducted on the optimised Si/SiC and their SOI and bulk-Si equivalents. Based upon this, several comparative studies are conducted on their simulation results to see the effects of the Si/SiC architecture on the LDMOS designs.

The comparative studies are made on the 600 V Si/SiC LDMOSFETs and their bulk Si and SOI equivalents. It is shown that the Si/SiC devices have the potential to operate with an off-state leakage current as low as the SOI device. However, the low-side resistance of the SOI LDMOSFET is smaller in value and less sensitive to temperature, outperforming both Si/SiC devices. Conversely, under high-side configurations, the Si/SiC transistors have resistances lower than that of the SOI at high substrate bias, and invariable with substrate potential up to -200 V, which behaves similar to the bulk-Si LDMOS at 300 K. A clamped-inductive switching circuit is simulated for the Philips SOI and the Si/SiC equivalent. It is shown that even though the SOI has a smaller chip area and suffered from strong substrate effects during the transient state, the two devices had similar currents and power dissipations at the gate, drain and source. The turn-on losses are higher than that of the turn-off losses due to the presence of parasitic capacitors. However, these similarities do not lead to similar thermal responses in both devices and the SOI is heated up at a much faster rate. By contrast, the SiC substrate in the Si/SiC behaves like an embedded heat sink regulating device temperature close to that of the ambient environment (423 K). In the high current condition, the peak temperature in the Si/SiC is 425 K, lower than 463 K in the SOI, thereby increasing reliability.

The comparative studies are carried out on the 190 V LDMOSFETs in SOI, Si/SiC, Partial SOI (PSOI) and PSOSIC technology, based upon a capacitive and an inductive switching circuit. It is revealed that in spite of having a chip area 75% larger than the SOI structure, the Si/SiC solution undergoes negligible heating in any of the switching conditions simulated, exhibiting a very high energy capability. By contrast, the 22% area increase in the PSOSiC does not considerably change the way the energy is handled. This indicates that the Si/SiC is much more effective than PSOI and PSOSIC in dealing with the transient heating.

# List of symbols and abbreviations

| Ea                   | Thermal Activation Energy                      |

|----------------------|------------------------------------------------|

| $C_P$                | Specific Heat at constant pressure             |

| $E_g$                | Band Gap                                       |

| N <sub>A</sub>       | Acceptor Doping                                |

| N <sub>C</sub>       | Effective Density Of States For Electron       |

| $N_V$                | Effective Density Of States For Hole           |

| $N_b$                | Base Doping                                    |

| $Q_{eff}$            | Effective Dose                                 |

| $T_L$                | Lattice Temperature                            |

| V <sub>dep</sub>     | Depletion Volume                               |

| $t_{ox}$             | Oxide Thickness                                |

| $t_{si}^*$           | Effective Si Layer Thickness                   |

| $\varepsilon_{ox}$   | Oxide Dielectric Constant                      |

| $\kappa_{  }$        | Thermal Conductivity In Parallel To The C Axis |

| $\kappa_{\perp}$     | Thermal Conductivity In Normal To The C Axis   |

| BV <sub>DSS</sub>    | Breakdown Voltage                              |

| Ec                   | Conduction Band                                |

| E <sub>Cri</sub>     | Critical Electric Field                        |

| E <sub>F</sub>       | Fermi Level                                    |

| ε <sub>M</sub>       | Maximum Electric Field                         |

| E <sub>surface</sub> | Surface Electric Field                         |

| Ev                   | Valance Band                                   |

| $E_x$                | Horizontal Electric Field                      |

| $E_y$                | Vertical Electric Field                        |

| Н                                                                                               | Heat Generation                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hc.a                                                                                            | Coefficient For Calculating Heat Capacitance                                                                                                                                                                                        |

| hc.b                                                                                            | Coefficient For Calculating Heat Capacitance                                                                                                                                                                                        |

| hc.c                                                                                            | Coefficient For Calculating Heat Capacitance                                                                                                                                                                                        |

| hc.d                                                                                            | Coefficient For Calculating Heat Capacitance                                                                                                                                                                                        |

| j                                                                                               | Current Density                                                                                                                                                                                                                     |

| k                                                                                               | Boltzmann Constant                                                                                                                                                                                                                  |