A Thesis Submitted for the Degree of PhD at the University of Warwick

**Permanent WRAP URL:**

http://wrap.warwick.ac.uk/160913

#### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

Student ID: 1218779

This student has been formally diagnosed with Specific Learning Differences. Please make appropriate allowance when marking.

Guidance is available at: http://www2.warwick.ac.uk/services/

tutors/disability/guidance

Disability Services

# Data Structure Abstraction and Parallelisation of Multi-Material Hydrodynamic Applications

by

### Richard Oliver Kirk

A thesis submitted to The University of Warwick in partial fulfilment of the requirements

for admission to the degree of

### Doctor of Philosophy in Computer Science

## Department of Computer Science

The University of Warwick

September 2020

## Copyright

© British Crown Owned Copyright 2020/AWE. Published with permission of the Controller of Her Britannic Majesty's Stationery Office. This document is of United Kingdom origin and contains proprietary information which is the property of the Secretary of State for Defence. It is furnished in confidence and may not be copied, used or disclosed in whole or in part without prior written consent of Defence Intellectual Property Rights DGDCDIPR-PL—Ministry of Defence, Abbey Wood, Bristol, BS34 8JH, England.

# Contents

| Copyright                 |                    |                                                          |  |

|---------------------------|--------------------|----------------------------------------------------------|--|

| Li                        | List of Figures vi |                                                          |  |

| Li                        | st of              | Tables x                                                 |  |

| Li                        | st of              | Listings xiii                                            |  |

| Ac                        | knov               | vledgements xiv                                          |  |

| De                        | eclar              | ations xv                                                |  |

| Al                        | ostra              | ct xvii                                                  |  |

| Al                        | obrev              | viations xviii                                           |  |

| Sponsorship and Grants xx |                    | orship and Grants xxi                                    |  |

| 1                         | Intr               | oduction 1                                               |  |

|                           | 1.1                | Motivation                                               |  |

|                           | 1.2                | Thesis Contributions                                     |  |

|                           | 1.3                | Thesis Overview                                          |  |

| 2                         | Ana                | lyse and Performance of Applications and Architectures 7 |  |

|                           | 2.1                | Benchmarking                                             |  |

|                           | 2.2                | Representative Applications                              |  |

|                           | 2.3                | Profiling                                                |  |

|                           | 2.4                | Speedup                                                  |  |

|                           | 2.5                | Amdahl's Law                                             |  |

|                           | 2.6                | Overhead                                                 |  |

|                           | 27                 | Performance Portability 14                               |  |

|   | 2.8 | Summ    | nary                                                 | 16 |

|---|-----|---------|------------------------------------------------------|----|

| 3 | Ach | ieving  | Performance through Hardware Optimisations           | 17 |

|   | 3.1 | Moore   | e's Law                                              | 18 |

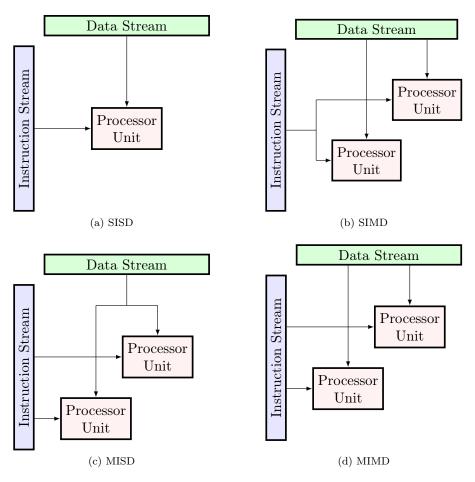

|   | 3.2 | Flynn   | 's Taxonomy                                          | 18 |

|   |     | 3.2.1   | Single Instruction - Single Data                     | 20 |

|   |     | 3.2.2   | Single Instruction - Multiple Data                   | 20 |

|   |     | 3.2.3   | Multiple Instruction - Single Data                   | 22 |

|   |     | 3.2.4   | Multiple Instruction - Multiple Data                 | 22 |

|   | 3.3 | Parall  |                                                      | 23 |

|   |     | 3.3.1   | Vectorising                                          | 24 |

|   |     | 3.3.2   | Multithreading and Multiprocessing                   | 26 |

|   |     | 3.3.3   | Distributed computing                                | 29 |

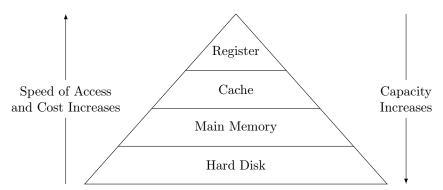

|   | 3.4 | Memo    | ory Layouts and Data Structures                      | 30 |

|   |     | 3.4.1   | Structure of Arrays                                  | 33 |

|   |     | 3.4.2   | Array of Structures                                  | 34 |

|   |     | 3.4.3   | Array of Structures of Arrays                        | 35 |

|   |     | 3.4.4   | Abstract Data Structures                             | 36 |

|   | 3.5 | Summ    | nary                                                 | 41 |

|   |     |         |                                                      |    |

| 4 | Ana | alysing | the Performance Portability of a Heat-Conduction     | l  |

|   | Mir | ni-App  | lication                                             | 43 |

|   | 4.1 | Motiv   | ation                                                | 45 |

|   | 4.2 | Parall  | elisation of a Heat-Conduction Mini-Application      | 46 |

|   |     | 4.2.1   | Reference Implementation and Manual Parallelisations | 47 |

|   |     | 4.2.2   | Oxford Parallel Library for Structured-mesh solvers  | 48 |

|   |     | 4.2.3   | Kokkos and RAJA                                      | 48 |

|   | 4.3 | Perfor  | mance of TeaLeaf                                     | 49 |

|   |     | 4.3.1   | Experimental Setup                                   | 51 |

|   |     | 4.3.2   | Results                                              | 52 |

|   |     | 4.3.3   | System Analysis                                      | 59 |

|   | 4.4                  | Perfor  | mance Portability                                  |

|---|----------------------|---------|----------------------------------------------------|

|   |                      | 4.4.1   | Architecture Efficiency                            |

|   |                      | 4.4.2   | Application Efficiency                             |

|   | 4.5                  | Summ    | nary                                               |

| 5 | $\operatorname{Cre}$ | ation.  | Development, Implementation and Optimisations of   |

|   |                      | •       | ructure Abstraction Library 67                     |

|   | 5.1                  | Motiv   | ation                                              |

|   | 5.2                  | Initial | Implementation                                     |

|   | 5.3                  | Librar  | y Structure                                        |

|   |                      | 5.3.1   | High-Level Functionality Classes                   |

|   |                      | 5.3.2   | Data Storage Classes                               |

|   |                      | 5.3.3   | Data Access Classes                                |

|   | 5.4                  | Librar  | y Features                                         |

|   |                      | 5.4.1   | Conversion of Variables                            |

|   |                      | 5.4.2   | Data Adjacency                                     |

|   | 5.5                  | Data    | Structures and Optimisations                       |

|   |                      | 5.5.1   | Structure of Arrays                                |

|   |                      | 5.5.2   | Array of Structures of Arrays                      |

|   |                      | 5.5.3   | Specialised Data Structures                        |

|   | 5.6                  | Summ    | ary                                                |

| 6 | Per                  | formaı  | nce Analysis of the Data Structure Abstraction Li- |

|   | bra                  | ry      | 109                                                |

|   | 6.1                  | Bench   | mark Testing and Overhead                          |

|   | 6.2                  | Mini-   | Application Performance and Overhead               |

|   |                      | 6.2.1   | Hardware and Compilers                             |

|   |                      | 6.2.2   | Unstructured Physics Mini-Application              |

|   |                      | 6.2.3   | Heat Conduction Mini-Application                   |

|   |                      | 6.2.4   | Molecular Dynamics Mini-Application 123            |

|   | 6.3                  | Scalin  | σ Performance and Overhead 125                     |

|                  | 6.4   | Summ    | ary                                                                       | . 129 |

|------------------|-------|---------|---------------------------------------------------------------------------|-------|

| 7                | Dat   | a Stru  | cture Abstraction Library Specialisation                                  | 130   |

|                  | 7.1   | Motiva  | ation                                                                     | . 131 |

|                  | 7.2   | Multi-  | Material Data Structures                                                  | . 131 |

|                  |       | 7.2.1   | Compact Cell Multi-Material Data Structure                                | . 133 |

|                  |       | 7.2.2   | Compact Cell Flat Multi-Material Data Structure                           | . 135 |

|                  | 7.3   | Imple   | mentation of Abstract Data Structures                                     | . 136 |

|                  | 7.4   | Perfor  | mance of Data Structure Abstraction Library                               | . 140 |

|                  |       | 7.4.1   | Experimental Setup                                                        | . 141 |

|                  |       | 7.4.2   | Results                                                                   | . 143 |

|                  | 7.5   | Summ    | ary                                                                       | . 145 |

| 8                | Con   | clusio  | n and Future Work                                                         | 146   |

|                  | 8.1   | Limita  | ations                                                                    | . 147 |

|                  | 8.2   | Future  | e Work                                                                    | . 148 |

|                  |       | 8.2.1   | Warwick Data Store                                                        | . 149 |

|                  |       | 8.2.2   | Multi-Material Data Structures                                            | . 150 |

|                  |       | 8.2.3   | Data Structure Optimisations                                              | . 151 |

|                  |       | 8.2.4   | Just-In-Time Compilation                                                  | . 152 |

|                  | 8.3   | Reflec  | tions                                                                     | . 153 |

| Bi               | bliog | graphy  |                                                                           | 154   |

| $\mathbf{A}_{]}$ | ppen  | dices   |                                                                           | 166   |

| $\mathbf{A}$     | Con   | npilers | and compiler flags used for Analysing the Perfo                           | r-    |

|                  | mar   | nce Po  | $rtability\ of\ a\ Heat\text{-}Conduction\ Mini\text{-}Application\ (C.)$ | hap-  |

|                  | ter   | 4)      |                                                                           | 167   |

|                  |       |         |                                                                           |       |

# List of Figures

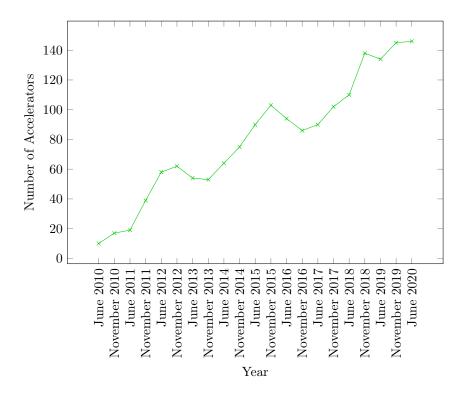

| 1.1 | Trend of accelerators for the Top500 supercomputers [113] over          |    |

|-----|-------------------------------------------------------------------------|----|

|     | the last decade                                                         | 2  |

| 3.1 | Graphical representation of the different categories in Flynn's         |    |

|     | Taxonomy                                                                | 19 |

| 3.2 | Graphical representation of the Memory Hierarchy                        | 32 |

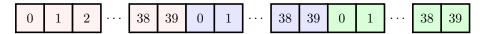

| 3.3 | Graphical representation of the memory when using a Structure           |    |

|     | of Arrays (SoA) data structure                                          | 34 |

| 3.4 | Graphical representation of the memory when using a Array of            |    |

|     | Structures (AoS) data structure                                         | 35 |

| 3.5 | Graphical representation of the memory when using a Array of            |    |

|     | Structures of Arrays (AoSoA) data structure                             | 36 |

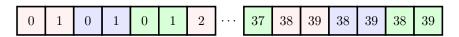

| 3.6 | Graphical Examples of Linked Lists data structures                      | 38 |

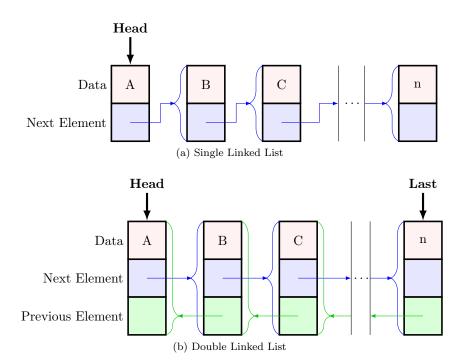

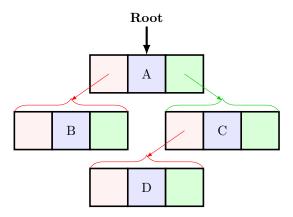

| 3.7 | Graphical example of a Binary Tree based data structure $$              | 39 |

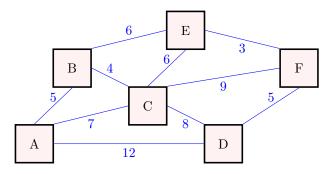

| 3.8 | Graphical example of a Graph data structure                             | 40 |

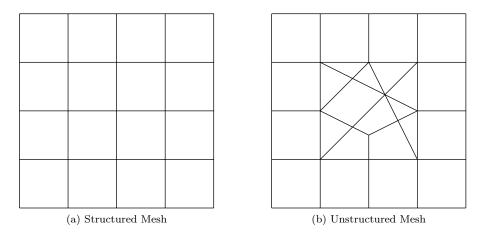

| 3.9 | Graphical examples of different types of Meshes                         | 41 |

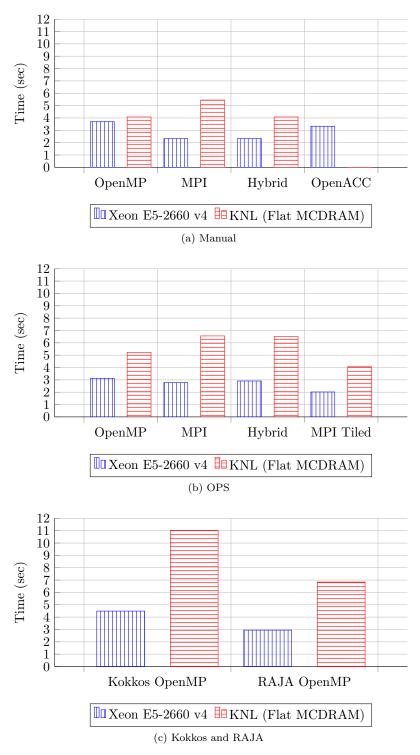

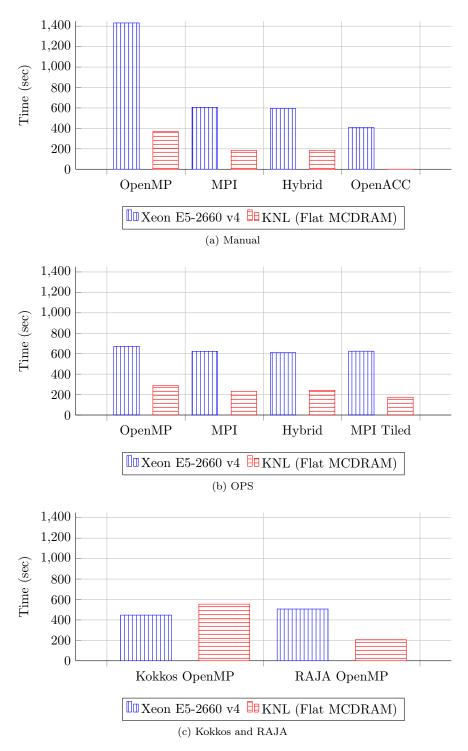

| 4.1 | Times for Tea<br>Leaf using $1000^2$ dataset on Central Processing Unit |    |

|     | (CPU) systems                                                           | 54 |

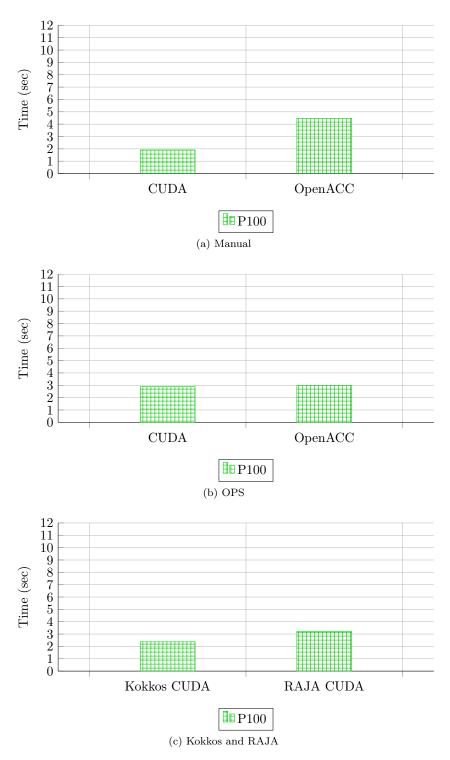

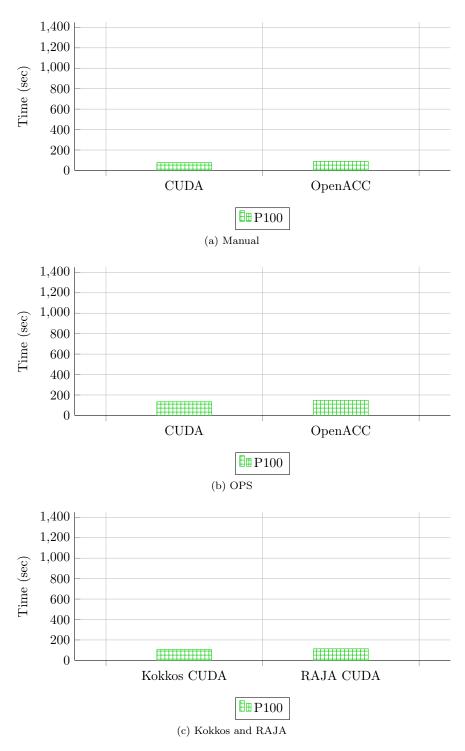

| 4.2 | Times for Tea<br>Leaf using $1000^2$ dataset on Graphics Processing     |    |

|     | Unit (GPU) systems                                                      | 55 |

| 4.3 | Times for TeaLeaf using $4000^2$ dataset on CPU systems                 | 56 |

| 4.4 | Times for TeaLeaf using $4000^2$ dataset on GPU systems                 | 57 |

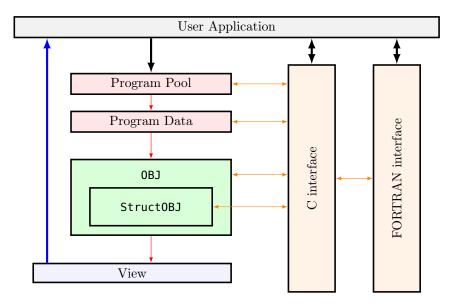

| 5.1 | Graphical representation of the original structure and control flow     |    |

|     | of Warryick Data Store (WDS)                                            | 79 |

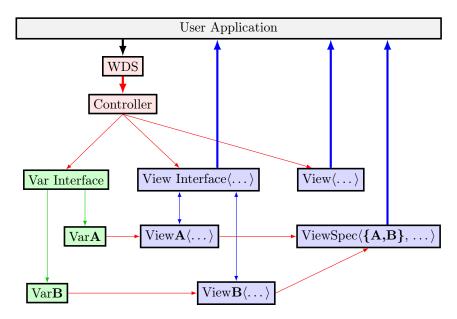

| 5.2 | Graphical representation of the structure and control flow of the           |

|-----|-----------------------------------------------------------------------------|

|     | final version of WDS                                                        |

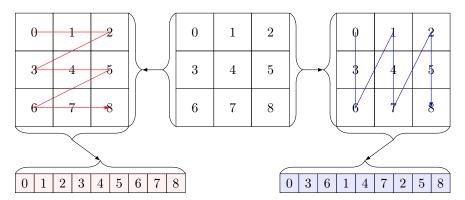

| 5.3 | Graphical example of how the order of the data can differ, without          |

|     | changing the underlying data structure                                      |

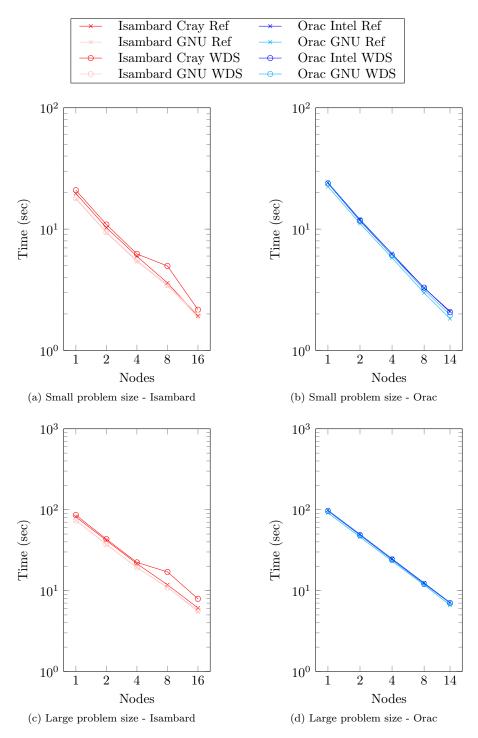

| 6.1 | Strong scaling results for MiniMD across all architectures and              |

|     | compilers for one to $16$ nodes on Isambard and one to $14$ nodes           |

|     | for Orac, utilising both problem sizes $(64^3,\ 1000\ \text{timesteps}$ for |

|     | small problem size, $128^3$ , $500$ timesteps for large problem size) $128$ |

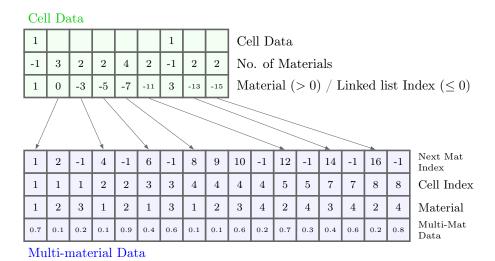

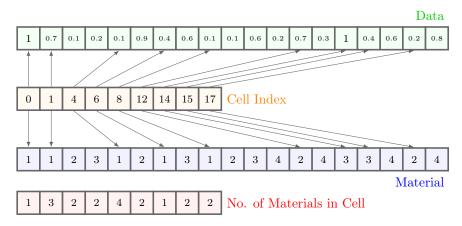

| 7.1 | Graphic representation of multi-material mesh $3\times 3$ mesh with         |

|     | four materials                                                              |

| 7.2 | Graphical representation of Fogerty et al. Compact Cell [23] data           |

|     | structure using the example mesh shown in Figure 7.1 134                    |

| 7.3 | Graphical representation of WDS' Compact Cell Flat data struc-              |

|     | ture using the example mesh shown in Figure 7.1 135                         |

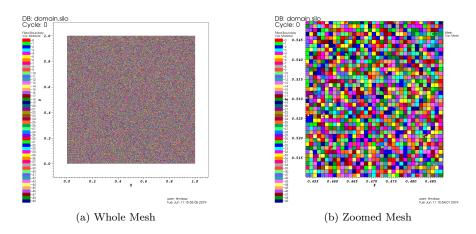

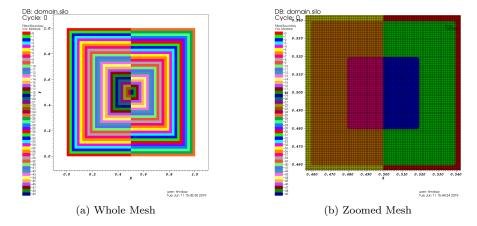

| 7.4 | Graphical example of a randomised multi-material mesh 142                   |

| 7.5 | Graphical example of a geometric multi-material mesh 142                    |

# List of Tables

| 4.1 | Systems utilised to measure the performance of the different ver-        |

|-----|--------------------------------------------------------------------------|

|     | sion of TeaLeaf                                                          |

| 4.2 | Computational architectural efficiency (%) and Performance Porta-        |

|     | bility $(P)$ on Xeon Broadwell, Intel's Xeon Phi Knights Land-           |

|     | ing (KNL) (Multi-Channel Dynamic Random Access Memory                    |

|     | (MCDRAM)) and a P100 card for the larger dataset $(4000^2)$ 63           |

| 4.3 | Memory bandwidth architectural efficiency (%) and Performance            |

|     | Portability $(P)$ on Xeon Broadwell, KNL (MCDRAM) and a                  |

|     | P100 card for the larger dataset $(4000^2)$ 63                           |

| 4.4 | Application efficiency (%) and Performance Portability $(P)$ on          |

|     | Xeon Broadwell, KNL (MCDRAM) and a P100 card for the larger              |

|     | dataset $(4000^2)$                                                       |

| 6.1 | Systems used to measure the performance impact of Warwick                |

|     | Data Store (WDS) when testing benchmarks 111                             |

| 6.2 | Results for different benchmark kernels across architectures, com-       |

|     | pilers and data structures                                               |

| 6.3 | Input sizes for small and large problems across all mini-aplications 113 |

| 6.4 | Systems used to measure the performance impact of WDS when               |

|     | tesing mini applications                                                 |

| 6.5 | Results for BookLeaf input decks across architectures, compilers         |

|     | and input decks                                                          |

| 6.6 | Results for TeaLeaf Message Passing Interface (MPI), across all          |

|     | input decks, solvers, architectures and compilers                        |

| 6.7 | Results for TeaLeaf OpenMP, across all input decks, solvers, ar-         |

|     | chitectures and compilers                                                |

| 6.8  | Results for TeaLeaf MPI and OpenMP, across all input decks,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | solvers, architectures and compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 122 |

| 6.9  | Results for MiniMD input decks, across all architectures and com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | pilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 124 |

| 6.10 | Results showing the overhead for all strong scaling results utilis-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | ing MiniMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 127 |

| 7.1  | Results of multi-material average kernel within Benchmarking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | suite, across different architectures and compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 143 |

| 7.2  | Results of multi-material Equation of State (EOS) kernels within                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | Benchmarking suite, across different architectures and compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 144 |

| A.1  | List of the manual implementation of TeaLeaf with compilers and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|      | corresponding flags used on the single node, multi-core systems $% \left( 1\right) =\left( 1\right) \left( $ | 167 |

| A.2  | List of the Oxford Parallel Library for Structured mesh solvers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |